Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 35                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 13x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

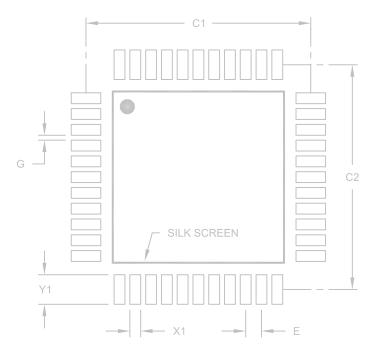

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 44-TQFP                                                                        |

| Supplier Device Package    | 44-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp504t-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

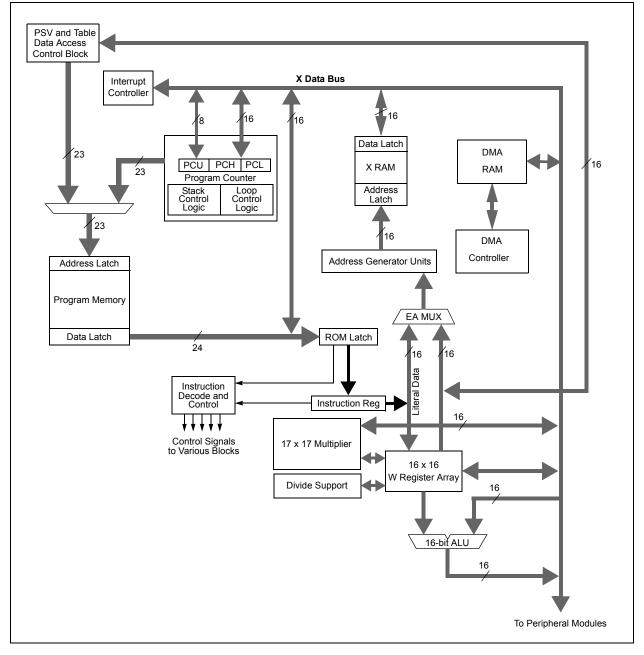

### 3.3 Special MCU Features

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 features a 17-bit by 17bit, single-cycle multiplier. The multiplier can perform signed, unsigned and mixed-sign multiplication. Using a 17-bit by 17-bit multiplier for 16-bit by 16-bit multiplication makes mixed-sign multiplication possible. The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices support 16/16 and 32/16 integer divide operations. All divide instructions are iterative operations. They must be executed within a REPEAT loop, resulting in a total execution time of 19 instruction cycles. The divide operation can be interrupted during any of those 19 cycles without loss of data.

A multi-bit data shifter is used to perform up to a 16-bit, left or right shift in a single cycle.

# FIGURE 3-1: PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04 CPU CORE BLOCK DIAGRAM

# TABLE 4-10: UART2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15                          | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6   | Bit 5 | Bit 4      | Bit 3        | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|----------|-------------|---------------------------------|--------|----------|--------|--------|--------|-------|-------|--------|---------|-------|------------|--------------|-------|--------|-------|---------------|

| U2MODE   | 0230        | UARTEN                          | —      | USIDL    | IREN   | RTSMD  | —      | UEN1  | UEN0  | WAKE   | LPBACK  | ABAUD | URXINV     | BRGH         | PDSE  | L<1:0> | STSEL | 0000          |

| U2STA    | 0232        | UTXISEL1                        | UTXINV | UTXISEL0 | —      | UTXBRK | UTXEN  | UTXBF | TRMT  | URXISE | EL<1:0> | ADDEN | RIDLE      | PERR         | FERR  | OERR   | URXDA | 0110          |

| U2TXREG  | 0234        | _                               | _      | _        | _      | _      | _      | _     | UTX8  |        |         | U     | ART Transm | nit Register |       |        |       | XXXX          |

| U2RXREG  | 0236        | _                               | _      | _        | _      | _      | _      | _     | URX8  |        |         | U     | ART Receiv | e Register   |       |        |       | 0000          |

| U2BRG    | 0238        | Baud Rate Generator Prescaler C |        |          |        |        |        |       | 0000  |        |         |       |            |              |       |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-11: SPI1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8       | Bit 7        | Bit 6    | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|---------|--------|--------|--------|------------|-------------|--------------|----------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI1STAT | 0240        | SPIEN  | _      | SPISIDL | —      | —      | —      | _          | _           | —            | SPIROV   | —     | _     | —         | —     | SPITBF | SPIRBF | 0000          |

| SPI1CON1 | 0242        | —      | _      | _       | DISSCK | DISSDO | MODE16 | SMP        | CKE         | SSEN         | CKP      | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI1CON2 | 0244        | FRMEN  | SPIFSD | FRMPOL  | —      | —      | —      | -          | -           | —            | _        | —     |       | _         | —     | FRMDLY | _      | 0000          |

| SPI1BUF  | 0248        |        |        |         |        |        |        | SPI1 Trans | mit and Red | ceive Buffer | Register |       |       |           |       |        |        | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-12: SPI2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                        | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6  | Bit 5 | Bit 4 | Bit 3     | Bit 2 | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|-----------------------------------------------|---------|--------|--------|--------|-------|-------|-------|--------|-------|-------|-----------|-------|--------|--------|---------------|

| SPI2STAT | 0260        | SPIEN  | —                                             | SPISIDL | _      | —      | —      |       | —     | —     | SPIROV | —     | _     | —         |       | SPITBF | SPIRBF | 0000          |

| SPI2CON1 | 0262        | _      | _                                             | _       | DISSCK | DISSDO | MODE16 | SMP   | CKE   | SSEN  | CKP    | MSTEN |       | SPRE<2:0> |       | PPRE   | <1:0>  | 0000          |

| SPI2CON2 | 0264        | FRMEN  | SPIFSD                                        | FRMPOL  | _      | _      | _      | -     | —     | _     | _      | —     | _     | _         | —     | FRMDLY | —      | 0000          |

| SPI2BUF  | 0268        |        | SPI2 Transmit and Receive Buffer Register 000 |         |        |        |        |       | 0000  |       |        |       |       |           |       |        |        |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 4-13: ADC1 REGISTER MAP FOR PIC24HJ64GP202/502, PIC24HJ128GP202/502 AND PIC24HJ32GP302

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10   | Bit 9   | Bit 8   | Bit 7       | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|----------|---------|---------|-------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |          |         | ADC Da  | ta Buffer 0 |           |       |       |        |          |          |         | XXXX          |

| AD1CON1   | 0320 | ADON   | _        | ADSIDL | ADDMABM | —      | AD12B    | FOR     | M<1:0>  | ;           | SSRC<2:0> |       | —     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       | _      | CSCNA    | CHP     | S<1:0>  | BUFS        | _         |       | SMPI  | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _        | _      |         | S      | AMC<4:0> |         |         |             |           |       | ADCS  | <7:0>  |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N   | NB<1:0> | CH123SB | _           | _         | _     | _     | _      | CH123N   | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | C      | H0SB<4:0 | >       |         | CH0NA       | _         | _     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _        | _      | PCFG12  | PCFG11 | PCFG10   | PCFG9   | _       | _           | _         | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | —      | _        | —      | CSS12   | CSS11  | CSS10    | CSS9    | —       | —           | _         | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          |        | _       | —      | -        |         | _       |             | _         | _     |       | _      | [        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-14: ADC1 REGISTER MAP FOR PIC24HJ64GP204/504, PIC24HJ128GP204/504 AND PIC24HJ32GP304

| File Name | Addr | Bit 15 | Bit 14   | Bit 13 | Bit 12  | Bit 11 | Bit 10    | Bit 9    | Bit 8   | Bit 7        | Bit 6     | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|----------|--------|---------|--------|-----------|----------|---------|--------------|-----------|-------|-------|--------|----------|----------|---------|---------------|

| ADC1BUF0  | 0300 |        |          |        |         |        |           |          | ADC Da  | ata Buffer 0 |           |       |       |        |          |          |         | xxxx          |

| AD1CON1   | 0320 | ADON   | —        | ADSIDL | ADDMABM | —      | AD12B     | FOR      | M<1:0>  | :            | SSRC<2:0> |       | —     | SIMSAM | ASAM     | SAMP     | DONE    | 0000          |

| AD1CON2   | 0322 | V      | 'CFG<2:0 | >      | _       | _      | CSCNA     | CHP      | S<1:0>  | BUFS         | _         |       | SMP   | <3:0>  |          | BUFM     | ALTS    | 0000          |

| AD1CON3   | 0324 | ADRC   | _        | _      |         | S      | AMC<4:0>  |          |         |              |           |       | ADCS  | <7:0>  |          |          |         | 0000          |

| AD1CHS123 | 0326 | _      | _        | _      | _       | _      | CH123N    | IB<1:0>  | CH123SB | _            | _         | _     | _     | _      | CH123    | NA<1:0>  | CH123SA | 0000          |

| AD1CHS0   | 0328 | CH0NB  | _        | _      |         | C      | +0SB<4:0> | <b>`</b> |         | CH0NA        | _         | _     |       | С      | H0SA<4:0 | >        |         | 0000          |

| AD1PCFGL  | 032C | _      | _        | _      | PCFG12  | PCFG11 | PCFG10    | PCFG9    | PCFG8   | PCFG7        | PCFG6     | PCFG5 | PCFG4 | PCFG3  | PCFG2    | PCFG1    | PCFG0   | 0000          |

| AD1CSSL   | 0330 | _      | _        | _      | CSS12   | CSS11  | CSS10     | CSS9     | CSS8    | CSS7         | CSS6      | CSS5  | CSS4  | CSS3   | CSS2     | CSS1     | CSS0    | 0000          |

| AD1CON4   | 0332 | _      |          | _      | _       |        | _         | _        | _       | _            | _         | _     |       | _      | I        | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| U-0          | R/W-1        | R/W-0                                     | R/W-0          | U-0                    | R/W-1                       | R/W-0           | R/W-0 |

|--------------|--------------|-------------------------------------------|----------------|------------------------|-----------------------------|-----------------|-------|

| _            |              | C1IP<2:0> <sup>(1)</sup>                  |                | _                      |                             | C1RXIP<2:0>(1)  |       |

| bit 15       | •            |                                           |                |                        |                             |                 | bit 8 |

|              |              |                                           |                |                        |                             |                 |       |

| U-0          | R/W-1        | R/W-0                                     | R/W-0          | U-0                    | R/W-1                       | R/W-0           | R/W-0 |

| —            |              | SPI2IP<2:0>                               |                | _                      |                             | SPI2EIP<2:0>    |       |

| bit 7        |              |                                           |                |                        |                             |                 | bit C |

| Legend:      |              |                                           |                |                        |                             |                 |       |

| R = Readab   | le bit       | W = Writable b                            | oit            | U = Unimple            | mented bit, re              | ead as '0'      |       |

| -n = Value a | t POR        | '1' = Bit is set                          |                | '0' = Bit is cle       |                             | x = Bit is unkn | own   |

|              |              |                                           |                |                        |                             |                 |       |

| bit 15       | Unimpleme    | ented: Read as '0                         | ,              |                        |                             |                 |       |

| bit 14-12    | C1IP<2:0>:   | ECAN1 Event In                            | terrupt Priori | ty bits <sup>(1)</sup> |                             |                 |       |

|              | 111 = Interr | rupt is priority 7 (h                     | nighest priori | ty interrupt)          |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              |              | rupt is priority 1                        |                |                        |                             |                 |       |

|              |              | rupt source is disa                       |                |                        |                             |                 |       |

| bit 11       |              | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 10-8     |              | 0>: ECAN1 Rece                            |                |                        | riority bits <sup>(1)</sup> |                 |       |

|              | 111 = Interr | rupt is priority 7 (h                     | highest priori | ty interrupt)          |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              |              | rupt is priority 1                        |                |                        |                             |                 |       |

| h:+ 7        |              | rupt source is disa                       |                |                        |                             |                 |       |

| bit 7        | -            | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 6-4      |              | SPI2 Event Int<br>rupt is priority 7 (h   | -              | -                      |                             |                 |       |

|              | •            |                                           | lighest phon   | ly interrupt)          |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | •            | unt in priority 1                         |                |                        |                             |                 |       |

|              |              | rupt is priority 1<br>rupt source is disa | abled          |                        |                             |                 |       |

| bit 3        |              | ented: Read as '0                         |                |                        |                             |                 |       |

| bit 2-0      | -            | :0>: SPI2 Error In                        |                | tv bits                |                             |                 |       |

|              |              | rupt is priority 7 (h                     |                | •                      |                             |                 |       |

|              | •            |                                           | -              |                        |                             |                 |       |

|              | •            |                                           |                |                        |                             |                 |       |

|              | 001 = Interr | rupt is priority 1                        |                |                        |                             |                 |       |

|              |              | rupt io priority i<br>rupt course is die  |                |                        |                             |                 |       |

# 000 = Interrupt source is disabled

Note 1: Interrupts disabled on devices without ECAN<sup>™</sup> modules.

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|---------------|---------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| _             |               | CRCIP<2:0>                             |                 | _                |                  | U2EIP<2:0>      |       |

| bit 15        |               |                                        |                 |                  |                  |                 | bit 8 |

|               |               |                                        |                 |                  |                  |                 |       |

| U-0           | R/W-1         | R/W-0                                  | R/W-0           | U-0              | U-0              | U-0             | U-0   |

|               |               | U1EIP<2:0>                             |                 |                  |                  |                 |       |

| bit 7         |               |                                        |                 |                  |                  |                 | bit   |

| Legend:       |               |                                        |                 |                  |                  |                 |       |

| R = Readabl   | e bit         | W = Writable                           | bit             | U = Unimple      | mented bit, read | d as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |

|               |               |                                        |                 |                  |                  |                 |       |

| bit 15        | -             | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 14-12     |               | CRC Generate                           |                 |                  | ty bits          |                 |       |

|               | 111 = Interro | upt is priority 7 (                    | highest priorit | ty interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 11        |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 10-8      | -             | : UART2 Error I                        |                 | ity bite         |                  |                 |       |

| DIL 10-0      |               | upt is priority 7 (                    |                 | •                |                  |                 |       |

|               | •             |                                        | nightest phone  | ly interrupt)    |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               | upt is priority 1<br>upt source is dis | abled           |                  |                  |                 |       |

| bit 7         |               | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 6-4       | -             | UART1 Error I                          |                 | itv bits         |                  |                 |       |

|               |               | upt is priority 7 (                    | -               | -                |                  |                 |       |

|               | •             | · · · · · · · · · · · · · · ·          | 5               | - <b>J</b>       |                  |                 |       |

|               | •             |                                        |                 |                  |                  |                 |       |

|               |               |                                        |                 |                  |                  |                 |       |

|               | •             | upt is priority 1                      |                 |                  |                  |                 |       |

bit 3-0 Unimplemented: Read as '0'

# 8.3 DMA Control Registers

| <b>D 2 1 1</b>     | <b>D</b> *** * | <b>D</b> # • * •                       | <b>D</b> # • * * | <b>D</b> #14.4   |                  |                   |          |

|--------------------|----------------|----------------------------------------|------------------|------------------|------------------|-------------------|----------|

| R/W-0              | R/W-0          | R/W-0                                  | R/W-0            | R/W-0            | U-0              | U-0               | U-0      |

| CHEN               | SIZE           | DIR                                    | HALF             | NULLW            |                  | —                 |          |

| bit 15             |                |                                        |                  |                  |                  |                   | bit 8    |

|                    |                |                                        |                  |                  |                  |                   |          |

| U-0                | U-0            | R/W-0                                  | R/W-0            | U-0              | U-0              | R/W-0             | R/W-0    |

|                    | —              | AMOD                                   | E<1:0>           |                  |                  | MODE              | <1:0>    |

| bit 7              |                |                                        |                  |                  |                  |                   | bit 0    |

|                    |                |                                        |                  |                  |                  |                   |          |

| Legend:            |                |                                        |                  |                  |                  |                   |          |

| R = Readable       | e bit          | W = Writable                           | bit              | U = Unimple      | mented bit, read | d as '0'          |          |

| -n = Value at      | POR            | '1' = Bit is set                       |                  | '0' = Bit is cle | eared            | x = Bit is unkno  | own      |

|                    |                |                                        |                  |                  |                  |                   |          |

| bit 15             | CHEN: Char     | nel Enable bit                         |                  |                  |                  |                   |          |

|                    | 1 = Channel    | enabled                                |                  |                  |                  |                   |          |

|                    | 0 = Channel    | disabled                               |                  |                  |                  |                   |          |

| bit 14             | SIZE: Data T   | ransfer Size bit                       |                  |                  |                  |                   |          |

|                    | 1 = Byte       |                                        |                  |                  |                  |                   |          |

|                    | 0 = Word       |                                        | <i></i>          |                  | ~                |                   |          |

| bit 13             |                | r Direction bit (s                     |                  |                  | -                |                   |          |

|                    |                | m DMA RAM ao<br>m peripheral ad        |                  |                  |                  |                   |          |

| bit 12             |                | Block Transfer                         |                  |                  |                  |                   |          |

| 51172              |                | lock transfer co                       | •                | •                |                  | een moved         |          |

|                    |                | lock transfer co                       |                  |                  |                  |                   |          |

| bit 11             |                | I Data Periphera                       |                  |                  |                  |                   |          |

|                    | 1 = Null data  | write to periphe                       | eral in addition | n to DMA RAM     | write (DIR bit r | nust also be clea | ar)      |

|                    | 0 = Normal c   | peration                               |                  |                  |                  |                   |          |

| bit 10-6           | Unimplemer     | nted: Read as '                        | 0'               |                  |                  |                   |          |

| bit 5-4            | AMODE<1:0      | >: DMA Chann                           | el Operating I   | Mode Select bi   | ts               |                   |          |

|                    |                | ed (acts as Peri                       |                  |                  | node)            |                   |          |

|                    |                | eral Indirect Add                      |                  |                  |                  |                   |          |

|                    |                | r Indirect withou<br>r Indirect with F |                  |                  |                  |                   |          |

| bit 3-2            | 0              | nted: Read as '                        |                  | it mode          |                  |                   |          |

| bit 0 2<br>bit 1-0 |                | : DMA Channel                          |                  | ode Select hits  |                  |                   |          |

| bit i o            |                |                                        |                  |                  |                  | each DMA RAM      | buffer)  |

|                    |                | ious, Ping-Pong                        |                  |                  |                  |                   | building |

|                    | 01 = One-Sh    | ot, Ping-Pong r                        | nodes disable    | ed               |                  |                   |          |

|                    | 00 = Continu   | ious, Ping-Pong                        | modes disat      | bled             |                  |                   |          |

|                    |                |                                        |                  |                  |                  |                   |          |

# REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

# REGISTER 8-9: DSADR: MOST RECENT DMA RAM ADDRESS

| R-0             | R-0 | R-0              | R-0  | R-0                 | R-0           | R-0             | R-0   |

|-----------------|-----|------------------|------|---------------------|---------------|-----------------|-------|

|                 |     |                  | DSAD | R<15:8>             |               |                 |       |

| bit 15          |     |                  |      |                     |               |                 | bit 8 |

|                 |     |                  |      |                     |               |                 |       |

| R-0             | R-0 | R-0              | R-0  | R-0                 | R-0           | R-0             | R-0   |

|                 |     |                  | DSAD | )R<7:0>             |               |                 |       |

| bit 7           |     |                  |      |                     |               |                 | bit 0 |

|                 |     |                  |      |                     |               |                 |       |

| Legend:         |     |                  |      |                     |               |                 |       |

| R = Readable I  | bit | W = Writable b   | it   | U = Unimplemer      | ited bit, rea | d as '0'        |       |

| -n = Value at P | OR  | '1' = Bit is set |      | '0' = Bit is cleare | d             | x = Bit is unkr | nown  |

bit 15-0 DSADR<15:0>: Most Recent DMA RAM Address Accessed by DMA Controller bits

# REGISTER 11-21: RPOR6: PERIPHERAL PIN SELECT OUTPUT REGISTERS 6

| U-0             | U-0 | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-----|------------------|-------|------------------|-----------------|-----------------|-------|

|                 | _   |                  |       |                  | RP13R<4:0       | >               |       |

| bit 15          |     |                  |       |                  |                 |                 | bit 8 |

|                 |     |                  | DAMA  | D/// 0           |                 | DAVO            | DAVA  |

| U-0             | U-0 | U-0              | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _               |     | _                |       |                  | RP12R<4:0       | >               |       |

| bit 7           |     |                  |       |                  |                 |                 | bit 0 |

| Legend:         |     |                  |       |                  |                 |                 |       |

| R = Readable    | bit | W = Writable I   | oit   | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at P | OR  | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 15-13 | Unimplemented: Read as '0'                                                                                                               |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 12-8  | <b>RP13R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP13 Output Pin bits (see Table 11-2 for peripheral function numbers) |

| bit 7-5   | Unimplemented: Read as '0'                                                                                                               |

| bit 4-0   | <b>RP12R&lt;4:0&gt;:</b> Peripheral Output Function is Assigned to RP12 Output Pin bits (see Table 11-2 for peripheral function numbers) |

### REGISTER 11-22: RPOR7: PERIPHERAL PIN SELECT OUTPUT REGISTERS 7

| U-0    | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|--------|-----|-----|-------|-------|------------|-------|-------|

| —      | —   | —   |       |       | RP15R<4:0> |       |       |

| bit 15 |     |     |       |       |            |       | bit 8 |

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|------------|-------|-------|

| —     | —   | —   |       |       | RP14R<4:0> |       |       |

| bit 7 |     |     |       |       |            |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-13 Unimplemented: Read as '0'

bit 12-8 **RP15R<4:0>:** Peripheral Output Function is Assigned to RP15 Output Pin bits (see Table 11-2 for peripheral function numbers)

bit 7-5 Unimplemented: Read as '0'

bit 4-0 **RP14R<4:0>:** Peripheral Output Function is Assigned to RP14 Output Pin bits (see Table 11-2 for peripheral function numbers)

# 12.2 Timer1 Control Register

# REGISTER 12-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0  | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-------|-----|-----|-----|-----|-------|

| TON    | —   | TSIDL | —   | —   | —   | _   | —     |

| bit 15 |     |       |     |     |     |     | bit 8 |

|        |     |       |     |     |     |     |       |

| U-0   | R/W-0 | R/W-0      | R/W-0 | U-0 | R/W-0 | R/W-0 | U-0   |

|-------|-------|------------|-------|-----|-------|-------|-------|

| —     | TGATE | TCKPS<1:0> |       |     | TSYNC | TCS   | —     |

| bit 7 |       |            |       |     |       |       | bit 0 |

| Legend:      |                 |                                                         |                            |                    |

|--------------|-----------------|---------------------------------------------------------|----------------------------|--------------------|

| R = Readal   | ble bit         | W = Writable bit                                        | U = Unimplemented bit,     | read as '0'        |

| -n = Value a | at POR          | '1' = Bit is set                                        | '0' = Bit is cleared       | x = Bit is unknown |

|              |                 |                                                         |                            |                    |

| bit 15       | TON: Time       |                                                         |                            |                    |

|              |                 | 16-bit Timer1                                           |                            |                    |

| bit 11       | •               | 16-bit Timer1                                           |                            |                    |

| bit 14       | -               | nented: Read as '0'                                     |                            |                    |

| bit 13       |                 | op in Idle Mode bit                                     | on dovice entere Idle mode |                    |

|              |                 | ue module operation in Idle                             | en device enters Idle mode |                    |

| bit 12-7     |                 | nented: Read as '0'                                     |                            |                    |

| bit 6        | -               | imer1 Gated Time Accumul                                | ation Enable bit           |                    |

|              | When TCS        | <b>S</b> = 1:                                           |                            |                    |

|              | This bit is     |                                                         |                            |                    |

|              | When TCS        |                                                         |                            |                    |

|              |                 | time accumulation enabled<br>time accumulation disabled |                            |                    |

| bit 5-4      |                 |                                                         |                            |                    |

| DIL 3-4      | 11 = 1:25       | :0>: Timer1 Input Clock Pre                             |                            |                    |

|              | 10 = 1:64       |                                                         |                            |                    |

|              | 01 <b>= 1:8</b> |                                                         |                            |                    |

|              | 00 = 1:1        |                                                         |                            |                    |

| bit 3        | -               | nented: Read as '0'                                     |                            |                    |

| bit 2        |                 | ïmer1 External Clock Input                              | Synchronization Select bit |                    |

|              | <u>When TCS</u> | <u>S = 1:</u><br>ronize external clock input            |                            |                    |

|              | •               | t synchronize external clock                            | cinput                     |                    |

|              | When TCS        | •                                                       |                            |                    |

|              | This bit is     |                                                         |                            |                    |

| bit 1        | TCS: Time       | er1 Clock Source Select bit                             |                            |                    |

|              |                 | al clock from pin T1CK (on<br>al clock (Fcy)            | the rising edge)           |                    |

| bit 0        | Unimplem        | nented: Read as '0'                                     |                            |                    |

|              | -               |                                                         |                            |                    |

# PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 AND PIC24HJ128GPX02/X04

| U-0          | U-0                                                                | U-0                                                                                                 | U-0           | U-0               | U-0                | U-0             | U-0   |  |  |  |

|--------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|---------------|-------------------|--------------------|-----------------|-------|--|--|--|

|              | _                                                                  | _                                                                                                   | _             | _                 | _                  |                 | _     |  |  |  |

| bit 15       |                                                                    |                                                                                                     |               |                   |                    |                 | bit 8 |  |  |  |

|              |                                                                    |                                                                                                     |               |                   |                    |                 |       |  |  |  |

| R/W-0        | R/W-0                                                              | R/W-0 R/W-0 U-0 R/W-0 R/W-0 R/W-0                                                                   |               |                   |                    |                 | R/W-0 |  |  |  |

| IVRIE        | WAKIE                                                              | ERRIE                                                                                               |               | FIFOIE            | RBOVIE             | RBIE            | TBIE  |  |  |  |

| bit 7        |                                                                    |                                                                                                     |               |                   |                    |                 | bit 0 |  |  |  |

| Legend:      |                                                                    | C = Writeable                                                                                       | bit, but only | '0' can be writte | en to clear the bi | it              |       |  |  |  |

| R = Readab   | le bit                                                             | W = Writable                                                                                        |               |                   | mented bit, read   |                 |       |  |  |  |

| -n = Value a | t POR                                                              | '1' = Bit is set                                                                                    |               | '0' = Bit is cle  | ared               | x = Bit is unkr | nown  |  |  |  |

|              |                                                                    |                                                                                                     |               |                   |                    |                 |       |  |  |  |

| bit 15-8     |                                                                    | nted: Read as '                                                                                     |               |                   |                    |                 |       |  |  |  |

| bit 7        |                                                                    | d Message Rec                                                                                       |               | pt Enable bit     |                    |                 |       |  |  |  |

|              | 1 = Interrupt Request Enabled<br>0 = Interrupt Request not enabled |                                                                                                     |               |                   |                    |                 |       |  |  |  |

| L:1 0        | •                                                                  | •                                                                                                   |               | 1 h 14            |                    |                 |       |  |  |  |

| bit 6        |                                                                    | us Wake-up Activity Interrupt Flag bit<br>pt Request Enabled                                        |               |                   |                    |                 |       |  |  |  |

|              |                                                                    | Request not en                                                                                      |               |                   |                    |                 |       |  |  |  |

| bit 5        |                                                                    | r Interrupt Enab                                                                                    |               |                   |                    |                 |       |  |  |  |

|              |                                                                    | = Interrupt Request Enabled                                                                         |               |                   |                    |                 |       |  |  |  |

|              | 0 = Interrupt Request not enabled                                  |                                                                                                     |               |                   |                    |                 |       |  |  |  |

| bit 4        | Unimpleme                                                          | nted: Read as '                                                                                     | 0'            |                   |                    |                 |       |  |  |  |

| bit 3        | FIFOIE: FIFO                                                       | O Almost Full In                                                                                    | terrupt Enabl | e bit             |                    |                 |       |  |  |  |

|              |                                                                    | Request Enable                                                                                      |               |                   |                    |                 |       |  |  |  |

|              | •                                                                  | Request not en                                                                                      |               |                   |                    |                 |       |  |  |  |

| bit 2        |                                                                    | RBOVIE: RX Buffer Overflow Interrupt Enable bit                                                     |               |                   |                    |                 |       |  |  |  |

|              | 1 = Interrupt Request Enabled                                      |                                                                                                     |               |                   |                    |                 |       |  |  |  |

| bit 1        |                                                                    | <ul> <li>0 = Interrupt Request not enabled</li> <li>RBIE: RX Buffer Interrupt Enable bit</li> </ul> |               |                   |                    |                 |       |  |  |  |

| DILI         |                                                                    | Request Enable                                                                                      |               |                   |                    |                 |       |  |  |  |

|              |                                                                    | Request not en                                                                                      |               |                   |                    |                 |       |  |  |  |

|              |                                                                    | iffer Interrupt En                                                                                  |               |                   |                    |                 |       |  |  |  |

| bit 0        |                                                                    |                                                                                                     | ומטוכ טונ     |                   |                    |                 |       |  |  |  |

| bit U        |                                                                    | Request Enable                                                                                      |               |                   |                    |                 |       |  |  |  |

# 20.0 10-BIT/12-BIT ANALOG-TO-DIGITAL CONVERTER (ADC1)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 of families devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Analog-to-Digital Converter (ADC)" (DS70183) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com). 2: Some registers and associated bits

- described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices have up to 13 ADC input channels.

The AD12B bit (AD1CON1<10>) allows each of the ADC modules to be configured by the user as either a 10-bit, 4-sample/hold ADC (default configuration) or a 12-bit, 1-sample/hold ADC.

Note: The ADC module needs to be disabled before modifying the AD12B bit.

# 20.1 Key Features

The 10-bit ADC configuration has the following key features:

- Successive Approximation (SAR) conversion

- Conversion speeds of up to 1.1 Msps

- Up to 13 analog input pins

- External voltage reference input pins

- Simultaneous sampling of up to four analog input pins

- Automatic Channel Scan mode

- Selectable conversion trigger source

- Selectable Buffer Fill modes

- · Operation during CPU Sleep and Idle modes

The 12-bit ADC configuration supports all the above features, except:

- In the 12-bit configuration, conversion speeds of up to 500 ksps are supported

- There is only one sample/hold amplifier in the 12-bit configuration, so simultaneous sampling of multiple channels is not supported.

Depending on the particular device pinout, the ADC can have up to 13 analog input pins, designated AN0 through AN12. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs can be shared with other analog input pins. The actual number of analog input pins and external voltage reference input configuration depends on the specific device.

Block diagrams of the ADC module are shown in Figure 20-1 and Figure 20-2.

# 20.2 ADC Initialization

The following configuration steps should be performed.

- 1. Configure the ADC module:

- a) Select port pins as analog inputs (AD1PCFGH<15:0> or AD1PCFGL<15:0>)

- b) Select voltage reference source to match expected range on analog inputs (AD1CON2<15:13>)

- c) Select the analog conversion clock to match desired data rate with processor clock (AD1CON3<7:0>)

- d) Determine how many S/H channels are used (AD1CON2<9:8> and AD1PCFGH<15:0> or AD1PCFGL<15:0>)

- e) Select the appropriate sample/conversion sequence (AD1CON1<7:5> and AD1CON3<12:8>)

- f) Select how conversion results are presented in the buffer (AD1CON1<9:8>)

- g) Turn on ADC module (AD1CON1<15>)

- 2. Configure ADC interrupt (if required):

- a) Clear the AD1IF bit

- b) Select ADC interrupt priority

# 20.3 ADC and DMA

If more than one conversion result needs to be buffered before triggering an interrupt, DMA data transfers can be used. ADC1 can trigger a DMA data transfer. If ADC1 is selected as the DMA IRQ source, a DMA transfer occurs when the AD1IF bit gets set as a result of an ADC1 sample conversion sequence.

The SMPI<3:0> bits (AD1CON2<5:2>) are used to select how often the DMA RAM buffer pointer is incremented.

The ADDMABM bit (AD1CON1<12>) determines how the conversion results are filled in the DMA RAM buffer area being used for ADC. If this bit is set, DMA buffers are written in the order of conversion. The module provides an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer. If the ADDMABM bit is cleared, then DMA buffers are written in Scatter/Gather mode. The module provides a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer.

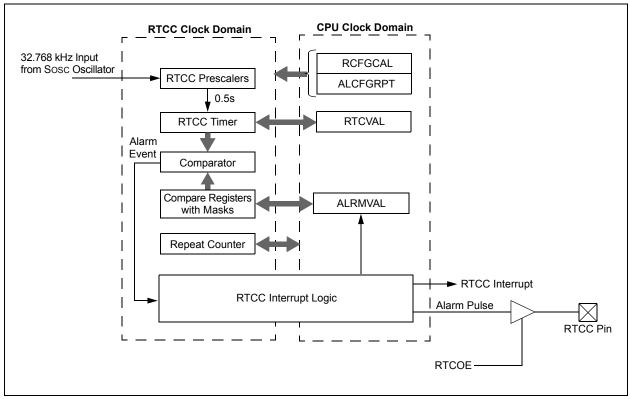

# 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

- Note 1: This data sheet summarizes the features PIC24HJ32GP302/304, of the PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Real-Time Clock and Calendar (RTCC)" (DS70301) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

This chapter discusses the Real-Time Clock and Calendar (RTCC) module, available on PIC24HJ32GP302/304, PIC24HJ64GPX02/X04 and PIC24HJ128GPX02/X04 devices, and its operation.

Some of the key features of this module are:

- Time: hours, minutes and seconds

- 24-hour format (military time)

- · Calendar: weekday, date, month and year

- Alarm configurable

- Year range: 2000 to 2099

- · Leap year correction

- BCD format for compact firmware

- Optimized for low-power operation

- · User calibration with auto-adjust

- Calibration range: ±2.64 seconds error per month

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

The RTCC module is intended for applications where accurate time must be maintained for extended periods of time with minimum to no intervention from the CPU. The RTCC module is optimized for low-power usage to provide extended battery lifetime while keeping track of time.

The RTCC module is a 100-year clock and calendar with automatic leap year detection. The range of the clock is from 00:00:00 (midnight) on January 1, 2000 to 23:59:59 on December 31, 2099.

The hours are available in 24-hour (military time) format. The clock provides a granularity of one second with half-second visibility to the user.

# FIGURE 22-1: RTCC BLOCK DIAGRAM

© 2007-2012 Microchip Technology Inc.

| TABLE 26-2 | INSTRUCTION SET OVERVIEW | (CONTINUED) |  |

|------------|--------------------------|-------------|--|

|            |                          |             |  |

| Base<br>Instr<br># | Assembly<br>Mnemonic |        | Assembly Syntax | Description                                       | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------|-----------------|---------------------------------------------------|---------------|----------------|--------------------------|

| 35                 | INC                  | INC    | f               | f = f + 1                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | f,WREG          | WREG = f + 1                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC    | Ws,Wd           | Wd = Ws + 1                                       | 1             | 1              | C,DC,N,OV,Z              |

| 36                 | INC2                 | INC2   | f               | f = f + 2                                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | f,WREG          | WREG = f + 2                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | INC2   | Ws,Wd           | Wd = Ws + 2                                       | 1             | 1              | C,DC,N,OV,Z              |

| 37                 | IOR                  | IOR    | f               | f = f .IOR. WREG                                  | 1             | 1              | N,Z                      |

|                    |                      | IOR    | f,WREG          | WREG = f .IOR. WREG                               | 1             | 1              | N,Z                      |

|                    |                      | IOR    | #lit10,Wn       | Wd = lit10 .IOR. Wd                               | 1             | 1              | N,Z                      |

|                    |                      | IOR    | Wb,Ws,Wd        | Wd = Wb .IOR. Ws                                  | 1             | 1              | N,Z                      |

|                    |                      | IOR    | Wb,#lit5,Wd     | Wd = Wb .IOR. lit5                                | 1             | 1              | N,Z                      |

| 38                 | LNK                  | LNK    | #lit14          | Link Frame Pointer                                | 1             | 1              | None                     |

| 39                 | LSR                  | LSR    | f               | f = Logical Right Shift f                         | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | f,WREG          | WREG = Logical Right Shift f                      | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | Ws,Wd           | Wd = Logical Right Shift Ws                       | 1             | 1              | C,N,OV,Z                 |

|                    |                      | LSR    | Wb,Wns,Wnd      | Wnd = Logical Right Shift Wb by Wns               | 1             | 1              | N,Z                      |

|                    |                      | LSR    | Wb,#lit5,Wnd    | Wnd = Logical Right Shift Wb by lit5              | 1             | 1              | N,Z                      |

| 40                 | MOV                  | MOV    | f,Wn            | Move f to Wn                                      | 1             | 1              | None                     |

|                    |                      | MOV    | f               | Move f to f                                       | 1             | 1              | None                     |

|                    |                      | MOV    | f,WREG          | Move f to WREG                                    | 1             | 1              | N,Z                      |

|                    |                      | MOV    | #lit16,Wn       | Move 16-bit literal to Wn                         | 1             | 1              | None                     |

|                    |                      | MOV.b  | #lit8,Wn        | Move 8-bit literal to Wn                          | 1             | 1              | None                     |

|                    |                      | MOV    | Wn,f            | Move Wn to f                                      | 1             | 1              | None                     |

|                    |                      | MOV    | Wso,Wdo         | Move Ws to Wd                                     | 1             | 1              | None                     |

|                    |                      | MOV    | WREG, f         | Move WREG to f                                    | 1             | 1              | None                     |

|                    |                      | MOV.D  | Wns,Wd          | Move Double from W(ns):W(ns + 1) to Wd            | 1             | 2              | None                     |

|                    |                      | MOV.D  | Ws,Wnd          | Move Double from Ws to W(nd + 1):W(nd)            | 1             | 2              | None                     |

| 41                 | MUL                  | MUL.SS | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * signed(Ws)          | 1             | 1              | None                     |

|                    |                      | MUL.SU | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = signed(Wb) * unsigned(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.US | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) * signed(Ws)        | 1             | 1              | None                     |

|                    |                      | MUL.UU | Wb,Ws,Wnd       | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(Ws)   | 1             | 1              | None                     |

|                    |                      | MUL.SU | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = signed(Wb) * unsigned(lit5)      | 1             | 1              | None                     |

|                    |                      | MUL.UU | Wb,#lit5,Wnd    | {Wnd + 1, Wnd} = unsigned(Wb) *<br>unsigned(lit5) | 1             | 1              | None                     |

|                    |                      | MUL    | f               | W3:W2 = f * WREG                                  | 1             | 1              | None                     |

| 42                 | NEG                  | NEG    | f               | $f = \overline{f} + 1$                            | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | f,WREG          | WREG = $\overline{f}$ + 1                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | NEG    | Ws,Wd           | $Wd = \overline{Ws} + 1$                          | 1             | 1              | C,DC,N,OV,Z              |

| 43                 | NOP                  | NOP    | -, -            | No Operation                                      | 1             | 1              | None                     |

|                    |                      | NOPR   |                 | No Operation                                      | 1             | 1              | None                     |

| 44                 | POP                  | POP    | f               | Pop f from Top-of-Stack (TOS)                     | 1             | 1              | None                     |

|                    |                      | POP    | Wdo             | Pop from Top-of-Stack (TOS) to Wdo                | 1             | 1              | None                     |

|                    |                      | POP.D  | Wnd             | Pop from Top-of-Stack (TOS) to                    | 1             | 2              | None                     |

|                    |                      | 101.5  | ma              | W(nd):W(nd + 1)                                   |               | -              | 10110                    |

|                    |                      | POP.S  |                 | Pop Shadow Registers                              | 1             | 1              | All                      |

| 45                 | PUSH                 | PUSH   | f               | Push f to Top-of-Stack (TOS)                      | 1             | 1              | None                     |

|                    |                      | PUSH   | Wso             | Push Wso to Top-of-Stack (TOS)                    | 1             | 1              | None                     |

|                    |                      | PUSH.D | Wns             | Push W(ns):W(ns + 1) to Top-of-Stack (TOS)        | 1             | 2              | None                     |

|                    |                      | PUSH.S |                 | Push Shadow Registers                             | 1             | 1              | None                     |

| 46                 | PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode                        | 1             | 1              | WDTO,Sleep               |

| 47                 | RCALL                | RCALL  | Expr            | Relative Call                                     | 1             | 2              | None                     |

|                    |                      | RCALL  | Wn              | Computed Call                                     | 1             | 2              | None                     |

| DC CHA   | RACTER                                                                                                                   | ISTICS                                                                                                       | Standar<br>(unless<br>Operatir                                                                                              | otherwi | se state | <b>ed)</b><br>-40°C ≤                        | <b>:: 3.0V to 3.6V</b><br>≤TA ≤+85°C for Industrial<br>≤TA ≤+125°C for Extended |

|----------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------|----------|----------------------------------------------|---------------------------------------------------------------------------------|

| Param.   | Symbol                                                                                                                   | Characteristic                                                                                               | Min.                                                                                                                        | Тур.    | Max.     | Units                                        | Conditions                                                                      |

|          |                                                                                                                          | Output Low Voltage<br>I/O Pins:<br>2x Sink Driver Pins - RA2, RA7-<br>RA10, RB10, RB11, RB7, RB4,<br>RC3-RC9 | _                                                                                                                           | _       | 0.4      | V                                            | Io∟ ≤3 mA, Vdd = 3.3V<br>See <b>Note 1</b>                                      |

| DO10 Vol | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - RA0, RA1,<br>RB0-RB3, RB5, RB6, RB8, RB9,<br>RB12-RB15, RC0-RC2 | _                                                                                                            | _                                                                                                                           | 0.4     | v        | IoL ⊴6 mA, VDD = 3.3V<br>See <b>Note 1</b>   |                                                                                 |

|          |                                                                                                                          | <b>Output Low Voltage</b><br>I/O Pins:<br>8x Sink Driver Pins - RA3, RA4                                     | _                                                                                                                           | _       | 0.4      | V                                            | Io∟ ≤10 mA, VDD = 3.3V<br>See <b>Note 1</b>                                     |

| DO20 Vон | Output High Voltage<br>I/O Pins:<br>2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,<br>RB11, RC3-RC9           | 2.4                                                                                                          | _                                                                                                                           | _       | v        | Іон ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b> |                                                                                 |

|          | Vон                                                                                                                      | Voh I<br>F                                                                                                   | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - RA0,<br>RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2 | 2.4     | _        | _                                            | V                                                                               |

|          |                                                                                                                          | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - RA4,<br>RA3                                      | 2.4                                                                                                                         | _       | _        | v                                            | IOH ≥ -10 mA, VDD = 3.3V<br>See <b>Note 1</b>                                   |

|          |                                                                                                                          | Output High Voltage<br>I/O Pins:                                                                             | 1.5                                                                                                                         | _       | _        |                                              | IOH ≥ -6 mA, VDD = 3.3V<br>See <b>Note 1</b>                                    |

|          |                                                                                                                          | 2x Source Driver Pins - RA2,<br>RA7-RA10, RB4, RB7, RB10,                                                    | 2.0                                                                                                                         | _       | _        | V                                            | IOH ≥ -5 mA, VDD <b>=</b> 3.3V<br>See <b>Note 1</b>                             |

|          |                                                                                                                          | RB11, RC3-RC9                                                                                                | 3.0                                                                                                                         | _       | —        |                                              | IOH ≥ -2 mA, VDD = 3.3V<br>See <b>Note 1</b>                                    |

|          |                                                                                                                          | <b>Output High Voltage</b><br>4x Source Driver Pins - RA0,                                                   | 1.5                                                                                                                         | -       | _        |                                              | Іон ≥ -12 mA, Voo = 3.3V<br>See <b>Note 1</b>                                   |

| DO20A    | Vон1                                                                                                                     | RA1, RB0-RB3, RB5, RB6, RB8,<br>RB9, RB12-RB15, RC0-RC2                                                      | 2.0                                                                                                                         | _       | _        | V                                            | IOH ≥ -11 mA, VDD = 3.3V<br>See <b>Note 1</b>                                   |

|          |                                                                                                                          |                                                                                                              | 3.0                                                                                                                         | _       |          |                                              | IOH ≥ -3 mA, VDD = 3.3V<br>See <b>Note 1</b>                                    |

|          |                                                                                                                          | Output High Voltage                                                                                          | 1.5                                                                                                                         | _       | _        |                                              | IOH ≥ -16 mA, VDD = 3.3V<br>See <b>Note 1</b>                                   |

|          |                                                                                                                          | 8x Source Driver Pins - RA3,<br>RA4                                                                          | 2.0                                                                                                                         | _       |          | V                                            | IOH ≥ -12 mA, VDD = 3.3V<br>See <b>Note 1</b>                                   |

|          |                                                                                                                          |                                                                                                              | 3.0                                                                                                                         | _       | _        |                                              | IOH ≥ -4 mA, VDD = 3.3V<br>See <b>Note 1</b>                                    |

### TABLE 28-10: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

**Note 1:** Parameters are characterized, but not tested.

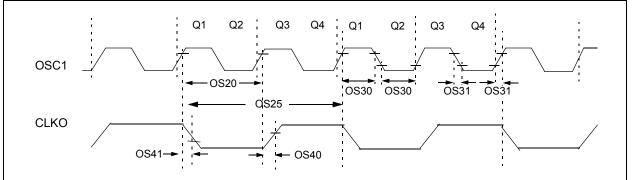

# FIGURE 28-2: EXTERNAL CLOCK TIMING