#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 833MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DDR, SDRAM                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | -                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8555pxapf |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters that can generate interrupts

- Supports additional internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs

- Interrupt summary registers allow fast identification of interrupt source

- Two I<sup>2</sup>C controllers (one is contained within the CPM, the other is a stand-alone controller which is not part of the CPM)

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the stand-alone I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (RXD, TXD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 166 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Two Three-speed (10/100/1000)Ethernet controllers (TSECs)

- Dual IEEE 802.3, 802.3u, 802.3x, 802.3z AC compliant controllers

- Support for Ethernet physical interfaces:

- 10/100/1000 Mbps IEEE 802.3 GMII

- 10/100 Mbps IEEE 802.3 MII

**Power Characteristics**

| Interface     | Parameters     | GV <sub>DD</sub><br>(2.5 V) | OV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | Unit | Comments                                                  |

|---------------|----------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|------|-----------------------------------------------------------|

| DDR I/O       | CCB = 200 MHz  | 0.46                        | _                           | _                           | _                           | W    | _                                                         |

|               | CCB = 266 MHz  | 0.59                        | _                           | _                           | —                           | W    | —                                                         |

|               | CCB = 300 MHz  | 0.66                        | _                           | _                           | —                           | W    | —                                                         |

|               | CCB = 333 MHz  | 0.73                        | _                           | _                           | —                           | W    | —                                                         |

| PCI I/O       | 64b, 66 MHz    | —                           | 0.14                        | _                           | —                           | W    | —                                                         |

|               | 64b, 33 MHz    | —                           | 0.08                        | _                           | —                           | W    | —                                                         |

|               | 32b, 66 MHz    | —                           | 0.07                        | _                           | —                           | W    | Multiply by 2 if using two 32b ports                      |

|               | 32b, 33 MHz    | —                           | 0.04                        | _                           | —                           | W    |                                                           |

| Local Bus I/O | 32b, 167 MHz   | —                           | 0.30                        | —                           | —                           | W    | —                                                         |

|               | 32b, 133 MHz   | —                           | 0.24                        | _                           | —                           | W    | —                                                         |

|               | 32b, 83 MHz    | —                           | 0.16                        | _                           | —                           | W    | —                                                         |

|               | 32b, 66 MHz    | —                           | 0.13                        | _                           | —                           | W    | —                                                         |

|               | 32b, 33 MHz    | —                           | 0.07                        | _                           | —                           | W    | —                                                         |

| TSEC I/O      | MII            | —                           | _                           | 0.01                        | —                           | W    | Multiply by number of interfaces                          |

|               | GMII or TBI    | —                           | _                           | 0.07                        | —                           | W    | used.                                                     |

|               | RGMII or RTBI  | —                           | _                           | _                           | 0.04                        | W    |                                                           |

| CPM - FCC     | MII            | —                           | 0.015                       | _                           | —                           | W    | —                                                         |

|               | RMII           | —                           | 0.013                       | _                           | —                           | W    | —                                                         |

|               | HDLC 16 Mbps   | —                           | 0.009                       | _                           | —                           | W    | —                                                         |

|               | UTOPIA-8 SPHY  | —                           | 0.06                        | _                           | —                           | W    | —                                                         |

|               | UTOPIA-8 MPHY  | —                           | 0.1                         | _                           | —                           | W    | _                                                         |

|               | UTOPIA-16 SPHY | —                           | 0.094                       | _                           | —                           | W    | —                                                         |

|               | UTOPIA-16 MPHY | —                           | 0.135                       | _                           | —                           | W    | —                                                         |

| CPM - SCC     | HDLC 16 Mbps   | _                           | 0.004                       | _                           | _                           | W    | _                                                         |

| TDMA or TDMB  | Nibble Mode    | —                           | 0.01                        | _                           | —                           | W    | -                                                         |

| TDMA or TDMB  | Per Channel    | -                           | 0.005                       | —                           | —                           | W    | Up to 4 TDM channels, multiply by number of TDM channels. |

## Table 5. Typical I/O Power Dissipation

**RESET** Initialization

# 4.3 Real Time Clock Timing

Table 8 provides the real time clock (RTC) AC timing specifications.

Table 8. RTC AC Timing Specifications

| Parameter/Condition | Symbol            | Min                         | Typical | Max | Unit | Notes |

|---------------------|-------------------|-----------------------------|---------|-----|------|-------|

| RTC clock high time | t <sub>RTCH</sub> | 2 х<br>t <sub>CCB_CLK</sub> | _       | _   | ns   |       |

| RTC clock low time  | t <sub>RTCL</sub> | 2 х<br>t <sub>CCB_CLK</sub> | —       | -   | ns   | —     |

# 5 **RESET Initialization**

This section describes the AC electrical specifications for the RESET initialization timing requirements of the MPC8555E. Table 9 provides the RESET initialization AC timing specifications.

### Table 9. RESET Initialization Timing Specifications

| Parameter/Condition                                                                                     | Min | Мах | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 | —   | μs      | _     |

| Minimum assertion time for SRESET                                                                       | 512 | —   | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 | _   | μs      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _   | SYSCLKs | 1     |

| Input hold time for POR configs (including PLL config) with respect to negation of HRESET               | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

Notes:

1. SYSCLK is identical to the PCI\_CLK signal and is the primary clock input for the MPC8555E. See the MPC8555E PowerQUICC<sup>™</sup> III Integrated Communications Processor Reference Manual for more details.

## Table 10 provides the PLL and DLL lock times.

### Table 10. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit       | Notes |

|---------------------|------|---------|------------|-------|

| PLL lock times      | —    | 100     | μs         | _     |

| DLL lock times      | 7680 | 122,880 | CCB Clocks | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the platform (or CCB) clock. A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The CCB clock is determined by the SYSCLK  $\times$  platform PLL ratio.

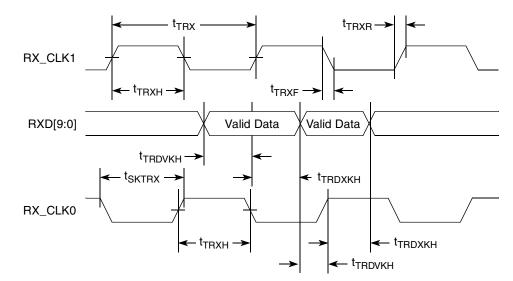

## 8.2.4.2 TBI Receive AC Timing Specifications

Table 25 provides the TBI receive AC timing specifications.

| Table 25. | . TBI Receive | <b>AC</b> Timing | Specifications |

|-----------|---------------|------------------|----------------|

|-----------|---------------|------------------|----------------|

At recommended operating conditions with  $LV_{DD}$  of 3.3 V ± 5%.

| Parameter/Condition                  | Symbol <sup>1</sup>                                  | Min | Тур  | Max | Unit |

|--------------------------------------|------------------------------------------------------|-----|------|-----|------|

| RX_CLK clock period                  | t <sub>TRX</sub>                                     |     | 16.0 |     | ns   |

| RX_CLK skew                          | t <sub>SKTRX</sub>                                   | 7.5 | _    | 8.5 | ns   |

| RX_CLK duty cycle                    | t <sub>TRXH</sub> /t <sub>TRX</sub>                  | 40  | —    | 60  | %    |

| RCG[9:0] setup time to rising RX_CLK | t <sub>TRDVKH</sub>                                  | 2.5 | —    | _   | ns   |

| RCG[9:0] hold time to rising RX_CLK  | t <sub>TRDXKH</sub>                                  | 1.5 | —    | _   | ns   |

| RX_CLK clock rise time and fall time | t <sub>TRXR</sub> , t <sub>TRXF</sub> <sup>2,3</sup> | 0.7 |      | 2.4 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of  $t_{(first two letters of functional block)(signal)(state)}$ (reference)(state) for inputs and  $t_{(first two letters of functional block)(reference)(state)(signal)(state)}$  for outputs. For example,  $t_{TRDVKH}$  symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the  $t_{TRX}$  clock reference (K) going to the high (H) state or setup time. Also,  $t_{TRDXKH}$  symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the  $t_{TRX}$  clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of  $t_{TRX}$  represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).

2. Guaranteed by design.

Figure 13 shows the TBI receive AC timing diagram.

Figure 13. TBI Receive AC Timing Diagram

Ethernet: Three-Speed, MII Management

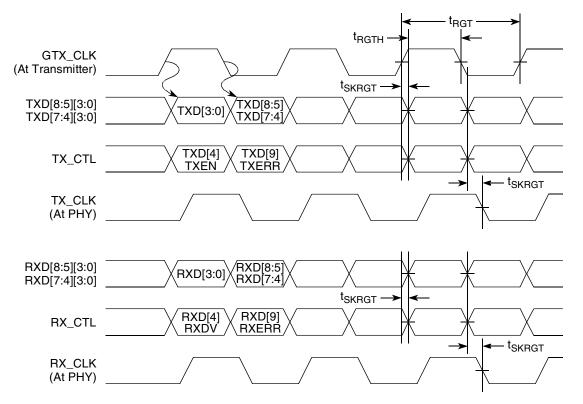

## 8.2.5 RGMII and RTBI AC Timing Specifications

Table 26 presents the RGMII and RTBI AC timing specifications.

### Table 26. RGMII and RTBI AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 2.5 V  $\pm$  5%.

| Parameter/Condition                                 | Symbol <sup>1</sup>                                                 | Min  | Тур | Мах  | Unit |

|-----------------------------------------------------|---------------------------------------------------------------------|------|-----|------|------|

| Data to clock output skew (at transmitter)          | tskrgt <sup>5</sup>                                                 | -500 | 0   | 500  | ps   |

| Data to clock input skew (at receiver) <sup>2</sup> | t <sub>SKRGT</sub>                                                  | 1.0  |     | 2.8  | ns   |

| Clock cycle duration <sup>3</sup>                   | t <sub>RGT</sub> 6                                                  | 7.2  | 8.0 | 8.8  | ns   |

| Duty cycle for 1000Base-T <sup>4</sup>              | t <sub>RGTH</sub> /t <sub>RGT</sub> 6                               | 45   | 50  | 55   | %    |

| Duty cycle for 10BASE-T and 100BASE-TX $^3$         | t <sub>RGTH</sub> /t <sub>RGT</sub> 6                               | 40   | 50  | 60   | %    |

| Rise and fall times                                 | t <sub>RGTR</sub> <sup>6,7</sup> , t <sub>RGTF</sub> <sup>6,7</sup> | —    | —   | 0.75 | ns   |

#### Notes:

1. Note that, in general, the clock reference symbol representation for this section is based on the symbols RGT to represent RGMII and RTBI timing. For example, the subscript of t<sub>RGT</sub> represents the TBI (T) receive (RX) clock. Note also that the notation for rise (R) and fall (F) times follows the clock symbol that is being represented. For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (RGT).

The RGMII specification requires that PC board designer add 1.5 ns or greater in trace delay to the RX\_CLK in order to meet this specification. However, as stated above, this device functions with only 1.0 ns of delay.

3. For 10 and 100 Mbps,  $t_{RGT}$  scales to 400 ns ± 40 ns and 40 ns ± 4 ns, respectively.

4. Duty cycle may be stretched/shrunk during speed changes or while transitioning to a received packet's clock domains as long as the minimum duty cycle is not violated and stretching occurs for no more than three t<sub>RGT</sub> of the lowest speed transitioned between.

5. Guaranteed by characterization.

6. Guaranteed by design.

7. Signal timings are measured at 0.5 and 2.0 V voltage levels.

Figure 14 shows the RBMII and RTBI AC timing and multiplexing diagrams.

Figure 14. RGMII and RTBI AC Timing and Multiplexing Diagrams

## 8.3 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, TBI and RTBI are specified in Section 8.1, "Three-Speed Ethernet Controller (TSEC) (10/100/1000 Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics."

## 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 27.

| Parameter              | Symbol           | Conditions                                 |                        | Min  | Мах                    | Unit |

|------------------------|------------------|--------------------------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | —                                          |                        | 3.13 | 3.47                   | V    |

| Output high voltage    | V <sub>OH</sub>  | $I_{OH} = -1.0 \text{ mA}$ $LV_{DD} = Min$ |                        | 2.10 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA                   | LV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | _                                          |                        | 1.70 | —                      | V    |

| Input low voltage      | V <sub>IL</sub>  | —<br>—                                     |                        | —    | 0.90                   | V    |

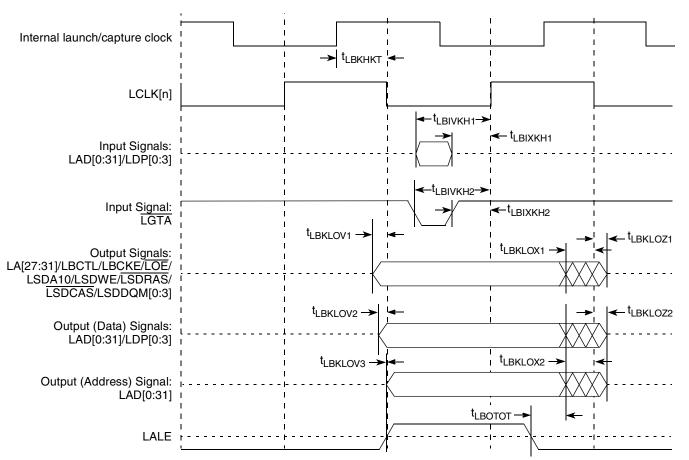

Local Bus

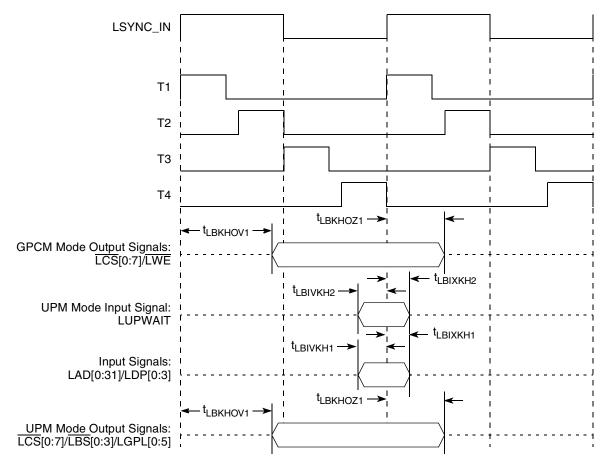

Figure 18. Local Bus Signals, Nonspecial Signals Only (DLL Bypass Mode)

Figure 21. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 4 or 8 (DLL Enabled)

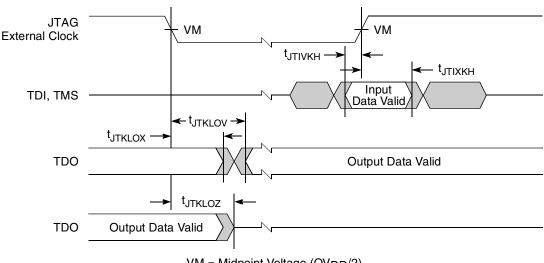

Figure 36 provides the test access port timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2) Figure 36. Test Access Port Timing Diagram

# 12 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the I<sup>2</sup>C interface of the MPC8555E.

# 12.1 I<sup>2</sup>C DC Electrical Characteristics

Table 39 provides the DC electrical characteristics for the  $I^2C$  interface of the MPC8555E.

## Table 39. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with  $\text{OV}_{\text{DD}}$  of 3.3 V  $\pm$  5%.

| Parameter                                                                                               | Symbol              | Min                   | Max                                | Unit | Notes |

|---------------------------------------------------------------------------------------------------------|---------------------|-----------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                | V <sub>IH</sub>     | $0.7 \times OV_{DD}$  | OV <sub>DD</sub> + 0.3             | V    |       |

| Input low voltage level                                                                                 | V <sub>IL</sub>     | -0.3                  | $0.3 \times \text{OV}_{\text{DD}}$ | V    |       |

| Low level output voltage                                                                                | V <sub>OL</sub>     | 0                     | $0.2 \times \text{OV}_{\text{DD}}$ | V    | 1     |

| Output fall time from $V_{IH}$ (min) to $V_{IL}$ (max) with a bus capacitance from 10 to 400 pF         | <sup>t</sup> I2KLKV | $20 + 0.1 \times C_B$ | 250                                | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                                      | t <sub>I2KHKL</sub> | 0                     | 50                                 | ns   | 3     |

| Input current each I/O pin (input voltage is between 0.1 $\times$ OV_{DD} and 0.9 $\times$ OV_{DD}(max) | I                   | -10                   | 10                                 | μA   | 4     |

| Capacitance for each I/O pin                                                                            | Cl                  | —                     | 10                                 | pF   |       |

Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2.  $C_B$  = capacitance of one bus line in pF.

3. Refer to the MPC8555E PowerQUICC<sup>™</sup> III Integrated Communications Processor Reference Manual for information on the digital filter used.

4. I/O pins obstruct the SDA and SCL lines if  $\mathrm{OV}_\mathrm{DD}$  is switched off.

Package and Pin Listings

## Table 43. MPC8555E Pinout Listing (continued)

| Signal         | Package Pin Number               | Pin Type | Power<br>Supply  | Notes    |

|----------------|----------------------------------|----------|------------------|----------|

| TSEC2_CRS      | D9                               | I        | LV <sub>DD</sub> | —        |

| TSEC2_COL      | F8                               | I        | LV <sub>DD</sub> | —        |

| TSEC2_RXD[7:0] | F9, E9, C9, B9, A9, H9, G10, F10 | I        | LV <sub>DD</sub> | —        |

| TSEC2_RX_DV    | H8                               | I        | LV <sub>DD</sub> | —        |

| TSEC2_RX_ER    | A8                               | I        | LV <sub>DD</sub> | —        |

| TSEC2_RX_CLK   | E10                              | I        | LV <sub>DD</sub> | —        |

|                | DUART                            |          |                  |          |

| UART_CTS[0,1]  | Y2, Y3                           | I        | OV <sub>DD</sub> | _        |

| UART_RTS[0,1]  | Y1, AD1                          | 0        | OV <sub>DD</sub> |          |

| UART_SIN[0,1]  | P11, AD5                         | I        | OV <sub>DD</sub> | —        |

| UART_SOUT[0,1] | N6, AD2                          | 0        | OV <sub>DD</sub> |          |

|                | I <sup>2</sup> C interface       |          |                  |          |

| IIC_SDA        | AH22                             | I/O      | OV <sub>DD</sub> | 4, 19    |

| IIC_SCL        | AH23                             | I/O      | OV <sub>DD</sub> | 4, 19    |

|                | System Control                   |          |                  |          |

| HRESET         | AH16                             | I        | OV <sub>DD</sub> | _        |

| HRESET_REQ     | AG20                             | 0        | OV <sub>DD</sub> | 18       |

| SRESET         | AF20                             | I        | OV <sub>DD</sub> | —        |

| CKSTP_IN       | M11                              | I        | OV <sub>DD</sub> | —        |

| CKSTP_OUT      | G1                               | 0        | OV <sub>DD</sub> | 2, 4     |

|                | Debug                            | ·        |                  |          |

| TRIG_IN        | N12                              | I        | OV <sub>DD</sub> | _        |

| TRIG_OUT/READY | G2                               | 0        | OV <sub>DD</sub> | 6, 9, 18 |

| MSRCID[0:1]    | J9, G3                           | 0        | OV <sub>DD</sub> | 5, 6, 9  |

| MSRCID[2:3]    | F3, F5                           | 0        | OV <sub>DD</sub> | 6        |

| MSRCID4        | F2                               | 0        | OV <sub>DD</sub> | 6        |

| MDVAL          | F4                               | 0        | OV <sub>DD</sub> | 6        |

|                | Clock                            | I        |                  |          |

| SYSCLK         | AH21                             | I        | OV <sub>DD</sub> | _        |

| RTC            | AB23                             | I        | OV <sub>DD</sub> | —        |

| CLK_OUT        | AF22                             | 0        | OV <sub>DD</sub> | —        |

Package and Pin Listings

| Table 43. | MPC8555E | Pinout | Listing | (continued) |

|-----------|----------|--------|---------|-------------|

|-----------|----------|--------|---------|-------------|

| Signal             | Package Pin Number       | Pin Type                      | Power<br>Supply    | Notes |

|--------------------|--------------------------|-------------------------------|--------------------|-------|

|                    | JTAG                     |                               |                    | 1     |

| ТСК                | AF21                     | I                             | OV <sub>DD</sub>   | _     |

| TDI                | AG21                     | I                             | OV <sub>DD</sub>   | 12    |

| TDO                | AF19                     | 0                             | OV <sub>DD</sub>   | 11    |

| TMS                | AF23                     | I                             | OV <sub>DD</sub>   | 12    |

| TRST               | AG23                     | I                             | OV <sub>DD</sub>   | 12    |

|                    | DFT                      |                               |                    |       |

| LSSD_MODE          | AG19                     | I                             | OV <sub>DD</sub>   | 20    |

| L1_TSTCLK          | AB22                     | I                             | OV <sub>DD</sub>   | 20    |

| L2_TSTCLK          | AG22                     | I                             | $OV_{DD}$          | 20    |

| TEST_SEL0          | AH20                     | I                             | $OV_{DD}$          | 3     |

| TEST_SEL1          | AG26                     | I                             | $OV_{DD}$          | 3     |

|                    | Thermal Management       |                               |                    |       |

| THERM0             | AG2                      | —                             | _                  | 14    |

| THERM1             | AH3                      | —                             | _                  | 14    |

|                    | Power Management         |                               |                    |       |

| ASLEEP             | AG18                     | —                             | _                  | 9, 18 |

|                    | Power and Ground Signals |                               |                    |       |

| AV <sub>DD</sub> 1 | AH19                     | Power for e500<br>PLL (1.2 V) | AV <sub>DD</sub> 1 | _     |

| AV <sub>DD</sub> 2 | AH18                     | Power for CCB<br>PLL (1.2 V)  | AV <sub>DD</sub> 2 | -     |

| AV <sub>DD</sub> 3 | AH17                     | Power for CPM<br>PLL (1.2 V)  | AV <sub>DD</sub> 3 | -     |

| AV <sub>DD</sub> 4 | AF28                     | Power for PCI1<br>PLL (1.2 V) | $AV_{DD}4$         | -     |

| AV <sub>DD</sub> 5 | AE28                     | Power for PCI2<br>PLL (1.2 V) | $AV_{DD}5$         | —     |

# 15 Clocking

This section describes the PLL configuration of the MPC8555E. Note that the platform clock is identical to the CCB clock.

# 15.1 Clock Ranges

Table 44 provides the clocking specifications for the processor core and Table 44 provides the clocking specifications for the memory bus.

|                                     |     | Maximum Processor Core Frequency |     |     |     |     |     |     |      |       |      |         |

|-------------------------------------|-----|----------------------------------|-----|-----|-----|-----|-----|-----|------|-------|------|---------|

| Characteristic                      | 533 | MHz                              | 600 | MHz | 667 | MHz | 833 | MHz | 1000 | ) MHz | Unit | Notes   |

|                                     | Min | Max                              | Min | Max | Min | Max | Min | Max | Min  | Max   |      |         |

| e500 core<br>processor<br>frequency | 400 | 533                              | 400 | 600 | 400 | 667 | 400 | 833 | 400  | 1000  | MHz  | 1, 2, 3 |

**Table 44. Processor Core Clocking Specifications**

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

2.) The minimum e500 core frequency is based on the minimum platform frequency of 200 MHz.

3. 1000 MHz frequency supports only a 1.3 V core.

## Table 45. Memory Bus Clocking Specifications

| Characteristic       | Maximum Pro<br>Frequ<br>533, 600, 667, | Unit | Notes |         |

|----------------------|----------------------------------------|------|-------|---------|

|                      | Min                                    | Max  |       |         |

| Memory bus frequency | 100                                    | 166  | MHz   | 1, 2, 3 |

Notes:

- 1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR data rate, hence, half of the platform clock frequency.

- 3. 1000 MHz frequency supports only a 1.3 V core.

## 15.2 Platform/System PLL Ratio

The platform clock is the clock that drives the L2 cache, the DDR SDRAM data rate, and the e500 core complex bus (CCB), and is also called the CCB clock. The values are determined by the binary value on LA[28:31] at power up, as shown in Table 46.

There is no default for this PLL ratio; these signals must be pulled to the desired values.

For specifications on the PCI\_CLK, refer to the PCI 2.2 Specification.

| Binary Value of<br>LA[28:31] Signals | Ratio Description                      |

|--------------------------------------|----------------------------------------|

| 0000                                 | 16:1 ratio CCB clock: SYSCLK (PCI bus) |

| 0001                                 | Reserved                               |

| 0010                                 | 2:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0011                                 | 3:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0100                                 | 4:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0101                                 | 5:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0110                                 | 6:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 0111                                 | Reserved                               |

| 1000                                 | 8:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 1001                                 | 9:1 ratio CCB clock: SYSCLK (PCI bus)  |

| 1010                                 | 10:1 ratio CCB clock: SYSCLK (PCI bus) |

| 1011                                 | Reserved                               |

| 1100                                 | 12:1 ratio CCB clock: SYSCLK (PCI bus) |

| 1101                                 | Reserved                               |

| 1110                                 | Reserved                               |

| 1111                                 | Reserved                               |

| Table | 46. | CCB | Clock | Ratio  |

|-------|-----|-----|-------|--------|

| Tuble | -0. | 000 | 01000 | ilulio |

FC-PBGA Package Heat Sink Clip Thermal Interface Material

Printed-Circuit Board

### Figure 43. Package Exploded Cross-Sectional View with Several Heat Sink Options

The system board designer can choose between several types of heat sinks to place on the MPC8555E. There are several commercially-available heat sinks from the following vendors:

| Aavid Thermalloy<br>80 Commercial St.<br>Concord, NH 03301<br>Internet: www.aavidthermalloy.com                                | 603-224-9988 |

|--------------------------------------------------------------------------------------------------------------------------------|--------------|

| Alpha Novatech<br>473 Sapena Ct. #15<br>Santa Clara, CA 95054<br>Internet: www.alphanovatech.com                               | 408-749-7601 |

| International Electronic Research Corporation (IERC)<br>413 North Moss St.<br>Burbank, CA 91502<br>Internet: www.ctscorp.com   | 818-842-7277 |

| Millennium Electronics (MEI)<br>Loroco Sites<br>671 East Brokaw Road<br>San Jose, CA 95112<br>Internet: www.mei-millennium.com | 408-436-8770 |

| Tyco Electronics<br>Chip Coolers™<br>P.O. Box 3668<br>Harrisburg, PA 17105-3668<br>Internet: www.chipcoolers.com               | 800-522-6752 |

| Wakefield Engineering<br>33 Bridge St.<br>Pelham, NH 03076<br>Internet: www.wakefield.com                                      | 603-635-5102 |

Ultimately, the final selection of an appropriate heat sink depends on many factors, such as thermal performance at a given air velocity, spatial volume, mass, attachment method, assembly, and cost. Several heat sinks offered by Aavid Thermalloy, Alpha Novatech, IERC, Chip Coolers, Millennium Electronics, and Wakefield Engineering offer different heat sink-to-ambient thermal resistances, that allows the MPC8555E to function in various environments.

## 16.2.1 Recommended Thermal Model

For system thermal modeling, the MPC8555E thermal model is shown in Figure 44. Five cuboids are used to represent this device. To simplify the model, the solder balls and substrate are modeled as a single block 29x29x1.6 mm with the conductivity adjusted accordingly. The die is modeled as 8.7 x 9.3 mm at a thickness of 0.75 mm. The bump/underfill layer is modeled as a collapsed resistance between the die and substrate assuming a conductivity of 4.4 W/m•K in the thickness dimension of 0.07 mm. The lid attach adhesive is also modeled as a collapsed resistance with dimensions of 8.7 x 9.3 x 0.05 mm and the conductivity of 1.07 W/m•K. The nickel plated copper lid is modeled as 11 x 11 x 1 mm.

| Conductivity                      | Value                                                                       | Unit             |                                                                 |

|-----------------------------------|-----------------------------------------------------------------------------|------------------|-----------------------------------------------------------------|

| Li<br>(11 × 11                    |                                                                             |                  |                                                                 |

| k <sub>x</sub>                    | 360                                                                         | W/(m $\times$ K) | Lid Adhesive                                                    |

| k <sub>y</sub>                    | 360                                                                         |                  | z Die Bump/underfill                                            |

| k <sub>z</sub>                    | 360                                                                         |                  |                                                                 |

|                                   | Lid Adhesive—Collapsed resistance $(8.7 \times 9.3 \times 0.05 \text{ mm})$ |                  | Substrate and solder balls<br>Side View of Model (Not to Scale) |

| k <sub>z</sub>                    | 1.07                                                                        | -                |                                                                 |

|                                   | Die<br>(8.7 × 9.3 × 0.75 mm)                                                |                  | <b>X</b>                                                        |

| Bump/Underfill—Co<br>(8.7 × 9.3 × |                                                                             |                  |                                                                 |

| k <sub>z</sub>                    | 4.4                                                                         |                  | Substrate                                                       |

|                                   | Substrate and Solder Balls ( $25 \times 25 \times 1.6$ mm)                  |                  | Heat Source                                                     |

| k <sub>x</sub>                    | 14.2                                                                        |                  | ▲                                                               |

| k <sub>y</sub>                    | 14.2                                                                        |                  |                                                                 |

| k <sub>z</sub>                    | 1.2                                                                         |                  |                                                                 |

|                                   |                                                                             |                  | У                                                               |

Top View of Model (Not to Scale)

Figure 44. MPC8555E Thermal Model

the heat sink should be slowly removed. Heating the heat sink to 40–50°C with an air gun can soften the interface material and make the removal easier. The use of an adhesive for heat sink attach is not recommended.

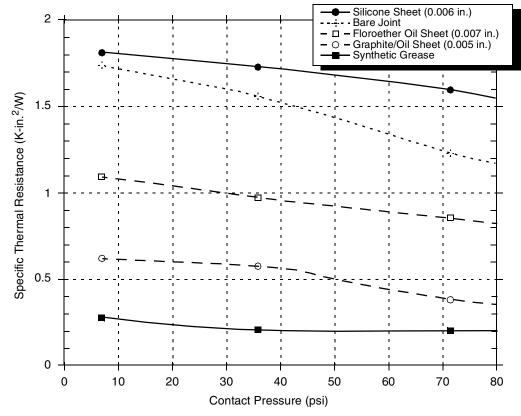

Figure 46. Thermal Performance of Select Thermal Interface Materials

The system board designer can choose between several types of thermal interface. There are several commercially-available thermal interfaces provided by the following vendors:

| Chomerics, Inc.<br>77 Dragon Ct.<br>Woburn, MA 01888-4014<br>Internet: www.chomerics.com                                                      | 781-935-4850 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Dow-Corning Corporation<br>Dow-Corning Electronic Materials<br>2200 W. Salzburg Rd.<br>Midland, MI 48686-0997<br>Internet: www.dowcorning.com | 800-248-2481 |

| Shin-Etsu MicroSi, Inc.<br>10028 S. 51st St.<br>Phoenix, AZ 85044<br>Internet: www.microsi.com                                                | 888-642-7674 |

| The Bergquist Company<br>18930 West 78 <sup>th</sup> St.                                                                                      | 800-347-4572 |

System Design Information

# 17 System Design Information

This section provides electrical and thermal design recommendations for successful application of the MPC8555E.

# 17.1 System Clocking

The MPC8555E includes five PLLs.

- 1. The platform PLL (AV<sub>DD</sub>1) generates the platform clock from the externally supplied SYSCLK input. The frequency ratio between the platform and SYSCLK is selected using the platform PLL ratio configuration bits as described in Section 15.2, "Platform/System PLL Ratio."

- 2. The e500 Core PLL (AV<sub>DD</sub>2) generates the core clock as a slave to the platform clock. The frequency ratio between the e500 core clock and the platform clock is selected using the e500 PLL ratio configuration bits as described in Section 15.3, "e500 Core PLL Ratio."

- 3. The CPM PLL ( $AV_{DD}$ 3) is slaved to the platform clock and is used to generate clocks used internally by the CPM block. The ratio between the CPM PLL and the platform clock is fixed and not under user control.

- 4. The PCI1 PLL ( $AV_{DD}4$ ) generates the clocking for the first PCI bus.

- 5. The PCI2 PLL (AV<sub>DD</sub>5) generates the clock for the second PCI bus.

# 17.2 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins (AV<sub>DD</sub>1, AV<sub>DD</sub>2, AV<sub>DD</sub>3, AV<sub>DD</sub>4, and AV<sub>DD</sub>5 respectively). The AV<sub>DD</sub> level should always be equivalent to V<sub>DD</sub>, and preferably these voltages are derived directly from V<sub>DD</sub> through a low frequency filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide five independent filter circuits as illustrated in Figure 50, one to each of the five  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum Effective Series Inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of the 783 FC-PBGA footprint, without the inductance of vias.

# NP

#### System Design Information

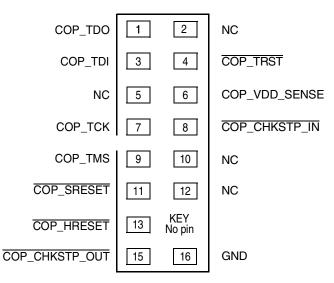

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 52 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 52, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 52 is common to all known emulators.

Figure 52. COP Connector Physical Pinout

# **18 Document Revision History**

Table 51 provides a revision history for this hardware specification.

| Table 51 | . Document | Revision | History |

|----------|------------|----------|---------|

|----------|------------|----------|---------|

| Rev. No. | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.2      | 1/2008  | Added "Note: Rise/Fall Time on CPM Input Pins" and following note text to Section 10.2, "CPM AC Timing Specifications."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 4.1      | 7/2007  | Inserted Figure 3, ""Maximum AC Waveforms on PCI interface for 3.3-V Signaling."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4        | 12/2006 | Updated Section 2.1.2, "Power Sequencing."<br>Updated back page information.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2      | 11/2006 | Updated Section 2.1.2, "Power Sequencing."<br>Replaced Section 17.8, "JTAG Configuration Signals."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1      | 10/2005 | Added footnote 2 about junction temperature in Table 4.         Added max. power values for 1000 MHz core frequency in Table 4.         Removed Figure 3, "Maximum AC Waveforms on PCI Interface for 3.3-V Signaling."         Modified note to t <sub>LBKSKEW</sub> from 8 to 9 in Table 30.         Changed t <sub>LBKHOZ1</sub> and t <sub>LBKHOV2</sub> values inTable 30.         Added note 3 to t <sub>LBKHOV1</sub> in Table 30.         Modified note 3 in Table 30 and Table 31.         Added note 3 to t <sub>LBKLOV1</sub> in Table 31.         Modified values for t <sub>LBKHKT</sub> , t <sub>LBKLOV1</sub> , t <sub>LBKLOV2</sub> , t <sub>LBKLOV3</sub> , t <sub>LBKLOZ1</sub> , and t <sub>LBKLOZ2</sub> in Table 31.         Changed Input Signals: LAD[0:31]/LDP[0:3] in Figure 21.         Modified note for signal CLK_OUT in Table 43.         PCI1_CLK and PCI2_CLK changed from I/O to I in Table 43.         Added column for Encryption Acceleration in Table 52. |

| 3        | 8/2005  | Modified max. power values in Table 4.<br>Modified notes for signals TSEC1_TXD[3:0], TSEC2_TXD[3:0], TRIG_OUT/READY, MSRCID4,<br>CLK_OUT, and MDVAL in Table 43.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2        | 8/2005  | Previous revision's history listed incorrect cross references. Table 2 is now correctly listed as<br>Table 27 and Table 38 is now listed as Table 31.<br>Added note 2 in Table 7.<br>Modified min and max values for t <sub>DDKHMP</sub> in Table 14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1        | 6/2005  | Changed $LV_{dd}$ to $OV_{dd}$ for the supply voltage Ethernet management interface in Table 27.<br>Modified footnote 4 and changed typical power for the 1000 MHz core frequency inTable 4.<br>Corrected symbols for body rows 9–15, effectively changing them from a high state to a low state in Table 31.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0        | 6/2005  | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 19.2 Part Marking

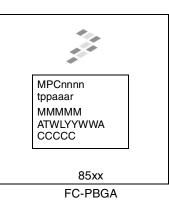

Parts are marked as the example shown in Figure 54.

#### Notes:

MMMMM is the 5-digit mask number. ATWLYYWWA is the traceability code. CCCCC is the country of assembly. This space is left blank if parts are assembled in the United States.

Figure 54. Part Marking for FC-PBGA Device