# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | PowerPC e500                                                          |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 833MHz                                                                |

| Co-Processors/DSP               | Communications; CPM                                                   |

| RAM Controllers                 | DDR, SDRAM                                                            |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | 10/100/1000Mbps (2)                                                   |

| SATA                            | ·                                                                     |

| USB                             | USB 2.0 (1)                                                           |

| Voltage - I/O                   | 2.5V, 3.3V                                                            |

| Operating Temperature           | 0°C ~ 105°C (TA)                                                      |

| Security Features               | ·                                                                     |

| Package / Case                  | 783-BBGA, FCBGA                                                       |

| Supplier Device Package         | 783-FCPBGA (29x29)                                                    |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/kmpc8555vtapf |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

— Two full-duplex fast communications controllers (FCCs) that support the following protocols:

- ATM protocol through two UTOPIA level 2 interfaces

- IEEE Std 802.3<sup>TM</sup>/Fast Ethernet (10/100)

- HDLC

- Totally transparent operation

- Three full-duplex serial communications controllers (SCCs) support the following protocols:

- High level/synchronous data link control (HDLC/SDLC)

- LocalTalk (HDLC-based local area network protocol)

- Universal asynchronous receiver transmitter (UART)

- Synchronous UART (1x clock mode)

- Binary synchronous communication (BISYNC)

- Totally transparent operation

- QMC support, providing 64 channels per SCC using only one physical TDM interface

- Universal serial bus (USB) controller that is full/low-speed compliant (multiplexed on an SCC)

- USB host mode

- Supports USB slave mode

- Serial peripheral interface (SPI) support for master or slave

- $I^2 C$  bus controller

- Two serial management controllers (SMCs) supporting:

- UART

- Transparent

- General-circuit interfaces (GCI)

- Time-slot assigner supports multiplexing of data from any of the SCCs and FCCs onto eight time-division multiplexed (TDM) interfaces. The time-slot assigner supports the following TDM formats:

- T1/CEPT lines

- T3/E3

- Pulse code modulation (PCM) highway interface

- ISDN primary rate

- Freescale interchip digital link (IDL)

- General circuit interface (GCI)

- User-defined interfaces

- Eight independent baud rate generators (BRGs)

- Four general-purpose 16-bit timers or two 32-bit timers

- General-purpose parallel ports—16 parallel I/O lines with interrupt capability

- 256 Kbytes of on-chip memory

- Can act as a 256-Kbyte level-2 cache

- Can act as a 256-Kbyte or two 128-Kbyte memory-mapped SRAM arrays

#### **Electrical Characteristics**

Items on the same line have no ordering requirement with respect to one another. Items on separate lines must be ordered sequentially such that voltage rails on a previous step must reach 90 percent of their value before the voltage rails on the current step reach ten percent of theirs.

#### NOTE

If the items on line 2 must precede items on line 1, please ensure that the delay does not exceed 500 ms and the power sequence is not done greater than once per day in production environment.

#### NOTE

From a system standpoint, if the I/O power supplies ramp prior to the  $V_{DD}$  core supply, the I/Os on the MPC8555E may drive a logic one or zero during power-up.

### 2.1.3 Recommended Operating Conditions

Table 2 provides the recommended operating conditions for the MPC8555E. Note that the values in Table 2 are the recommended and tested operating conditions. Proper device operation outside of these conditions is not guaranteed.

| Characteristic Core supply voltage                             |                                                                                                                 | Symbol            | Recommended Value                                                  | Unit |

|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------|------|

|                                                                |                                                                                                                 | $V_{DD}$          | $1.2 \text{ V} \pm 60 \text{ mV}$<br>1.3 V± 50 mV (for 1 GHz only) | V    |

| PLL supply voltage                                             |                                                                                                                 | AV <sub>DD</sub>  | 1.2 V ± 60 mV<br>1.3 V ± 50 mV (for 1 GHz only)                    | V    |

| DDR DRAM I/O voltage                                           | 9                                                                                                               | GV <sub>DD</sub>  | 2.5 V ± 125 mV                                                     | V    |

| Three-speed Ethernet I/O voltage                               |                                                                                                                 | LV <sub>DD</sub>  | 3.3 V ± 165 mV<br>2.5 V ± 125 mV                                   | V    |

| PCI, local bus, DUART,<br>I <sup>2</sup> C, and JTAG I/O volta | system control and power management,<br>ge                                                                      | $OV_{DD}$         | 3.3 V ± 165 mV                                                     | V    |

| Input voltage                                                  | DDR DRAM signals                                                                                                | MV <sub>IN</sub>  | GND to GV <sub>DD</sub>                                            | V    |

|                                                                | DDR DRAM reference                                                                                              | MV <sub>REF</sub> | GND to GV <sub>DD</sub>                                            | V    |

|                                                                | Three-speed Ethernet signals                                                                                    | LV <sub>IN</sub>  | GND to LV <sub>DD</sub>                                            | V    |

|                                                                | PCI, local bus, DUART,<br>SYSCLK, system control and<br>power management, I <sup>2</sup> C, and<br>JTAG signals | OV <sub>IN</sub>  | GND to OV <sub>DD</sub>                                            | V    |

| Die-junction Temperatu                                         | re                                                                                                              | Тj                | 0 to 105                                                           | °C   |

#### **Table 2. Recommended Operating Conditions**

**RESET** Initialization

## 4.3 Real Time Clock Timing

Table 8 provides the real time clock (RTC) AC timing specifications.

Table 8. RTC AC Timing Specifications

| Parameter/Condition | Symbol            | Min                         | Typical | Max | Unit | Notes |

|---------------------|-------------------|-----------------------------|---------|-----|------|-------|

| RTC clock high time | t <sub>RTCH</sub> | 2 х<br>t <sub>CCB_CLK</sub> | _       | _   | ns   | _     |

| RTC clock low time  | t <sub>RTCL</sub> | 2 х<br>t <sub>CCB_CLK</sub> | —       | -   | ns   | —     |

## 5 **RESET Initialization**

This section describes the AC electrical specifications for the RESET initialization timing requirements of the MPC8555E. Table 9 provides the RESET initialization AC timing specifications.

#### Table 9. RESET Initialization Timing Specifications

| Parameter/Condition                                                                                     | Min | Мах | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 | —   | μs      | _     |

| Minimum assertion time for SRESET                                                                       | 512 | —   | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 | _   | μs      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _   | SYSCLKs | 1     |

| Input hold time for POR configs (including PLL config) with respect to negation of HRESET               | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

Notes:

1. SYSCLK is identical to the PCI\_CLK signal and is the primary clock input for the MPC8555E. See the MPC8555E PowerQUICC<sup>™</sup> III Integrated Communications Processor Reference Manual for more details.

#### Table 10 provides the PLL and DLL lock times.

#### Table 10. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit       | Notes |

|---------------------|------|---------|------------|-------|

| PLL lock times      | —    | 100     | μs         | _     |

| DLL lock times      | 7680 | 122,880 | CCB Clocks | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the platform (or CCB) clock. A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The CCB clock is determined by the SYSCLK  $\times$  platform PLL ratio.

#### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                                | Мах                       | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------|---------------------------|------|-------|

| MCS(n) output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz            | t <sub>DDKHCX</sub>                         | 2.0<br>2.65<br>3.8                 | _                         | ns   | 4     |

| MCK to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                                       | t <sub>DDKHMH</sub>                         | -0.9<br>-1.1<br>-1.2               | 0.3<br>0.5<br>0.6         | ns   | 5     |

| MDQ/MECC/MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 900<br>900<br>1200                 | _                         | ps   | 6     |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 900<br>900<br>1200                 | _                         | ps   | 6     |

| MDQS preamble start                                                                | t <sub>DDKHMP</sub>                         | $-0.5 \times t_{\text{MCK}} - 0.9$ | $-0.5 	imes t_{MCK}$ +0.3 | ns   | 7     |

| MDQS epilogue end                                                                  | t <sub>DDKLME</sub>                         | -0.9                               | 0.3                       | ns   | 7     |

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the Clock Control Register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the Clock Control register is set to adjust the memory clocks by 1/2 applied cycle. The MCSx pins are separated from the ADDR/CMD (address and command) bus in the HW spec. This was separated because the MCSx pins typically have different loadings than the rest of the address and command bus, even though they have the same timings.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). In the source synchronous mode, MDQS can launch later than MCK by 0.3 ns at the maximum. However, MCK may launch later than MDQS by as much as 0.9 ns. t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this typically is set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the *MPC8555E PowerQUICC™ III Integrated Communications Processor Reference Manual* for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8555E.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8555E. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

Ethernet: Three-Speed, MII Management

## 7.2 DUART AC Electrical Specifications

Table 17 provides the AC timing parameters for the DUART interface of the MPC8555E.

| Parameter         | Value                          | Unit | Notes |

|-------------------|--------------------------------|------|-------|

| Minimum baud rate | f <sub>CCB_CLK</sub> / 1048576 | baud | 3     |

| Maximum baud rate | f <sub>CCB_CLK</sub> / 16      | baud | 1, 3  |

| Oversample rate   | 16                             | —    | 2, 3  |

#### Table 17. DUART AC Timing Specifications

#### Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

- The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

- 3. Guaranteed by design.

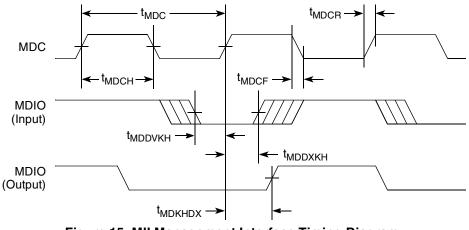

## 8 Ethernet: Three-Speed, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

## 8.1 Three-Speed Ethernet Controller (TSEC) (10/100/1000 Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all GMII (gigabit media independent interface), the MII (media independent interface), TBI (ten-bit interface), RGMII (reduced gigabit media independent interface), and RTBI (reduced ten-bit interface) signals except MDIO (management data input/output) and MDC (management data clock). The RGMII and RTBI interfaces are defined for 2.5 V, while the GMII and TBI interfaces can be operated at 3.3 V or 2.5 V. Whether the GMII, MII, or TBI interface is operated at 3.3 or 2.5 V, the timing is compliant with the IEEE 802.3 standard. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for Gigabit Ethernet Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 TSEC DC Electrical Characteristics

All GMII, MII, TBI, RGMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 18 and Table 19. The potential applied to the input of a GMII, MII, TBI, RGMII, or RTBI receiver may exceed the potential of the receiver's power supply (for example, a GMII driver powered from a 3.6-V supply driving  $V_{OH}$  into a GMII receiver powered from a 2.5-V supply). Tolerance for dissimilar GMII driver and receiver supply potentials is implicit in these specifications. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter            | Symbol           | Conditions                |                        | Min  | Max                    | Unit |

|----------------------|------------------|---------------------------|------------------------|------|------------------------|------|

| Supply voltage 3.3 V | LV <sub>DD</sub> | _                         |                        | 3.13 | 3.47                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -4.0 mA | LV <sub>DD</sub> = Min | 2.40 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 4.0 mA  | LV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage   | V <sub>IH</sub>  | _                         | —                      | 1.70 | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | _                         | —                      | -0.3 | 0.90                   | V    |

| Input high current   | I <sub>IH</sub>  | $V_{IN}^{1} = LV_{DD}$    |                        | _    | 40                     | μA   |

| Input low current    | IIL              | $V_{IN}^{1} = 0$          | GND                    | -600 | —                      | μA   |

#### Table 18. GMII, MII, and TBI DC Electrical Characteristics

#### Note:

1. The symbol  $V_{\text{IN}}$  in this case, represents the  $\text{LV}_{\text{IN}}$  symbol referenced in Table 1 and Table 2.

#### Table 19. GMII, MII, RGMII RTBI, and TBI DC Electrical Characteristics

| Parameters                                                            | Symbol           | Min       | Мах                    | Unit |

|-----------------------------------------------------------------------|------------------|-----------|------------------------|------|

| Supply voltage 2.5 V                                                  | LV <sub>DD</sub> | 2.37      | 2.63                   | V    |

| Output high voltage (LV <sub>DD</sub> = Min, $I_{OH} = -1.0$ mA)      | V <sub>OH</sub>  | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage (LV <sub>DD</sub> = Min, I <sub>OL</sub> = 1.0 mA) | V <sub>OL</sub>  | GND – 0.3 | 0.40                   | V    |

| Input high voltage (LV <sub>DD</sub> = Min)                           | V <sub>IH</sub>  | 1.70      | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage (LV <sub>DD</sub> = Min)                            | V <sub>IL</sub>  | -0.3      | 0.70                   | V    |

| Input high current (V <sub>IN</sub> <sup>1</sup> = LV <sub>DD</sub> ) | Ι <sub>ΙΗ</sub>  | —         | 10                     | μA   |

| Input low current (V <sub>IN</sub> <sup>1</sup> = GND)                | ۱ <sub>IL</sub>  | –15       |                        | μA   |

#### Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbol referenced in Table 1 and Table 2.

Ethernet: Three-Speed, MII Management

## 8.2 GMII, MII, TBI, RGMII, and RTBI AC Timing Specifications

The AC timing specifications for GMII, MII, TBI, RGMII, and RTBI are presented in this section.

### 8.2.1 GMII AC Timing Specifications

This section describes the GMII transmit and receive AC timing specifications.

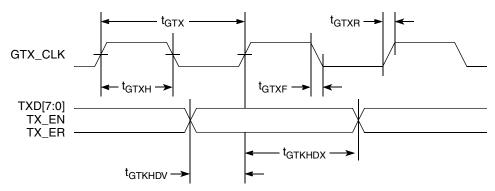

### 8.2.2 GMII Transmit AC Timing Specifications

Table 20 provides the GMII transmit AC timing specifications.

#### Table 20. GMII Transmit AC Timing Specifications

At recommended operating conditions with LV<sub>DD</sub> of 3.3 V  $\pm$  5%.

| Parameter/Condition                               | Symbol <sup>1</sup>                                               | Min | Тур | Мах | Unit |

|---------------------------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| GTX_CLK clock period                              | t <sub>GTX</sub>                                                  | _   | 8.0 | —   | ns   |

| GTX_CLK duty cycle                                | t <sub>GTXH</sub> /t <sub>GTX</sub>                               | 40  | _   | 60  | %    |

| GMII data TXD[7:0], TX_ER, TX_EN setup time       | t <sub>GTKHDV</sub>                                               | 2.5 | _   | —   | ns   |

| GTX_CLK to GMII data TXD[7:0], TX_ER, TX_EN delay | t <sub>GTKHDX</sub>                                               | 0.5 | _   | 5.0 | ns   |

| GTX_CLK data clock rise and fall times            | t <sub>GTXR</sub> <sup>3</sup> , t <sub>GTXR</sub> <sup>2,4</sup> | _   | _   | 1.0 | ns   |

Notes:

1. The symbols used for timing specifications herein follow the pattern t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state) for outputs. For example, t<sub>GTKHDV</sub> symbolizes GMII transmit timing (GT) with respect to the t<sub>GTX</sub> clock reference (K) going to the high state (H) relative to the time date input signals (D) reaching the valid state (V) to state or setup time. Also, t<sub>GTKHDX</sub> symbolizes GMII transmit timing (GT) with respect to the high state (H) relative to the time date input signals (D) going invalid (X) or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>GTX</sub> represents the GMII(G) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub></sub>

- 2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

- 3. Guaranteed by characterization.

- 4. Guaranteed by design.

Figure 7 shows the GMII transmit AC timing diagram.

Figure 7. GMII Transmit AC Timing Diagram

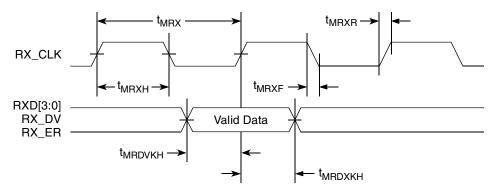

### 8.2.3.2 MII Receive AC Timing Specifications

Table 23 provides the MII receive AC timing specifications.

#### Table 23. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 3.3 V ± 5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                                  | Min  | Тур | Мах | Unit |

|---------------------------------------------|------------------------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRx</sub> <sup>2</sup>                        | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                                     | _    | 40  | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub>                  | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                                  | 10.0 |     | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                                  | 10.0 |     | —   | ns   |

| RX_CLK clock rise and fall time             | t <sub>MRXR</sub> , t <sub>MRXF</sub> <sup>2,3</sup> | 1.0  | _   | 4.0 | ns   |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

Figure 11 shows the MII receive AC timing diagram.

Figure 11. MII Receive AC Timing Diagram

Figure 15 shows the MII management AC timing diagram.

Figure 15. MII Management Interface Timing Diagram

## 9 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8555E.

## 9.1 Local Bus DC Electrical Characteristics

Table 29 provides the DC electrical characteristics for the local bus interface.

| Parameter                 | Symbol          | Test Condition                                     | Min                   | Max                    | Unit |

|---------------------------|-----------------|----------------------------------------------------|-----------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                      | 2                     | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | V <sub>OUT</sub> ≤ V <sub>OL</sub> (max)           | -0.3                  | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}$ <sup>1</sup> = 0 V or $V_{IN}$ = $V_{DD}$ | —                     | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | $OV_{DD} = min,$<br>$I_{OH} = -2mA$                | OV <sub>DD</sub> -0.2 | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min, I <sub>OL</sub> = 2mA      | —                     | 0.2                    | V    |

#### Table 29. Local Bus DC Electrical Characteristics

#### Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

Table 30. Local Bus General Timing Parameters—DLL Enabled (continued)

| Parameter                                    | Configuration <sup>7</sup>     | Symbol <sup>1</sup>  | Min | Мах | Unit | Notes |

|----------------------------------------------|--------------------------------|----------------------|-----|-----|------|-------|

| Local bus clock to output high impedance for | $\overline{LWE[0:1]} = 00$     | t <sub>LBKHOZ2</sub> | _   | 2.8 | ns   | 5, 9  |

| LAD/LDP                                      | <u>LWE[0:1]</u> = 11 (default) |                      |     | 4.2 |      |       |

Notes:

The symbols used for timing specifications herein follow the pattern of t<sub>(First two letters of functional block)(signal)(state)</sub> (reference)(state) for inputs and t<sub>(First two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>LBIXKH1</sub> symbolizes local bus timing (LB) for the input (I) to go invalid (X) with respect to the time the t<sub>LBK</sub> clock reference (K) goes high (H), in this case for clock one(1). Also, t<sub>LBKHOX</sub> symbolizes local bus timing (LB) for the t<sub>LBK</sub> clock reference (K) to go high (H), with respect to the output (O) going invalid (X) or output hold time.

- 2. All timings are in reference to LSYNC\_IN for DLL enabled mode.

- 3. All signals are measured from  $OV_{DD}/2$  of the rising edge of LSYNC\_IN for DLL enabled to  $0.4 \times OV_{DD}$  of the signal in question for 3.3-V signaling levels.

- 4. Input timings are measured at the pin.

- 5. For purposes of active/float timing measurements, the Hi-Z or off state is defined to be when the total current delivered through the component pin is less than or equal to the leakage current specification.

- The value of t<sub>LBOTOT</sub> is defined as the sum of 1/2 or 1 ccb\_clk cycle as programmed by LBCR[AHD], and the number of local bus buffer delays used as programmed at power-on reset with configuration pins LWE[0:1].

- Maximum possible clock skew between a clock LCLK[m] and a relative clock LCLK[n]. Skew measured between complementary signals at OV<sub>DD</sub>/2.

- 8. Guaranteed by characterization.

- 9. Guaranteed by design.

Table 31 describes the general timing parameters of the local bus interface of the MPC8555E with the DLL bypassed.

| Parameter                                                             | Configuration <sup>7</sup>                          | Symbol <sup>1</sup>  | Min  | Max | Unit | Notes |

|-----------------------------------------------------------------------|-----------------------------------------------------|----------------------|------|-----|------|-------|

| Local bus cycle time                                                  |                                                     | t <sub>LBK</sub>     | 6.0  | —   | ns   | 2     |

| Internal launch/capture clock to LCLK delay                           |                                                     | t <sub>LBKHKT</sub>  | 1.8  | 3.4 | ns   | 8     |

| LCLK[n] skew to LCLK[m] or LSYNC_OUT                                  |                                                     | t <sub>lbkskew</sub> | _    | 150 | ps   | 7, 9  |

| Input setup to local bus clock (except LUPWAIT)                       |                                                     | t <sub>LBIVKH1</sub> | 5.2  | —   | ns   | 3, 4  |

| LUPWAIT input setup to local bus clock                                |                                                     | t <sub>LBIVKH2</sub> | 5.1  | —   | ns   | 3, 4  |

| Input hold from local bus clock (except LUPWAIT)                      |                                                     | t <sub>LBIXKH1</sub> | -1.3 | —   | ns   | 3, 4  |

| LUPWAIT input hold from local bus clock                               |                                                     | t <sub>LBIXKH2</sub> | -0.8 | —   | ns   | 3, 4  |

| LALE output transition to LAD/LDP output transition (LATCH hold time) |                                                     | t <sub>LBOTOT</sub>  | 1.5  |     | ns   | 6     |

| Local bus clock to output valid (except                               | $\overline{LWE[0:1]} = 00$                          | t <sub>LBKLOV1</sub> | _    | 0.5 | ns   | 3     |

| LAD/LDP and LALE)                                                     | $\overline{LWE[0:1]} = 11$ (default)                |                      |      | 2.0 | ]    |       |

| Local bus clock to data valid for LAD/LDP                             | LWE[0:1] = 00                                       | t <sub>LBKLOV2</sub> | _    | 0.7 | ns   | 3     |

|                                                                       | $\overline{\text{LWE}[0:1]} = 11 \text{ (default)}$ |                      |      | 2.2 |      |       |

Table 31. Local Bus General Timing Parameters—DLL Bypassed

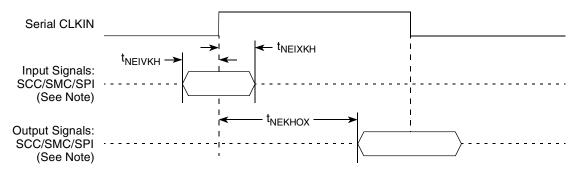

Figure 27 shows the SCC/SMC/SPI external clock.

Note: The clock edge is selectable on SCC and SPI.

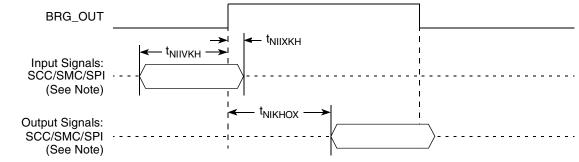

Figure 28 shows the SCC/SMC/SPI internal clock.

Note: The clock edge is selectable on SCC and SPI.

#### Figure 28. SCC/SMC/SPI AC Timing Internal Clock Diagram

#### NOTE

<sup>1</sup> SPI AC timings are internal mode when it is master because SPICLK is an output, and external mode when it is slave.

<sup>2</sup> SPI AC timings refer always to SPICLK.

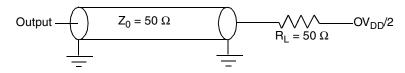

Figure 32 provides the AC test load for TDO and the boundary-scan outputs of the MPC8555E.

Figure 32. AC Test Load for the JTAG Interface

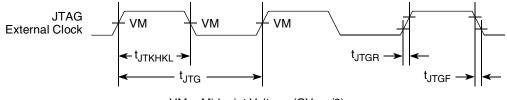

Figure 33 provides the JTAG clock input timing diagram.

$VM = Midpoint Voltage (OV_{DD}/2)$

Figure 33. JTAG Clock Input Timing Diagram

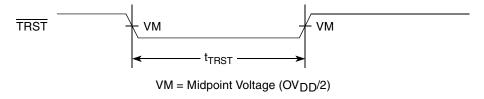

Figure 34 provides the TRST timing diagram.

Figure 34. TRST Timing Diagram

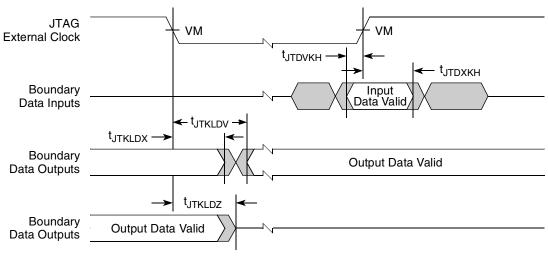

Figure 35 provides the boundary-scan timing diagram.

VM = Midpoint Voltage (OV<sub>DD</sub>/2)

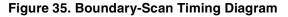

Figure 40 shows the PCI input AC timing conditions.

Figure 40. PCI Input AC Timing Measurement Conditions

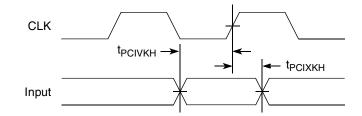

Figure 41 shows the PCI output AC timing conditions.

Figure 41. PCI Output AC Timing Measurement Condition

## 14 Package and Pin Listings

This section details package parameters, pin assignments, and dimensions.

## 14.1 Package Parameters for the MPC8555E FC-PBGA

The package parameters are as provided in the following list. The package type is  $29 \text{ mm} \times 29 \text{ mm}$ , 783 flip chip plastic ball grid array (FC-PBGA).

| Die size                | $8.7 \text{ mm} \times 9.3 \text{ mm} \times 0.75 \text{ mm}$ |

|-------------------------|---------------------------------------------------------------|

| Package outline         | $29 \text{ mm} \times 29 \text{ mm}$                          |

| Interconnects           | 783                                                           |

| Pitch                   | 1 mm                                                          |

| Minimum module height   | 3.07 mm                                                       |

| Maximum module height   | 3.75 mm                                                       |

| Solder Balls            | 62 Sn/36 Pb/2 Ag                                              |

| Ball diameter (typical) | 0.5 mm                                                        |

Package and Pin Listings

## 14.3 Pinout Listings

Table 43 provides the pin-out listing for the MPC8555E, 783 FC-PBGA package.

#### Table 43. MPC8555E Pinout Listing

| Signal                                   | Package Pin Number                                                                                                                                                                              | Pin Type                                                                | Power<br>Supply  | Notes |  |  |  |  |  |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|-------|--|--|--|--|--|

| PCI1 and PCI2 (one 64-bit or two 32-bit) |                                                                                                                                                                                                 |                                                                         |                  |       |  |  |  |  |  |

| PCI1_AD[63:32],<br>PCI2_AD[31:0]         | AA14, AB14, AC14, AD14, AE14, AF14, AG14, AH14,<br>V15, W15, Y15, AA15, AB15, AC15, AD15, AG15,<br>AH15, V16, W16, AB16, AC16, AD16, AE16, AF16,<br>V17, W17, Y17, AA17, AB17, AE17, AF17, AF18 | 15, AC15, AD15, AG15,<br>216, AD16, AE16, AF16,<br>17, AE17, AF17, AF18 |                  |       |  |  |  |  |  |

| PCI1_AD[31:0]                            | AH6, AD7, AE7, AH7, AB8, AC8, AF8, AG8, AD9,<br>AE9, AF9, AG9, AH9, W10, Y10, AA10, AE11, AF11,<br>AG11, AH11, V12, W12, Y12, AB12, AD12, AE12,<br>AG12, AH12, V13, Y13, AB13, AC13             | I/O                                                                     | OV <sub>DD</sub> | 17    |  |  |  |  |  |

| PCI_C_BE64[7:4]<br>PCI2_C_BE[3:0]        | AG13, AH13, V14, W14                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 17    |  |  |  |  |  |

| PCI_C_BE64[3:0]<br>PCI1_C_BE[3:0]        | AH8, AB10, AD11, AC12                                                                                                                                                                           | I/O                                                                     | OV <sub>DD</sub> | 17    |  |  |  |  |  |

| PCI1_PAR                                 | AA11                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | —     |  |  |  |  |  |

| PCI1_PAR64/PCI2_PAR                      | Y14                                                                                                                                                                                             | I/O                                                                     | OV <sub>DD</sub> | —     |  |  |  |  |  |

| PCI1_FRAME                               | AC10                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_TRDY                                | AG10                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_IRDY                                | AD10                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_STOP                                | V11                                                                                                                                                                                             | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_DEVSEL                              | AH10                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_IDSEL                               | AA9                                                                                                                                                                                             | I                                                                       | OV <sub>DD</sub> | —     |  |  |  |  |  |

| PCI1_REQ64/PCI2_FRAME                    | AE13                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 5, 10 |  |  |  |  |  |

| PCI1_ACK64/PCI2_DEVSEL                   | AD13                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_PERR                                | W11                                                                                                                                                                                             | I/O                                                                     | OV <sub>DD</sub> | 2     |  |  |  |  |  |

| PCI1_SERR                                | Y11                                                                                                                                                                                             | I/O                                                                     | OV <sub>DD</sub> | 2, 4  |  |  |  |  |  |

| PCI1_REQ[0]                              | AF5                                                                                                                                                                                             | I/O                                                                     | OV <sub>DD</sub> | _     |  |  |  |  |  |

| PCI1_REQ[1:4]                            | AF3, AE4, AG4, AE5                                                                                                                                                                              | I                                                                       | OV <sub>DD</sub> | —     |  |  |  |  |  |

| PCI1_GNT[0]                              | AE6                                                                                                                                                                                             | I/O                                                                     | OV <sub>DD</sub> | —     |  |  |  |  |  |

| PCI1_GNT[1:4]                            | AG5, AH5, AF6, AG6                                                                                                                                                                              | 0                                                                       | OV <sub>DD</sub> | 5, 9  |  |  |  |  |  |

| PCI1_CLK                                 | AH25                                                                                                                                                                                            | I                                                                       | OV <sub>DD</sub> |       |  |  |  |  |  |

| PCI2_CLK                                 | AH27                                                                                                                                                                                            | I                                                                       | OV <sub>DD</sub> | —     |  |  |  |  |  |

| PCI2_GNT[0]                              | AC18                                                                                                                                                                                            | I/O                                                                     | OV <sub>DD</sub> | —     |  |  |  |  |  |

Package and Pin Listings

| Signal           | Package Pin Number                             | Pin Type | Power<br>Supply  | Notes    |

|------------------|------------------------------------------------|----------|------------------|----------|

| IRQ[0:7]         | AA18, Y18, AB18, AG24, AA21, Y19, AA19, AG25   | I        | OV <sub>DD</sub> | —        |

| IRQ8             | AB20                                           | I        | OV <sub>DD</sub> | 9        |

| IRQ9/DMA_DREQ3   | Y20                                            | I        | OV <sub>DD</sub> | 1        |

| IRQ10/DMA_DACK3  | AF26                                           | I/O      | OV <sub>DD</sub> | 1        |

| IRQ11/DMA_DDONE3 | AH24                                           | I/O      | OV <sub>DD</sub> | 1        |

| IRQ_OUT          | AB21                                           | 0        | OV <sub>DD</sub> | 2, 4     |

|                  | Ethernet Management Interface                  |          | 1                |          |

| EC_MDC           | F1                                             | 0        | OV <sub>DD</sub> | 5, 9     |

| EC_MDIO          | E1                                             | I/O      | OV <sub>DD</sub> | _        |

|                  | Gigabit Reference Clock                        |          | 1                |          |

| EC_GTX_CLK125    | E2                                             | I        | LV <sub>DD</sub> | _        |

|                  | Three-Speed Ethernet Controller (Gigabit Ether | net 1)   | 1                |          |

| TSEC1_TXD[7:4]   | A6, F7, D7, C7                                 | 0        | LV <sub>DD</sub> | _        |

| TSEC1_TXD[3:0]   | B7, A7, G8, E8                                 | 0        | LV <sub>DD</sub> | 9, 18    |

| TSEC1_TX_EN      | C8                                             | 0        | LV <sub>DD</sub> | 11       |

| TSEC1_TX_ER      | B8                                             | 0        | LV <sub>DD</sub> | —        |

| TSEC1_TX_CLK     | C6                                             | I        | LV <sub>DD</sub> | —        |

| TSEC1_GTX_CLK    | B6                                             | 0        | LV <sub>DD</sub> | —        |

| TSEC1_CRS        | C3                                             | I        | LV <sub>DD</sub> | —        |

| TSEC1_COL        | G7                                             | I        | LV <sub>DD</sub> | —        |

| TSEC1_RXD[7:0]   | D4, B4, D3, D5, B5, A5, F6, E6                 | I        | LV <sub>DD</sub> | —        |

| TSEC1_RX_DV      | D2                                             | I        | LV <sub>DD</sub> | —        |

| TSEC1_RX_ER      | E5                                             | I        | LV <sub>DD</sub> | —        |

| TSEC1_RX_CLK     | D6                                             | I        | LV <sub>DD</sub> | —        |

|                  | Three-Speed Ethernet Controller (Gigabit Ether | net 2)   |                  |          |

| TSEC2_TXD[7:4]   | B10, A10, J10, K11                             | 0        | LV <sub>DD</sub> | —        |

| TSEC2_TXD[3:0]   | J11, H11, G11, E11                             | 0        | LV <sub>DD</sub> | 5, 9, 18 |

| TSEC2_TX_EN      | B11                                            | 0        | LV <sub>DD</sub> | 11       |

| TSEC2_TX_ER      | D11                                            | 0        | LV <sub>DD</sub> | —        |

| TSEC2_TX_CLK     | D10                                            | I        | LV <sub>DD</sub> | —        |

| TSEC2_GTX_CLK    | C10                                            | 0        | LV <sub>DD</sub> | —        |

#### Package and Pin Listings

#### Table 43. MPC8555E Pinout Listing (continued)

| Signal              | Package Pin Number                                                                                                    | Pin Type | Power<br>Supply  | Notes |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PB[18:31]           | P7, P6, P5, P4, P3, P2, P1, R1, R2, R3, R4, R5, R6,<br>R7                                                             | I/O      | OV <sub>DD</sub> | —     |

| PC[0, 1, 4–29]      | R8, R9, T9, T6, T5, T4, T1, U1, U2, U3, U4, U7, U8,<br>U9, U10, V9, V6, V5, V4, V3, V2, V1, W1, W2, W3,<br>W6, W7, W8 | I/O      | OV <sub>DD</sub> | —     |

| PD[7, 14–25, 29–31] | Y4, AA2, AA1, AB1, AB2, AB3, AB5, AB6, AC7, AC4, AC3, AC2, AC1, AD6, AE3, AE2                                         | Ι/Ο      | OV <sub>DD</sub> | —     |

Notes:

- 1. All multiplexed signals are listed only once and do not re-occur. For example, LCS5/DMA\_REQ2 is listed only once in the Local Bus Controller Interface section, and is not mentioned in the DMA section even though the pin also functions as DMA\_REQ2.

- 2. Recommend a weak pull-up resistor (2–10 k $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 3. TEST\_SEL0 must be pulled-high, TEST\_SEL1 must be tied to ground.

- 4. This pin is an open drain signal.

- 5. This pin is a reset configuration pin. It has a weak internal pull-up P-FET which is enabled only when the MPC8555E is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kΩ pull-down resistor. If an external device connected to this pin might pull it down during reset, then a pull-up or active driver is needed if the signal is intended to be high during reset.

- 6. Treat these pins as no connects (NC) unless using debug address functionality.

- The value of LA[28:31] during reset sets the CCB clock to SYSCLK PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See Section 15.2, "Platform/System PLL Ratio."

- The value of LALE and LGPL2 at reset set the e500 core clock to CCB Clock PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See the Section 15.3, "e500 Core PLL Ratio."

- 9. Functionally, this pin is an output, but structurally it is an I/O because it either samples configuration input during reset or because it has other manufacturing test functions. This pin therefore is described as an I/O for boundary scan.

- This pin functionally requires a pull-up resistor, but during reset it is a configuration input that controls 32- vs. 64-bit PCI operation. Therefore, it must be actively driven low during reset by reset logic if the device is to be configured to be a 64-bit PCI device. Refer to the PCI Specification.

- 11. This output is actively driven during reset rather than being three-stated during reset.

- 12. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 13. These pins are connected to the V<sub>DD</sub>/GND planes internally and may be used by the core power supply to improve tracking and regulation.

- 14. Internal thermally sensitive resistor.

- 15. No connections should be made to these pins.

- 16. These pins are not connected for any functional use.

- PCI specifications recommend that a weak pull-up resistor (2–10 kΩ) be placed on the higher order pins to OV<sub>DD</sub> when using 64-bit buffer mode (pins PCI\_AD[63:32] and PCI2\_C\_BE[7:4]).

- 18. If this pin is connected to a device that pulls down during reset, an external pull-up is required to that is strong enough to pull this signal to a logic 1 during reset.

- 19. Recommend a pull-up resistor (~1 k $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 20. These are test signals for factory use only and must be pulled up (100 $\Omega$  to 1k $\Omega$ ) to OV<sub>DD</sub> for normal machine operation.

- 21. If this signal is used as both an input and an output, a weak pull-up ( $\sim 10 k\Omega$ ) is required on this pin.

- 22. MSYNC\_IN and MSYNC\_OUT should be connected together for proper operation.

## 15 Clocking

This section describes the PLL configuration of the MPC8555E. Note that the platform clock is identical to the CCB clock.

## 15.1 Clock Ranges

Table 44 provides the clocking specifications for the processor core and Table 44 provides the clocking specifications for the memory bus.

|                                     |     |         |     | Maximur | n Proce | ssor Core            | Frequen | су       |     |      |       |         |  |  |  |  |

|-------------------------------------|-----|---------|-----|---------|---------|----------------------|---------|----------|-----|------|-------|---------|--|--|--|--|

| Characteristic                      | 533 | 533 MHz |     | 600 MHz |         | 667 MHz 833 MHz 1000 |         | 1000 MHz |     |      | Notes |         |  |  |  |  |

|                                     | Min | Max     | Min | Max     | Min     | Max                  | Min     | Max      | Min | Max  |       |         |  |  |  |  |

| e500 core<br>processor<br>frequency | 400 | 533     | 400 | 600     | 400     | 667                  | 400     | 833      | 400 | 1000 | MHz   | 1, 2, 3 |  |  |  |  |

**Table 44. Processor Core Clocking Specifications**

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

2.) The minimum e500 core frequency is based on the minimum platform frequency of 200 MHz.

3. 1000 MHz frequency supports only a 1.3 V core.

#### Table 45. Memory Bus Clocking Specifications

| Characteristic       | Maximum Pro<br>Frequ<br>533, 600, 667, | Unit | Notes |         |

|----------------------|----------------------------------------|------|-------|---------|

|                      | Min                                    | Max  |       |         |

| Memory bus frequency | 100                                    | 166  | MHz   | 1, 2, 3 |

Notes:

- 1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR data rate, hence, half of the platform clock frequency.

- 3. 1000 MHz frequency supports only a 1.3 V core.

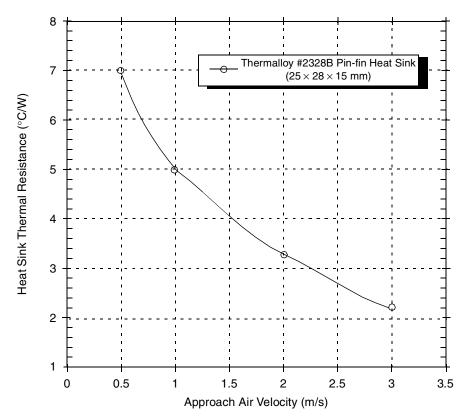

Figure 47. Thermalloy #2328B Heat Sink-to-Ambient Thermal Resistance Versus Airflow Velocity

#### 16.2.4.2 Case 2

Every system application has different conditions that the thermal management solution must solve. As an alternate example, assume that the air reaching the component is 85 °C with an approach velocity of 1 m/sec. For a maximum junction temperature of 105 °C at 8 W, the total thermal resistance of junction to case thermal resistance plus thermal interface material plus heat sink thermal resistance must be less than 2.5 °C/W. The value of the junction to case thermal resistance in Table 49 includes the thermal interface resistance of a thin layer of thermal grease as documented in footnote 4 of the table. Assuming that the heat sink is flat enough to allow a thin layer of grease or phase change material, then the heat sink must be less than 1.5 °C/W.

Millennium Electronics (MEI) has tooled a heat sink MTHERM-1051 for this requirement assuming a compactPCI environment at 1 m/sec and a heat sink height of 12 mm. The MEI solution is illustrated in Figure 48 and Figure 49. This design has several significant advantages:

- The heat sink is clipped to a plastic frame attached to the application board with screws or plastic inserts at the corners away from the primary signal routing areas.

- The heat sink clip is designed to apply the force holding the heat sink in place directly above the die at a maximum force of less than 10 lbs.

- For applications with significant vibration requirements, silicone damping material can be applied between the heat sink and plastic frame.

System Design Information

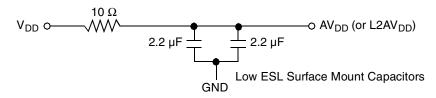

Figure 50 shows the PLL power supply filter circuit.

Figure 50. PLL Power Supply Filter Circuit

## 17.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the MPC8555E can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8555E system, and the MPC8555E itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  pins of the MPC8555E. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $OV_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ ,  $OV_{DD}$ , OV

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $OV_{DD}$ ,  $GV_{DD}$ , and  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100–330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON).

## 17.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $OV_{DD}$ ,  $GV_{DD}$ , or  $LV_{DD}$  as required. Unused active high inputs should be connected to GND. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ ,  $OV_{DD}$ , and GND pins of the MPC8555E.

## 17.5 Output Buffer DC Impedance

The MPC8555E drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for  $I^2C$ ).

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $OV_{DD}$  or GND. Then, the value of each resistor is varied until the pad voltage is  $OV_{DD}/2$  (see Figure 51). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices.

# NP

#### System Design Information

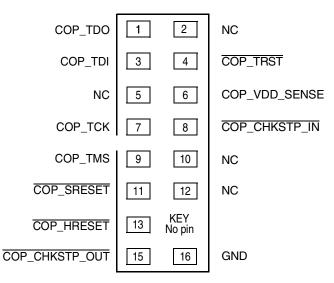

The COP function of these processors allow a remote computer system (typically, a PC with dedicated hardware and debugging software) to access and control the internal operations of the processor. The COP interface connects primarily through the JTAG port of the processor, with some additional status monitoring signals. The COP port requires the ability to independently assert HRESET or TRST in order to fully control the processor. If the target system has independent reset sources, such as voltage monitors, watchdog timers, power supply failures, or push-button switches, then the COP reset signals must be merged into these signals with logic.

The arrangement shown in Figure 52 allows the COP port to independently assert  $\overline{\text{HRESET}}$  or  $\overline{\text{TRST}}$ , while ensuring that the target can drive  $\overline{\text{HRESET}}$  as well.

The COP interface has a standard header, shown in Figure 52, for connection to the target system, and is based on the 0.025" square-post, 0.100" centered header assembly (often called a Berg header). The connector typically has pin 14 removed as a connector key.

The COP header adds many benefits such as breakpoints, watchpoints, register and memory examination/modification, and other standard debugger features. An inexpensive option can be to leave the COP header unpopulated until needed.

There is no standardized way to number the COP header; consequently, many different pin numbers have been observed from emulator vendors. Some are numbered top-to-bottom then left-to-right, while others use left-to-right then top-to-bottom, while still others number the pins counter clockwise from pin 1 (as with an IC). Regardless of the numbering, the signal placement recommended in Figure 52 is common to all known emulators.

Figure 52. COP Connector Physical Pinout