#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                    |

|---------------------------------|-----------------------------------------------------------|

| Core Processor                  | PowerPC e500                                              |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                            |

| Speed                           | 667MHz                                                    |

| Co-Processors/DSP               | Communications; CPM                                       |

| RAM Controllers                 | DDR, SDRAM                                                |

| Graphics Acceleration           | No                                                        |

| Display & Interface Controllers | -                                                         |

| Ethernet                        | 10/100/1000Mbps (2)                                       |

| SATA                            | -                                                         |

| USB                             | USB 2.0 (1)                                               |

| Voltage - I/O                   | 2.5V, 3.3V                                                |

| Operating Temperature           | 0°C ~ 105°C (TA)                                          |

| Security Features               | Cryptography, Random Number Generator                     |

| Package / Case                  | 783-BBGA, FCBGA                                           |

| Supplier Device Package         | 783-FCPBGA (29x29)                                        |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8555vtalf |

|                                 |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Overview

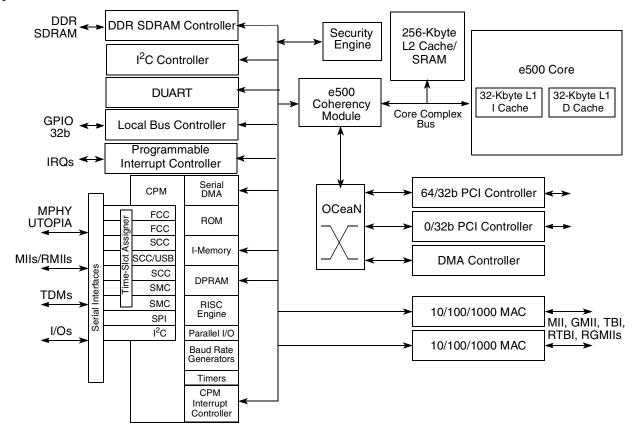

The following section provides a high-level overview of the MPC8555E features. Figure 1 shows the major functional units within the MPC8555E.

Figure 1. MPC8555E Block Diagram

## 1.1 Key Features

The following lists an overview of the MPC8555E feature set.

- Embedded e500 Book E-compatible core

- High-performance, 32-bit Book E-enhanced core that implements the PowerPC architecture

- Dual-issue superscalar, 7-stage pipeline design

- 32-Kbyte L1 instruction cache and 32-Kbyte L1 data cache with parity protection

- Lockable L1 caches—entire cache or on a per-line basis

- Separate locking for instructions and data

- Single-precision floating-point operations

- Memory management unit especially designed for embedded applications

- Enhanced hardware and software debug support

- Dynamic power management

- Performance monitor facility

- Can be partitioned into 128-Kbyte L2 cache plus 128-Kbyte SRAM

- Full ECC support on 64-bit boundary in both cache and SRAM modes

- SRAM operation supports relocation and is byte-accessible

- Cache mode supports instruction caching, data caching, or both

- External masters can force data to be allocated into the cache through programmed memory ranges or special transaction types (stashing).

- Eight-way set-associative cache organization (1024 sets of 32-byte cache lines)

- Supports locking the entire cache or selected lines

- Individual line locks set and cleared through Book E instructions or by externally mastered transactions

- Global locking and flash clearing done through writes to L2 configuration registers

- Instruction and data locks can be flash cleared separately

- Read and write buffering for internal bus accesses

- Address translation and mapping unit (ATMU)

- Eight local access windows define mapping within local 32-bit address space

- Inbound and outbound ATMUs map to larger external address spaces

- Three inbound windows plus a configuration window on PCI

- Four inbound windows

- Four outbound windows plus default translation for PCI

- DDR memory controller

- Programmable timing supporting first generation DDR SDRAM

- 64-bit data interface, up to MHz data rate

- Four banks of memory supported, each up to 1 Gbyte

- DRAM chip configurations from 64 Mbits to 1 Gbit with x8/x16 data ports

- Full ECC support

- Page mode support (up to 16 simultaneous open pages)

- Contiguous or discontiguous memory mapping

- Sleep mode support for self refresh DDR SDRAM

- Supports auto refreshing

- On-the-fly power management using CKE signal

- Registered DIMM support

- Fast memory access via JTAG port

- 2.5-V SSTL2 compatible I/O

- Programmable interrupt controller (PIC)

- Programming model is compliant with the OpenPIC architecture

- Supports 16 programmable interrupt and processor task priority levels

- Supports 12 discrete external interrupts

- Supports 4 message interrupts with 32-bit messages

Overview

- Supports connection of an external interrupt controller such as the 8259 programmable interrupt controller

- Four global high resolution timers/counters that can generate interrupts

- Supports additional internal interrupt sources

- Supports fully nested interrupt delivery

- Interrupts can be routed to external pin for external processing

- Interrupts can be routed to the e500 core's standard or critical interrupt inputs

- Interrupt summary registers allow fast identification of interrupt source

- Two I<sup>2</sup>C controllers (one is contained within the CPM, the other is a stand-alone controller which is not part of the CPM)

- Two-wire interface

- Multiple master support

- Master or slave I<sup>2</sup>C mode support

- On-chip digital filtering rejects spikes on the bus

- Boot sequencer

- Optionally loads configuration data from serial ROM at reset via the stand-alone I<sup>2</sup>C interface

- Can be used to initialize configuration registers and/or memory

- Supports extended I<sup>2</sup>C addressing mode

- Data integrity checked with preamble signature and CRC

- DUART

- Two 4-wire interfaces (RXD, TXD, RTS, CTS)

- Programming model compatible with the original 16450 UART and the PC16550D

- Local bus controller (LBC)

- Multiplexed 32-bit address and data operating at up to 166 MHz

- Eight chip selects support eight external slaves

- Up to eight-beat burst transfers

- The 32-, 16-, and 8-bit port sizes are controlled by an on-chip memory controller

- Three protocol engines available on a per chip select basis:

- General purpose chip select machine (GPCM)

- Three user programmable machines (UPMs)

- Dedicated single data rate SDRAM controller

- Parity support

- Default boot ROM chip select with configurable bus width (8-, 16-, or 32-bit)

- Two Three-speed (10/100/1000)Ethernet controllers (TSECs)

- Dual IEEE 802.3, 802.3u, 802.3x, 802.3z AC compliant controllers

- Support for Ethernet physical interfaces:

- 10/100/1000 Mbps IEEE 802.3 GMII

- 10/100 Mbps IEEE 802.3 MII

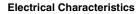

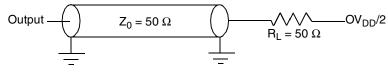

Figure 2 shows the undershoot and overshoot voltages at the interfaces of the MPC8555E.

1. Note that  $t_{\mbox{\scriptsize SYS}}$  refers to the clock period associated with the  $\mbox{\scriptsize SYSCLK}$  signal.

### Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/OV<sub>DD</sub>/LV<sub>DD</sub>

The MPC8555E core voltage must always be provided at nominal 1.2 V (see Table 2 for actual recommended core voltage). Voltage to the processor interface I/Os are provided through separate sets of supply pins and must be provided at the voltages shown in Table 2. The input voltage threshold scales with respect to the associated I/O supply voltage.  $OV_{DD}$  and  $LV_{DD}$  based receivers are simple CMOS I/O circuits and satisfy appropriate LVCMOS type specifications. The DDR SDRAM interface uses a single-ended differential receiver referenced the externally supplied  $MV_{REF}$  signal (nominally set to  $GV_{DD}/2$ ) as is appropriate for the SSTL2 electrical signaling standard.

**RESET** Initialization

## 4.3 Real Time Clock Timing

Table 8 provides the real time clock (RTC) AC timing specifications.

Table 8. RTC AC Timing Specifications

| Parameter/Condition | Symbol            | Min                         | Typical | Max | Unit | Notes |

|---------------------|-------------------|-----------------------------|---------|-----|------|-------|

| RTC clock high time | t <sub>RTCH</sub> | 2 х<br>t <sub>CCB_CLK</sub> | _       | _   | ns   |       |

| RTC clock low time  | t <sub>RTCL</sub> | 2 х<br>t <sub>CCB_CLK</sub> | —       | -   | ns   | —     |

# 5 **RESET Initialization**

This section describes the AC electrical specifications for the RESET initialization timing requirements of the MPC8555E. Table 9 provides the RESET initialization AC timing specifications.

### Table 9. RESET Initialization Timing Specifications

| Parameter/Condition                                                                                     | Min | Мах | Unit    | Notes |

|---------------------------------------------------------------------------------------------------------|-----|-----|---------|-------|

| Required assertion time of HRESET                                                                       | 100 | —   | μs      | _     |

| Minimum assertion time for SRESET                                                                       | 512 | —   | SYSCLKs | 1     |

| PLL input setup time with stable SYSCLK before HRESET negation                                          | 100 | _   | μs      | —     |

| Input setup time for POR configs (other than PLL config) with respect to negation of HRESET             | 4   | _   | SYSCLKs | 1     |

| Input hold time for POR configs (including PLL config) with respect to negation of HRESET               | 2   | _   | SYSCLKs | 1     |

| Maximum valid-to-high impedance time for actively driven POR configs with respect to negation of HRESET | _   | 5   | SYSCLKs | 1     |

Notes:

1. SYSCLK is identical to the PCI\_CLK signal and is the primary clock input for the MPC8555E. See the MPC8555E PowerQUICC<sup>™</sup> III Integrated Communications Processor Reference Manual for more details.

### Table 10 provides the PLL and DLL lock times.

### Table 10. PLL and DLL Lock Times

| Parameter/Condition | Min  | Мах     | Unit       | Notes |

|---------------------|------|---------|------------|-------|

| PLL lock times      | —    | 100     | μs         | _     |

| DLL lock times      | 7680 | 122,880 | CCB Clocks | 1, 2  |

Notes:

1. DLL lock times are a function of the ratio between the output clock and the platform (or CCB) clock. A 2:1 ratio results in the minimum and an 8:1 ratio results in the maximum.

2. The CCB clock is determined by the SYSCLK  $\times$  platform PLL ratio.

### Table 14. DDR SDRAM Output AC Timing Specifications for Source Synchronous Mode (continued)

At recommended operating conditions with  $GV_{DD}$  of 2.5 V ± 5%.

| Parameter                                                                          | Symbol <sup>1</sup>                         | Min                                | Мах                       | Unit | Notes |

|------------------------------------------------------------------------------------|---------------------------------------------|------------------------------------|---------------------------|------|-------|

| MCS(n) output hold with respect to MCK<br>333 MHz<br>266 MHz<br>200 MHz            | t <sub>DDKHCX</sub>                         | 2.0<br>2.65<br>3.8                 | _                         | ns   | 4     |

| MCK to MDQS<br>333 MHz<br>266 MHz<br>200 MHz                                       | t <sub>DDKHMH</sub>                         | -0.9<br>-1.1<br>-1.2               | 0.3<br>0.5<br>0.6         | ns   | 5     |

| MDQ/MECC/MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 900<br>900<br>1200                 | _                         | ps   | 6     |

| MDQ/MECC/MDM output hold with respect to<br>MDQS<br>333 MHz<br>266 MHz<br>200 MHz  | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 900<br>900<br>1200                 | _                         | ps   | 6     |

| MDQS preamble start                                                                | t <sub>DDKHMP</sub>                         | $-0.5 \times t_{\text{MCK}} - 0.9$ | $-0.5 	imes t_{MCK}$ +0.3 | ns   | 7     |

| MDQS epilogue end                                                                  | t <sub>DDKLME</sub>                         | -0.9                               | 0.3                       | ns   | 7     |

#### Notes:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- In the source synchronous mode, MCK/MCK can be shifted in 1/4 applied cycle increments through the Clock Control Register. For the skew measurements referenced for t<sub>AOSKEW</sub> it is assumed that the clock adjustment is set to align the address/command valid with the rising edge of MCK.

- 4. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS. For the ADDR/CMD setup and hold specifications, it is assumed that the Clock Control register is set to adjust the memory clocks by 1/2 applied cycle. The MCSx pins are separated from the ADDR/CMD (address and command) bus in the HW spec. This was separated because the MCSx pins typically have different loadings than the rest of the address and command bus, even though they have the same timings.

- 5. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK(n) clock (KH) until the MDQS signal is valid (MH). In the source synchronous mode, MDQS can launch later than MCK by 0.3 ns at the maximum. However, MCK may launch later than MDQS by as much as 0.9 ns. t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. In source synchronous mode, this typically is set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these two parameters have been set to the same adjustment value. See the *MPC8555E PowerQUICC™ III Integrated Communications Processor Reference Manual* for a description and understanding of the timing modifications enabled by use of these bits.

- 6. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the MPC8555E.

- 7. All outputs are referenced to the rising edge of MCK(n) at the pins of the MPC8555E. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

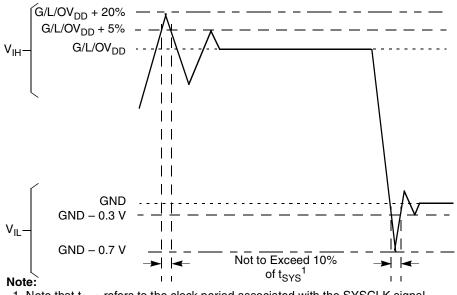

## 8.2.3.2 MII Receive AC Timing Specifications

Table 23 provides the MII receive AC timing specifications.

#### Table 23. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  of 3.3 V ± 5%.

| Parameter/Condition                         | Symbol <sup>1</sup>                                  | Min  | Тур | Мах | Unit |

|---------------------------------------------|------------------------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                 | t <sub>MRx</sub> <sup>2</sup>                        | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                | t <sub>MRX</sub>                                     | _    | 40  | —   | ns   |

| RX_CLK duty cycle                           | t <sub>MRXH</sub> /t <sub>MRX</sub>                  | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK | t <sub>MRDVKH</sub>                                  | 10.0 |     | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK  | t <sub>MRDXKH</sub>                                  | 10.0 |     | —   | ns   |

| RX_CLK clock rise and fall time             | t <sub>MRXR</sub> , t <sub>MRXF</sub> <sup>2,3</sup> | 1.0  | _   | 4.0 | ns   |

#### Notes:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).</sub>

2. Signal timings are measured at 0.7 V and 1.9 V voltage levels.

3.Guaranteed by design.

Figure 11 shows the MII receive AC timing diagram.

Figure 11. MII Receive AC Timing Diagram

## 8.2.4.2 TBI Receive AC Timing Specifications

Table 25 provides the TBI receive AC timing specifications.

| Table 25. | . TBI Receive | <b>AC</b> Timing | Specifications |

|-----------|---------------|------------------|----------------|

|-----------|---------------|------------------|----------------|

At recommended operating conditions with  $LV_{DD}$  of 3.3 V ± 5%.

| Parameter/Condition                  | Symbol <sup>1</sup>                                  | Min | Тур  | Max | Unit |

|--------------------------------------|------------------------------------------------------|-----|------|-----|------|

| RX_CLK clock period                  | t <sub>TRX</sub>                                     |     | 16.0 |     | ns   |

| RX_CLK skew                          | t <sub>SKTRX</sub>                                   | 7.5 | _    | 8.5 | ns   |

| RX_CLK duty cycle                    | t <sub>TRXH</sub> /t <sub>TRX</sub>                  | 40  | —    | 60  | %    |

| RCG[9:0] setup time to rising RX_CLK | t <sub>TRDVKH</sub>                                  | 2.5 | —    | _   | ns   |

| RCG[9:0] hold time to rising RX_CLK  | t <sub>TRDXKH</sub>                                  | 1.5 | —    | _   | ns   |

| RX_CLK clock rise time and fall time | t <sub>TRXR</sub> , t <sub>TRXF</sub> <sup>2,3</sup> | 0.7 |      | 2.4 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of  $t_{(first two letters of functional block)(signal)(state)}$ (reference)(state) for inputs and  $t_{(first two letters of functional block)(reference)(state)(signal)(state)}$  for outputs. For example,  $t_{TRDVKH}$  symbolizes TBI receive timing (TR) with respect to the time data input signals (D) reach the valid state (V) relative to the  $t_{TRX}$  clock reference (K) going to the high (H) state or setup time. Also,  $t_{TRDXKH}$  symbolizes TBI receive timing (TR) with respect to the time data input signals (D) went invalid (X) relative to the  $t_{TRX}$  clock reference (K) going to the high (H) state. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of  $t_{TRX}$  represents the TBI (T) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall). For symbols representing skews, the subscript is skew (SK) followed by the clock that is being skewed (TRX).

2. Guaranteed by design.

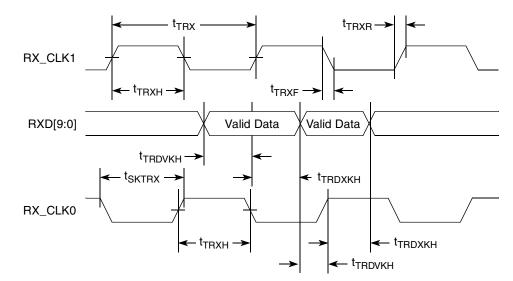

Figure 13 shows the TBI receive AC timing diagram.

Figure 13. TBI Receive AC Timing Diagram

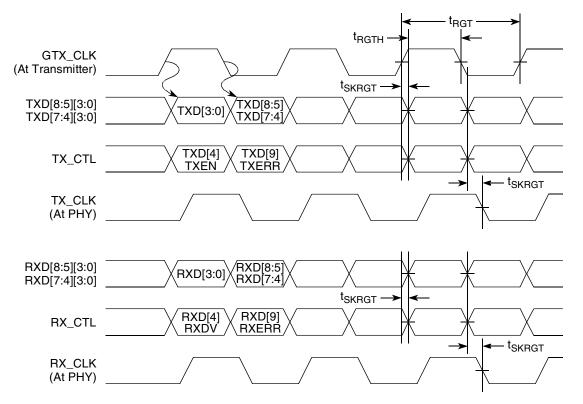

Figure 14 shows the RBMII and RTBI AC timing and multiplexing diagrams.

Figure 14. RGMII and RTBI AC Timing and Multiplexing Diagrams

## 8.3 Ethernet Management Interface Electrical Characteristics

The electrical characteristics specified here apply to MII management interface signals MDIO (management data input/output) and MDC (management data clock). The electrical characteristics for GMII, RGMII, TBI and RTBI are specified in Section 8.1, "Three-Speed Ethernet Controller (TSEC) (10/100/1000 Mbps)—GMII/MII/TBI/RGMII/RTBI Electrical Characteristics."

## 8.3.1 MII Management DC Electrical Characteristics

The MDC and MDIO are defined to operate at a supply voltage of 3.3 V. The DC electrical characteristics for MDIO and MDC are provided in Table 27.

| Parameter              | Symbol           | Conditions                |                        | Min  | Мах                    | Unit |

|------------------------|------------------|---------------------------|------------------------|------|------------------------|------|

| Supply voltage (3.3 V) | OV <sub>DD</sub> | —                         |                        | 3.13 | 3.47                   | V    |

| Output high voltage    | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA | LV <sub>DD</sub> = Min | 2.10 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage     | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA  | LV <sub>DD</sub> = Min | GND  | 0.50                   | V    |

| Input high voltage     | V <sub>IH</sub>  | —                         |                        | 1.70 | —                      | V    |

| Input low voltage      | V <sub>IL</sub>  | -                         | _                      | —    | 0.90                   | V    |

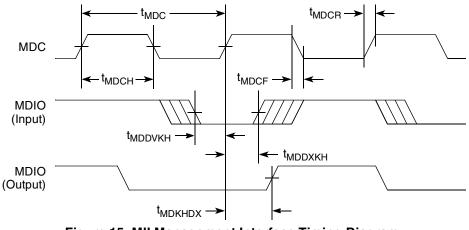

Figure 15 shows the MII management AC timing diagram.

Figure 15. MII Management Interface Timing Diagram

## 9 Local Bus

This section describes the DC and AC electrical specifications for the local bus interface of the MPC8555E.

## 9.1 Local Bus DC Electrical Characteristics

Table 29 provides the DC electrical characteristics for the local bus interface.

| Parameter                 | Symbol          | Test Condition                                     | Min                   | Max                    | Unit |

|---------------------------|-----------------|----------------------------------------------------|-----------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                      | 2                     | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | V <sub>OUT</sub> ≤ V <sub>OL</sub> (max)           | -0.3                  | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}$ <sup>1</sup> = 0 V or $V_{IN}$ = $V_{DD}$ | —                     | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | $OV_{DD} = min,$<br>$I_{OH} = -2mA$                | OV <sub>DD</sub> -0.2 | _                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | OV <sub>DD</sub> = min, I <sub>OL</sub> = 2mA      | —                     | 0.2                    | V    |

### Table 29. Local Bus DC Electrical Characteristics

### Note:

1. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

```

Local Bus

```

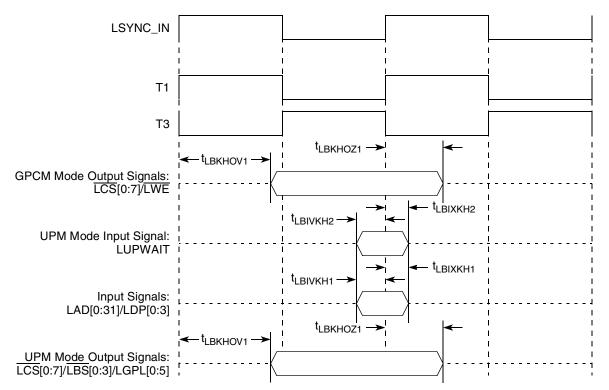

Figure 19. Local Bus Signals, GPCM/UPM Signals for LCCR[CLKDIV] = 2 (DLL Enabled)

The following two tables are examples of I2C AC parameters at I2C clock value of 100k and 400k respectively.

| Characteristic                      | Expression         | Frequenc | Unit |     |

|-------------------------------------|--------------------|----------|------|-----|

| Characteristic                      | Expression -       | Min      | Мах  |     |

| SCL clock frequency (slave)         | f <sub>SCL</sub>   | —        | 100  | kHz |

| SCL clock frequency (master)        | f <sub>SCL</sub>   | _        | 100  | kHz |

| Bus free time between transmissions | t <sub>SDHDL</sub> | 4.7      | —    | μs  |

| Low period of SCL                   | t <sub>SCLCH</sub> | 4.7      | _    | μs  |

| High period of SCL                  | t <sub>SCHCL</sub> | 4        | —    | μs  |

| Start condition setup time          | tSCHDL             | 2        | —    | μs  |

| Start condition hold time           | t <sub>SDLCL</sub> | 3        | —    | μs  |

| Data hold time                      | t <sub>SCLDX</sub> | 2        | —    | μs  |

| Data setup time                     | t <sub>SDVCH</sub> | 3        | —    | μs  |

| SDA/SCL rise time                   | t <sub>SRISE</sub> | —        | 1    | μs  |

| SDA/SCL fall time (master)          | t <sub>SFALL</sub> | —        | 303  | ns  |

| Stop condition setup time           | t <sub>SCHDH</sub> | 2        | —    | μs  |

## Table 36. CPM I2C Timing (f<sub>SCL</sub>=100 kHz)

### Table 37. CPM I2C Timing (f<sub>SCL</sub>=400 kHz)

| Characteristic                      | Expression         | Frequenc | Unit |      |

|-------------------------------------|--------------------|----------|------|------|

| Characteristic                      | Expression         | Min      | Max  | Unit |

| SCL clock frequency (slave)         | f <sub>SCL</sub>   | —        | 400  | kHz  |

| SCL clock frequency (master)        | f <sub>SCL</sub>   | —        | 400  | kHz  |

| Bus free time between transmissions | t <sub>SDHDL</sub> | 1.2      | —    | μs   |

| Low period of SCL                   | t <sub>SCLCH</sub> | 1.2      | —    | μs   |

| High period of SCL                  | t <sub>SCHCL</sub> | 1        | —    | μs   |

| Start condition setup time          | t <sub>SCHDL</sub> | 420      | _    | ns   |

| Start condition hold time           | t <sub>SDLCL</sub> | 630      | —    | ns   |

| Data hold time                      | t <sub>SCLDX</sub> | 420      | —    | ns   |

| Data setup time                     | t <sub>SDVCH</sub> | 630      | _    | ns   |

| SDA/SCL rise time                   | t <sub>SRISE</sub> | _        | 250  | ns   |

| SDA/SCL fall time                   | t <sub>SFALL</sub> | _        | 75   | ns   |

| Stop condition setup time           | t <sub>SCHDH</sub> | 420      | —    | ns   |

Figure 16 provides the AC test load for the  $I^2C$ .

Figure 37. I<sup>2</sup>C AC Test Load

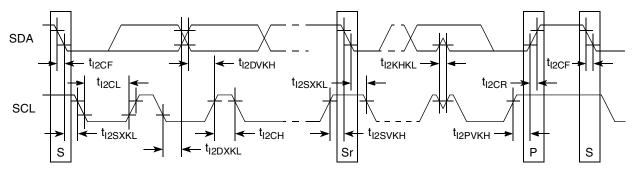

Figure 38 shows the AC timing diagram for the  $I^2C$  bus.

Figure 38. I<sup>2</sup>C Bus AC Timing Diagram

# 13 PCI

This section describes the DC and AC electrical specifications for the PCI bus of the MPC8555E.

## **13.1 PCI DC Electrical Characteristics**

Table 41 provides the DC electrical characteristics for the PCI interface of the MPC8555E.

| Parameter                 | Symbol          | Test Condition                               | Min                    | Мах                    | Unit |

|---------------------------|-----------------|----------------------------------------------|------------------------|------------------------|------|

| High-level input voltage  | V <sub>IH</sub> | $V_{OUT} \ge V_{OH}$ (min) or                | 2                      | OV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage   | V <sub>IL</sub> | V <sub>OUT</sub> ≤ V <sub>OL</sub> (max)     | -0.3                   | 0.8                    | V    |

| Input current             | I <sub>IN</sub> | $V_{IN}^2 = 0 V \text{ or } V_{IN} = V_{DD}$ | —                      | ±5                     | μA   |

| High-level output voltage | V <sub>OH</sub> | $OV_{DD} = min,$<br>$I_{OH} = -100 \ \mu A$  | OV <sub>DD</sub> – 0.2 | —                      | V    |

| Low-level output voltage  | V <sub>OL</sub> | $OV_{DD}$ = min,<br>I <sub>OL</sub> = 100 µA | —                      | 0.2                    | V    |

Table 41. PCI DC Electrical Characteristics <sup>1</sup>

### Notes:

1. Ranges listed do not meet the full range of the DC specifications of the PCI 2.2 Local Bus Specifications.

2. Note that the symbol  $V_{IN}$ , in this case, represents the  $OV_{IN}$  symbol referenced in Table 1 and Table 2.

Package and Pin Listings

| Signal           | Package Pin Number                             | Pin Type | Power<br>Supply    | Notes    |

|------------------|------------------------------------------------|----------|--------------------|----------|

| IRQ[0:7]         | AA18, Y18, AB18, AG24, AA21, Y19, AA19, AG25   | I        | OV <sub>DD</sub>   | —        |

| IRQ8             | AB20                                           | I        | OV <sub>DD</sub>   | 9        |

| IRQ9/DMA_DREQ3   | Y20                                            | I        | OV <sub>DD</sub>   | 1        |

| IRQ10/DMA_DACK3  | AF26                                           | I/O      | OV <sub>DD</sub>   | 1        |

| IRQ11/DMA_DDONE3 | AH24                                           | I/O      | OV <sub>DD</sub>   | 1        |

| IRQ_OUT          | AB21                                           | 0        | OV <sub>DD</sub>   | 2, 4     |

|                  | Ethernet Management Interface                  |          | 1                  |          |

| EC_MDC           | F1                                             | 0        | OV <sub>DD</sub>   | 5, 9     |

| EC_MDIO          | E1                                             | I/O      | OV <sub>DD</sub>   | _        |

|                  | Gigabit Reference Clock                        |          | 1                  |          |

| EC_GTX_CLK125    | E2                                             | I        | LV <sub>DD</sub>   | _        |

|                  | Three-Speed Ethernet Controller (Gigabit Ether | net 1)   | 1                  |          |

| TSEC1_TXD[7:4]   | A6, F7, D7, C7                                 | 0        | LV <sub>DD</sub>   | _        |

| TSEC1_TXD[3:0]   | B7, A7, G8, E8                                 | 0        | LV <sub>DD</sub>   | 9, 18    |

| TSEC1_TX_EN      | C8                                             | 0        | LV <sub>DD</sub>   | 11       |

| TSEC1_TX_ER      | B8                                             | 0        | LV <sub>DD</sub>   | —        |

| TSEC1_TX_CLK     | C6                                             | I        | LV <sub>DD</sub>   | —        |

| TSEC1_GTX_CLK    | B6                                             | 0        | LV <sub>DD</sub>   | —        |

| TSEC1_CRS        | C3                                             | I        | LV <sub>DD</sub>   | —        |

| TSEC1_COL        | G7                                             | I        | LV <sub>DD</sub>   | —        |

| TSEC1_RXD[7:0]   | D4, B4, D3, D5, B5, A5, F6, E6                 | I        | LV <sub>DD</sub>   | _        |

| TSEC1_RX_DV      | D2                                             | I        | LV <sub>DD</sub>   | _        |

| TSEC1_RX_ER      | E5                                             | I        | LV <sub>DD</sub>   | —        |

| TSEC1_RX_CLK     | D6                                             | I        | LV <sub>DD</sub>   | —        |

|                  | Three-Speed Ethernet Controller (Gigabit Ether | net 2)   |                    |          |

| TSEC2_TXD[7:4]   | B10, A10, J10, K11                             | 0        | LV <sub>DD</sub>   | _        |

| TSEC2_TXD[3:0]   | J11, H11, G11, E11                             | 0        | LV <sub>DD</sub>   | 5, 9, 18 |

| TSEC2_TX_EN      | B11                                            | 0        | LV <sub>DD</sub>   | 11       |

| TSEC2_TX_ER      | D11                                            | 0        | LV <sub>DD</sub> — |          |

| TSEC2_TX_CLK     | D10                                            | I        | LV <sub>DD</sub>   | —        |

| TSEC2_GTX_CLK    | C10                                            | 0        | LV <sub>DD</sub>   | —        |

#### Package and Pin Listings

#### Table 43. MPC8555E Pinout Listing (continued)

| Signal              | Package Pin Number                                                                                                    | Pin Type | Power<br>Supply  | Notes |

|---------------------|-----------------------------------------------------------------------------------------------------------------------|----------|------------------|-------|

| PB[18:31]           | P7, P6, P5, P4, P3, P2, P1, R1, R2, R3, R4, R5, R6,<br>R7                                                             | I/O      | OV <sub>DD</sub> | —     |

| PC[0, 1, 4–29]      | R8, R9, T9, T6, T5, T4, T1, U1, U2, U3, U4, U7, U8,<br>U9, U10, V9, V6, V5, V4, V3, V2, V1, W1, W2, W3,<br>W6, W7, W8 | I/O      | OV <sub>DD</sub> | —     |

| PD[7, 14–25, 29–31] | Y4, AA2, AA1, AB1, AB2, AB3, AB5, AB6, AC7, AC4, AC3, AC2, AC1, AD6, AE3, AE2                                         | Ι/Ο      | OV <sub>DD</sub> | —     |

Notes:

- 1. All multiplexed signals are listed only once and do not re-occur. For example, LCS5/DMA\_REQ2 is listed only once in the Local Bus Controller Interface section, and is not mentioned in the DMA section even though the pin also functions as DMA\_REQ2.

- 2. Recommend a weak pull-up resistor (2–10 k $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 3. TEST\_SEL0 must be pulled-high, TEST\_SEL1 must be tied to ground.

- 4. This pin is an open drain signal.

- 5. This pin is a reset configuration pin. It has a weak internal pull-up P-FET which is enabled only when the MPC8555E is in the reset state. This pull-up is designed such that it can be overpowered by an external 4.7-kΩ pull-down resistor. If an external device connected to this pin might pull it down during reset, then a pull-up or active driver is needed if the signal is intended to be high during reset.

- 6. Treat these pins as no connects (NC) unless using debug address functionality.

- The value of LA[28:31] during reset sets the CCB clock to SYSCLK PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See Section 15.2, "Platform/System PLL Ratio."

- The value of LALE and LGPL2 at reset set the e500 core clock to CCB Clock PLL ratio. These pins require 4.7-kΩ pull-up or pull-down resistors. See the Section 15.3, "e500 Core PLL Ratio."

- 9. Functionally, this pin is an output, but structurally it is an I/O because it either samples configuration input during reset or because it has other manufacturing test functions. This pin therefore is described as an I/O for boundary scan.

- This pin functionally requires a pull-up resistor, but during reset it is a configuration input that controls 32- vs. 64-bit PCI operation. Therefore, it must be actively driven low during reset by reset logic if the device is to be configured to be a 64-bit PCI device. Refer to the PCI Specification.

- 11. This output is actively driven during reset rather than being three-stated during reset.

- 12. These JTAG pins have weak internal pull-up P-FETs that are always enabled.

- 13. These pins are connected to the V<sub>DD</sub>/GND planes internally and may be used by the core power supply to improve tracking and regulation.

- 14. Internal thermally sensitive resistor.

- 15. No connections should be made to these pins.

- 16. These pins are not connected for any functional use.

- PCI specifications recommend that a weak pull-up resistor (2–10 kΩ) be placed on the higher order pins to OV<sub>DD</sub> when using 64-bit buffer mode (pins PCI\_AD[63:32] and PCI2\_C\_BE[7:4]).

- 18. If this pin is connected to a device that pulls down during reset, an external pull-up is required to that is strong enough to pull this signal to a logic 1 during reset.

- 19. Recommend a pull-up resistor (~1 k $\Omega$ ) be placed on this pin to OV<sub>DD</sub>.

- 20. These are test signals for factory use only and must be pulled up (100 $\Omega$  to 1k $\Omega$ ) to OV<sub>DD</sub> for normal machine operation.

- 21. If this signal is used as both an input and an output, a weak pull-up ( $\sim 10 k\Omega$ ) is required on this pin.

- 22. MSYNC\_IN and MSYNC\_OUT should be connected together for proper operation.

# 15 Clocking

This section describes the PLL configuration of the MPC8555E. Note that the platform clock is identical to the CCB clock.

## 15.1 Clock Ranges

Table 44 provides the clocking specifications for the processor core and Table 44 provides the clocking specifications for the memory bus.

|                                     | Maximum Processor Core Frequency |     |     |     |     |     |     |     |      |       |      |         |

|-------------------------------------|----------------------------------|-----|-----|-----|-----|-----|-----|-----|------|-------|------|---------|

| Characteristic                      | 533                              | MHz | 600 | MHz | 667 | MHz | 833 | MHz | 1000 | ) MHz | Unit | Notes   |

|                                     | Min                              | Max | Min | Max | Min | Max | Min | Max | Min  | Max   |      |         |

| e500 core<br>processor<br>frequency | 400                              | 533 | 400 | 600 | 400 | 667 | 400 | 833 | 400  | 1000  | MHz  | 1, 2, 3 |

**Table 44. Processor Core Clocking Specifications**

Notes:

1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

2.) The minimum e500 core frequency is based on the minimum platform frequency of 200 MHz.

3. 1000 MHz frequency supports only a 1.3 V core.

### Table 45. Memory Bus Clocking Specifications

| Characteristic       | Maximum Pro<br>Frequ<br>533, 600, 667, | Unit | Notes |         |

|----------------------|----------------------------------------|------|-------|---------|

|                      | Min                                    | Max  |       |         |

| Memory bus frequency | 100                                    | 166  | MHz   | 1, 2, 3 |

Notes:

- 1. **Caution:** The CCB to SYSCLK ratio and e500 core to CCB ratio settings must be chosen such that the resulting SYSCLK frequency, e500 (core) frequency, and CCB frequency do not exceed their respective maximum or minimum operating frequencies. Refer to Section 15.2, "Platform/System PLL Ratio," and Section 15.3, "e500 Core PLL Ratio," for ratio settings.

- 2. The memory bus speed is half of the DDR data rate, hence, half of the platform clock frequency.

- 3. 1000 MHz frequency supports only a 1.3 V core.

Chanhassen, MN 55317 Internet: www.bergquistcompany.com Thermagon Inc. 4707 Detroit Ave. Cleveland, OH 44102 Internet: www.thermagon.com

888-246-9050

## 16.2.4 Heat Sink Selection Examples

The following section provides a heat sink selection example using one of the commercially available heat sinks.

## 16.2.4.1 Case 1

For preliminary heat sink sizing, the die-junction temperature can be expressed as follows:

$$T_J = T_I + T_R + (\theta_{JC} + \theta_{INT} + \theta_{SA}) \times P_D$$

where

$T_J$  is the die-junction temperature

T<sub>I</sub> is the inlet cabinet ambient temperature

$T_R$  is the air temperature rise within the computer cabinet

$\theta_{IC}$  is the junction-to-case thermal resistance

$\theta_{INT}$  is the adhesive or interface material thermal resistance

$\theta_{SA}$  is the heat sink base-to-ambient thermal resistance

$P_D$  is the power dissipated by the device. See Table 4 and Table 5.

During operation the die-junction temperatures  $(T_J)$  should be maintained within the range specified in Table 2. The temperature of air cooling the component greatly depends on the ambient inlet air temperature and the air temperature rise within the electronic cabinet. An electronic cabinet inlet-air temperature  $(T_A)$  may range from 30° to 40°C. The air temperature rise within a cabinet  $(T_R)$  may be in the range of 5° to 10°C. The thermal resistance of some thermal interface material ( $\theta_{INT}$ ) may be about 1°C/W. For the purposes of this example, the  $\theta_{JC}$  value given in Table 49 that includes the thermal grease interface and is documented in note 4 is used. If a thermal pad is used,  $\theta_{INT}$  must be added.

Assuming a T<sub>I</sub> of 30°C, a T<sub>R</sub> of 5°C, a FC-PBGA package  $\theta_{JC} = 0.96$ , and a power consumption (P<sub>D</sub>) of 8.0 W, the following expression for T<sub>J</sub> is obtained:

Die-junction temperature:  $T_J = 30^{\circ}C + 5^{\circ}C + (0.96^{\circ}C/W + \theta_{SA}) \times 8.0 W$

The heat sink-to-ambient thermal resistance ( $\theta_{SA}$ ) versus airflow velocity for a Thermalloy heat sink #2328B is shown in Figure 47.

Assuming an air velocity of 2 m/s, we have an effective  $\theta_{SA+}$  of about 3.3°C/W, thus

$T_{\rm J} = 30^{\circ}\text{C} + 5^{\circ}\text{C} + (0.96^{\circ}\text{C/W} + 3.3^{\circ}\text{C/W}) \times 8.0 \text{ W},$

resulting in a die-junction temperature of approximately 69°C which is well within the maximum operating temperature of the component.

# NP

#### System Design Information

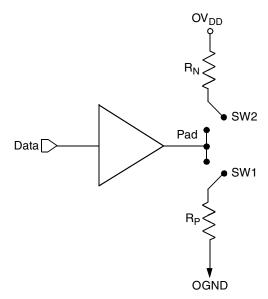

When data is held high, SW1 is closed (SW2 is open) and  $R_P$  is trimmed until the voltage at the pad equals  $OV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

Figure 51. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = 1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

Table 50 summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal  $OV_{DD}$ , 105°C.

| Impedance      | Local Bus, Ethernet, DUART, Control, Configuration, Power<br>Management | PCI       | DDR DRAM  | Symbol            | Unit |

|----------------|-------------------------------------------------------------------------|-----------|-----------|-------------------|------|

| R <sub>N</sub> | 43 Target                                                               | 25 Target | 20 Target | Z <sub>0</sub>    | Ω    |

| R <sub>P</sub> | 43 Target                                                               | 25 Target | 20 Target | Z <sub>0</sub>    | Ω    |

| Differential   | ΝΑ                                                                      | NA        | NA        | Z <sub>DIFF</sub> | Ω    |

| Table 50 | . Impedance | Characteristics |

|----------|-------------|-----------------|

|----------|-------------|-----------------|

Note: Nominal supply voltages. See Table 1,  $T_i = 105^{\circ}C$ .

## 17.8.1 Termination of Unused Signals

If the JTAG interface and COP header are not used, Freescale recommends the following connections:

- TRST should be tied to HRESET through a 0 k $\Omega$  isolation resistor so that it is asserted when the system reset signal (HRESET) is asserted, ensuring that the JTAG scan chain is initialized during the power-on reset flow. Freescale recommends that the COP header be designed into the system as shown in Figure 53. If this is not possible, the isolation resistor allows future access to TRST in case a JTAG interface may need to be wired onto the system in future debug situations.

- Tie TCK to  $OV_{DD}$  through a 10 k $\Omega$  resistor. This prevents TCK from changing state and reading incorrect data into the device.

- No connection is required for TDI, TMS, or TDO.

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 +1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 +1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale<sup>™</sup> and the Freescale logo are trademarks of Freescale Semiconductor, Inc. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org. The described product contains a PowerPC processor core. The PowerPC name is a trademark of IBM Corp. and used under license. IEEE 802.3 and 1149.1 are registered trademarks of the Institute of Electrical and Electronics Engineers, Inc. (IEEE). This product is not endorsed or approved by the IEEE. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc., 2008. All rights reserved.

Document Number: MPC8555EEC Rev. 4.2 1/2008