Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | M8C                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 24MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 24                                                                         |

| Program Memory Size        | 4KB (4K x 8)                                                               |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                 |

| Data Converters            | A/D 2x14b; D/A 2x9b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                                             |

| Supplier Device Package    | 28-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c24423-24sit |

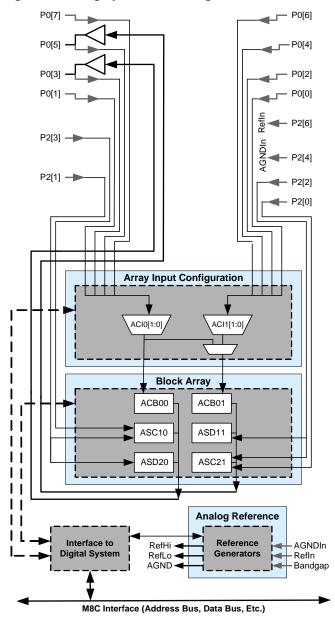

#### **Analog System**

The Analog System is composed of six configurable blocks, each comprised of an opamp circuit allowing the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- Analog-to-digital converters (up to two, with 6 to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR)

- Filters (two and four pole band-pass, low-pass, and notch)

- Amplifiers (up to two, with selectable gain to 48x)

- Instrumentation amplifiers (one with selectable gain to 93x)

- Comparators (up to two, with 16 selectable thresholds)

- DACs (up to two, with 6 to 9-bit resolution)

- Multiplying DACs (up to two, with 6- to 9-bit resolution)

- High current output drivers (two with 30 mA drive as a Core Resource)

- 1.3V reference (as a System Resource)

- DTMF dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are provided in columns of three, which includes one CT (Continuous Time) and two SC (Switched Capacitor) blocks. The number of blocks is dependant on the device family which is detailed in the table PSoC Device Characteristics on page 4.

Figure 2. Analog System Block Diagram

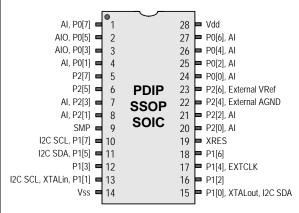

## 28-Pin Part Pinout

Table 5. 28-Pin Part Pinout (PDIP, SSOP, SOIC)

| Pin | Ту      | ре     | Pin   | 5                                                                 |

|-----|---------|--------|-------|-------------------------------------------------------------------|

| No. | Digital | Analog | Name  | Description                                                       |

| 1   | Ю       | I      | P0[7] | Analog column mux input                                           |

| 2   | Ю       | Ю      | P0[5] | Analog column mux input and column output                         |

| 3   | Ю       | 0      | P0[3] | Analog column mux input and column output                         |

| 4   | Ю       | -      | P0[1] | Analog column mux input.                                          |

| 5   | Ю       |        | P2[7] |                                                                   |

| 6   | Ю       |        | P2[5] |                                                                   |

| 7   | Ю       | ı      | P2[3] | Direct switched capacitor block input                             |

| 8   | Ю       | ı      | P2[1] | Direct switched capacitor block input                             |

| 9   | Pov     | wer    | SMP   | Switch Mode Pump (SMP) connection to external components required |

| 10  | Ю       |        | P1[7] | I2C Serial Clock (SCL)                                            |

| 11  | Ю       |        | P1[5] | I2C Serial Data (SDA)                                             |

| 12  | Ю       |        | P1[3] |                                                                   |

| 13  | Ю       |        | P1[1] | Crystal Input (XTALin), I2C Serial Clock (SCL)                    |

| 14  | Pov     | wer    | Vss   | Ground connection                                                 |

| 15  | Ю       |        | P1[0] | Crystal Output (XTALout), I2C Serial Data (SDA)                   |

| 16  | Ю       |        | P1[2] |                                                                   |

| 17  | Ю       |        | P1[4] | Optional External Clock Input (EXTCLK)                            |

| 18  | Ю       |        | P1[6] |                                                                   |

| 19  | Inp     | out    | XRES  | Active high external reset with internal pull down                |

| 20  | Ю       | ı      | P2[0] | Direct switched capacitor block input                             |

| 21  | Ю       | I      | P2[2] | Direct switched capacitor block input                             |

| 22  | Ю       |        | P2[4] | External Analog Ground (AGND)                                     |

| 23  | Ю       |        | P2[6] | External Voltage Reference (VRef)                                 |

| 24  | Ю       | I      | P0[0] | Analog column mux input                                           |

| 25  | Ю       | I      | P0[2] | Analog column mux input                                           |

| 26  | Ю       | I      | P0[4] | Analog column mux input                                           |

| 27  | Ю       | I      | P0[6] | Analog column mux input                                           |

| 28  | Pov     | wer    | Vdd   | Supply voltage                                                    |

Figure 8. CY8C24423 28-Pin PSoC Device

$\textbf{LEGEND} \hbox{: A = Analog, I = Input, and O = Output.}$

Document Number: 38-12011 Rev. \*G Page 9 of 43

## **Register Reference**

This section lists the registers of the CY8C27xxx PSoC device by way of mapping tables, in offset order. For detailed register information, reference the PSoC Programmable System-on-Chip Technical Reference Manual.

#### **Register Conventions**

Abbreviations Used

The register conventions specific to this section are listed in the following table.

Table 7. Abbreviations

| Convention | Description                       |

|------------|-----------------------------------|

| RW         | Read and write register or bit(s) |

| R          | Read register or bit(s)           |

| W          | Write register or bit(s)          |

| L          | Logical register or bit(s)        |

| С          | Clearable register or bit(s)      |

| #          | Access is bit specific            |

# **Register Mapping Tables**

The PSoC device has a total register address space of 512 bytes. The register space is also referred to as IO space and is broken into two parts. The XOI bit in the Flag register determines which bank the user is currently in. When the XOI bit is set, the user is said to be in the "extended" address space or the "configuration" registers.

**Note** In the following register mapping tables, blank fields are Reserved and must not be accessed.

Document Number: 38-12011 Rev. \*G Page 11 of 43

Table 8. Register Map Bank 0 Table: User Space (continued)

| Name     | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access | Name    | Addr<br>(0,Hex) | Access | Name     | Addr<br>(0,Hex) | Access |

|----------|-----------------|--------|----------|-----------------|--------|---------|-----------------|--------|----------|-----------------|--------|

| DCB03DR2 | 2E              | RW     |          | 6E              |        |         | AE              |        | ACC_DR3  | EE              | RW     |

| DCB03CR0 | 2F              | #      |          | 6F              |        |         | AF              |        | ACC_DR2  | EF              | RW     |

|          | 30              |        | ACB00CR3 | 70              | RW     | RDI0RI  | В0              | RW     |          | F0              |        |

|          | 31              |        | ACB00CR0 | 71              | RW     | RDI0SYN | B1              | RW     |          | F1              |        |

|          | 32              |        | ACB00CR1 | 72              | RW     | RDI0IS  | B2 RW           |        |          | F2              |        |

|          | 33              |        | ACB00CR2 | 73              | RW     | RDI0LT0 | В3              | RW     |          | F3              |        |

|          | 34              |        | ACB01CR3 | 74              | RW     | RDIOLT1 | B4              | RW     |          | F4              |        |

|          | 35              |        | ACB01CR0 | 75              | RW     | RDI0RO0 | B5              | RW     |          | F5              |        |

|          | 36              |        | ACB01CR1 | 76              | RW     | RDI0RO1 | B6              | RW     |          | F6              |        |

|          | 37              |        | ACB01CR2 | 77              | RW     |         | В7              |        | CPU_F    | F7              | RL     |

|          | 38              |        |          | 78              |        |         | B8              |        |          | F8              |        |

|          | 39              |        |          | 79              |        |         | В9              |        |          | F9              |        |

|          | ЗА              |        |          | 7A              |        |         | ВА              |        |          | FA              |        |

|          | 3B              |        |          | 7B              |        |         | BB              |        |          | FB              |        |

|          | 3C              |        |          | 7C              |        |         | ВС              |        |          | FC              |        |

|          | 3D              |        |          | 7D              |        |         | BD              |        |          | FD              |        |

|          | 3E              |        |          | 7E              |        |         | BE              |        | CPU_SCR1 | FE              | #      |

|          | 3F              |        |          | 7F              |        |         | BF              |        | CPU_SCR0 | FF              | #      |

Blank fields are Reserved and must not be accessed.

# Access is bit specific.

Table 9. Register Map Bank 1 Table: Configuration Space

| Name    | Addr<br>(1, Hex) | Access | Name | Addr<br>(1,Hex) | Access | Name     | Addr<br>(1, Hex) | Access | Name     | Addr<br>(1,Hex) | Access |

|---------|------------------|--------|------|-----------------|--------|----------|------------------|--------|----------|-----------------|--------|

| PRT0DM0 | 00               | RW     | Z    | 40              | ۹.     | ASC10CR0 | 80               | RW     | Z        | C0              | 4      |

| PRT0DM1 | 01               | RW     |      | 41              |        | ASC10CR1 | 81               | RW     |          | C1              | †      |

| PRT0IC0 | 02               | RW     |      | 42              |        | ASC10CR2 | 82               | RW     |          | C2              |        |

| PRT0IC1 | 03               | RW     |      | 43              |        | ASC10CR3 | 83               | RW     |          | C3              |        |

| PRT1DM0 | 04               | RW     |      | 44              |        | ASD11CR0 | 84               | RW     |          | C4              |        |

| PRT1DM1 | 05               | RW     |      | 45              |        | ASD11CR1 | 85               | RW     |          | C5              |        |

| PRT1IC0 | 06               | RW     |      | 46              |        | ASD11CR2 | 86               | RW     |          | C6              |        |

| PRT1IC1 | 07               | RW     |      | 47              |        | ASD11CR3 | 87               | RW     |          | C7              |        |

| PRT2DM0 | 08               | RW     |      | 48              |        |          | 88               |        |          | C8              |        |

| PRT2DM1 | 09               | RW     |      | 49              |        |          | 89               |        |          | C9              |        |

| PRT2IC0 | 0A               | RW     |      | 4A              |        |          | 8A               |        |          | CA              |        |

| PRT2IC1 | 0B               | RW     |      | 4B              |        |          | 8B               |        |          | СВ              |        |

|         | 0C               |        |      | 4C              |        |          | 8C               |        |          | СС              |        |

|         | 0D               |        |      | 4D              |        |          | 8D               |        |          | CD              |        |

|         | 0E               |        |      | 4E              |        |          | 8E               |        |          | CE              |        |

|         | 0F               |        |      | 4F              |        |          | 8F               |        |          | CF              |        |

|         | 10               |        |      | 50              |        | ASD20CR0 | 90               | RW     | GDI_O_IN | D0              | RW     |

|         | 11               |        |      | 51              |        | ASD20CR1 | 91               | RW     | GDI_E_IN | D1              | RW     |

|         | 12               |        |      | 52              |        | ASD20CR2 | 92               | RW     | GDI_O_OU | D2              | RW     |

|         | 13               |        |      | 53              |        | ASD20CR3 | 93               | RW     | GDI_E_OU | D3              | RW     |

|         | 14               |        |      | 54              |        | ASC21CR0 | 94               | RW     |          | D4              |        |

|         | 15               |        |      | 55              |        | ASC21CR1 | 95               | RW     |          | D5              |        |

|         | 16               |        |      | 56              |        | ASC21CR2 | 96               | RW     |          | D6              |        |

Blank fields are Reserved and must not be accessed.

# Access is bit specific.

Document Number: 38-12011 Rev. \*G

Table 9. Register Map Bank 1 Table: Configuration Space (continued)

| Name    | Addr<br>(1,Hex) | Access | Name     | Addr<br>(1,Hex) | Access | Name     | Addr<br>(1,Hex) | Access | Name      | Addr<br>(1,Hex) | Access |

|---------|-----------------|--------|----------|-----------------|--------|----------|-----------------|--------|-----------|-----------------|--------|

|         | 17              |        |          | 57              |        | ASC21CR3 | 97              | RW     |           | D7              |        |

|         | 18              |        |          | 58              |        |          | 98              |        |           | D8              |        |

|         | 19              |        |          | 59              |        |          | 99              |        |           | D9              |        |

|         | 1A              |        |          | 5A              |        |          | 9A              |        |           | DA              |        |

|         | 1B              |        |          | 5B              |        |          | 9B              |        |           | DB              |        |

|         | 1C              |        |          | 5C              |        |          | 9C              |        |           | DC              |        |

|         | 1D              |        |          | 5D              |        |          | 9D              |        | OSC_GO_EN | DD              | RW     |

|         | 1E              |        |          | 5E              |        |          | 9E              |        | OSC_CR4   | DE              | RW     |

|         | 1F              |        |          | 5F              |        |          | 9F              |        | OSC_CR3   | DF              | RW     |

| DBB00FN | 20              | RW     | CLK_CR0  | 60              | RW     |          | A0              |        | OSC_CR0   | E0              | RW     |

| DBB00IN | 21              | RW     | CLK_CR1  | 61              | RW     |          | A1              |        | OSC_CR1   | E1              | RW     |

| DBB00OU | 22              | RW     | ABF_CR0  | 62              | RW     |          | A2              |        | OSC_CR2   | E2              | RW     |

|         | 23              |        | AMD_CR0  | 63              | RW     |          | А3              |        | VLT_CR    | E3              | RW     |

| DBB01FN | 24              | RW     |          | 64              |        |          | A4              |        | VLT_CMP   | E4              | R      |

| DBB01IN | 25              | RW     |          | 65              |        |          | A5              |        |           | E5              |        |

| DBB01OU | 26              | RW     | AMD_CR1  | 66              | RW     |          | A6              |        |           | E6              |        |

|         | 27              |        | ALT_CR0  | 67              | RW     |          | A7              |        |           | E7              |        |

| DCB02FN | 28              | RW     |          | 68              |        |          | A8              |        | IMO_TR    | E8              | W      |

| DCB02IN | 29              | RW     |          | 69              |        |          | A9              |        | ILO_TR    | E9              | W      |

| DCB02OU | 2A              | RW     |          | 6A              |        |          | AA              |        | BDG_TR    | EA              | RW     |

|         | 2B              |        |          | 6B              |        |          | AB              |        | ECO_TR    | EB              | W      |

| DCB03FN | 2C              | RW     |          | 6C              |        |          | AC              |        |           | EC              |        |

| DCB03IN | 2D              | RW     |          | 6D              |        |          | AD              |        |           | ED              |        |

| DCB03OU | 2E              | RW     |          | 6E              |        |          | AE              |        |           | EE              |        |

|         | 2F              |        |          | 6F              |        |          | AF              |        |           | EF              |        |

|         | 30              |        | ACB00CR3 | 70              | RW     | RDI0RI   | В0              | RW     |           | F0              |        |

|         | 31              |        | ACB00CR0 | 71              | RW     | RDI0SYN  | B1              | RW     |           | F1              |        |

|         | 32              |        | ACB00CR1 | 72              | RW     | RDI0IS   | B2              | RW     |           | F2              |        |

|         | 33              |        | ACB00CR2 | 73              | RW     | RDI0LT0  | В3              | RW     |           | F3              |        |

|         | 34              |        | ACB01CR3 | 74              | RW     | RDIOLT1  | B4              | RW     |           | F4              |        |

|         | 35              |        | ACB01CR0 | 75              | RW     | RDI0RO0  | B5              | RW     |           | F5              |        |

|         | 36              |        | ACB01CR1 | 76              | RW     | RDI0RO1  | B6              | RW     |           | F6              |        |

|         | 37              |        | ACB01CR2 | 77              | RW     |          | В7              |        | CPU_F     | F7              | RL     |

|         | 38              |        |          | 78              |        |          | B8              |        |           | F8              |        |

|         | 39              |        |          | 79              |        |          | В9              |        |           | F9              |        |

|         | 3A              |        |          | 7A              |        |          | ВА              |        |           | FA              |        |

|         | 3B              |        |          | 7B              |        |          | ВВ              |        |           | FB              |        |

|         | 3C              |        |          | 7C              |        |          | ВС              |        |           | FC              |        |

|         | 3D              |        |          | 7D              |        |          | BD              |        |           | FD              |        |

|         | 3E              |        |          | 7E              |        |          | BE              |        | CPU_SCR1  | FE              | #      |

|         | 3F              | İ      |          | 7F              |        |          | BF              |        | CPU_SCR0  | FF              | #      |

Blank fields are Reserved and must not  $\overline{\text{be accessed.}}$

# Access is bit specific.

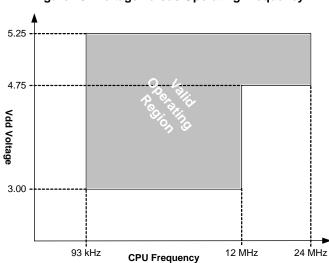

# **Electrical Specifications**

This section presents the DC and AC electrical specifications of the CY8C24x23 PSoC device. For latest electrical specifications, http://www.cypress.com.

Specifications are valid for -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C and T<sub>J</sub>  $\leq$  100°C, except where noted. Specifications for devices running at greater than 12 MHz are valid for -40°C  $\leq$  T<sub>A</sub>  $\leq$  70°C and T<sub>J</sub>  $\leq$  82°C.

Figure 10. Voltage versus Operating Frequency

The following table lists the units of measure that are used in this section.

Table 10. Units of Measure

| Symbol | Unit of Measure              | Symbol | Unit of Measure               |

|--------|------------------------------|--------|-------------------------------|

| °C     | degree Celsius               | μW     | micro watts                   |

| dB     | decibels                     | mA     | milli-ampere                  |

| fF     | femto farad                  | ms     | milli-second                  |

| Hz     | hertz                        | mV     | milli-volts                   |

| KB     | 1024 bytes                   | nA     | nano ampere                   |

| Kbit   | 1024 bits                    | ns     | nanosecond                    |

| kHz    | kilohertz                    | nV     | nanovolts                     |

| kΩ     | kilohm                       | W      | ohm                           |

| MHz    | megahertz                    | рА     | pico ampere                   |

| ΜΩ     | megaohm                      | pF     | pico farad                    |

| μΑ     | micro ampere                 | рр     | peak-to-peak                  |

| μF     | micro farad                  | ppm    | parts per million             |

| μН     | micro henry                  | ps     | picosecond                    |

| μS     | microsecond                  | sps    | samples per second            |

| μV     | micro volts                  | S      | sigma: one standard deviation |

| μVrms  | micro volts root-mean-square | V      | volts                         |

Document Number: 38-12011 Rev. \*G Page 15 of 43

# **Absolute Maximum Ratings**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

**Table 11. Absolute Maximum Ratings**

| Symbol            | Description                                                   | Min       | Тур | Max       | Units | Notes                                                   |

|-------------------|---------------------------------------------------------------|-----------|-----|-----------|-------|---------------------------------------------------------|

| T <sub>STG</sub>  | Storage Temperature                                           | -55       | -   | +100      | °C    | Higher storage temperatures reduce data retention time. |

| T <sub>A</sub>    | Ambient Temperature with Power Applied                        | -40       | _   | +85       | °C    |                                                         |

| Vdd               | Supply Voltage on Vdd Relative to Vss                         | -0.5      | _   | +6.0      | V     |                                                         |

| V <sub>IO</sub>   | DC Input Voltage                                              | Vss - 0.5 | _   | Vdd + 0.5 | V     |                                                         |

| _                 | DC Voltage Applied to Tri-state                               | Vss - 0.5 | -   | Vdd + 0.5 | V     |                                                         |

| I <sub>MIO</sub>  | Maximum Current into any Port Pin                             | -25       | _   | +50       | mA    |                                                         |

| I <sub>MAIO</sub> | Maximum Current into any Port Pin Configured as Analog Driver | -50       | -   | +50       | mA    |                                                         |

| _                 | Static Discharge Voltage                                      | 2000      | _   | _         | V     |                                                         |

| _                 | Latch-up Current                                              | _         | -   | 200       | mΑ    |                                                         |

# **Operating Temperature**

# **Table 12. Operating Temperature**

| Symbol         | Description          | Min | Тур | Max  | Units | Notes                                                                                                                                                                                        |

|----------------|----------------------|-----|-----|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>A</sub> | Ambient Temperature  | -40 | _   | +85  | °С    |                                                                                                                                                                                              |

| TJ             | Junction Temperature | -40 | 1   | +100 | °C    | The temperature rise from ambient to junction is package specific. See Thermal Impedances per Package on page 41. The user must limit the power consumption to comply with this requirement. |

Document Number: 38-12011 Rev. \*G Page 16 of 43

**Table 15. 5V DC Operational Amplifier Specifications** (continued)

| Symbol               | Description                                                                                                                                                                                | Min                                 | Тур                                       | Max                                       | Units                            | Notes                                                                                                                       |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| G <sub>OLOA</sub>    | Open Loop Gain<br>Power = Low<br>Power = Medium<br>Power = High                                                                                                                            | 60<br>60<br>80                      | -                                         | -                                         | dB                               | Specification is applicable at high power. For all other bias modes (except high power, high opamp bias), minimum is 60 dB. |

| V <sub>OHIGHOA</sub> | High Output Voltage Swing (worst case internal load) Power = Low Power = Medium Power = High                                                                                               | Vdd - 0.2<br>Vdd - 0.2<br>Vdd - 0.5 | _<br>_<br>_                               | -<br>-<br>-                               | V<br>V<br>V                      |                                                                                                                             |

| V <sub>OLOWOA</sub>  | Low Output Voltage Swing (worst case internal load) Power = Low Power = Medium Power = High                                                                                                | -<br>-<br>-                         | _<br>_<br>_                               | 0.2<br>0.2<br>0.5                         | V<br>V<br>V                      |                                                                                                                             |

| Isoa                 | Supply Current (including associated AGND buffer) Power = Low Power = Low, Opamp Bias = High Power = Medium Power = Medium, Opamp Bias = High Power = High Power = High, Opamp Bias = High | -<br>-<br>-<br>-<br>-               | 150<br>300<br>600<br>1200<br>2400<br>4600 | 200<br>400<br>800<br>1600<br>3200<br>6400 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |                                                                                                                             |

| PSRR <sub>OA</sub>   | Supply Voltage Rejection Ratio                                                                                                                                                             | 60                                  | _                                         | -                                         | dB                               |                                                                                                                             |

Document Number: 38-12011 Rev. \*G Page 19 of 43

Table 16. 3.3V DC Operational Amplifier Specifications

| Symbol               | Description                                                                                                                                                                                                               | Min                                   | Тур                                       | Max                                       | Units                            | Notes                                                                                                                                                                                   |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-------------------------------------------|-------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOA</sub>    | Input Offset Voltage (absolute value) Low Power Input Offset Voltage (absolute value) Mid Power High Power is 5 Volt Only                                                                                                 | _<br>_                                | 1.65<br>1.32                              | 10<br>8                                   | mV<br>mV                         |                                                                                                                                                                                         |

| TCV <sub>OSOA</sub>  | Average Input Offset Voltage Drift                                                                                                                                                                                        | _                                     | 7.0                                       | 35.0                                      | μV/°C                            |                                                                                                                                                                                         |

| I <sub>EBOA</sub>    | Input Leakage Current (Port 0 Analog Pins)                                                                                                                                                                                | _                                     | 20                                        | _                                         | pА                               | Gross tested to 1 μA.                                                                                                                                                                   |

| C <sub>INOA</sub>    | Input Capacitance (Port 0 Analog Pins)                                                                                                                                                                                    | _                                     | 4.5                                       | 9.5                                       | pF                               | Package and pin dependent. Temp = 25°C.                                                                                                                                                 |

| V <sub>CMOA</sub>    | Common Mode Voltage Range                                                                                                                                                                                                 | 0.2                                   | _                                         | Vdd - 0.2                                 | V                                | The common-mode input voltage range is measured through an analog output buffer. The specification includes the limitations imposed by the characteristics of the analog output buffer. |

| G <sub>OLOA</sub>    | Open Loop Gain Power = Low Power = Medium Power = High                                                                                                                                                                    | 60<br>60<br>80                        | _                                         | -                                         | dB                               | Specification is applicable at high power. For all other bias modes (except high power, high opamp bias), minimum is 60 dB.                                                             |

| V <sub>OHIGHOA</sub> | High Output Voltage Swing (worst case internal load) Power = Low Power = Medium Power = High is 5V only                                                                                                                   | Vdd - 0.2<br>Vdd - 0.2<br>Vdd - 0.2   | _<br>_<br>_                               | -<br>-<br>-                               | V<br>V<br>V                      |                                                                                                                                                                                         |

| V <sub>OLOWOA</sub>  | Low Output Voltage Swing (worst case internal load) Power = Low Power = Medium Power = High                                                                                                                               | -<br>-<br>-                           | -<br>-<br>-                               | 0.2<br>0.2<br>0.2                         | V<br>V<br>V                      |                                                                                                                                                                                         |

| I <sub>SOA</sub>     | Supply Current (including associated AGND buffer) Power = Low Power = Low, Opamp Bias = High Power = Medium Power = Medium, Opamp Bias = High Power = High Power = High, Opamp Bias = High Supply Voltage Rejection Ratio | -<br>-<br>-<br>-<br>-<br>-<br>-<br>50 | 150<br>300<br>600<br>1200<br>2400<br>4600 | 200<br>400<br>800<br>1600<br>3200<br>6400 | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |                                                                                                                                                                                         |

Document Number: 38-12011 Rev. \*G Page 20 of 43

## DC Analog Output Buffer Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ , or 3.0V to 3.6V and  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ , respectively. Typical parameters apply to 5V and 3.3V at  $25^{\circ}C$  and are for design guidance only or unless otherwise specified.

Table 17. 5V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                  | Min                                | Тур        | Max                                | Units    |

|----------------------|------------------------------------------------------------------------------|------------------------------------|------------|------------------------------------|----------|

| V <sub>OSOB</sub>    | Input Offset Voltage (Absolute Value)                                        | _                                  | 3          | 12                                 | mV       |

| TCV <sub>OSOB</sub>  | Average Input Offset Voltage Drift                                           | _                                  | +6         | _                                  | μV/°C    |

| $V_{CMOB}$           | Common-Mode Input Voltage Range                                              | 0.5                                | -          | Vdd - 1.0                          | V        |

| R <sub>OUTOB</sub>   | Output Resistance Power = Low Power = High                                   |                                    | 1          | -<br>-                             | W        |

| V <sub>OHIGHOB</sub> | High Output Voltage Swing (Load = 32 ohms to Vdd/2) Power = Low Power = High | 0.5 x Vdd + 1.1<br>0.5 x Vdd + 1.1 | _<br>_     | _<br>_                             | V        |

| V <sub>OLOWOB</sub>  | Low Output Voltage Swing (Load = 32 ohms to Vdd/2) Power = Low Power = High  |                                    | _<br>_     | 0.5 x Vdd - 1.3<br>0.5 x Vdd - 1.3 | V        |

| I <sub>SOB</sub>     | Supply Current Including Bias Cell (No Load) Power = Low Power = High        |                                    | 1.1<br>2.6 | 5.1<br>8.8                         | mA<br>mA |

| PSRR <sub>OB</sub>   | Supply Voltage Rejection Ratio                                               | 60                                 | _          | _                                  | dB       |

Table 18. 3.3V DC Analog Output Buffer Specifications

| Symbol               | Description                                                                  | Min                                | Тур        | Max                                | Units    |

|----------------------|------------------------------------------------------------------------------|------------------------------------|------------|------------------------------------|----------|

| V <sub>OSOB</sub>    | Input Offset Voltage (Absolute Value)                                        | _                                  | 3          | 12                                 | mV       |

| TCV <sub>OSOB</sub>  | Average Input Offset Voltage Drift                                           | _                                  | +6         | _                                  | μV/°C    |

| $V_{CMOB}$           | Common-Mode Input Voltage Range                                              | 0.5                                | ı          | Vdd - 1.0                          | V        |

| R <sub>OUTOB</sub>   | Output Resistance Power = Low Power = High                                   |                                    | 1          | -<br>-                             | W        |

| V <sub>OHIGHOB</sub> | High Output Voltage Swing (Load = 1K ohms to Vdd/2) Power = Low Power = High | 0.5 x Vdd + 1.0<br>0.5 x Vdd + 1.0 |            | _<br>_<br>_                        | V<br>V   |

| V <sub>OLOWOB</sub>  | Low Output Voltage Swing (Load = 1K ohms to Vdd/2) Power = Low Power = High  |                                    |            | 0.5 x Vdd - 1.0<br>0.5 x Vdd - 1.0 | V<br>V   |

| I <sub>SOB</sub>     | Supply Current Including Bias Cell (No Load) Power = Low Power = High        | _                                  | 0.8<br>2.0 | 2.0<br>4.3                         | mA<br>mA |

| PSRR <sub>OB</sub>   | Supply Voltage Rejection Ratio                                               | 50                                 | _          | _                                  | dB       |

Document Number: 38-12011 Rev. \*G Page 21 of 43

#### DC Analog Reference Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ , or 3.0V to 3.6V and  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ , respectively. Typical parameters apply to 5V and 3.3V at  $25^{\circ}C$  and are for design guidance only or unless otherwise specified.

The guaranteed specifications are measured through the Analog Continuous Time PSoC blocks. The power levels for AGND refer to the power of the Analog Continuous Time PSoC block. The power levels for RefHi and RefLo refer to the Analog Reference Control register. The limits stated for AGND include the offset error of the AGND buffer local to the Analog Continuous Time PSoC block.

**Note** Avoid using P2[4] for digital signaling when using an analog resource that depends on the Analog Reference. Some coupling of the digital signal may appear on the AGND.

Table 20. 5V DC Analog Reference Specifications

| Symbol | Description                                                                       | Min                       | Тур                       | Max                       | Units |

|--------|-----------------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|-------|

| BG     | Bandgap Voltage Reference                                                         | 1.274                     | 1.30                      | 1.326                     | V     |

| _      | AGND = Vdd/2 <sup>a</sup><br>CT Block Power = High                                | Vdd/2 - 0.043             | Vdd/2 - 0.025             | Vdd/2 + 0.003             | V     |

| _      | AGND = 2 x BandGap <sup>a</sup><br>CT Block Power = High                          | 2 x BG - 0.048            | 2 x BG - 0.030            | 2 x BG + 0.024            | V     |

| _      | AGND = P2[4] (P2[4] = Vdd/2) <sup>a</sup><br>CT Block Power = High                | P2[4] - 0.013             | P2[4]                     | P2[4] + 0.014             | V     |

| _      | AGND = BandGap <sup>a</sup><br>CT Block Power = High                              | BG - 0.009                | BG + 0.008                | BG + 0.016                | V     |

| _      | AGND = 1.6 x BandGap <sup>a</sup><br>CT Block Power = High                        | 1.6 x BG - 0.022          | 1.6 x BG - 0.010          | 1.6 x BG + 0.018          | V     |

| _      | AGND Column to Column Variation (AGND = Vdd/2) <sup>a</sup> CT Block Power = High | -0.034                    | 0.000                     | 0.034                     | ٧     |

| _      | RefHi = Vdd/2 + BandGap<br>Ref Control Power = High                               | Vdd/2 + BG - 0.140        | Vdd/2 + BG - 0.018        | Vdd/2 + BG +<br>0.103     | V     |

| _      | RefHi = 3 x BandGap<br>Ref Control Power = High                                   | 3 x BG - 0.112            | 3 x BG - 0.018            | 3 x BG + 0.076            | V     |

| _      | RefHi = 2 x BandGap + P2[6] (P2[6] = 1.3V)<br>Ref Control Power = High            | 2 x BG + P2[6] -<br>0.113 | 2 x BG + P2[6] -<br>0.018 | 2 x BG + P2[6] +<br>0.077 | ٧     |

| _      | RefHi = P2[4] + BandGap (P2[4] = Vdd/2)<br>Ref Control Power = High               | P2[4] + BG - 0.130        | P2[4] + BG - 0.016        | P2[4] + BG + 0.098        | V     |

| _      | RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 1.3V)<br>Ref Control Power = High   | P2[4] + P2[6] - 0.133     | P2[4] + P2[6] -<br>0.016  | P2[4] + P2[6]+<br>0.100   | V     |

| _      | RefHi = 3.2 x BandGap<br>Ref Control Power = High                                 | 3.2 x BG - 0.112          | 3.2 x BG                  | 3.2 x BG + 0.076          | V     |

| _      | RefLo = Vdd/2 - BandGap<br>Ref Control Power = High                               | Vdd/2 - BG - 0.051        | Vdd/2 - BG + 0.024        | Vdd/2 - BG + 0.098        | V     |

| _      | RefLo = BandGap<br>Ref Control Power = High                                       | BG - 0.082                | BG + 0.023                | BG + 0.129                | V     |

| _      | RefLo = 2 x BandGap - P2[6] (P2[6] = 1.3V)<br>Ref Control Power = High            | 2 x BG - P2[6] -<br>0.084 | 2 x BG - P2[6] +<br>0.025 | 2 x BG - P2[6] +<br>0.134 | V     |

| _      | RefLo = P2[4] – BandGap (P2[4] = Vdd/2)<br>Ref Control Power = High               | P2[4] - BG - 0.056        | P2[4] - BG + 0.026        | P2[4] - BG + 0.107        | V     |

| _      | RefLo = P2[4]-P2[6] (P2[4] = Vdd/2, P2[6] = 1.3V)<br>Ref Control Power = High     | P2[4] - P2[6] - 0.057     | P2[4] - P2[6] +<br>0.026  | P2[4] - P2[6] +<br>0.110  | V     |

a. AGND tolerance includes the offsets of the local buffer in the PSoC block. Bandgap voltage is 1.3V  $\pm$  2%.

Document Number: 38-12011 Rev. \*G Page 23 of 43

Table 21. 3.3V DC Analog Reference Specifications

| Symbol | Description                                                                          | Min                        | Тур                      | Max                      | Units |  |  |

|--------|--------------------------------------------------------------------------------------|----------------------------|--------------------------|--------------------------|-------|--|--|

| BG     | Bandgap Voltage Reference                                                            | 1.274                      | 1.30                     | 1.326                    | V     |  |  |

| -      | AGND = Vdd/2 <sup>a</sup><br>CT Block Power = High                                   | Vdd/2 - 0.037 Vdd/2 - 0.02 |                          | Vdd/2 + 0.002            | V     |  |  |

| _      | AGND = 2 x BandGap <sup>a</sup> CT Block Power = High                                |                            | Not Allowed              | d                        |       |  |  |

| 1      | AGND = P2[4] (P2[4] = Vdd/2)<br>CT Block Power = High                                | P2[4] - 0.008              | P2[4] + 0.001            | P2[4] + 0.009            | V     |  |  |

| 1      | AGND = BandGap <sup>a</sup> CT Block Power = High                                    | BG - 0.009                 | BG + 0.005               | BG + 0.015               | V     |  |  |

| -      | AGND = 1.6 x BandGap <sup>a</sup><br>CT Block Power = High                           | 1.6 x BG - 0.027           | 1.6 x BG - 0.010         | 1.6 x BG + 0.018         | V     |  |  |

| -      | AGND Column to Column Variation (AGND = Vdd/2) <sup>a</sup><br>CT Block Power = High | -0.034                     | 0.000                    | 0.034                    | mV    |  |  |

| _      | RefHi = Vdd/2 + BandGap<br>Ref Control Power = High                                  | Not Allowed                |                          |                          |       |  |  |

| _      | RefHi = 3 x BandGap<br>Ref Control Power = High                                      | Not Allowed                |                          |                          |       |  |  |

| _      | RefHi = 2 x BandGap + P2[6] (P2[6] = 0.5V)<br>Ref Control Power = High               | Not Allowed                |                          |                          |       |  |  |

| _      | RefHi = P2[4] + BandGap (P2[4] = Vdd/2)<br>Ref Control Power = High                  |                            | Not Allowed              | t                        |       |  |  |

| _      | RefHi = P2[4] + P2[6] (P2[4] = Vdd/2, P2[6] = 0.5V)<br>Ref Control Power = High      | P2[4] + P2[6] -<br>0.075   | P2[4] + P2[6] -<br>0.009 | P2[4] + P2[6] +<br>0.057 | V     |  |  |

| _      | RefHi = 3.2 x BandGap<br>Ref Control Power = High                                    |                            | Not Allowed              | d                        |       |  |  |

| _      | RefLo = Vdd/2 - BandGap<br>Ref Control Power = High                                  | Not Allowed                |                          |                          |       |  |  |

| _      | RefLo = BandGap<br>Ref Control Power = High                                          | Not Allowed                |                          |                          |       |  |  |

| _      | RefLo = 2 x BandGap - P2[6] (P2[6] = 0.5V)<br>Ref Control Power = High               | Not Allowed                |                          |                          |       |  |  |

| _      | RefLo = P2[4] - BandGap (P2[4] = Vdd/2)<br>Ref Control Power = High                  | Not Allowed                |                          |                          |       |  |  |

| _      | RefLo = P2[4]-P2[6] (P2[4] = Vdd/2, P2[6] = 0.5V)<br>Ref Control Power = High        | P2[4] - P2[6] -<br>0.048   | P2[4]- P2[6] +<br>0.022  | P2[4] - P2[6] +<br>0.092 | V     |  |  |

a. AGND tolerance includes the offsets of the local buffer in the PSoC block. Bandgap voltage is 1.3V  $\pm\,2\%$

Document Number: 38-12011 Rev. \*G Page 24 of 43

#### **AC Electrical Characteristics**

#### AC Chip-Level Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and  $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ , or 3.0V to 3.6V and  $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ , respectively. Typical parameters apply to 5V and 3.3V at 25°C and are for design guidance only or unless otherwise specified.

Table 25. AC Chip-Level Specifications

| Symbol                   | Description                                             | Min  | Тур    | Max                   | Units | Notes                                                        |

|--------------------------|---------------------------------------------------------|------|--------|-----------------------|-------|--------------------------------------------------------------|

| F <sub>IMO</sub>         | Internal Main Oscillator Frequency                      | 23.4 | 24     | 24.6 <sup>a</sup>     | MHz   | Trimmed. Using factory trim values.                          |

| F <sub>CPU1</sub>        | CPU Frequency (5V Nominal)                              |      | 24     | 24.6 <sup>a,b</sup>   | MHz   |                                                              |

| F <sub>CPU2</sub>        | CPU Frequency (3.3V Nominal)                            | 0.93 | 12     | 12.3 <sup>b,c</sup>   | MHz   |                                                              |

| F <sub>48M</sub>         | Digital PSoC Block Frequency                            | 0    | 48     | 49.2 <sup>a,b,d</sup> | MHz   | Refer to the AC Digital Block Specifications.                |

| F <sub>24M</sub>         | Digital PSoC Block Frequency                            | 0    | 24     | 24.6 <sup>b,e,d</sup> | MHz   |                                                              |

| F <sub>32K1</sub>        | Internal Low Speed Oscillator Frequency                 | 15   | 32     | 64                    | kHz   |                                                              |

| F <sub>32K2</sub>        | External Crystal Oscillator                             | -    | 32.768 | _                     | kHz   | Accuracy is capacitor and crystal dependent. 50% duty cycle. |

| F <sub>PLL</sub>         | PLL Frequency                                           | -    | 23.986 | _                     | MHz   | Is a multiple (x732) of crystal frequency.                   |

| Jitter24M2               | 24 MHz Period Jitter (PLL)                              | _    | _      | 600                   | ps    |                                                              |

| T <sub>PLLSLEW</sub>     | PLL Lock Time                                           | 0.5  | _      | 10                    | ms    |                                                              |

| T <sub>PLLSLEWSLOW</sub> | PLL Lock Time for Low Gain Setting                      | 0.5  | _      | 50                    | ms    |                                                              |

| T <sub>OS</sub>          | External Crystal Oscillator Startup to 1%               | -    | 1700   | 2620                  | ms    |                                                              |

| T <sub>OSACC</sub>       | External Crystal Oscillator Startup to 100 ppm          | -    | 2800   | 3800 <sup>f</sup>     | ms    |                                                              |

| Jitter32k                | 32 kHz Period Jitter                                    | -    | 100    |                       | ns    |                                                              |

| T <sub>XRST</sub>        | External Reset Pulse Width                              | 10   | _      | _                     | μS    |                                                              |

| DC24M                    | 24 MHz Duty Cycle                                       | 40   | 50     | 60                    | %     |                                                              |

| Step24M                  | 24 MHz Trim Step Size                                   | _    | 50     | _                     | kHz   |                                                              |

| Fout48M                  | 48 MHz Output Frequency                                 | 46.8 | 48.0   | 49.2 <sup>a,c</sup>   | MHz   | Trimmed. Using factory trim values.                          |

| Jitter24M1               | 24 MHz Period Jitter (IMO)                              | _    | 600    |                       | ps    |                                                              |

| F <sub>MAX</sub>         | Maximum frequency of signal on row input or row output. | -    | _      | 12.3                  | MHz   |                                                              |

| T <sub>RAMP</sub>        | Supply Ramp Time                                        | 0    | _      | _                     | μS    |                                                              |

a. 4.75V < Vdd < 5.25V.

Document Number: 38-12011 Rev. \*G Page 27 of 43

Accuracy derived from Internal Main Oscillator with appropriate trim for Vdd range.

3.0V < Vdd < 3.6V. See Application Note AN2012 "Adjusting PSoC Microcontroller Trims for Dual Voltage-Range Operation" for information on trimming for opera-</li>

d. See the individual user module data sheets for information on maximum frequencies for user modules.

<sup>3.0</sup>V < 5.25V.

f. The crystal oscillator frequency is within 100 ppm of its final value by the end of the T<sub>osacc</sub> period. Correct operation assumes a properly loaded 1 uW maximum drive level 32.768 kHz crystal. 3.0V  $\leq$  Vdd  $\leq$  5.5V, -40  $^{o}C$   $\leq$   $T_{A}$   $\leq$  85  $^{o}C.$

## AC General Purpose IO Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, or 3.0V to 3.6V and -40°C  $\leq$  T<sub>A</sub>  $\leq$  85°C, respectively. Typical parameters apply to 5V and 3.3V at 25°C and are for design guidance only or unless otherwise specified.

Table 26. AC GPIO Specifications

| Symbol            | Description                                  | Min | Тур | Max | Units | Notes                         |

|-------------------|----------------------------------------------|-----|-----|-----|-------|-------------------------------|

| F <sub>GPIO</sub> | GPIO Operating Frequency                     | 0   | _   | 12  | MHz   |                               |

| TRiseF            | Rise Time, Normal Strong Mode, Cload = 50 pF | 3   | _   | 18  | ns    | Vdd = 4.5 to 5.25V, 10% - 90% |

| TFallF            | Fall Time, Normal Strong Mode, Cload = 50 pF | 2   | _   | 18  | ns    | Vdd = 4.5 to 5.25V, 10% - 90% |

| TRiseS            | Rise Time, Slow Strong Mode, Cload = 50 pF   | 10  | 27  | _   | ns    | Vdd = 3 to 5.25V, 10% - 90%   |

| TFallS            | Fall Time, Slow Strong Mode, Cload = 50 pF   | 10  | 22  | -   | ns    | Vdd = 3 to 5.25V, 10% - 90%   |

GPIO Pin

TRiseF TRiseS TFallF TFallS

Figure 17. GPIO Timing Diagram

Document Number: 38-12011 Rev. \*G Page 29 of 43

Table 28. 3.3V AC Operational Amplifier Specifications

| Symbol            | Description                                                                                                                                                                                                                                                                                       | Min                   | Тур              | Max          | Units                                        | Notes                                                                                                                                                             |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------------|--------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T <sub>ROA</sub>  | Rising Settling Time from 80% of $\Delta V$ to 0.1% of $\Delta V$ (10 pF load, Unity Gain)  Power = Low  Power = Low, Opamp Bias = High  Power = Medium  Power = Medium, Opamp Bias = High  Power = High (3.3 Volt High Bias Operation not                                                        |                       |                  | 3.92<br>0.72 | μs<br>μs<br>μs<br>μs<br>μs                   | Specification maximums for low power and high opamp bias, medium power, and medium power and high opamp bias levels are between low and high power levels.        |

|                   | supported) Power = High, Opamp Bias = High (3.3 Volt High Power, High Opamp Bias not supported)                                                                                                                                                                                                   | -                     | _                | _            | μS                                           |                                                                                                                                                                   |

| T <sub>SOA</sub>  | Falling Settling Time from 20% of ∆V to 0.1% of ∆V (10 pF load, Unity Gain) Power = Low Power = Low, Opamp Bias = High Power = Medium Power = Medium, Opamp Bias = High                                                                                                                           | -<br>-<br>-<br>-      | _                | 5.41<br>0.72 | μs<br>μs<br>μs<br>μs                         | Specification maximums for<br>low power and high opamp<br>bias, medium power, and<br>medium power and high<br>opamp bias levels are<br>between low and high power |

|                   | Power = High (3.3 Volt High Bias Operation not supported) Power = High, Opamp Bias = High (3.3 Volt High Power, High Opamp Bias not supported)                                                                                                                                                    | _                     | _                | _            | μS<br>μS                                     | levels.                                                                                                                                                           |

| SR <sub>ROA</sub> | Rising Slew Rate (20% to 80%) (10 pF load, Unity Gain) Power = Low Power = Low, Opamp Bias = High Power = Medium Power = Medium, Opamp Bias = High Power = High (3.3 Volt High Bias Operation not supported) Power = High, Opamp Bias = High (3.3 Volt High Power, High Opamp Bias not supported) | 0.31<br>2.7<br>-      | -<br>-<br>-      | _            | V/µs<br>V/µs<br>V/µs<br>V/µs<br>V/µs<br>V/µs | Specification minimums for low power and high opamp bias, medium power, and medium power and high opamp bias levels are between low and high power levels.        |

| SR <sub>FOA</sub> | Falling Slew Rate(20% to 80%) (10 pF load, Unity Gain) Power = Low Power = Low, Opamp Bias = High Power = Medium Power = Medium, Opamp Bias = High Power = High (3.3 Volt High Bias Operation not supported) Power = High, Opamp Bias = High (3.3 Volt High Power, High Opamp Bias not supported) | 0.24<br>1.8<br>-      | -<br>-<br>-      | -            | V/µs<br>V/µs<br>V/µs<br>V/µs<br>V/µs<br>V/µs | Specification minimums for low power and high opamp bias, medium power, and medium power and high opamp bias levels are between low and high power levels.        |

| BW <sub>OA</sub>  | Gain Bandwidth Product Power = Low Power = Low, Opamp Bias = High Power = Medium Power = Medium, Opamp Bias = High Power = High (3.3 Volt High Bias Operation not supported) Power = High, Opamp Bias = High (3.3 Volt High Power, High Opamp Bias not supported)                                 | 0.67<br>2.8<br>-<br>- | -<br>-<br>-<br>- | -            | MHz<br>MHz<br>MHz<br>MHz<br>MHz              | Specification minimums for low power and high opamp bias, medium power, and medium power and high opamp bias levels are between low and high power levels.        |

| E <sub>NOA</sub>  | Noise at 1 kHz (Power = Medium, Opamp Bias = High)                                                                                                                                                                                                                                                | _                     | 200              | _            | nV/rt-Hz                                     |                                                                                                                                                                   |

Document Number: 38-12011 Rev. \*G

Page 31 of 43

## AC Digital Block Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75V to 5.25V and  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ , or 3.0V to 3.6V and  $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ , respectively. Typical parameters apply to 5V and 3.3V at  $25^{\circ}C$  and are for design guidance only or unless otherwise specified.

Table 29. AC Digital Block Specifications

| Function             | Description                               | Min             | Тур | Max  | Units | Notes               |

|----------------------|-------------------------------------------|-----------------|-----|------|-------|---------------------|

| Timer                | Capture Pulse Width                       |                 | _   | _    | ns    |                     |

|                      | Maximum Frequency, No Capture             | _               | -   | 49.2 | MHz   | 4.75V < Vdd < 5.25V |

|                      | Maximum Frequency, With Capture           | _               | -   | 24.6 | MHz   |                     |

| Counter              | Enable Pulse Width                        | 50 <sup>a</sup> | -   | _    | ns    |                     |

|                      | Maximum Frequency, No Enable Input        | _               | -   | 49.2 | MHz   | 4.75V < Vdd < 5.25V |

|                      | Maximum Frequency, Enable Input           | _               | -   | 24.6 | MHz   |                     |

| Dead Band            | Kill Pulse Width:                         |                 |     |      |       |                     |

|                      | Asynchronous Restart Mode                 | 20              | -   | _    | ns    |                     |

|                      | Synchronous Restart Mode                  | 50 <sup>a</sup> | _   | _    | ns    |                     |

|                      | Disable Mode                              | 50 <sup>a</sup> | _   | _    | ns    |                     |

|                      | Maximum Frequency                         | _               | -   | 49.2 | MHz   | 4.75V < Vdd < 5.25V |

| CRCPRS<br>(PRS Mode) | Maximum Input Clock Frequency             | _               | _   | 49.2 | MHz   | 4.75V < Vdd < 5.25V |

| CRCPRS<br>(CRC Mode) | Maximum Input Clock Frequency             |                 | _   | 24.6 | MHz   |                     |

| SPIM                 | Maximum Input Clock Frequency             | _               | _   | 8.2  | MHz   |                     |

| SPIS                 | Maximum Input Clock Frequency             | _               | _   | 4.1  | ns    |                     |

|                      | Width of SS_Negated Between Transmissions | 50 <sup>a</sup> | _   | _    | ns    |                     |

| Transmitter          | Maximum Input Clock Frequency             | _               | _   | 16.4 | MHz   |                     |

| Receiver             | Maximum Input Clock Frequency             | _               | 16  | 49.2 | MHz   | 4.75V < Vdd < 5.25V |

a. 50 ns minimum input pulse width is based on the input synchronizers running at 24 MHz (42 ns nominal period).

Document Number: 38-12011 Rev. \*G Page 32 of 43

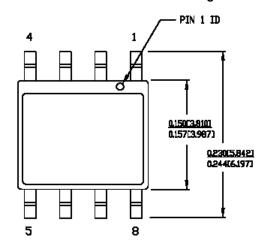

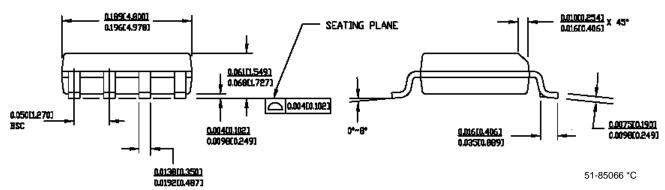

Figure 20. 8-Pin (150-Mil) SOIC

- 1. DIMENSIONS IN INCHESIMMI MIN. MAX.

- 2. PIN 1 ID IS OPTIONAL, ROUND ON SINGLE LEADFRAME RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART #  |                |  |  |  |  |

|---------|----------------|--|--|--|--|

| S08.15  | STANDARD PKG.  |  |  |  |  |

| SZ08.15 | LEAD FREE PKG. |  |  |  |  |

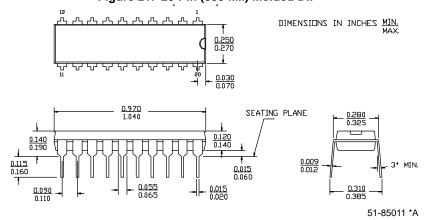

Figure 21. 20-Pin (300-Mil) Molded DIP

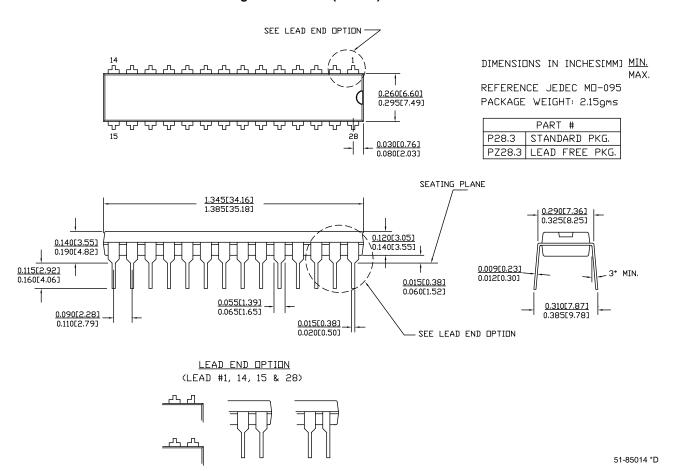

Figure 24. 28-Pin (300-Mil) Molded DIP

Document Number: 38-12011 Rev. \*G Page 39 of 43

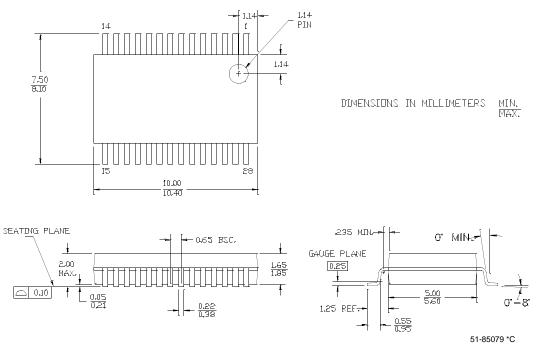

Figure 25. 28-Pin (210-Mil) SSOP

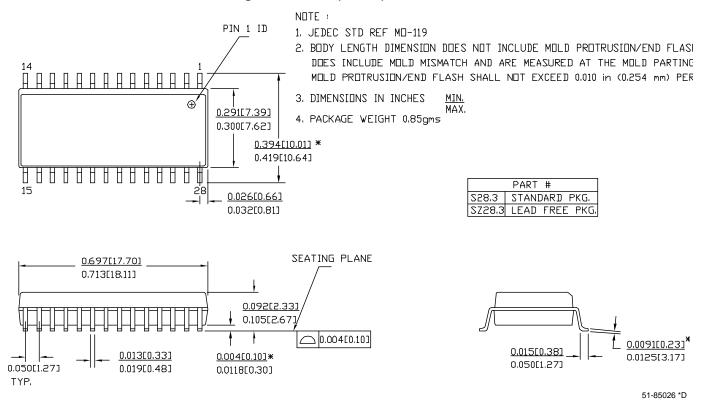

Figure 26. 28-Pin (300-Mil) Molded SOIC

Document Number: 38-12011 Rev. \*G

Page 40 of 43

## **Document History Page**

|          | nt Title: CY<br>nt Number: |                     | 24223, CY8C2       | 24423 PSoC <sup>®</sup> Programmable System-on-Chip™                                                                                                                                                                                                                                                                            |

|----------|----------------------------|---------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision | ECN                        | Orig. of<br>Change  | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                           |

| **       | 127043                     | New Silicon and NWJ | 05/15/2003         | New document – Advanced Data Sheet (two page product brief).                                                                                                                                                                                                                                                                    |

| *A       | 128779                     | NWJ                 | 08/13/2003         | New document – Preliminary Data Sheet (300 page product detail).                                                                                                                                                                                                                                                                |

| *B       | 129775                     | MWR/NWJ             | 09/26/2003         | Changes to Electrical Specifications section, Register Details chapter, and chapter changes in the Analog System section.                                                                                                                                                                                                       |

| *C       | 130128                     | NWJ                 | 10/14/2003         | Revised document for Silicon Revision A.                                                                                                                                                                                                                                                                                        |

| *D       | 131678                     | NWJ                 | 12/04/2003         | Changes to Electrical Specifications section, Miscellaneous changes to I2C, GDI, RDI, Registers, and Digital Block chapters.                                                                                                                                                                                                    |

| *E       | 131802                     | NWJ                 | 12/22/2003         | Changes to Electrical Specifications and miscellaneous small changes throughout the data sheet.                                                                                                                                                                                                                                 |

| *F       | 229418                     | SFV                 | 06/04/2004         | New data sheet format and organization. Reference the <i>PSoC Programmable System-on-Chip Technical Reference Manual</i> for additional information. Title change.                                                                                                                                                              |

| *G       | 2619935                    | ONGE/AESA           | 12/11/2008         | Changed title to "CY8C24123, CY8C24223, CY8C24423 PSoC® Programmable System-on-Chip <sup>TM</sup> " Updated package diagrams 51-85188, 51-85024, 51-85014, and 51-85026. Added note on digital signaling in Table on page 23. Added Die Sales information note to Ordering Information on page 42. Updated data sheet template. |

# Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at cypress.com/sales.

| Products         |                      | PSoC Solutions        |                                   |

|------------------|----------------------|-----------------------|-----------------------------------|

| PSoC             | psoc.cypress.com     | General               | psoc.cypress.com/solutions        |

| Clocks & Buffers | clocks.cypress.com   | Low Power/Low Voltage | psoc.cypress.com/low-power        |

| Wireless         | wireless.cypress.com | Precision Analog      | psoc.cypress.com/precision-analog |

| Memories         | memory.cypress.com   | LCD Drive             | psoc.cypress.com/lcd-drive        |

| Image Sensors    | image.cypress.com    | CAN 2.0b              | psoc.cypress.com/can              |

|                  |                      | USB                   | psoc.cypress.com/usb              |

© Cypress Semiconductor Corporation, 2003-2008. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.