Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                 |

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, MMC, SPI, SSC, UART/USART, USB                         |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 34                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 8x10/12b                                                             |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 48-LQFP                                                                  |

| Supplier Device Package    | 48-LQFP (7x7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam3s1aa-aur |

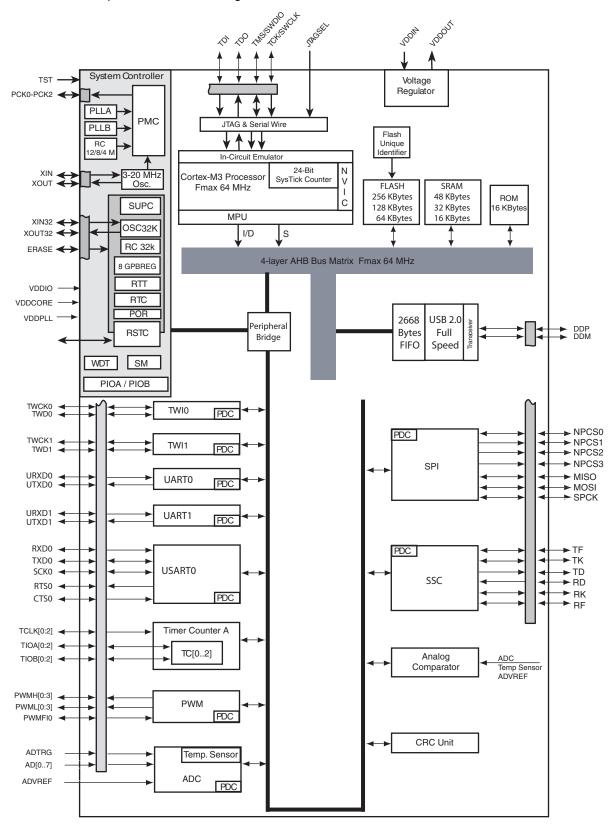

Figure 2-3. SAM3S 48-pin Version Block Diagram

Table 3-1.

Signal Description List (Continued)

| Signal Name   | Function                       | Туре             | Active<br>Level | Voltage reference | Comments                                                                                    |

|---------------|--------------------------------|------------------|-----------------|-------------------|---------------------------------------------------------------------------------------------|

|               | Universal Asynchronous         | Receiver Trans   | smitter - U     | ARTx              |                                                                                             |

| URXDx         | UART Receive Data              | Input            |                 |                   |                                                                                             |

| UTXDx         | UART Transmit Data             | Output           |                 |                   |                                                                                             |

|               | PIO Controller -               | PIOA - PIOB -    | PIOC            |                   |                                                                                             |

| PA0 - PA31    | Parallel IO Controller A       | I/O              |                 | Reset State:      |                                                                                             |

| PB0 - PB14    | Parallel IO Controller B       | I/O              |                 | VDDIO             | - PIO or System IOs <sup>(2)</sup>                                                          |

| PC0 - PC31    | Parallel IO Controller C       | I/O              |                 |                   | <ul> <li>Internal pull-up enabled</li> <li>Schmitt Trigger enabled<sup>(1)</sup></li> </ul> |

|               | PIO Controller - Paralle       | I Capture Mode   | e (PIOA Oi      | nly)              |                                                                                             |

| PIODC0-PIODC7 | Parallel Capture Mode Data     | Input            |                 |                   |                                                                                             |

| PIODCCLK      | Parallel Capture Mode Clock    | Input            |                 | VDDIO             |                                                                                             |

| PIODCEN1-2    | Parallel Capture Mode Enable   | Input            |                 |                   |                                                                                             |

|               | External                       | Bus Interface    |                 |                   |                                                                                             |

| D0 - D7       | Data Bus                       | I/O              |                 |                   |                                                                                             |

| A0 - A23      | Address Bus                    | Output           |                 |                   |                                                                                             |

| NWAIT         | External Wait Signal           | Input            | Low             |                   |                                                                                             |

|               | Static Memor                   | y Controller - S | МС              |                   |                                                                                             |

| NCS0 - NCS3   | Chip Select Lines              | Output           | Low             |                   |                                                                                             |

| NRD           | Read Signal                    | Output           | Low             |                   |                                                                                             |

| NWE           | Write Enable                   | Output           | Low             |                   |                                                                                             |

|               | NAND                           | Flash Logic      |                 |                   |                                                                                             |

| NANDOE        | NAND Flash Output Enable       | Output           | Low             |                   |                                                                                             |

| NANDWE        | NAND Flash Write Enable        | Output           | Low             |                   |                                                                                             |

|               | High Speed Multimed            | lia Card Interfa | ce - HSMC       | CI                |                                                                                             |

| MCCK          | Multimedia Card Clock          | I/O              |                 |                   |                                                                                             |

| MCCDA         | Multimedia Card Slot A Command | I/O              |                 |                   |                                                                                             |

| MCDA0 - MCDA3 | Multimedia Card Slot A Data    | I/O              |                 |                   |                                                                                             |

|               | Universal Synchronous Asynchi  | onous Receive    | er Transmi      | tter USARTx       | (                                                                                           |

| SCKx          | USARTx Serial Clock            | I/O              |                 |                   |                                                                                             |

| TXDx          | USARTx Transmit Data           | I/O              |                 |                   |                                                                                             |

| RXDx          | USARTx Receive Data            | Input            |                 |                   |                                                                                             |

| RTSx          | USARTx Request To Send         | Output           |                 |                   |                                                                                             |

| CTSx          | USARTx Clear To Send           | Input            |                 |                   |                                                                                             |

| DTR1          | USART1 Data Terminal Ready     | I/O              |                 |                   |                                                                                             |

| DSR1          | USART1 Data Set Ready          | Input            |                 |                   |                                                                                             |

| DCD1          | USART1 Data Carrier Detect     | Input            |                 |                   |                                                                                             |

| RI1           | USART1 Ring Indicator          | Input            |                 |                   |                                                                                             |

## 4.1.3 100-Lead LQFP Pinout

Table 4-1. 100-lead LQFP SAM3S4/2/1C Pinout

| 1  | ADVREF          |

|----|-----------------|

| 2  | GND             |

| 3  | PB0/AD4         |

| 4  | PC29/AD13       |

| 5  | PB1/AD5         |

| 6  | PC30/AD14       |

| 7  | PB2/AD6         |

| 8  | PC31            |

| 9  | PB3/AD7         |

| 10 | VDDIN           |

| 11 | VDDOUT          |

| 12 | PA17/PGMD5/AD0  |

| 13 | PC26            |

| 14 | PA18/PGMD6/AD1  |

| 15 | PA21/PGMD9/AD8  |

| 16 | VDDCORE         |

| 17 | PC27            |

| 18 | PA19/PGMD7/AD2  |

| 19 | PC15/AD11       |

| 20 | PA22/PGMD10/AD9 |

| 21 | PC13/AD10       |

| 22 | PA23/PGMD1      |

| 23 | PC12/AD12       |

| 24 | PA20/PGMD8/AD3  |

| 25 | PC0             |

|    | ·               |

| 77 (17100-172) 10 1 1110dt |                         |  |

|----------------------------|-------------------------|--|

| 26                         | GND                     |  |

| 27                         | VDDIO                   |  |

| 28                         | PA16/PGMD4              |  |

| 29                         | PC7                     |  |

| 30                         | PA15/PGMD3              |  |

| 31                         | PA14/PGMD2              |  |

| 32                         | PC6                     |  |

| 33                         | PA13/PGMD1              |  |

| 34                         | PA24/PGMD12             |  |

| 35                         | PC5                     |  |

| 36                         | VDDCORE                 |  |

| 37                         | PC4                     |  |

| 38                         | PA25/PGMD13             |  |

| 39                         | PA26/PGMD14             |  |

| 40                         | PC3                     |  |

| 41                         | PA12/PGMD0              |  |

| 42                         | PA11/PGMM3              |  |

| 43                         | PC2                     |  |

| 44                         | PA10/PGMM2              |  |

| 45                         | GND                     |  |

| 46                         | PA9/PGMM1               |  |

| 47                         | PC1                     |  |

| 48                         | PA8/XOUT32/<br>PGMM0    |  |

| 49                         | PA7/XIN32/<br>PGMNVALID |  |

| 50                         | VDDIO                   |  |

| 50                         | VDDIO                   |  |

| 51 | TDI/PB4     |

|----|-------------|

| 52 | PA6/PGMNOE  |

| 53 | PA5/PGMRDY  |

| 54 | PC28        |

| 55 | PA4/PGMNCMD |

| 56 | VDDCORE     |

| 57 | PA27/PGMD15 |

| 58 | PC8         |

| 59 | PA28        |

| 60 | NRST        |

| 61 | TST         |

| 62 | PC9         |

| 63 | PA29        |

| 64 | PA30        |

| 65 | PC10        |

| 66 | PA3         |

| 67 | PA2/PGMEN2  |

| 68 | PC11        |

| 69 | VDDIO       |

| 70 | GND         |

| 71 | PC14        |

| 72 | PA1/PGMEN1  |

| 73 | PC16        |

| 74 | PA0/PGMEN0  |

| 75 | PC17        |

| 76  | TDO/TRACESWO/PB<br>5 |

|-----|----------------------|

| 77  | JTAGSEL              |

| 78  | PC18                 |

| 79  | TMS/SWDIO/PB6        |

| 80  | PC19                 |

| 81  | PA31                 |

| 82  | PC20                 |

| 83  | TCK/SWCLK/PB7        |

| 84  | PC21                 |

| 85  | VDDCORE              |

| 86  | PC22                 |

| 87  | ERASE/PB12           |

| 88  | DDM/PB10             |

| 89  | DDP/PB11             |

| 90  | PC23                 |

| 91  | VDDIO                |

| 92  | PC24                 |

| 93  | PB13/DAC0            |

| 94  | PC25                 |

| 95  | GND                  |

| 96  | PB8/XOUT             |

| 97  | PB9/PGMCK/XIN        |

| 98  | VDDIO                |

| 99  | PB14/DAC1            |

| 100 | VDDPLL               |

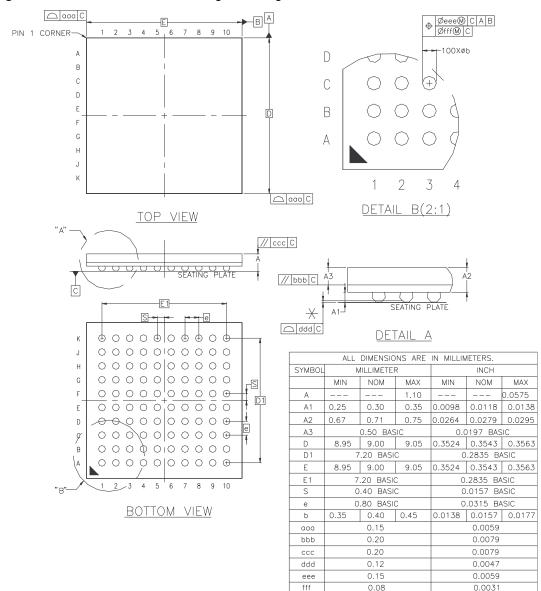

## 4.3.1 48-Lead LQFP and QFN Pinout

**Table 4-4.** 48-pin SAM3S4/2/1A Pinout

| Iable | 4-4. 40-pin SAN    | 1004/2/1 |

|-------|--------------------|----------|

| 1     | ADVREF             | 13       |

| 2     | GND                | 14       |

| 3     | PB0/AD4            | 15       |

| 4     | PB1/AD5            | 16       |

| 5     | PB2/AD6            | 17       |

| 6     | PB3/AD7            | 18       |

| 7     | VDDIN              | 19       |

| 8     | VDDOUT             | 20       |

| 9     | PA17/PGMD5/<br>AD0 | 21       |

| 10    | PA18/PGMD6/<br>AD1 | 22       |

| 11    | PA19/PGMD7/<br>AD2 | 23       |

| 12    | PA20/AD3           | 24       |

| 13 | VDDIO       |

|----|-------------|

| 14 | PA16/PGMD4  |

| 15 | PA15/PGMD3  |

| 16 | PA14/PGMD2  |

| 17 | PA13/PGMD1  |

| 18 | VDDCORE     |

| 19 | PA12/PGMD0  |

| 20 | PA11/PGMM3  |

| 21 | PA10/PGMM2  |

| 22 | PA9/PGMM1   |

| 23 | PA8/XOUT32/ |

|    | PGMM0       |

| 24 | PA7/XIN32/  |

| 24 | PGMNVALID   |

| 25 | TDI/PB4     |

|----|-------------|

| 26 | PA6/PGMNOE  |

| 27 | PA5/PGMRDY  |

| 28 | PA4/PGMNCMD |

| 29 | NRST        |

| 30 | TST         |

| 31 | PA3         |

| 32 | PA2/PGMEN2  |

| 33 | VDDIO       |

| 34 | GND         |

| 35 | PA1/PGMEN1  |

| 36 | PA0/PGMEN0  |

| 37 | TDO/TRACESWO/<br>PB5 |

|----|----------------------|

| 38 | JTAGSEL              |

| 39 | TMS/SWDIO/PB6        |

| 40 | TCK/SWCLK/PB7        |

| 41 | VDDCORE              |

| 42 | ERASE/PB12           |

| 43 | DDM/PB10             |

| 44 | DDP/PB11             |

| 45 | XOUT/PB8             |

| 46 | XIN/PB9/PGMCK        |

| 47 | VDDIO                |

| 48 | VDDPLL               |

Note: The bottom pad of the QFN package must be connected to ground.

### 5. Power Considerations

## 5.1 Power Supplies

The SAM3S product has several types of power supply pins:

- VDDCORE pins: Power the core, the embedded memories and the peripherals; voltage ranges from 1.62V and 1.95V.

- VDDIO pins: Power the Peripherals I/O lines (Input/Output Buffers); USB transceiver; Backup part, 32kHz crystal oscillator and oscillator pads; ranges from 1.62V and 3.6V

- VDDIN pin: Voltage Regulator Input, ADC, DAC and Analog Comparator Power Supply; Voltage ranges from 1.8V to 3.6V

- VDDPLL pin: Powers the PLLA, PLLB, the Fast RC and the 3 to 20 MHz oscillator; voltage ranges from 1.62V and 1.95V.

## 5.2 Voltage Regulator

The SAM3S embeds a voltage regulator that is managed by the Supply Controller.

This internal regulator is intended to supply the internal core of SAM3S. It features two different operating modes:

- In Normal mode, the voltage regulator consumes less than 700 μA static current and draws 80 mA of output current. Internal adaptive biasing adjusts the regulator quiescent current depending on the required load current. In Wait Mode quiescent current is only 7 μA.

- In Backup mode, the voltage regulator consumes less than 1  $\mu$ A while its output (VDDOUT) is driven internally to GND. The default output voltage is 1.80V and the start-up time to reach Normal mode is inferior to 100  $\mu$ s.

For adequate input and output power supply decoupling/bypassing, refer to the Voltage Regulator section in the Electrical Characteristics section of the datasheet.

## 5.3 Typical Powering Schematics

The SAM3S supports a 1.62V-3.6V single supply mode. The internal regulator input connected to the source and its output feeds VDDCORE. Figure 5-1 shows the power schematics.

As VDDIN powers the voltage regulator, the ADC/DAC and the analog comparator, when the user does not want to use the embedded voltage regulator, it can be disabled by software via the SUPC (note that it is different from Backup mode).

## 6. Input/Output Lines

The SAM3S has several kinds of input/output (I/O) lines such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functionality due to multiplexing capabilities of the PIO controllers. The same PIO line can be used whether in IO mode or by the multiplexed peripheral. System I/Os include pins such as test pins, oscillators, erase or analog inputs.

## 6.1 General Purpose I/O Lines

GPIO Lines are managed by PIO Controllers. All I/Os have several input or output modes such as pull-up or pull-down, input Schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these modes is performed independently for each I/O line through the PIO controller user interface. For more details, refer to the product PIO controller section.

The input output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM3S embeds high speed pads able to handle up to 32 MHz for HSMCI (MCK/2), 45 MHz for SPI clock lines and 35 MHz on other lines. See AC Characteristics Section in the Electrical Characteristics Section of the datasheet for more details. Typical pull-up and pull-down value is 100 k $\Omega$  for all I/Os.

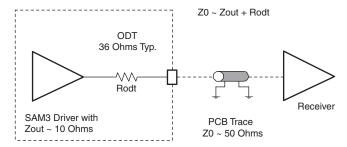

Each I/O line also embeds an ODT (On-Die Termination), see Figure 6-1. It consists of an internal series resistor termination scheme for impedance matching between the driver output (SAM3S) and the PCB trace impedance preventing signal reflection. The series resistor helps to reduce IOs switching current (di/dt) thereby reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect between devices or between boards. In conclusion ODT helps diminish signal integrity issues.

Figure 6-1. On-Die Termination

### 6.2 System I/O Lines

System I/O lines are pins used by oscillators, test mode, reset and JTAG to name but a few. Described below are the SAM3S system I/O lines shared with PIO lines:

These pins are software configurable as general purpose I/O or system pins. At startup the default function of these pins is always used.

### 7. Processor and Architecture

#### 7.1 ARM Cortex-M3 Processor

- Version 2.0

- Thumb-2 (ISA) subset consisting of all base Thumb-2 instructions, 16-bit and 32-bit

- · Harvard processor architecture enabling simultaneous instruction fetch with data load/store

- Three-stage pipeline

- Single cycle 32-bit multiply

- · Hardware divide

- Thumb and Debug states

- · Handler and Thread modes

- · Low latency ISR entry and exit

## 7.2 APB/AHB bridge

The SAM3S product embeds one peripheral bridge:

The peripherals of the bridge are clocked by MCK.

### 7.3 Matrix Masters

The Bus Matrix of the SAM3S product manages 4 masters, which means that each master can perform an access concurrently with others, to an available slave.

Each master has its own decoder, which is defined specifically for each master. In order to simplify the addressing, all the masters have the same decodings.

Table 7-1. List of Bus Matrix Masters

| Master 0 | Cortex-M3 Instruction/Data      |

|----------|---------------------------------|

| Master 1 | Cortex-M3 System                |

| Master 2 | Peripheral DMA Controller (PDC) |

| Master 3 | CRC Calculation Unit            |

#### 7.4 Matrix Slaves

The Bus Matrix of the SAM3S product manages 5 slaves. Each slave has its own arbiter, allowing a different arbitration per slave.

Table 7-2. List of Bus Matrix Slaves

| Slave 0 | Internal SRAM          |

|---------|------------------------|

| Slave 1 | Internal ROM           |

| Slave 2 | Internal Flash         |

| Slave 3 | External Bus Interface |

| Slave 4 | Peripheral Bridge      |

### 9. Memories

#### 9.1 Embedded Memories

#### 9.1.1 Internal SRAM

The ATSAM3S4 product (256-Kbyte internal Flash version) embeds a total of 48 Kbytes high-speed SRAM.

The ATSAM3S2 product (128-Kbyte internal Flash version) embeds a total of 32 Kbytes high-speed SRAM.

The ATSAM3S1 product (64-Kbyte internal Flash version) embeds a total of 16 Kbytes high-speed SRAM.

The SRAM is accessible over System Cortex-M3 bus at address 0x2000 0000.

The SRAM is in the bit band region. The bit band alias region is mapped from 0x2200 0000 to 0x23FF FFFF.

#### 9.1.2 Internal ROM

The SAM3S product embeds an Internal ROM, which contains the SAM Boot Assistant (SAM-BA), In Application Programming routines (IAP) and Fast Flash Programming Interface (FFPI).

At any time, the ROM is mapped at address 0x0080 0000.

#### 9.1.3 Embedded Flash

#### 9.1.3.1 Flash Overview

The Flash of the ATSAM3S4 (256-Kbytes internal Flash version) is organized in one bank of 1024 pages (Single plane) of 256 bytes.

The Flash of the ATSAM3S2 (128-Kbytes internal Flash version) is organized in one bank of 512 pages (Single plane) of 256 bytes.

The Flash of the ATSAM3S1 (64-Kbytes internal Flash version) is organized in one bank of 256 pages (Single plane) of 256 bytes.

The Flash contains a 128-byte write buffer, accessible through a 32-bit interface.

## 9.1.3.2 Flash Power Supply

The Flash is supplied by VDDCORE.

#### 9.1.3.3 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller (EEFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped on the APB.

The Enhanced Embedded Flash Controller ensures the interface of the Flash block with the 32-bit internal bus. Its 128-bit wide memory interface increases performance.

The user can choose between high performance or lower current consumption by selecting either 128-bit or 64-bit access. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands.

One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash organization, thus making the software generic.

#### 9.1.3.4 Flash Speed

The user needs to set the number of wait states depending on the frequency used.

For more details, refer to the AC Characteristics sub section in the product Electrical Characteristics Section.

#### 9.1.3.5 Lock Regions

Several lock bits used to protect write and erase operations on lock regions. A lock region is composed of several consecutive pages, and each lock region has its associated lock bit.

Table 9-1. Number of Lock Bits

| Product  | Number of Lock Bits    | Lock Region Size     |

|----------|------------------------|----------------------|

| ATSAM3S4 | 16                     | 16 kbytes (64 pages) |

| ATSAM3S2 | 8 16 kbytes (64 pages) |                      |

| ATSAM3S1 | 4                      | 16 kbytes (64 pages) |

If a locked-region's erase or program command occurs, the command is aborted and the EEFC triggers an interrupt.

The lock bits are software programmable through the EEFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

#### 9.1.3.6 Security Bit Feature

The SAM3S features a security bit, based on a specific General Purpose NVM bit (GPNVM bit 0). When the security is enabled, any access to the Flash, SRAM, Core Registers and Internal Peripherals either through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled, through the command "Set General Purpose NVM Bit 0" of the EEFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, and after a full Flash erase is performed. When the security bit is deactivated, all accesses to the Flash, SRAM, Core registers, Internal Peripherals are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 200 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.

#### 9.1.3.7 Calibration Bits

NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

#### 9.1.3.8 Unique Identifier

Each device integrates its own 128-bit unique identifier. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the unique identifier.

- Asynchronous read in Page Mode supported (4- up to 32-byte page size)

- Multiple device adaptability

- Control signals programmable setup, pulse and hold time for each Memory Bank

- Multiple Wait State Management

- Programmable Wait State Generation

- External Wait Request

- Programmable Data Float Time

- Slow Clock mode supported

- Additional Logic for NAND Flash

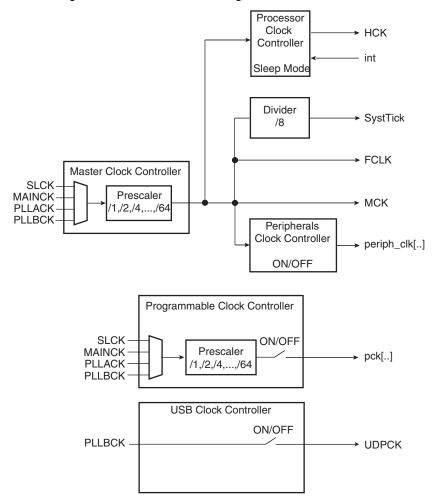

Figure 10-3. SAM3S Power Management Controller Block Diagram

The SysTick calibration value is fixed at 8000 which allows the generation of a time base of 1 ms with SystTick clock at 8 MHz (max HCLK/8 = 64 MHz/8).

## 10.7 Watchdog Timer

- 16-bit key-protected only-once-Programmable Counter

- Windowed, prevents the processor to be in a dead-lock on the watchdog access.

### 10.8 SysTick Timer

- 24-bit down counter

- · Self-reload capability

- Flexible System timer

#### 10.9 Real Time Timer

- Real Time Timer, allowing backup of time with different accuracies

- 32-bit free-running back-up counter

- Integrates a 16-bit programmable prescaler running on slow clock

## 11.2 Peripheral Signal Multiplexing on I/O Lines

The SAM3S product features 2 PIO controllers on 48-pin and 64-pin versions (PIOA, PIOB) or 3 PIO controllers on the 100-pin version, (PIOA, PIOB, PIOC), that multiplex the I/O lines of the peripheral set.

The SAM3S 64-pin and 100-pin PIO Controllers control up to 32 lines. (See, Table 10-2.) Each line can be assigned to one of three peripheral functions: A, B or C. The multiplexing tables in the following pages define how the I/O lines of the peripherals A, B and C are multiplexed on the PIO Controllers. The column "Comments" has been inserted in this table for the user's own comments; it may be used to track how pins are defined in an application.

Note that some peripheral functions which are output only, might be duplicated within the tables.

## 11.2.2 PIO Controller B Multiplexing

Table 11-3.

Multiplexing on PIO Controller B (PIOB)

| I/O Line | Peripheral A | Peripheral B | Peripheral C | Extra Function | System Function | Comments            |

|----------|--------------|--------------|--------------|----------------|-----------------|---------------------|

| PB0      | PWMH0        |              |              | AD4            |                 |                     |

| PB1      | PWMH1        |              |              | AD5            |                 |                     |

| PB2      | URXD1        | NPCS2        |              | AD6/ WKUP12    |                 |                     |

| PB3      | UTXD1        | PCK2         |              | AD7            |                 |                     |

| PB4      | TWD1         | PWMH2        |              |                | TDI             |                     |

| PB5      | TWCK1        | PWML0        |              | WKUP13         | TDO/TRACESWO    |                     |

| PB6      |              |              |              |                | TMS/SWDIO       |                     |

| PB7      |              |              |              |                | TCK/SWCLK       |                     |

| PB8      |              |              |              |                | XOUT            |                     |

| PB9      |              |              |              |                | XIN             |                     |

| PB10     |              |              |              |                | DDM             |                     |

| PB11     |              |              |              |                | DDP             |                     |

| PB12     | PWML1        |              |              |                | ERASE           |                     |

| PB13     | PWML2        | PCK0         |              | DAC0           |                 | 64/100-pin versions |

| PB14     | NPCS1        | PWMH3        |              | DAC1           |                 | 64/100-pin versions |

- Interval Measurement

- Pulse Generation

- Delay Timing

- Pulse Width Modulation

- Up/down Capabilities

- Each channel is user-configurable and contains:

- Three external clock inputs

- Five internal clock inputs

- Two multi-purpose input/output signals

- Two global registers that act on all three TC Channels

- · Quadrature decoder

- Advanced line filtering

- Position / revolution / speed

- 2-bit Gray Up/Down Counter for Stepper Motor

## 12.7 Pulse Width Modulation Controller (PWM)

- One Four-channel 16-bit PWM Controller, 16-bit counter per channel

- Common clock generator, providing Thirteen Different Clocks

- A Modulo n counter providing eleven clocks

- Two independent Linear Dividers working on modulo n counter outputs

- High Frequency Asynchronous clocking mode

- Independent channel programming

- Independent Enable Disable Commands

- Independent Clock Selection

- Independent Period and Duty Cycle, with Double Buffering

- Programmable selection of the output waveform polarity

- Programmable center or left aligned output waveform

- Independent Output Override for each channel

- Independent complementary Outputs with 12-bit dead time generator for each channel

- Independent Enable Disable Commands

- Independent Clock Selection

- Independent Period and Duty Cycle, with Double Buffering

- Synchronous Channel mode

- Synchronous Channels share the same counter

- Mode to update the synchronous channels registers after a programmable number of periods

- Connection to one PDC channel

- Offers Buffer transfer without Processor Intervention, to update duty cycle of synchronous channels

- independent event lines which can send up to 4 triggers on ADC within a period

- Programmable Fault Input providing an asynchronous protection of outputs

- Stepper motor control (2 Channels)

## 12.8 High Speed Multimedia Card Interface (HSMCI)

- 4-bit or 1-bit Interface

- Compatibility with MultiMedia Card Specification Version 4.3

- Compatibility with SD and SDHC Memory Card Specification Version 2.0

- Compatibility with SDIO Specification Version V1.1.

- Compatibility with CE-ATA Specification 1.1

- · Cards clock rate up to Master Clock divided by 2

- Boot Operation Mode support

- High Speed mode support

- Embedded power management to slow down clock rate when not used

- HSMCI has one slot supporting

- One MultiMediaCard bus (up to 30 cards) or

- One SD Memory Card

- One SDIO Card

- Support for stream, block and multi-block data read and write

### 12.9 USB Device Port (UDP)

- USB V2.0 full-speed compliant, 12 Mbits per second.

- Embedded USB V2.0 full-speed transceiver

- Embedded 2688-byte dual-port RAM for endpoints

- · Eight endpoints

- Endpoint 0: 64 bytes

- Endpoint 1 and 2: 64 bytes ping-pong

- Endpoint 3: 64 bytes

- Endpoint 4 and 5: 512 bytes ping-pong

- Endpoint 6 and 7: 64 bytes ping-pong

- Ping-pong Mode (two memory banks) for Isochronous and bulk endpoints

- Suspend/resume logic

- Integrated Pull-up on DDP

- Pull-down resistor on DDM and DDP when disabled

## 12.10 Analog-to-Digital Converter (ADC)

- up to 16 Channels,

- 10/12-bit resolution

- up to 1 MSample/s

- programmable sequence of conversion on each channel

- · Integrated temperature sensor

- Single ended/differential conversion

- output selection:

- Internal signal

- external pin

- selectable inverter

- Interrupt on:

- Rising edge, Falling edge, toggle

## 12.14 Cyclic Redundancy Check Calculation Unit (CRCCU)

- 32-bit cyclic redundancy check automatic calculation

- CRC calculation between two addresses of the memory

## 13. Package Drawings

The SAM3S series devices are available in LQFP, QFN and LFBGA packages.

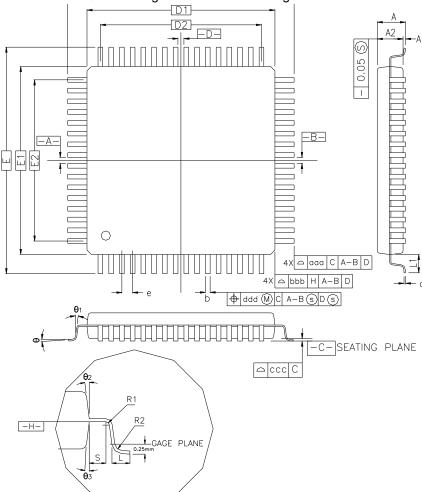

Figure 13-1. 100-lead LQFP Package Mechanical Drawing

| COTROL         | DIMENS    | IONS A   | RE IN     | MILLIM     | ETERS. |     |

|----------------|-----------|----------|-----------|------------|--------|-----|

| CVALDO         | М         | ILLIMETI | INCH      |            |        |     |

| SYMBOL         | MIN.      | NOM.     | MAX.      | MIN.       | NOM.   | ١   |

| А              | _         |          | 1.60      | _          | _      | 0   |

| A1             | 0.05      |          | 0.15      | 0.002      | _      | 0   |

| A2             | 1.35      | 1.40     | 1.45      | 0.053      | 0.055  | 0   |

| D              | 1         | 6.00 B   | 0.630 BSC |            |        |     |

| D1             | 1         | 4.00 B   | 0.551 BSC |            |        |     |

| Е              | 1         | 5.00 B   | 0.630 BSC |            |        |     |

| E1             | 1-        | 4.00 B   | 0.551 BSC |            |        |     |

| R <sub>2</sub> | 0.08      | _        | 0.20      | 0.003      | _      | 0   |

| R <sub>1</sub> | 0.08      |          | _         | 0.003      | _      | Γ.  |

| Θ              | 0.        | 3.5°     | 7*        | 0.         | 3.5°   |     |

| Θ1             | 0,        |          | _         | 0.         | _      | Γ.  |

| θг             | 11*       | 12*      | 13°       | 1 1°       | 12*    | Γ   |

| θз             | 11'       | 12*      | 13°       | 1 1°       | 12*    | Γ   |

| С              | 0.09      |          | 0.20      | 0.004      | _      | 0   |

| L              | 0.45      | 0.60     | 0.75      | 0.018      | 0.024  | 0   |

| L <sub>1</sub> | 1.00 REF  |          |           | 0.039 REF  |        |     |

| S              | 0.20      | _        | _         | 0.008      | _      |     |

| Ь              | 0.17      | 0.20     | 0.27      | 0.007      | 0.008  | C   |

| е              | 0.50 BSC. |          |           | 0.020 BSC. |        |     |

| D2             | 12.00     |          |           | 0.472      |        |     |

| E2             | 12.00     |          |           | 0.472      |        |     |

|                | TOLERA    | NCES     | OF FO     | RM AND     | POSIT  | ſΙC |

| aaa            |           | 0.20     |           | 0.008      |        |     |

| bbb            |           | 0.20     |           | 0.008      |        |     |

| ССС            | 0.08      |          |           | 0.003      |        |     |

Note: 1. This drawing is for general information only. Refer to JEDEC Drawing MS-026 for additional information.

Figure 13-2. 100-ball LFBGA Package Drawing

# 14. Ordering Information

Table 14-1. Ordering Codes for SAM3S Devices

| Ordering Code | MRL | Flash<br>(Kbytes) | Package (Kbytes) | Package Type | Temperature<br>Operating Range |

|---------------|-----|-------------------|------------------|--------------|--------------------------------|

| ATSAM3S4CA-AU | А   | 256               | QFP100           | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S4CA-CU | Α   | 256               | BGA100           | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S4BA-AU | А   | 256               | QFP64            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S4BA-MU | Α   | 256               | QFN64            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S4AA-AU | Α   | 256               | QFP48            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S4AA-MU | А   | 256               | QFN48            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S2CA-AU | А   | 128               | QFP100           | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S2CA-CU | А   | 128               | BGA100           | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S2BA-AU | А   | 128               | QFP64            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S2BA-MU | Α   | 128               | QFN64            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S2AA-AU | Α   | 128               | QFP48            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S2AA-MU | А   | 128               | QFN48            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S1CA-AU | А   | 64                | QFP100           | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S1CA-CU | А   | 64                | BGA100           | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S1BA-AU | Α   | 64                | QFP64            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S1BA-MU | А   | 64                | QFN64            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S1AA-AU | Α   | 64                | QFP48            | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3S1AA-MU | Α   | 64                | QFN48            | Green        | Industrial<br>-40°C to 85°C    |

### Headquarters

Atmel Corporation

2325 Orchard Parkway San Jose, CA 95131 USA

Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

#### International

Atmel Asia

Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong

Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe

Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France

Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11 Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site

www.atmel.com www.atmel.com/AT91SAM **Technical Support**AT91SAM Support

Atmel technical support

Sales Contacts

www.atmel.com/contacts/

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2011 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, SAM-BA<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM<sup>®</sup>, ARM<sup>®</sup>Powered logo, Cortex<sup>®</sup>, Thumb<sup>®</sup>-2 and others are registered trademarks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.