Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 64MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, MMC, SPI, SSC, UART/USART, USB                        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT            |

| Number of I/O              | 34                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 48K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                            |

| Data Converters            | A/D 8x10/12b                                                            |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 48-QFN (7×7)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam3s4aa-mu |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

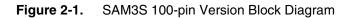

# 2. SAM3S Block Diagram

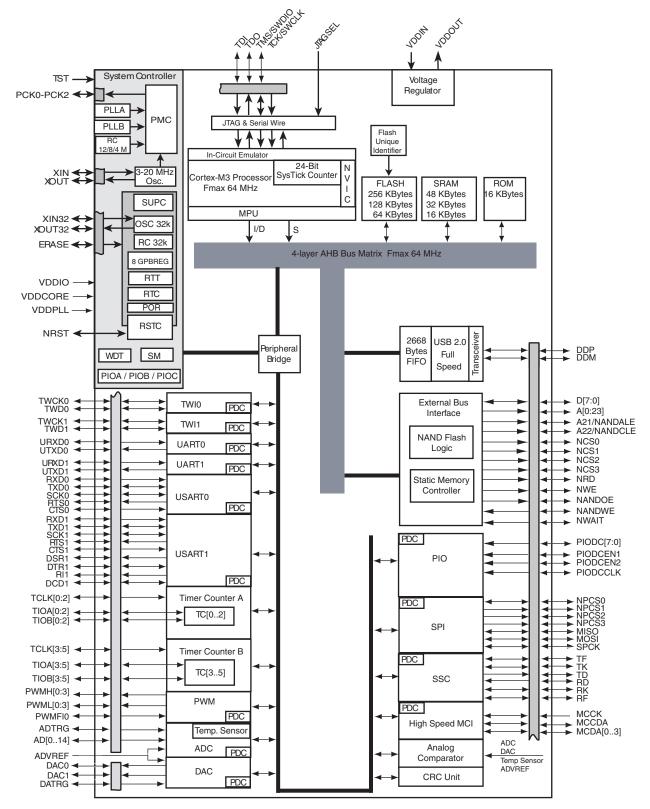

Figure 2-2. SAM3S 64-pin Version Block Diagram

SAM3S Summary

4

# Table 3-1. Signal Description List (Continued)

| Signal Name                                 | Function                                    | Туре               | Active<br>Level | Voltage reference | Comments                                                                       |

|---------------------------------------------|---------------------------------------------|--------------------|-----------------|-------------------|--------------------------------------------------------------------------------|

|                                             | Synchronous Seri                            | al Controller      | - SSC           |                   |                                                                                |

| TD                                          | SSC Transmit Data                           | Output             |                 |                   |                                                                                |

| RD                                          | SSC Receive Data                            | Input              |                 |                   |                                                                                |

| ТК                                          | SSC Transmit Clock                          | I/O                |                 |                   |                                                                                |

| RK                                          | SSC Receive Clock                           | I/O                |                 |                   |                                                                                |

| TF                                          | SSC Transmit Frame Sync                     | I/O                |                 |                   |                                                                                |

| RF                                          | SSC Receive Frame Sync                      | I/O                |                 |                   |                                                                                |

|                                             | Timer/Co                                    | unter - TC         |                 |                   |                                                                                |

| TCLKx                                       | TC Channel x External Clock Input           | Input              |                 |                   |                                                                                |

| TIOAx                                       | TC Channel x I/O Line A                     | I/O                |                 |                   |                                                                                |

| TIOBx                                       | TC Channel x I/O Line B                     | I/O                |                 |                   |                                                                                |

|                                             | Pulse Width Modulati                        | on Controlle       | er- PWMC        |                   |                                                                                |

| PWMHx                                       | PWM Waveform Output High for channel x      | Output             |                 |                   |                                                                                |

| PWMLx PWM Waveform Output Low for channel x |                                             | Output             |                 |                   | only output in<br>complementary mode when<br>dead time insertion is<br>enabled |

| PWMFI0                                      | PWM Fault Input                             | Input              |                 |                   |                                                                                |

|                                             | Serial Periphera                            | Interface -        | SPI             |                   |                                                                                |

| MISO                                        | Master In Slave Out                         | I/O                |                 |                   |                                                                                |

| MOSI                                        | Master Out Slave In                         | I/O                |                 |                   |                                                                                |

| SPCK                                        | SPI Serial Clock                            | I/O                |                 |                   |                                                                                |

| SPI_NPCS0                                   | SPI Peripheral Chip Select 0                | I/O                | Low             |                   |                                                                                |

| SPI_NPCS1 -<br>SPI_NPCS3                    | SPI Peripheral Chip Select                  | Output             | Low             |                   |                                                                                |

|                                             | Two-Wire In                                 | terface- TWI       |                 |                   |                                                                                |

| TWDx                                        | TWIx Two-wire Serial Data                   | I/O                |                 |                   |                                                                                |

| TWCKx                                       | TWIx Two-wire Serial Clock                  | I/O                |                 |                   |                                                                                |

|                                             | Ana                                         | log                |                 |                   |                                                                                |

| ADVREF                                      | ADC, DAC and Analog Comparator<br>Reference | Analog             |                 |                   |                                                                                |

|                                             | Analog-to-Digital                           | Converter -        | ADC             | 1                 |                                                                                |

| AD0 - AD14                                  | Analog Inputs                               | Analog,<br>Digital |                 |                   |                                                                                |

| ADTRG                                       | ADC Trigger                                 | Input              |                 | VDDIO             |                                                                                |

|                                             | 12-bit Digital-to-Ana                       | log Converte       | er - DAC        |                   |                                                                                |

| DAC0 - DAC1                                 | Analog output                               | Analog,<br>Digital |                 |                   |                                                                                |

| DACTRG                                      | DAC Trigger                                 | Input              |                 | VDDIO             |                                                                                |

#### 4.3.1 48-Lead LQFP and QFN Pinout

| 1  | ADVREF             | 13 | VDDIO                           |   | 25 | TDI/PB4     | 37 | TDO/TRACESWO/<br>PB5 |

|----|--------------------|----|---------------------------------|---|----|-------------|----|----------------------|

| 2  | GND                | 14 | PA16/PGMD4                      | 1 | 26 | PA6/PGMNOE  | 38 | JTAGSEL              |

| 3  | PB0/AD4            | 15 | PA15/PGMD3                      | [ | 27 | PA5/PGMRDY  | 39 | TMS/SWDIO/PB6        |

| 4  | PB1/AD5            | 16 | PA14/PGMD2                      | [ | 28 | PA4/PGMNCMD | 40 | TCK/SWCLK/PB7        |

| 5  | PB2/AD6            | 17 | PA13/PGMD1                      | 1 | 29 | NRST        | 41 | VDDCORE              |

| 6  | PB3/AD7            | 18 | VDDCORE                         | 1 | 30 | TST         | 42 | ERASE/PB12           |

| 7  | VDDIN              | 19 | PA12/PGMD0                      | 1 | 31 | PA3         | 43 | DDM/PB10             |

| 8  | VDDOUT             | 20 | PA11/PGMM3                      | 1 | 32 | PA2/PGMEN2  | 44 | DDP/PB11             |

| 9  | PA17/PGMD5/<br>AD0 | 21 | PA10/PGMM2                      |   | 33 | VDDIO       | 45 | XOUT/PB8             |

| 10 | PA18/PGMD6/<br>AD1 | 22 | PA9/PGMM1                       |   | 34 | GND         | 46 | XIN/PB9/PGMCK        |

| 11 | PA19/PGMD7/<br>AD2 | 23 | PA8/ <i>XOUT32/</i><br>PGMM0    |   | 35 | PA1/PGMEN1  | 47 | VDDIO                |

| 12 | PA20/AD3           | 24 | PA7/ <i>XIN32/</i><br>PGMNVALID |   | 36 | PA0/PGMEN0  | 48 | VDDPLL               |

### Table 4-4.48-pin SAM3S4/2/1A Pinout

Note: The bottom pad of the QFN package must be connected to ground.

# 5. Power Considerations

# 5.1 Power Supplies

The SAM3S product has several types of power supply pins:

- VDDCORE pins: Power the core, the embedded memories and the peripherals; voltage ranges from 1.62V and 1.95V.

- VDDIO pins: Power the Peripherals I/O lines (Input/Output Buffers); USB transceiver; Backup part, 32kHz crystal oscillator and oscillator pads; ranges from 1.62V and 3.6V

- VDDIN pin: Voltage Regulator Input, ADC, DAC and Analog Comparator Power Supply; Voltage ranges from 1.8V to 3.6V

- VDDPLL pin: Powers the PLLA, PLLB, the Fast RC and the 3 to 20 MHz oscillator; voltage ranges from 1.62V and 1.95V.

# 5.2 Voltage Regulator

The SAM3S embeds a voltage regulator that is managed by the Supply Controller.

This internal regulator is intended to supply the internal core of SAM3S. It features two different operating modes:

In Normal mode, the voltage regulator consumes less than 700 µA static current and draws 80 mA of output current. Internal adaptive biasing adjusts the regulator quiescent current depending on the required load current. In Wait Mode quiescent current is only 7 µA.

• In Backup mode, the voltage regulator consumes less than 1  $\mu$ A while its output (VDDOUT) is driven internally to GND. The default output voltage is 1.80V and the start-up time to reach Normal mode is inferior to 100  $\mu$ s.

For adequate input and output power supply decoupling/bypassing, refer to the Voltage Regulator section in the Electrical Characteristics section of the datasheet.

# 5.3 Typical Powering Schematics

The SAM3S supports a 1.62V-3.6V single supply mode. The internal regulator input connected to the source and its output feeds VDDCORE. Figure 5-1 shows the power schematics.

As VDDIN powers the voltage regulator, the ADC/DAC and the analog comparator, when the user does not want to use the embedded voltage regulator, it can be disabled by software via the SUPC (note that it is different from Backup mode).

- WKUPEN0-15 pins (level transition, configurable debouncing)

- Supply Monitor alarm

- RTC alarm

- RTT alarm

#### 5.5.2 Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of less than 10  $\mu$ s. Current Consumption in Wait mode is typically 15  $\mu$ A (total current consumption) if the internal voltage regulator is used or 8  $\mu$ A if an external regulator is used.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC\_FSMR). The Cortex-M3 is able to handle external events or internal events in order to wake-up the core (WFE). This is done by configuring the external lines WUP0-15 as fast startup wake-up pins (refer to Section 5.7 "Fast Startup"). RTC or RTT Alarm and USB wake-up events can be used to wake up the CPU (exit from WFE).

#### Entering Wait Mode:

- Select the 4/8/12 MHz fast RC oscillator as Main Clock

- Set the LPM bit in the PMC Fast Startup Mode Register (PMC\_FSMR)

- Execute the Wait-For-Event (WFE) instruction of the processor

- Note: Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to ensure that the core will not execute undesired instructions.

#### 5.5.3 Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode, only the core clock is stopped. The peripheral clocks can be enabled. The current consumption in this mode is application dependent.

This mode is entered via Wait for Interrupt (WFI) or Wait for Event (WFE) instructions with LPM = 0 in PMC\_FSMR.

The processor can be woke up from an interrupt if WFI instruction of the Cortex M3 is used, or from an event if the WFE instruction is used to enter this mode.

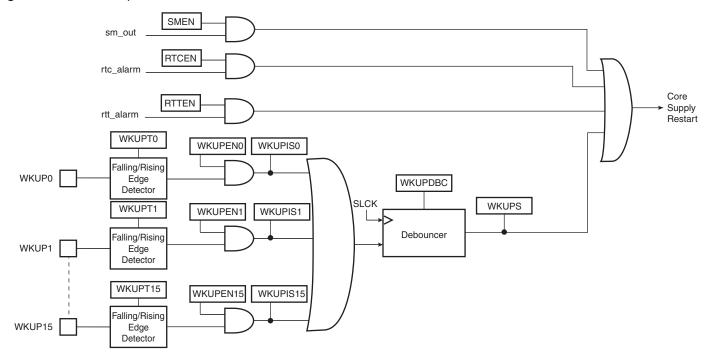

## 5.6 Wake-up Sources

The wake-up events allow the device to exit the backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power supply and the SRAM power supply, if they are not already enabled.

#### Figure 5-4. Wake-up Source

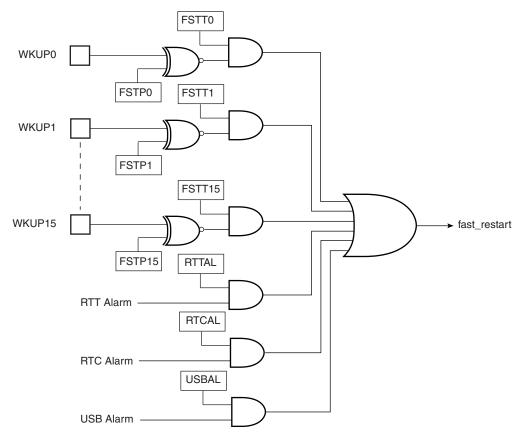

# 5.7 Fast Startup

The device allows the processor to restart in a few microseconds while the processor is in wait mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs (WKUP0 to 15 + SM + RTC + RTT).

The fast restart circuitry, as shown in Figure 5-5, is fully asynchronous and provides a fast startup signal to the Power Management Controller. As soon as the fast start-up signal is asserted, the PMC automatically restarts the embedded 4/8/12 MHz fast RC oscillator, switches the master clock on this 4MHz clock and reenables the processor clock.

Figure 5-5. Fast Start-Up Circuitry

# **SAM3S Summary**

| SYSTEM_IO<br>bit number | Default function<br>after reset | Other function | Constraints for<br>normal start     | Configuration                                                                                            |

|-------------------------|---------------------------------|----------------|-------------------------------------|----------------------------------------------------------------------------------------------------------|

| 12                      | ERASE                           | PB12           | Low Level at startup <sup>(1)</sup> |                                                                                                          |

| 10                      | DDM                             | PB10           | -                                   |                                                                                                          |

| 11                      | DDP                             | PB11           | -                                   | In Matrix User Interface Registers                                                                       |

| 7                       | TCK/SWCLK                       | PB7            | -                                   | (Refer to the SystemIO Configuration<br>Register in the Bus Matrix section of<br>the product datasheet.) |

| 6                       | TMS/SWDIO                       | PB6            | -                                   |                                                                                                          |

| 5                       | TDO/TRACESWO                    | PB5            | -                                   |                                                                                                          |

| 4                       | TDI                             | PB4            | -                                   |                                                                                                          |

| -                       | PA7                             | XIN32          | -                                   | On a factor sta (2) history                                                                              |

| -                       | PA8                             | XOUT32         | -                                   | See footnote <sup>(2)</sup> below                                                                        |

| -                       | PB9                             | XIN            | -                                   | On a factorista (3) halans                                                                               |

| -                       | PB8                             | XOUT           | -                                   | See footnote <sup>(3)</sup> below                                                                        |

#### Table 6-1. System I/O Configuration Pin List.

Notes: 1. If PB12 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PB12 into PIO mode,

- 2. In the product Datasheet Refer to: Slow Clock Generator of the Supply Controller section.

- 3. In the product Datasheet Refer to: 3 to 20 MHZ Crystal Oscillator information in PMC section.

#### 6.2.1 Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/SWO, TDI and commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 3-1 on page 6.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer to the Debug and Test Section of the product datasheet.

SWJ-DP pins can be used as standard I/Os to provide users more general input/output pins when the debug port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX\_SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to the Debug and Test Section.

# 6.3 Test Pin

The TST pin is used for JTAG Boundary Scan Manufacturing Test or Fast Flash programming mode of the SAM3S series. The TST pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations. To enter fast programming mode, see the Fast Flash Programming Interface (FFPI) section. For more on the manufacturing and test mode, refer to the "Debug and Test" section of the product datasheet.

## 6.4 NRST Pin

The NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. It will reset the Core and the peripherals except the Backup region (RTC, RTT and Supply Controller). There is no constraint on the length of the reset pulse and the reset controller can guarantee a minimum pulse length. The NRST pin integrates a permanent pull-up resistor to VDDIO of about 100 k $\Omega$ . By default, the NRST pin is configured as an input.

## 6.5 ERASE Pin

The ERASE pin is used to reinitialize the Flash content (and some of its NVM bits) to an erased state (all bits read as logic level 1). It integrates a pull-down resistor of about 100 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

This pin is debounced by SCLK to improve the glitch tolerance. When the ERASE pin is tied high during less than 100 ms, it is not taken into account. The pin must be tied high during more than 220 ms to perform a Flash erase operation.

The ERASE pin is a system I/O pin and can be used as a standard I/O. At startup, the ERASE pin is not configured as a PIO pin. If the ERASE pin is used as a standard I/O, startup level of this pin must be low to prevent unwanted erasing. Please refer to Section 11.2 "Peripheral Signal Multiplexing on I/O Lines" on page 43. Also, if the ERASE pin is used as a standard I/O output, asserting the pin to low does not erase the Flash.

# 7.5 Master to Slave Access

All the Masters can normally access all the Slaves. However, some paths do not make sense, for example allowing access from the Cortex-M3 S Bus to the Internal ROM. Thus, these paths are forbidden or simply not wired and shown as "-" in the following table.

|        | Masters                | 0                    | 1                  | 2   | 3     |

|--------|------------------------|----------------------|--------------------|-----|-------|

| Slaves |                        | Cortex-M3 I/D<br>Bus | Cortex-M3 S<br>Bus | PDC | CRCCU |

| 0      | Internal SRAM          | -                    | Х                  | Х   | Х     |

| 1      | Internal ROM           | х                    | -                  | Х   | Х     |

| 2      | Internal Flash         | х                    | -                  | -   | Х     |

| 3      | External Bus Interface | -                    | Х                  | Х   | Х     |

| 4      | Peripheral Bridge      | -                    | Х                  | Х   | -     |

Table 7-3. SAM3S Master to Slave Access

# 7.6 Peripheral DMA Controller

- Handles data transfer between peripherals and memories

- Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- Next Pointer management for reducing interrupt latency requirement

The Peripheral DMA Controller handles transfer requests from the channel according to the following priorities (Low to High priorities):

| Table 7-4. | Peripheral DMA Controller |

|------------|---------------------------|

|------------|---------------------------|

| Instance Name | Channel T/R | 100 & 64 Pins | 48 Pins |

|---------------|-------------|---------------|---------|

| PWM           | Transmit    | x             | х       |

| TWI1          | Transmit    | x             | х       |

| TWIO          | Transmit    | x             | х       |

| UART1         | Transmit    | x             | х       |

| UART0         | Transmit    | x             | х       |

| USART1        | Transmit    | x             | N/A     |

| USART0        | Transmit    | x             | х       |

| DAC           | Transmit    | x             | N/A     |

| SPI           | Transmit    | x             | х       |

| SSC           | Transmit    | x             | х       |

| HSMCI         | Transmit    | x             | N/A     |

| PIOA          | Transmit    | x             | х       |

| TWI1          | Receive     | x             | x       |

| TWIO          | Receive     | x             | х       |

| UART1         | Receive     | x             | N/A     |

# **SAM3S Summary**

# 9. Memories

# 9.1 Embedded Memories

#### 9.1.1 Internal SRAM

The ATSAM3S4 product (256-Kbyte internal Flash version) embeds a total of 48 Kbytes high-speed SRAM.

The ATSAM3S2 product (128-Kbyte internal Flash version) embeds a total of 32 Kbytes highspeed SRAM.

The ATSAM3S1 product (64-Kbyte internal Flash version) embeds a total of 16 Kbytes high-speed SRAM.

The SRAM is accessible over System Cortex-M3 bus at address 0x2000 0000.

The SRAM is in the bit band region. The bit band alias region is mapped from 0x2200 0000 to 0x23FF FFFF.

#### 9.1.2 Internal ROM

The SAM3S product embeds an Internal ROM, which contains the SAM Boot Assistant (SAM-BA), In Application Programming routines (IAP) and Fast Flash Programming Interface (FFPI).

At any time, the ROM is mapped at address 0x0080 0000.

#### 9.1.3 Embedded Flash

#### 9.1.3.1 Flash Overview

The Flash of the ATSAM3S4 (256-Kbytes internal Flash version) is organized in one bank of 1024 pages (Single plane) of 256 bytes.

The Flash of the ATSAM3S2 (128-Kbytes internal Flash version) is organized in one bank of 512 pages (Single plane) of 256 bytes.

The Flash of the ATSAM3S1 (64-Kbytes internal Flash version) is organized in one bank of 256 pages (Single plane) of 256 bytes.

The Flash contains a 128-byte write buffer, accessible through a 32-bit interface.

### 9.1.3.2 Flash Power Supply

The Flash is supplied by VDDCORE.

#### 9.1.3.3 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller (EEFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped on the APB.

The Enhanced Embedded Flash Controller ensures the interface of the Flash block with the 32bit internal bus. Its 128-bit wide memory interface increases performance.

The user can choose between high performance or lower current consumption by selecting either 128-bit or 64-bit access. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands.

- Asynchronous read in Page Mode supported (4- up to 32-byte page size)

- Multiple device adaptability

- Control signals programmable setup, pulse and hold time for each Memory Bank

- Multiple Wait State Management

- Programmable Wait State Generation

- External Wait Request

- Programmable Data Float Time

- Slow Clock mode supported

- Additional Logic for NAND Flash

# 11.2.3 PIO Controller C Multiplexing

| Table 11-4. | Multiplexing on | PIO Controller C | (PIOC)       |                |                 |                 |

|-------------|-----------------|------------------|--------------|----------------|-----------------|-----------------|

| I/O Line    | Peripheral A    | Peripheral B     | Peripheral C | Extra Function | System Function | Comments        |

| PC0         | D0              | PWML0            |              |                |                 | 100-pin version |

| PC1         | D1              | PWML1            |              |                |                 | 100-pin version |

| PC2         | D2              | PWML2            |              |                |                 | 100-pin version |

| PC3         | D3              | PWML3            |              |                |                 | 100-pin version |

| PC4         | D4              | NPCS1            |              |                |                 | 100-pin version |

| PC5         | D5              |                  |              |                |                 | 100-pin version |

| PC6         | D6              |                  |              |                |                 | 100-pin version |

| PC7         | D7              |                  |              |                |                 | 100-pin version |

| PC8         | NWE             |                  |              |                |                 | 100-pin version |

| PC9         | NANDOE          |                  |              |                |                 | 100-pin version |

| PC10        | NANDWE          |                  |              |                |                 | 100-pin version |

| PC11        | NRD             |                  |              |                |                 | 100-pin version |

| PC12        | NCS3            |                  |              | AD12           |                 | 100-pin version |

| PC13        | NWAIT           | PWML0            |              | AD10           |                 | 100-pin version |

| PC14        | NCS0            |                  |              |                |                 | 100-pin version |

| PC15        | NCS1            | PWML1            |              | AD11           |                 | 100-pin version |

| PC16        | A21/NANDALE     |                  |              |                |                 | 100-pin version |

| PC17        | A22/NANDCLE     |                  |              |                |                 | 100-pin version |

| PC18        | A0              | PWMH0            |              |                |                 | 100-pin version |

| PC19        | A1              | PWMH1            |              |                |                 | 100-pin version |

| PC20        | A2              | PWMH2            |              |                |                 | 100-pin version |

| PC21        | A3              | PWMH3            |              |                |                 | 100-pin version |

| PC22        | A4              | PWML3            |              |                |                 | 100-pin version |

| PC23        | A5              | TIOA3            |              |                |                 | 100-pin version |

| PC24        | A6              | TIOB3            |              |                |                 | 100-pin version |

| PC25        | A7              | TCLK3            |              |                |                 | 100-pin version |

| PC26        | A8              | TIOA4            |              |                |                 | 100-pin version |

| PC27        | A9              | TIOB4            |              |                |                 | 100-pin version |

| PC28        | A10             | TCLK4            |              |                |                 | 100-pin version |

| PC29        | A11             | TIOA5            |              | AD13           |                 | 100-pin version |

| PC30        | A12             | TIOB5            |              | AD14           |                 | 100-pin version |

| PC31        | A13             | TCLK5            |              |                |                 | 100-pin version |

| I           | l               | l                | 1            | 1              | 1               |                 |

Table 11-4.

Multiplexing on PIO Controller C (PIOC)

# 12.4 Universal Synchronous Asynchronous Receiver Transceiver (USART)

- Programmable Baud Rate Generator with Fractional Baud rate support

- 5- to 9-bit full-duplex synchronous or asynchronous serial communications

- 1, 1.5 or 2 stop bits in Asynchronous Mode or 1 or 2 stop bits in Synchronous Mode

- Parity generation and error detection

- Framing error detection, overrun error detection

- MSB- or LSB-first

- Optional break generation and detection

- By 8 or by-16 over-sampling receiver frequency

- Hardware handshaking RTS-CTS

- Receiver time-out and transmitter timeguard

- Optional Multi-drop Mode with address generation and detection

- Optional Manchester Encoding

- Full modem line support on USART1 (DCD-DSR-DTR-RI)

- RS485 with driver control signal

- ISO7816, T = 0 or T = 1 Protocols for interfacing with smart cards

- NACK handling, error counter with repetition and iteration limit

- SPI Mode

- Master or Slave

- Serial Clock programmable Phase and Polarity

- SPI Serial Clock (SCK) Frequency up to MCK/4

- IrDA modulation and demodulation

- Communication at up to 115.2 Kbps

- Test Modes

- Remote Loopback, Local Loopback, Automatic Echo

# 12.5 Synchronous Serial Controller (SSC)

- Provides serial synchronous communication links used in audio and telecom applications (with CODECs in Master or Slave Modes, I<sup>2</sup>S, TDM Buses, Magnetic Card Reader)

- · Contains an independent receiver and transmitter and a common clock divider

- Offers configurable frame sync and data length

- Receiver and transmitter can be programmed to start automatically or on detection of different event on the frame sync signal

- Receiver and transmitter include a data signal, a clock signal and a frame synchronization signal

# 12.6 Timer Counter (TC)

- Six 16-bit Timer Counter Channels

- Wide range of functions including:

- Frequency Measurement

- Event Counting

- 48 SAM3S Summary

- output selection:

- Internal signal

- external pin

- selectable inverter

- Interrupt on:

- Rising edge, Falling edge, toggle

# 12.14 Cyclic Redundancy Check Calculation Unit (CRCCU)

- 32-bit cyclic redundancy check automatic calculation

- CRC calculation between two addresses of the memory

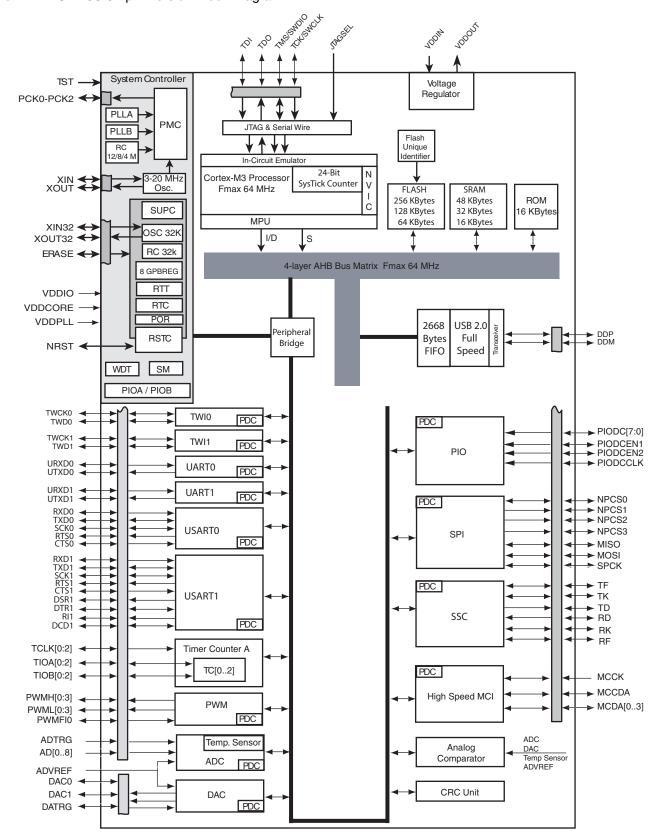

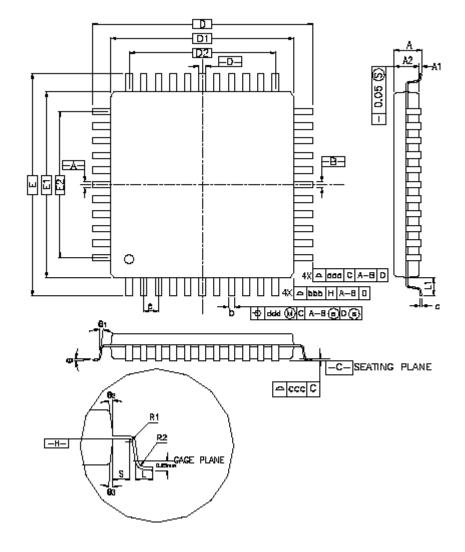

Figure 13-3. 64- and 48-lead LQFP Package Drawing

| O wash at  |      | Millimeter |                |            | Inch      |            |  |  |

|------------|------|------------|----------------|------------|-----------|------------|--|--|

| Symbol     | Min  | Nom        | Мах            | Min        | Nom       | Мах        |  |  |

| А          | -    | _          | 1.60           | _          | _         | 0.063      |  |  |

| A1         | 0.05 | -          | 0.15           | 0.002      | _         | 0.006      |  |  |

| A2         | 1.35 | 1.40       | 1.45           | 0.053      | 0.055     | 0.057      |  |  |

| D          |      | 9.00 BSC   |                |            | 0.354 BSC |            |  |  |

| D1         |      | 7.00 BSC   |                |            | 0.276 BSC |            |  |  |

| E          |      | 9.00 BSC   |                |            | 0.354 BSC |            |  |  |

| E1         |      | 7.00 BSC   |                |            | 0.276 BSC |            |  |  |

| R2         | 0.08 | -          | 0.20           | 0.003      | _         | 0.008      |  |  |

| R1         | 0.08 | -          | _              | 0.003      | _         | _          |  |  |

| q          | 0°   | 3.5°       | 7°             | 0°         | 3.5°      | <b>7</b> ° |  |  |

| $\theta_1$ | 0°   | -          | _              | 0°         | _         | _          |  |  |

| $\theta_2$ | 11°  | 12°        | 13°            | 11°        | 12°       | 13°        |  |  |

| $\theta_3$ | 11°  | 12°        | 13°            | 11°        | 12°       | 13°        |  |  |

| С          | 0.09 | -          | 0.20           | 0.004      | _         | 0.008      |  |  |

| L          | 0.45 | 0.60       | 0.75           | 0.018      | 0.024     | 0.030      |  |  |

| L1         |      | 1.00 REF   |                | 0.039 REF  |           |            |  |  |

| S          | 0.20 | _          | -              | 0.008      | -         | _          |  |  |

| b          | 0.17 | 0.20       | 0.27           | 0.007      | 0.008     | 0.011      |  |  |

| е          |      | 0.50 BSC.  |                | 0.020 BSC. |           |            |  |  |

| D2         |      | 5.50       |                |            | 0.217     |            |  |  |

| E2         |      | 5.50 0.217 |                |            |           |            |  |  |

|            |      | Tolerance  | es of Form and | d Position |           |            |  |  |

| aaa        |      | 0.20       |                |            | 0.008     |            |  |  |

| bbb        |      | 0.20       |                |            | 0.008     |            |  |  |

| ccc        |      | 0.08       |                |            | 0.003     |            |  |  |

| ddd        |      | 0.08       |                |            | 0.003     |            |  |  |

## Table 13-1. 48-lead LQFP Package Dimensions (in mm)

| 0      |      | Millimeter |                |           | Inch      |       |  |

|--------|------|------------|----------------|-----------|-----------|-------|--|

| Symbol | Min  | Nom        | Мах            | Min       | Nom       | Мах   |  |

| А      | _    | _          | 090            | _         | _         | 0.035 |  |

| A1     | _    | _          | 0.050          | _         | _         | 0.002 |  |

| A2     | _    | 0.65       | 0.70           | _         | 0.026     | 0.028 |  |

| A3     |      | 0.20 REF   |                |           | 0.008 REF |       |  |

| b      | 0.18 | 0.20       | 0.23           | 0.007     | 0.008     | 0.009 |  |

| D      |      | 7.00 bsc   |                |           | 0.276 bsc |       |  |

| D2     | 5.45 | 5.60       | 5.75           | 0.215     | 0.220     | 0.226 |  |

| Е      |      | 7.00 bsc   |                | 0.276 bsc |           |       |  |

| E2     | 5.45 | 5.60       | 5.75           | 0.215     | 0.220     | 0.226 |  |

| L      | 0.35 | 0.40       | 0.45           | 0.014     | 0.016     | 0.018 |  |

| е      |      | 0.50 bsc   |                | 0.020 bsc |           |       |  |

| R      | 0.09 | -          | _              | 0.004     | _         | _     |  |

|        |      | Toleranc   | es of Form and | Position  |           |       |  |

| aaa    |      | 0.10       |                |           | 0.004     |       |  |

| bbb    | 0.10 |            |                |           | 0.004     |       |  |

| CCC    |      | 0.05       |                |           | 0.002     |       |  |

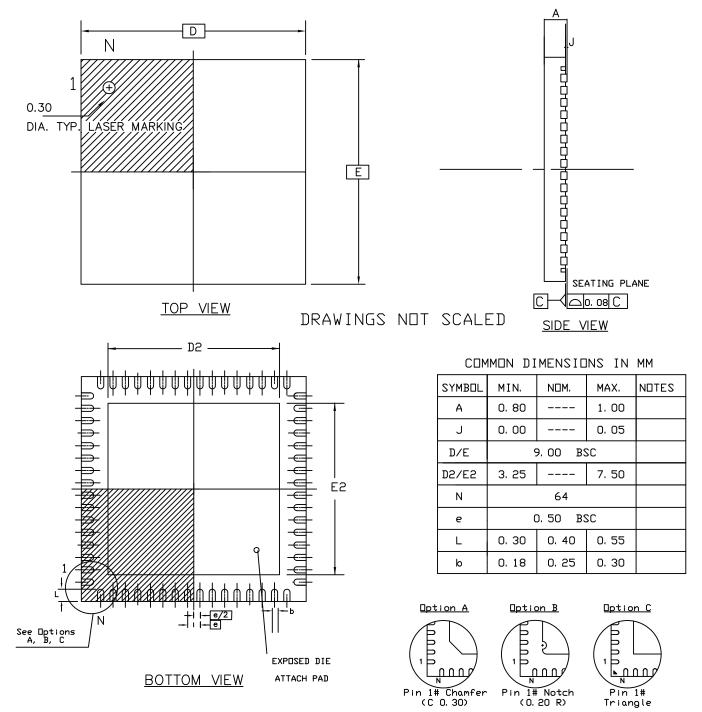

Table 13-3.

48-pad QFN Package Dimensions (in mm)

#### Figure 13-5. 64-pad QFN Package Drawing