# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 9x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-HLQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvmc12f2mkh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Chapter 11 Timer Module (TIM16B4CV3) Block Description

| 11.1 | Introduction                                                      | 441 |

|------|-------------------------------------------------------------------|-----|

|      | 11.1.1 Features                                                   | 441 |

|      | 11.1.2 Modes of Operation                                         | 441 |

|      | 11.1.3 Block Diagrams                                             | 442 |

| 11.2 | External Signal Description                                       | 443 |

|      | 11.2.1 IOC3 - IOC0 — Input Capture and Output Compare Channel 3-0 | 443 |

| 11.3 | Memory Map and Register Definition                                | 443 |

|      | 11.3.1 Module Memory Map                                          | 443 |

|      | 11.3.2 Register Descriptions                                      | 443 |

| 11.4 | Functional Description                                            | 455 |

|      | 11.4.1 Prescaler                                                  | 456 |

|      | 11.4.2 Input Capture                                              | 457 |

|      | 11.4.3 Output Compare                                             | 457 |

| 11.5 | Resets                                                            |     |

| 11.6 | Interrupts                                                        | 458 |

|      | 11.6.1 Channel [3:0] Interrupt (C[3:0]F)                          | 458 |

|      | 11.6.2 Timer Overflow Interrupt (TOF)                             | 458 |

# Chapter 12 Timer Module (TIM16B2CV3) Block Description

| Introduction                                                      |                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12.1.1 Features                                                   |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.1.2 Modes of Operation                                         | 459                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.1.3 Block Diagrams                                             |                                                                                                                                                                                                                                                                                                                                                                                        |

| External Signal Description                                       |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.2.1 IOC1 - IOC0 — Input Capture and Output Compare Channel 1-0 |                                                                                                                                                                                                                                                                                                                                                                                        |

| Memory Map and Register Definition                                |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.3.1 Module Memory Map                                          |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.3.2 Register Descriptions                                      |                                                                                                                                                                                                                                                                                                                                                                                        |

| Functional Description                                            |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.4.1 Prescaler                                                  | 474                                                                                                                                                                                                                                                                                                                                                                                    |

| 12.4.2 Input Capture                                              |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.4.3 Output Compare                                             |                                                                                                                                                                                                                                                                                                                                                                                        |

| Resets                                                            |                                                                                                                                                                                                                                                                                                                                                                                        |

| Interrupts                                                        |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.6.1 Channel [1:0] Interrupt (C[1:0]F)                          |                                                                                                                                                                                                                                                                                                                                                                                        |

| 12.6.2 Timer Overflow Interrupt (TOF)                             |                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                   | 12.1.1 Features12.1.2 Modes of Operation12.1.3 Block DiagramsExternal Signal Description12.2.1 IOC1 - IOC0 — Input Capture and Output Compare Channel 1-0Memory Map and Register Definition12.3.1 Module Memory Map12.3.2 Register DescriptionsFunctional Description12.4.1 Prescaler12.4.2 Input Capture12.4.3 Output CompareResetsInterrupts12.6.1 Channel [1:0] Interrupt (C[1:0]F) |

# Chapter 13

# Scalable Controller Area Network (S12MSCANV3)

| 13.1 Introduction | . 477 |

|-------------------|-------|

| 13.1.1 Glossary   | . 478 |

#### Chapter 4 Interrupt (S12ZINTV0)

| Address                     | Register<br>Name | Bit 7 | 6 | 5 | 4 | 3 | 2            | 1 | Bit 0 |

|-----------------------------|------------------|-------|---|---|---|---|--------------|---|-------|

| 0x00001D I                  | NT_CFDATA5 R     | 0     | 0 | 0 | 0 | 0 |              |   | 1     |

|                             | W                |       |   |   |   |   | PRIOLVL[2:0] |   |       |

| 0x00001E IN                 | NT_CFDATA6 R     | 0     | 0 | 0 | 0 | 0 | PRIOLVL[2:0] |   |       |

|                             | w                |       |   |   |   |   |              |   |       |

|                             |                  |       |   |   |   |   |              |   |       |

| 0x00001F I                  | NT_CFDATA7 R     | 0     | 0 | 0 | 0 | 0 | PRIOLVL[2:0] |   | 1     |

|                             | W                |       |   |   |   |   | 1            |   |       |

| = Unimplemented or Reserved |                  |       |   |   |   |   |              |   |       |

Figure 4-2. INT Register Summary

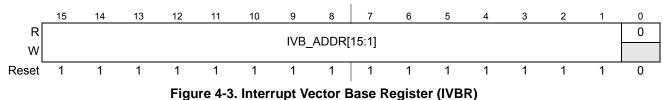

### 4.3.2.1 Interrupt Vector Base Register (IVBR)

Address: 0x000010

Read: Anytime

Write: Anytime

### Table 4-4. IVBR Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IVB_ADDR | <ul> <li>Interrupt Vector Base Address Bits — These bits represent the upper 15 bits of all vector addresses. Out of reset these bits are set to 0xFFFE (i.e., vectors are located at 0xFFFE00–0xFFFFF).</li> <li>Note: A system reset will initialize the interrupt vector base register with "0xFFFE" before it is used to determine the reset vector address. Therefore, changing the IVBR has no effect on the location of the reset vector (0xFFFFC–0xFFFFF).</li> </ul> |

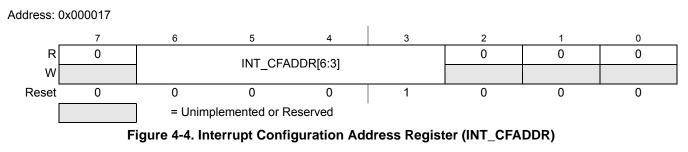

# 4.3.2.2 Interrupt Request Configuration Address Register (INT\_CFADDR)

Read: Anytime

Chapter 5 Background Debug Controller (S12ZBDCV2)

### 5.4.4.10 READ\_Rn

| Rea | nd CPU registe   | r                |                  |                  |                  | Acti             | ve Background |

|-----|------------------|------------------|------------------|------------------|------------------|------------------|---------------|

|     | 0x60+CRN         |                  | Data [31-24]     | Data [23-16]     | Data [15-8]      | Data [7-0]       |               |

|     | host →<br>target | D<br>A<br>C<br>K | target →<br>host | target →<br>host | target →<br>host | target →<br>host |               |

This command reads the selected CPU registers and returns the 32-bit result. Accesses to CPU registers are always 32-bits wide, regardless of implemented register width. Bytes that are not implemented return zero. The register is addressed through the CPU register number (CRN). See Section 5.4.5.1 for the CRN address decoding. If enabled, an ACK pulse is driven before the data bytes are transmitted.

If the device is not in active BDM, this command is illegal, the ILLCMD bit is set and no access is performed.

### 5.4.4.11 READ\_MEM.sz, READ\_MEM.sz\_WS

#### READ\_MEM.sz

Read memory at the specified address

| <br>0x30         | Address[23-0]    |                  | Data[7-0]        |                  |                  |                  |  |

|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|

| host →<br>target | host →<br>target | D<br>A<br>C<br>K | target →<br>host |                  |                  |                  |  |

| 0x34             | Address[23-0]    |                  | Data[15-8]       | Data[7-0]        | _                |                  |  |

| host →<br>target | host →<br>target | D<br>A<br>C<br>K | target →<br>host | target →<br>host |                  |                  |  |

| <br>0x38         | Address[23-0]    |                  | Data[31-24]      | Data[23-16]      | Data[15-8]       | Data[7-0]        |  |

| host →<br>target | host →<br>target | D<br>A<br>C<br>K | target →<br>host | target →<br>host | target →<br>host | target →<br>host |  |

MC9S12ZVM Family Reference Manual Rev. 2.11

Non-intrusive

### 6.4.3.1.2 Data Access Comparator Match

Data access matches are generated when an access occurs at the address contained in the comparator address register. The match can be qualified by the access data and by the access type (read/write). The breakpoint occurs a maximum of 2 instructions after the access in the CPU flow. Note, if a COF occurs between access and breakpoint, the opcode address of the breakpoint can be elsewhere in the memory map.

Opcode fetches are not classed as data accesses. Thus data access matches are not possible on opcode fetches.

# 6.4.3.2 External Event

The DBGEEV input signal can force a state sequencer transition, independent of internal comparator matches. The DBGEEV is an input signal mapped directly to a device pin and configured by the EEVE field in DBGC1. The external events can change the state sequencer state, or force a trace buffer entry, or gate trace buffer entries.

If configured to change the state sequencer state, then the external match is mapped to DBGSCRx bits C3SC[1:0]. In this configuration, internal comparator channel3 is de-coupled from the state sequencer but can still be used for timestamps. The DBGEFR bit EEVF is set when an external event occurs.

# 6.4.3.3 Setting The TRIG Bit

Independent of comparator matches it is possible to initiate a tracing session and/or breakpoint by writing the TRIG bit in DBGC1 to a logic "1". This forces the state sequencer into the Final State. If configured for End aligned tracing or for no tracing, the transition to Final State is followed immediately by a transition to State0. If configured for Begin- or Mid Aligned tracing, the state sequencer remains in Final State until tracing is complete, then it transitions to State0.

Breakpoints, if enabled, are issued on the transition to State0.

# 6.4.3.4 Profiling Trace Buffer Overflow Event

During code profiling a trace buffer overflow forces the state sequencer into the disarmed State0 and, if breakpoints are enabled, issues a breakpoint request to the CPU.

### 6.4.3.5 Event Priorities

If simultaneous events occur, the priority is resolved according to Table 6-46. Lower priority events are suppressed. It is thus possible to miss a lower priority event if it occurs simultaneously with an event of a higher priority. The event priorities dictate that in the case of simultaneous matches, the match on the higher comparator channel number (3,2,1,0) has priority.

If a write access to DBGC1 with the ARM bit position set occurs simultaneously to a hardware disarm from an internal event, then the ARM bit is cleared due to the hardware disarm.

| Priority | Source      | Action                                                                |

|----------|-------------|-----------------------------------------------------------------------|

| Highest  | TB Overflow | Immediate force to state 0, generate breakpoint and terminate tracing |

### Table 6-46. Event Priorities

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

# 8.3.2.10 S12CPMU\_UHV\_V10\_V6 PLL Control Register (CPMUPLL)

This register controls the PLL functionality.

Module Base + 0x000A

|       | 7 | 6 | 5   | 4   | 3 | 2 | 1 | 0 |

|-------|---|---|-----|-----|---|---|---|---|

| R     | 0 | 0 |     |     | 0 | 0 | 0 | 0 |

| w     |   |   | FM1 | FM0 |   |   |   |   |

| Reset | 0 | 0 | 0   | 0   | 0 | 0 | 0 | 0 |

### Figure 8-15. S12CPMU\_UHV\_V10\_V6 PLL Control Register (CPMUPLL)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

### NOTE

Write to this register clears the LOCK and UPOSC status bits.

### NOTE

Care should be taken to ensure that the bus frequency does not exceed the specified maximum when frequency modulation is enabled.

### Table 8-9. CPMUPLL Field Descriptions

| Field | Description                                                                                                                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PLL <b>Frequency Modulation Enable Bits</b> — FM1 and FM0 enable frequency modulation on the VCOCLK. This is to reduce noise emission. The modulation frequency is f <sub>ref</sub> divided by 16. See Table 8-10 for coding. |

### Table 8-10. FM Amplitude selection

| FM1 | FM0 | FM Amplitude /<br>f <sub>VCO</sub> Variation |

|-----|-----|----------------------------------------------|

| 0   | 0   | FM off                                       |

| 0   | 1   | ±1%                                          |

| 1   | 0   | ±2%                                          |

| 1   | 1   | ±4%                                          |

Chapter 11 Timer Module (TIM16B4CV3) Block Description

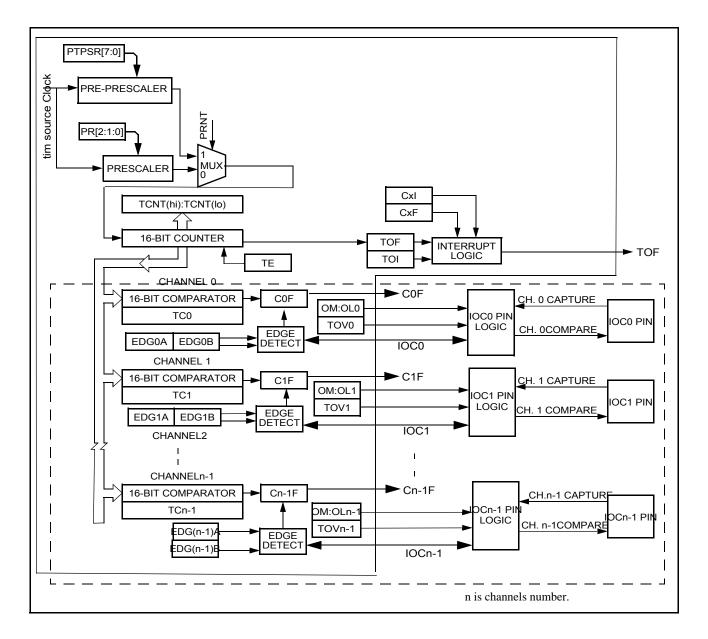

Figure 11-22. Detailed Timer Block Diagram

# 11.4.1 Prescaler

The prescaler divides the Bus clock by 1, 2, 4, 8, 16, 32, 64 or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in timer system control register 2 (TSCR2).

The prescaler divides the Bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

Chapter 12 Timer Module (TIM16B2CV3) Block Description

| Register<br>Name                          |        | Bit 7                 | 6            | 5            | 4            | 3            | 2            | 1     | Bit 0 |

|-------------------------------------------|--------|-----------------------|--------------|--------------|--------------|--------------|--------------|-------|-------|

| 0x000C<br>TIE                             | R<br>W | RESERV<br>ED          | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | C1I   | COI   |

| 0x000D<br>TSCR2                           | R<br>W | TOI                   | 0            | 0            | 0            | RESERV<br>ED | PR2          | PR1   | PR0   |

| 0x000E<br>TFLG1                           | R<br>W | RESERV<br>ED          | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | C1F   | C0F   |

| 0x000F<br>TFLG2                           | R      | TOF                   | 0            | 0            | 0            | 0            | 0            | 0     | 0     |

| _                                         | W      |                       |              |              |              |              |              |       |       |

| 0x0010–0x001F<br>TCxH–TCxL <sup>(1)</sup> | R<br>W | Bit 15                | Bit 14       | Bit 13       | Bit 12       | Bit 11       | Bit 10       | Bit 9 | Bit 8 |

|                                           | R<br>W | Bit 7                 | Bit 6        | Bit 5        | Bit 4        | Bit 3        | Bit 2        | Bit 1 | Bit 0 |

| 0x0024–0x002B<br>Reserved                 | R<br>W |                       |              |              |              |              |              |       |       |

| 0x002C<br>OCPD                            | R<br>W | RESERV<br>ED          | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | OCPD1 | OCPD0 |

| 0x002D<br>Reserved                        | R      |                       |              |              |              |              |              |       |       |

| 0x002E<br>PTPSR                           | R<br>W | PTPS7                 | PTPS6        | PTPS5        | PTPS4        | PTPS3        | PTPS2        | PTPS1 | PTPS0 |

| 0x002F<br>Reserved                        | R<br>W |                       |              |              |              |              |              |       |       |

|                                           |        | <b>F</b> <sup>1</sup> |              |              |              | (0)          |              |       |       |

Figure 12-3. TIM16B2CV3 Register Summary (Sheet 2 of 2)

1. The register is available only if corresponding channel exists.

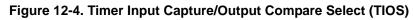

# 12.3.2.1 Timer Input Capture/Output Compare Select (TIOS)

Module Base + 0x0000

|        | 7        | 6        | 5        | 4        | 3        | 2        | 1    | 0    |

|--------|----------|----------|----------|----------|----------|----------|------|------|

| R<br>W | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | RESERVED | IOS1 | IOS0 |

| Reset  | 0        | 0        | 0        | 0        | 0        | 0        | 0    | 0    |

Read: Anytime

Write: Anytime

| Register<br>Name            |        | Bit 7                                                       | 6      | 5      | 4      | 3      | 2      | 1      | Bit 0  |

|-----------------------------|--------|-------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--------|

| 0x000E                      | R      | RXERR7                                                      | RXERR6 | RXERR5 | RXERR4 | RXERR3 | RXERR2 | RXERR1 | RXERR0 |

| CANRXERR                    | W      |                                                             |        |        |        |        |        |        |        |

| 0x000F                      | R      | TXERR7                                                      | TXERR6 | TXERR5 | TXERR4 | TXERR3 | TXERR2 | TXERR1 | TXERR0 |

| CANTXERR                    | W      |                                                             |        |        |        |        |        |        |        |

| 0x0010-0x0013<br>CANIDAR0-3 | R<br>W | AC7                                                         | AC6    | AC5    | AC4    | AC3    | AC2    | AC1    | AC0    |

| 0x0014–0x0017<br>CANIDMRx   | R<br>W | AM7                                                         | AM6    | AM5    | AM4    | AM3    | AM2    | AM1    | AM0    |

| 0x0018–0x001B<br>CANIDAR4–7 | R<br>W | AC7                                                         | AC6    | AC5    | AC4    | AC3    | AC2    | AC1    | AC0    |

| 0x001C–0x001F<br>CANIDMR4–7 | R<br>W | AM7                                                         | AM6    | AM5    | AM4    | AM3    | AM2    | AM1    | AM0    |

| 0x0020–0x002F<br>CANRXFG    | R<br>W | See Section 13.3.3, "Programmer's Model of Message Storage" |        |        |        |        |        |        |        |

| 0x0030–0x003F<br>CANTXFG    | R<br>W | See Section 13.3.3, "Programmer's Model of Message Storage" |        |        |        |        |        |        |        |

|                             |        | = Unimplemented or Reserved                                 |        |        |        |        |        |        |        |

Figure 13-3. MSCAN Register Summary (continued)

# 13.3.2 Register Descriptions

This section describes in detail all the registers and register bits in the MSCAN module. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. All bits of all registers in this module are completely synchronous to internal clocks during a register read.

# 13.3.2.1 MSCAN Control Register 0 (CANCTL0)

The CANCTL0 register provides various control bits of the MSCAN module as described below.

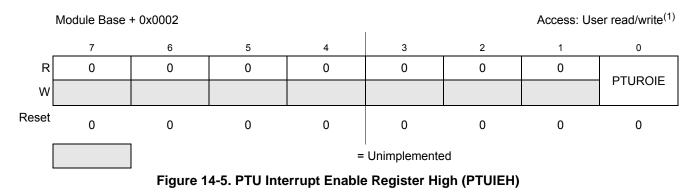

# 14.3.2.3 PTU Interrupt Enable Register High (PTUIEH)

<sup>1.</sup> Read: Anytime

### Table 14-5. PTUIEH Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                      |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0<br>PTUROIE | <ul> <li>PTU Reload Overrun Interrupt Enable — Enables PTU reload overrun interrupt.</li> <li>0 No interrupt will be requested whenever PTUROIF is set</li> <li>1 Interrupt will be requested whenever PTUROIF is set</li> </ul> |  |  |  |

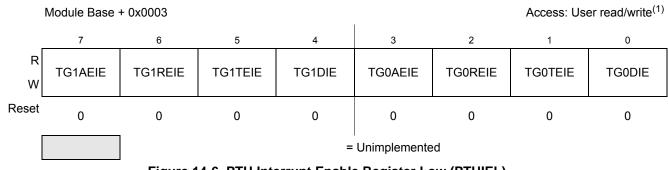

# 14.3.2.4 PTU Interrupt Enable Register Low (PTUIEL)

Figure 14-6. PTU Interrupt Enable Register Low (PTUIEL)

1. Read: Anytime

Write: Anytime

### Table 14-6. PTUIEL Register Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TG1AEIE | <ul> <li>Trigger Generator 1 Memory Access Error Interrupt Enable — Enables trigger generator memory access error interrupt.</li> <li>0 No interrupt will be requested whenever TG1AEIF is set</li> <li>1 Interrupt will be requested whenever TG1AEIF is set</li> </ul> |

| 6<br>TG1REIE | <ul> <li>Trigger Generator 1 Reload Error Interrupt Enable — Enables trigger generator reload error interrupt.</li> <li>0 No interrupt will be requested whenever TG1REIF is set</li> <li>1 Interrupt will be requested whenever TG1REIF is set</li> </ul>               |

Write: Anytime

Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

Figure 15-61. Correction with Negative Current

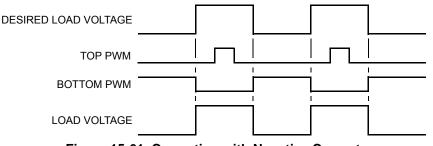

# 15.4.7 Asymmetric PWM Output

In complementary center-aligned mode, the PWM duty cycle is able to change alternatively at every half cycle. The count direction of the PWM counter selects either the odd or the even PWM value registers to use in the PWM cycle. For counting up, select even PWM value registers to use in the PWM cycle. For counting down, select odd PWM value registers to use in the PWM cycle. The related CINV*n* bits of the PWM pair must select the same polarity for both generators.

| Bit  | Logic State | Output Control                              |

|------|-------------|---------------------------------------------|

| ICCA | 0           | IPOLA Controls PWM0/PWM1 Pair               |

|      | 1           | PWM Count Direction Controls PWM0/PWM1 Pair |

| ICCB | 0           | IPOLB Controls PWM2/PWM3 Pair               |

|      | 1           | PWM Count Direction Controls PWM2/PWM3 Pair |

| ICCC | 0           | IPOLC Controls PWM4/PWM5 Pair               |

|      | 1           | PWM Count Direction Controls PWM4/PWM5 Pair |

### Table 15-44. Top/Bottom Corrections Selected by ICCn Bits

### NOTE

If an ICCx bit in the PMFICCTL register changes during a PWM period, the new value does not take effect until the next PWM period. ICCx bits take effect at the end of each PWM cycle regardless of the state of the related LDOKx bit or global load OK.

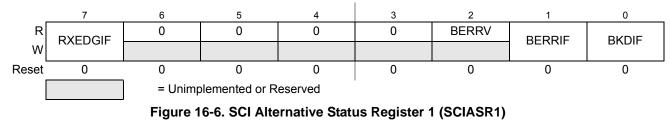

# 16.3.2.3 SCI Alternative Status Register 1 (SCIASR1)

Module Base + 0x0000

Read: Anytime, if AMAP = 1

Write: Anytime, if AMAP = 1

### Table 16-5. SCIASR1 Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RXEDGIF | Receive Input Active Edge Interrupt Flag — RXEDGIF is asserted, if an active edge (falling if RXPOL = 0, rising if RXPOL = 1) on the RXD input occurs. RXEDGIF bit is cleared by writing a "1" to it.<br>0 No active receive on the receive input has occurred<br>1 An active edge on the receive input has occurred                                                    |

| 2<br>BERRV   | <ul> <li>Bit Error Value — BERRV reflects the state of the RXD input when the bit error detect circuitry is enabled and a mismatch to the expected value happened. The value is only meaningful, if BERRIF = 1.</li> <li>0 A low input was sampled, when a high was expected</li> <li>1 A high input reassembled, when a low was expected</li> </ul>                    |

| 1<br>BERRIF  | <b>Bit Error Interrupt Flag</b> — BERRIF is asserted, when the bit error detect circuitry is enabled and if the value sampled at the RXD input does not match the transmitted value. If the BERRIE interrupt enable bit is set an interrupt will be generated. The BERRIF bit is cleared by writing a "1" to it.<br>0 No mismatch detected<br>1 A mismatch has occurred |

| 0<br>BKDIF   | <ul> <li>Break Detect Interrupt Flag — BKDIF is asserted, if the break detect circuitry is enabled and a break signal is received. If the BKDIE interrupt enable bit is set an interrupt will be generated. The BKDIF bit is cleared by writing a "1" to it.</li> <li>0 No break signal was received</li> <li>1 A break signal was received</li> </ul>                  |

The SCI also sets a flag, the transmit data register empty flag (TDRE), every time it transfers data from the buffer (SCIDRH/L) to the transmitter shift register. The transmit driver routine may respond to this flag by writing another byte to the Transmitter buffer (SCIDRH/SCIDRL), while the shift register is still shifting out the first byte.

To initiate an SCI transmission:

- 1. Configure the SCI:

- a) Select a baud rate. Write this value to the SCI baud registers (SCIBDH/L) to begin the baud rate generator. Remember that the baud rate generator is disabled when the baud rate is zero. Writing to the SCIBDH has no effect without also writing to SCIBDL.

- b) Write to SCICR1 to configure word length, parity, and other configuration bits (LOOPS,RSRC,M,WAKE,ILT,PE,PT).

- c) Enable the transmitter, interrupts, receive, and wake up as required, by writing to the SCICR2 register bits (TIE,TCIE,RIE,ILIE,TE,RE,RWU,SBK). A preamble or idle character will now be shifted out of the transmitter shift register.

- 2. Transmit Procedure for each byte:

- a) Poll the TDRE flag by reading the SCISR1 or responding to the TDRE interrupt. Keep in mind that the TDRE bit resets to one.

- b) If the TDRE flag is set, write the data to be transmitted to SCIDRH/L, where the ninth bit is written to the T8 bit in SCIDRH if the SCI is in 9-bit data format. A new transmission will not result until the TDRE flag has been cleared.

- 3. Repeat step 2 for each subsequent transmission.

### NOTE

The TDRE flag is set when the shift register is loaded with the next data to be transmitted from SCIDRH/L, which happens, generally speaking, a little over half-way through the stop bit of the previous frame. Specifically, this transfer occurs 9/16ths of a bit time AFTER the start of the stop bit of the previous frame.

Writing the TE bit from 0 to a 1 automatically loads the transmit shift register with a preamble of 10 logic 1s (if M = 0) or 11 logic 1s (if M = 1). After the preamble shifts out, control logic transfers the data from the SCI data register into the transmit shift register. A logic 0 start bit automatically goes into the least significant bit position of the transmit shift register. A logic 1 stop bit goes into the most significant bit position.

Hardware supports odd or even parity. When parity is enabled, the most significant bit (MSB) of the data character is the parity bit.

The transmit data register empty flag, TDRE, in SCI status register 1 (SCISR1) becomes set when the SCI data register transfers a byte to the transmit shift register. The TDRE flag indicates that the SCI data register can accept new data from the internal data bus. If the transmit interrupt enable bit, TIE, in SCI control register 2 (SCICR2) is also set, the TDRE flag generates a transmitter interrupt request.

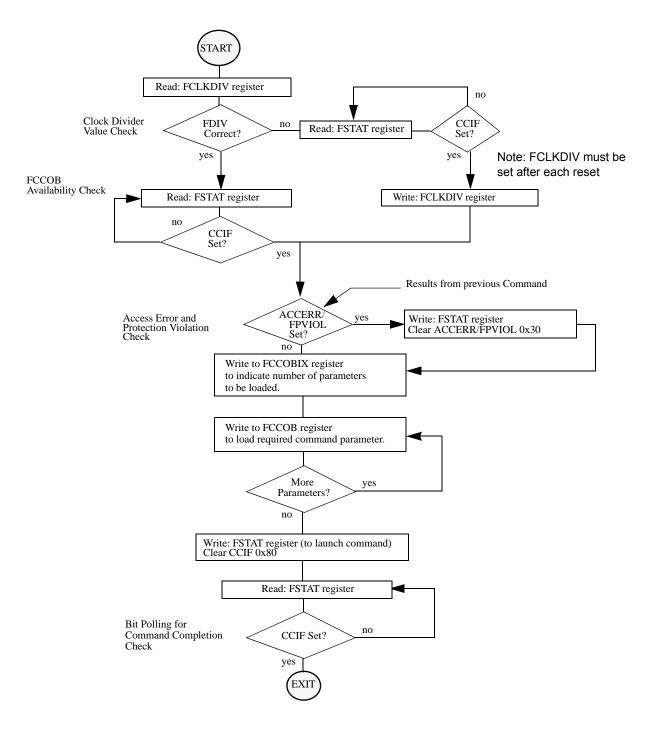

Chapter 20 Flash Module (S12ZFTMRZ)

Figure 20-30. Generic Flash Command Write Sequence Flowchart

# 22.4 Functional Description

# 22.4.1 PWM Clock Select

There are four available clocks: clock A, clock B, clock SA (scaled A), and clock SB (scaled B). These four clocks are based on the bus clock.

Clock A and B can be software selected to be 1, 1/2, 1/4, 1/8,..., 1/64, 1/128 times the bus clock. Clock SA uses clock A as an input and divides it further with a reloadable counter. Similarly, clock SB uses clock B as an input and divides it further with a reloadable counter. The rates available for clock SA are software selectable to be clock A divided by 2, 4, 6, 8,..., or 512 in increments of divide by 2. Similar rates are available for clock SB. Each PWM channel has the capability of selecting one of four clocks, clock A, Clock B, clock SA or clock SB.

The block diagram in Figure 22-15 shows the four different clocks and how the scaled clocks are created.

# 22.4.1.1 Prescale

The input clock to the PWM prescaler is the bus clock. It can be disabled whenever the part is in freeze mode by setting the PFRZ bit in the PWMCTL register. If this bit is set, whenever the MCU is in freeze mode (freeze mode signal active) the input clock to the prescaler is disabled. This is useful for emulation in order to freeze the PWM. The input clock can also be disabled when all available PWM channels are disabled (PWMEx-0 = 0). This is useful for reducing power by disabling the prescale counter.

Clock A and clock B are scaled values of the input clock. The value is software selectable for both clock A and clock B and has options of 1, 1/2, 1/4, 1/8, 1/16, 1/32, 1/64, or 1/128 times the bus clock. The value selected for clock A is determined by the PCKA2, PCKA1, PCKA0 bits in the PWMPRCLK register. The value selected for clock B is determined by the PCKB2, PCKB1, PCKB0 bits also in the PWMPRCLK register.

# 22.4.1.2 Clock Scale

The scaled A clock uses clock A as an input and divides it further with a user programmable value and then divides this by 2. The scaled B clock uses clock B as an input and divides it further with a user programmable value and then divides this by 2. The rates available for clock SA are software selectable to be clock A divided by 2, 4, 6, 8,..., or 512 in increments of divide by 2. Similar rates are available for clock SB.

# Appendix A MCU Electrical Specifications

# A.1 General

This section contains the most accurate electrical information available at the time of publication.

# A.1.1 Parameter Classification

The electrical parameters shown in the appendices are guaranteed by various methods.

The parameter classification is documented in the PPAP.

The parameter classification columns are for NXP internal use only.

| 5 | Latch-up Current of 5V GPIOs at T=125°C positive negative                                   | I <sub>LAT</sub> | +100<br>-100 | - | mA |

|---|---------------------------------------------------------------------------------------------|------------------|--------------|---|----|

| 6 | Latch-up Current (VCP, BST, LIN, HD, HS, HG, LG, LS, LD)<br>T=125°C<br>positive<br>negative | I <sub>LAT</sub> | +100<br>-100 | - | mA |

| 7 | Latch-up Current of 5V GPIOs at 27°C positive negative                                      | I <sub>LAT</sub> | +200<br>-200 | - | mA |

| 8 | Latch-up Current (VCP, BST, LIN, HD, HS, HG, LG, LS, LD)<br>T= 27°C<br>positive<br>negative | I <sub>LAT</sub> | +200<br>-200 | - | mA |

# A.1.6 Recommended Capacitor Values

### Table A-5. Recommended Capacitor Values (nominal component values)

| Num | Characteristic                               | Symbol                | Typical | Unit    |  |

|-----|----------------------------------------------|-----------------------|---------|---------|--|

| 1   | VDDX decoupling capacitor <sup>(1) (2)</sup> | C <sub>VDDX1,2</sub>  | 100-220 | nF      |  |

| 2   | VDDA decoupling capacitor <sup>(1)</sup>     | C <sub>VDDA</sub>     | 100-220 | nF      |  |

| 3   | VDDX stability capacitor <sup>(3) (4)</sup>  | $C_{VDD5}$            | 4.7-10  | uF      |  |

| 4   | VDDC stability capacitor                     | C <sub>VDDC</sub>     | 4.7-10  | uF      |  |

| 5   | VDDS[2:1] stability capacitor                | C <sub>VDDS</sub>     | 4.7-10  | uF      |  |

| 6   | VLS decoupling capacitor <sup>(1) (5)</sup>  | C <sub>VLS0,1,2</sub> | 100-220 | nF      |  |

| 7   | VLS stability capacitor <sup>(3) (6)</sup>   | C <sub>VLS</sub>      | 4.7-10  | uF      |  |

| 8   | VDD decoupling capacitor <sup>(1)</sup>      | C <sub>VDD</sub>      | 100-220 | -220 nF |  |

| 9   | VDDF decoupling capacitor <sup>(1)</sup>     | C <sub>VDDF</sub>     | 100-220 | 220 nF  |  |

| 10  | LIN decoupling capacitor <sup>(1)</sup>      | C <sub>LIN</sub>      | 220     | pF      |  |

1. X7R ceramic

- 2. One capacitor per VDDX pin

- 3. 4.7  $\mu F$  ceramic or  $10 \mu F$  tantalum

- 4. Can be placed anywhere on the 5V supply node (VDDA, VDDX)

- 5. One capacitor per each VLS[2:0] pin

- 6. Can be placed anywhere on the VLS node

# A.1.7 Operating Conditions

This section describes the operating conditions of the device. Unless otherwise noted these conditions apply to the following electrical parameters.

1. Outside of the given  $V_{HVI}$  range the error is significant. The ratio can be changed, if outside of the given range.

# A.2.2 HV Physical Interface Characteristics

The HV Physical Interface specification is included in the LINPHY electrical section.

# A.3 Supply Currents

This section describes the current consumption characteristics of the device as well as the conditions for the measurements.

### A.3.1 Measurement Conditions

Current is measured on VSUP. VDDX is connected to VDDA. It does not include the current to drive external loads. Unless otherwise noted the currents are measured in special single chip mode and the CPU code is executed from RAM. For Run and Wait current measurements PLL is on and the reference clock is the IRC1M trimmed to 1MHz. For the junction temperature range from -40°C to +150°C the bus frequency is 50MHz. For the temperature range from +150°C to +175°C, the bus frequency is 40MHz. Table A-16 and Table A-17 show the configuration of the CPMU module and the peripherals for Run, Wait and Stop current measurement.

| CPMU REGISTER | Bit settings/Conditions                                               |

|---------------|-----------------------------------------------------------------------|

| CPMUCLKS      | PLLSEL=0, PSTP=1, CSAD=0,<br>PRE=PCE=RTIOSCSEL=1<br>COPOSCSEL[1:0]=01 |

| CPMUOSC       | OSCE=1, Quartz oscillator f <sub>EXTAL</sub> =4MHz                    |

| CPMURTI       | RTDEC=0, RTR[6:4]=111, RTR[3:0]=1111                                  |

| CPMUCOP       | WCOP=1, CR[2:0]=111                                                   |

Table A-15. CPMU Configuration for Pseudo Stop Current Measurement

| Table A-16. CPMU Configuration for Run/Wait and Full Stop Current Measurement |

|-------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------|

| CPMU REGISTER | Bit settings/Conditions                                                |

|---------------|------------------------------------------------------------------------|

| CPMUSYNR      | VCOFRQ[1:0]= 3,SYNDIV[5:0] = 49                                        |

| CPMUPOSTDIV   | POSTDIV[4:0]=0                                                         |

| CPMUCLKS      | PLLSEL=1, CSAD=0                                                       |

| CPMUOSC       | OSCE=0, Reference clock for PLL is $f_{ref}=f_{irc1m}$ trimmed to 1MHz |

| CPMUVREGCTL   | EXTXON=0, INTXON=1                                                     |

# Appendix D LIN/HV PHY Electrical Specifications

# **D.1** Static Electrical Characteristics

### Table D-1. Static electrical characteristics of the LIN/HV PHY (Junction Temperature From -40°C To +175°C)

Characteristics noted under conditions 5.5V <=  $V_{LINSUP}$  <= 18V unless otherwise noted<sup>(1) (2) (3)</sup>. Typical values noted reflect the approximate parameter mean at  $T_A = 25^{\circ}$ C under nominal conditions unless otherwise noted.

| Num | с | Ratings                                                                                                                                                           | Symbol                  | Min                | Тур | Max   | Unit                |  |

|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--------------------|-----|-------|---------------------|--|

| 1   |   | V <sub>LINSUP</sub> range for LIN compliant electrical characteristics                                                                                            | V <sub>LINSUP</sub> LIN | 5.5 <sup>1 2</sup> | 12  | 18    | V                   |  |

| 2   |   | Current limitation into the LIN pin in dominant state <sup>(4)</sup> $V_{LIN} = V_{LINSUP\_LIN\_MAX}$                                                             | I <sub>LIN_LIM</sub>    | 40                 |     | 200   | mA                  |  |

| 3   |   | Input leakage current in dominant state, driver off,<br>internal pull-up on<br>(V <sub>LIN</sub> = 0V, V <sub>LINSUP</sub> = 12V)                                 | ILIN_PAS_dom            | -1                 | —   | —     | mA                  |  |

| 4   |   | Input leakage current in recessive state, driver off<br>(5V <v<sub>LINSUP&lt;18V, 5V<v<sub>LIN&lt;18V, V<sub>LIN</sub> =&gt; V<sub>LINSUP</sub> )</v<sub></v<sub> | ILIN_PAS_rec            | _                  | _   | 20    | μΑ                  |  |

| 5   |   | Input leakage current when ground disconnected $(GND_{Device} = V_{LINSUP}, 0V < V_{LIN} < 18V, V_{LINSUP} = 12V)$                                                | I <sub>LIN_NO_GND</sub> | -1                 | _   | 1     | mA                  |  |

| 6   |   | Input leakage current when battery disconnected<br>(V <sub>LINSUP</sub> = GND, 0 <v<sub>LIN&lt;18V)</v<sub>                                                       | I <sub>LIN_NO_BAT</sub> | _                  | _   | 30    | μΑ                  |  |

| 7   |   | Receiver dominant state                                                                                                                                           | V <sub>LINdom</sub>     | -                  | _   | 0.4   | V <sub>LINSUP</sub> |  |

| 8   |   | Receiver recessive state                                                                                                                                          | V <sub>LINrec</sub>     | 0.6                |     | —     | V <sub>LINSUP</sub> |  |

| 9   |   | V <sub>LIN_CNT</sub> =(V <sub>th_dom</sub> + V <sub>th_rec</sub> )/2                                                                                              | V <sub>LIN_CNT</sub>    | 0.475              | 0.5 | 0.525 | V <sub>LINSUP</sub> |  |

| 10  |   | V <sub>HYS</sub> = V <sub>th_rec</sub> -V <sub>th_dom</sub>                                                                                                       | V <sub>HYS</sub>        |                    |     | 0.175 | V <sub>LINSUP</sub> |  |

| 11  |   | Maximum capacitance allowed on slave node                                                                                                                         | C <sub>slave</sub>      |                    | 220 | 250   | pF                  |  |

| 12a |   | Capacitance of LIN pin -40°C < T <sub>J</sub> < 150°C,<br>Recessive state                                                                                         | C <sub>int</sub>        | _                  | 20  | _     | pF                  |  |

| 12b |   | Capacitance of LIN pin -40°C < T <sub>J</sub> < 150°C,<br>Recessive state                                                                                         | C <sub>int</sub>        | —                  | —   | 45    | pF                  |  |

| 12c |   | Capacitance of LIN pin 150°C < T <sub>J</sub> < 175°C,<br>Recessive state                                                                                         | C <sub>int</sub>        | _                  | —   | 39    | pF                  |  |

| 13  |   | Internal pull-up (slave)                                                                                                                                          | R <sub>slave</sub>      | 27                 | 34  | 40    | kΩ                  |  |

1. For 3.5V<= V<sub>LINSUP</sub> <5V, the LIN/HV PHY is still working but with degraded parametrics.

2. For 5V<= V<sub>LINSUP</sub> <5.5V, characterization showed that all parameters generally stay within the indicated specification, except the duty cycles D2 and D4 which may increase and potentially go beyond their maximum limits for highly loaded buses.

3. The V<sub>LINSUP</sub> voltage is provided by the VLINSUP supply. This supply mapping is described in device level documentation.

Appendix M Detailed Register Address Map

# M.3 0x0070-0x00FF S12ZMMC

| Address | Name      |        | Bit 7             | 6    | 5    | 4         | 3        | 2        | 1     | Bit 0 |  |  |

|---------|-----------|--------|-------------------|------|------|-----------|----------|----------|-------|-------|--|--|

| 0x0070  | MODE      | R      | MODC              | 0    | 0    | 0         | 0        | 0        | 0     | 0     |  |  |

|         |           | W      | MODO              |      |      |           |          |          |       |       |  |  |

| 0x0071- | Reserved  | R      | 0                 | 0    | 0    | 0         | 0        | 0        | 0     | 0     |  |  |

| 0x007F  |           | W      |                   |      |      |           |          |          |       |       |  |  |

| 0x0080  | MMCECH    | R<br>W | ITRI3:01 TGTI3:01 |      |      |           |          |          |       |       |  |  |

| 0x0081  | MMCECL    | R<br>W |                   | ACC[ | 3:0] |           |          | ERR      | [3:0] |       |  |  |

| 0x0082  | MMCCCRH   | R      | CPUU              | 0    | 0    | 0         | 0        | 0        | 0     | 0     |  |  |

|         |           | w      |                   |      |      |           |          | -        |       |       |  |  |

| 0x0083  | MMCCCRL   | R      | 0                 | CPUX | 0    | CPUI      | 0        | 0        | 0     | 0     |  |  |

|         |           | W      |                   |      |      |           |          |          |       |       |  |  |

|         |           |        |                   |      |      |           |          |          |       |       |  |  |

| 0x0084  | Reserved  | R      | 0                 | 0    | 0    | 0         | 0        | 0        | 0     | 0     |  |  |

|         |           | W      |                   |      |      |           |          |          |       |       |  |  |

| 0x0085  | MMCPCH    | R      |                   |      |      | CPUPC[23: | 16]      |          |       |       |  |  |

|         |           | W      |                   |      |      |           |          |          |       |       |  |  |

| 0x0086  | 86 MMCPCM |        | R                 |      |      |           | CPUPC[15 | :8]      |       |       |  |  |

|         |           |        | W                 |      |      |           |          |          |       |       |  |  |

| 0x0087  | MMCPCL    | MMCPCL | 7 MMCPCL          | R    |      |           |          | CPUPC[7: | 0]    |       |  |  |

|         |           | w      |                   |      |      |           |          |          |       |       |  |  |

| 0x0088- | Reserved  | R      | 0                 | 0    | 0    | 0         | 0        | 0        | 0     | 0     |  |  |

| 0x00FF  |           | w      |                   |      |      |           |          |          |       |       |  |  |

# M.4 0x0100-0x017F S12ZDBG

| Address | Name       |     | Bit 7 | 6        | 5       | 4   | 3                 | 2     | 1      | Bit 0    |       |                    |

|---------|------------|-----|-------|----------|---------|-----|-------------------|-------|--------|----------|-------|--------------------|

| 0x0100  | 00 DBGC1 R |     | DBGC1 |          | ARM     | 0   | reserved          | BDMBP | BRKCPU | reserved | EEVE1 | EEVE0 <sup>2</sup> |

|         |            | W   |       | TRIG     |         |     |                   |       |        |          |       |                    |

| 0x0101  | DBGC2      | R R |       | 0        | 0       | 0   | CDCM <sup>2</sup> |       | ABCM   |          |       |                    |

| 0.00101 |            | W   |       |          |         |     | CDC               |       | AD     |          |       |                    |

|         |            | -   |       |          |         |     | 1                 |       |        |          |       |                    |

| 0x0102  |            |     | R     | reserved | TSOURCE | TRA | NGE               | TRCI  | MOD    | TAL      | IGN   |                    |

|         | _          | W   |       |          |         |     |                   |       |        |          |       |                    |

#### Appendix M Detailed Register Address Map

| Address  | Name               |   | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1 | Bit 0  |

|----------|--------------------|---|-------|---|---|---|---|---|---|--------|

| 0x02F8-  | Reserved           | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0      |

| 0x02FC   |                    | W |       |   |   |   |   |   |   |        |

| 0x02FD   | RDRP               | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 | RDRP0  |

| 00021 D  | NDINI              | W |       |   |   |   |   |   |   |        |

| 0x02FE-  |                    | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0      |

| 0x0330   | Reserved           | W |       |   |   |   |   |   |   |        |

| 0.0004   | DTU 2              | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 | PTIL0  |

| 0x0331   | PTIL <sup>2</sup>  | W |       |   |   |   |   |   |   |        |

|          |                    | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0      |

| 0x0332 F | Reserved           | W |       |   |   |   |   |   |   |        |

|          | 2                  | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 |        |

| 0x0333 I | PTPSL <sup>2</sup> | W |       |   |   |   |   |   |   | PTPSL0 |

|          | 2                  | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 |        |

| 0x0334   | PPSL <sup>2</sup>  | W |       |   |   |   |   |   |   | PPSL0  |

|          |                    | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 | 0      |

| 0x0335 F | Reserved           | W |       |   |   |   |   |   |   |        |

|          | 2                  | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 |        |

| 0x0336   | PIEL <sup>2</sup>  | W |       |   |   |   |   |   |   | PIEL0  |

|          | 0                  | R | 0     | 0 | 0 | 0 | 0 | 0 | 0 |        |

| 0x0337   | PIFL <sup>2</sup>  | W |       |   |   |   |   |   |   | PIFL0  |