# E·XFL

# Welcome to <u>E-XFL.COM</u>

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 8K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 9x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-HLQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvmc12f3vkh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address       | Module                                                    | Size<br>(Bytes) |

|---------------|-----------------------------------------------------------|-----------------|

| 0x06E0-0x06EF | Reserved                                                  | 16              |

| 0x06F0-0x06F7 | BATS                                                      | 8               |

| 0x06F8-0x06FF | Reserved                                                  | 8               |

| 0x0700–0x0707 | SCI0                                                      | 8               |

| 0x0708–0x070F | Reserved                                                  | 8               |

| 0x0710–0x0717 | SCI1                                                      | 8               |

| 0x0718–0x077F | Reserved                                                  | 104             |

| 0x0780–0x0787 | SPIO                                                      | 8               |

| 0x0788–0x07FF | Reserved                                                  | 120             |

| 0x0800-0x083F | CAN0                                                      | 64              |

| 0x0840–0x097F | Reserved                                                  | 320             |

| 0x0980-0x0987 | LINPHY (S12ZVML derivatives)                              | 8               |

| 0x0980–0x0987 | HV Physical Interface<br>(S12ZVM32, S12ZVM16 derivatives) | 8               |

| 0x0988–0x098F | Reserved                                                  | 8               |

| 0x0990-0x0997 | CANPHY (ZVMC256 only)                                     | 8               |

| 0x0998-0x0FFF | Reserved                                                  | 1640            |

#### Table 1-5. Module Register Address Ranges

1. Reading from the first 16 locations in this reserved range returns undefined data

2. Address range = 0x0690-0x069F on Maskset N06E

#### NOTE

Reserved register space shown above is not allocated to any module. This register space is reserved for future use. Writing to these locations has no effect. Read access to these locations returns zero.

# 1.6.1 Flash Module

This device family instantiates different flash modules, depending on derivative. The flash documentation for the all devices is featured in the FTMRZ section.

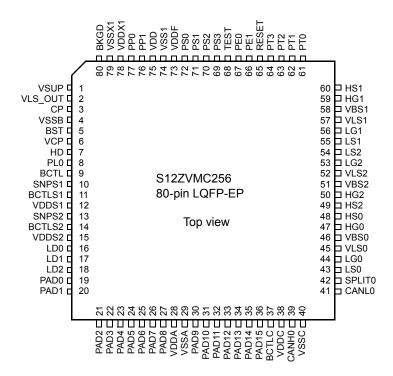

The exposed pad on the package bottom must be connected to a grounded contact pad on the PCB.

Figure 1-3. S12ZVMC256 80-pin LQFP pin out

Chapter 2 Port Integration Module (S12ZVMPIMV3)

# 2.3.1 Register Map

| Global<br>Address | Register<br>Name | Bit 7              | 6                  | 5                   | 4                        | 3        | 2        | 1         | Bit 0                 |

|-------------------|------------------|--------------------|--------------------|---------------------|--------------------------|----------|----------|-----------|-----------------------|

| 0x0200            | MODRR0           | R 0<br>W           | 0                  | SPI0SSRR            | SPIORR                   | SCI1RR   |          | SOLORR2-0 | I                     |

| 0x0201            | MODRR1           | R<br>W             | M0C0RR2-0          | 2                   | PWMPRR1-0 <sup>3</sup> F |          | PWM54RR  | PWM32RR   | PWM10RR               |

| 0x0202            | MODRR2           | R<br>T0C2<br>W     | RR1-0 <sup>4</sup> | T0C1RR <sup>4</sup> | T1IC0RR <sup>2</sup>     | T0IC3    | RR1-0    | T0IC1RR   | T0IC1RR0 <sup>4</sup> |

| 0x0203–           | Reserved         | R 0                | 0                  | 0                   | 0                        | 0        | 0        | 0         | 0                     |

| 0x0207            |                  | W                  |                    |                     |                          |          |          |           |                       |

| 0x0208            | ECLKCTL          | R<br>NECLK         | 0                  | 0                   | 0                        | 0        | 0        | 0         | 0                     |

|                   |                  | W                  |                    |                     |                          |          |          |           |                       |

| 0x0209            | IRQCR            | R<br>IRQE          | IRQEN              | 0                   | 0                        | 0        | 0        | 0         | 0                     |

|                   |                  | W                  |                    |                     |                          |          |          |           |                       |

| 0x020A            | PIMMISC          | R 0<br>W           | 0                  | 0                   | 0                        | 0        | 0        | OCPE1     | 0                     |

| 0x020B-           | Decement         | R 0                | 0                  | 0                   | 0                        | 0        | 0        | 0         | 0                     |

| 0x020C            | Reserved         | W                  |                    |                     |                          |          |          |           |                       |

| 0x020D            | Reserved         | R<br>Reserved<br>W | Reserved           | Reserved            | Reserved                 | Reserved | Reserved | Reserved  | Reserved              |

| 0x020E            | Reserved         | R<br>Reserved<br>W | Reserved           | Reserved            | Reserved                 | Reserved | Reserved | Reserved  | Reserved              |

| 0x020F            | Reserved         | R<br>Reserved<br>W | Reserved           | Reserved            | Reserved                 | Reserved | Reserved | Reserved  | Reserved              |

| 0x0210-           | Reserved         | R 0                | 0                  | 0                   | 0                        | 0        | 0        | 0         | 0                     |

| 0x025F            |                  | W                  |                    |                     |                          |          |          |           |                       |

| 0x0260            | PTE              | R 0<br>W           | 0                  | 0                   | 0                        | 0        | 0        | PTE1      | PTE0                  |

MC9S12ZVM Family Reference Manual Rev. 2.11

#### Chapter 2 Port Integration Module (S12ZVMPIMV3)

| Global<br>Address | Register<br>Name | Bit 7           | 6 | 5                  | 4                  | 3     | 2                  | 1     | Bit 0 |

|-------------------|------------------|-----------------|---|--------------------|--------------------|-------|--------------------|-------|-------|

| 0x02D6            | PIES             | R 0<br>W        | 0 | PIES5 <sup>5</sup> | PIES4 <sup>5</sup> | PIES3 | PIES2              | PIES1 | PIES0 |

| 0x02D7            | PIFS             | R 0<br>W        | 0 | PIFS5 <sup>5</sup> | PIFS4 <sup>5</sup> | PIFS3 | PIFS2              | PIFS1 | PIFS0 |

| 0x02D8–<br>0x02DE | Reserved         | R 0<br>W        | 0 | 0                  | 0                  | 0     | 0                  | 0     | 0     |

| 0x02DF            | WOMS             | R 0<br>W        | 0 | WOMS5 <sup>5</sup> | WOMS4 <sup>5</sup> | WOMS3 | WOMS2              | WOMS1 | WOMS0 |

| 0x02E0–<br>0x02EF | Reserved         | R 0<br>W        | 0 | 0                  | 0                  | 0     | 0                  | 0     | 0     |

| 0x02F0            | PTP              | R 0<br>W        | 0 | 0                  | 0                  | 0     | PTP2 <sup>5</sup>  | PTP1  | PTP0  |

| 0x02F1            | PTIP             | R 0<br>W        | 0 | 0                  | 0                  | 0     | PTIP2 <sup>5</sup> | PTIP1 | PTIP0 |

| 0x02F2            | DDRP             | R 0<br>W        | 0 | 0                  | 0                  | 0     | DDRP2 <sup>5</sup> | DDRP1 | DDRP0 |

| 0x02F3            | PERP             | R 0<br>W        | 0 | 0                  | 0                  | 0     | PERP2 <sup>5</sup> | PERP1 | PERP0 |

| 0x02F4            | PPSP             | R 0<br>W        | 0 | 0                  | 0                  | 0     | PPSP2 <sup>5</sup> | PPSP1 | PPSP0 |

| 0x02F5            | Reserved         | R 0<br>W        | 0 | 0                  | 0                  | 0     | 0                  | 0     | 0     |

| 0x02F6            | PIEP             | R<br>OCIE1<br>W | 0 | 0                  | 0                  | 0     | PIEP2 <sup>5</sup> | PIEP1 | PIEP0 |

| 0x02F7            | PIFP             | R<br>OCIF1<br>W | 0 | 0                  | 0                  | 0     | PIFP2 <sup>5</sup> | PIFP1 | PIFP0 |

MC9S12ZVM Family Reference Manual Rev. 2.11

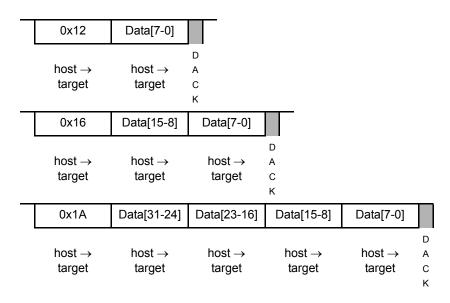

the BDCCSRL status byte is returned before the read data. This status byte reflects the state after the memory read was performed. If enabled, an ACK pulse is driven before the data bytes are transmitted. The effect of the access size and alignment on the next address to be accessed is explained in more detail in Section 5.4.5.2".

#### NOTE

DUMP\_MEM{\_WS} is a valid command only when preceded by SYNC, NOP, READ\_MEM{\_WS}, or another DUMP\_MEM{\_WS} command. Otherwise, an illegal command response is returned, setting the ILLCMD bit. NOP can be used for inter-command padding without corrupting the address pointer.

The size field (sz) is examined each time a DUMP\_MEM{\_WS} command is processed, allowing the operand size to be dynamically altered. The examples show the DUMP\_MEM.B{\_WS}, DUMP\_MEM.W{\_WS} and DUMP\_MEM.L{\_WS} commands.

## 5.4.4.6 FILL\_MEM.sz, FILL\_MEM.sz\_WS

#### FILL\_MEM.sz

Write memory specified by debug address register, then Non-intrusive increment address

#### FILL\_MEM.sz\_WS

Write memory specified by debug address register with Non-intrusive status, then increment address

| 0x13 Data[7-0] BDCCSRL |

|------------------------|

|------------------------|

#### MC9S12ZVM Family Reference Manual Rev. 2.11

| Field          | Description                                                                                                                                                              |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>EEVF      | <ul> <li>External Event Flag — Indicates the occurrence of an external event during the debug session.</li> <li>0 No external event</li> <li>1 External event</li> </ul> |

| 3–0<br>ME[3:0] | Match Event[3:0]— Indicates a comparator match event on the corresponding comparator channel.                                                                            |

#### Table 6-23. DBGEFR Field Descriptions

# 6.3.2.11 Debug Status Register (DBGSR)

Address: 0x010B

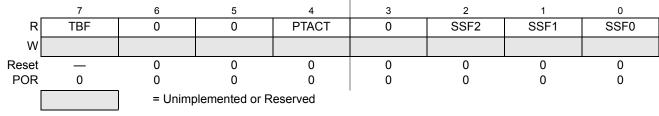

Figure 6-13. Debug Status Register (DBGSR)

Read: Anytime.

Write: Never.

#### Table 6-24. DBGSR Field Descriptions

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TBF        | <b>Trace Buffer Full</b> — The TBF bit indicates that the trace buffer has been filled with data since it was last armed. If this bit is set, then all trace buffer lines contain valid data, regardless of the value of DBGCNT bits CNT[6:0]. The TBF bit is cleared when ARM in DBGC1 is written to a one. The TBF is cleared by the power on reset initialization. Other system generated resets have no affect on this bit                                                                                                                                                                                                                         |

| 4<br>PTACT      | <b>Profiling Transmission Active</b> — The PTACT bit, when set, indicates that the profiling transmission is still active. When clear, PTACT then profiling transmission is not active. The PTACT bit is set when profiling begins with the first PTS format entry to the trace buffer. The PTACT bit is cleared when the profiling transmission ends.                                                                                                                                                                                                                                                                                                 |

| 2–0<br>SSF[2:0] | <b>State Sequencer Flag Bits</b> — The SSF bits indicate the current State Sequencer state. During a debug session on each transition to a new state these bits are updated. If the debug session is ended by software clearing the ARM bit, then these bits retain their value to reflect the last state of the state sequencer before disarming. If a debug session is ended by an internal event, then the state sequencer returns to State0 and these bits are cleared to indicate that State0 was entered during the session. On arming the module the state sequencer enters State1 and these bits are forced to SSF[2:0] = 001. See Table 6-25. |

| SSF[2:0] | Current State     |

|----------|-------------------|

| 000      | State0 (disarmed) |

| 001      | State1            |

| 010      | State2            |

| 011      | State3            |

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

# 8.1.3 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the S12CPMU\_UHV\_V10\_V6.

### 8.1.3.1 Run Mode

The voltage regulator is in Full Performance Mode (FPM).

## NOTE

The voltage regulator is active, providing the nominal supply voltages with full current sourcing capability (see also Appendix for VREG electrical parameters). The features ACLK clock source, Low Voltage Interrupt (LVI), Low Voltage Reset (LVR) and Power-On Reset (POR) are available.

The Phase Locked Loop (PLL) is on.

The Internal Reference Clock (IRC1M) is on.

The API is available.

- PLL Engaged Internal (PEI)

- This is the default mode after System Reset and Power-On Reset.

- The Bus Clock is based on the PLLCLK.

- After reset the PLL is configured for 50MHz VCOCLK operation.

Post divider is 0x03, so PLLCLK is VCOCLK divided by 4, that is 12.5MHz and Bus Clock is

- 6.25MHz.

- The PLL can be re-configured for other bus frequencies.

- The reference clock for the PLL (REFCLK) is based on internal reference clock IRC1M.

- PLL Engaged External (PEE)

- The Bus Clock is based on the PLLCLK.

- This mode can be entered from default mode PEI by performing the following steps:

- Configure the PLL for desired bus frequency.

- Program the reference divider (REFDIV[3:0] bits) to divide down oscillator frequency if necessary.

- Enable the external oscillator (OSCE bit).

- Wait for oscillator to start up (UPOSC=1) and PLL to lock (LOCK=1).

- PLL Bypassed External (PBE)

- The Bus Clock is based on the Oscillator Clock (OSCCLK).

- The PLLCLK is always on to qualify the external oscillator clock. Therefore it is necessary to make sure a valid PLL configuration is used for the selected oscillator frequency.

- This mode can be entered from default mode PEI by performing the following steps:

| Field        | Description                                                                                                                                                                                                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>EXTS1ON | <ul> <li>External voltage regulator Enable Bit for VDDS1 domain — Should be enabled after system startup if VDDS1 is used.</li> <li>0 VDDS1 domain disabled</li> <li>1 VDDS1 domain enabled. BCTLS1 pin is active.</li> </ul>                                                                                           |

| 2<br>EXTCON  | <ul> <li>External voltage regulator Enable Bit for VDDC domain — Should be disabled after system startup if VDDC domain is not used. Must be kept set, if an internal or external CANPHY is present in the application.</li> <li>0 VDDC domain disabled</li> <li>1 VDDC domain enabled. BCTLC pin is active.</li> </ul> |

| 1<br>EXTXON  | <ul> <li>External voltage regulator Enable Bit for VDDX domain — Should be set to 1 if external BJT is present on the PCB, cleared otherwise.</li> <li>0 VDDX control loop does not use external BJT</li> <li>1 VDDX control loop uses external BJT</li> </ul>                                                          |

| 0<br>INTXON  | <ul> <li>Internal voltage regulator Enable Bit for VDDX domain— Should be set to 1 if no external BJT is present on the PCB, cleared otherwise.</li> <li>0 VDDX control loop does not use internal power transistor</li> <li>1 VDDX control loop uses internal power transistor</li> </ul>                              |

#### Table 8-31. CPMUVREGCTL Field Descriptions (continued)

# 8.3.2.28 S12CPMU\_UHV\_V10\_V6 Oscillator Register 2 (CPMUOSC2)

This registers configures the external oscillator (XOSCLCP).

Module Base + 0x001E

Figure 8-39. S12CPMU\_UHV\_V10\_V6 Oscillator Register 2 (CPMUOSC2)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

#### Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

/\* put your code to loop and wait for the LOCKIF or \*/ /\* poll CPMUIFLG register until both LOCK status is "1" \*/ /\* that is CPMUIFLG == 0x18 \*/

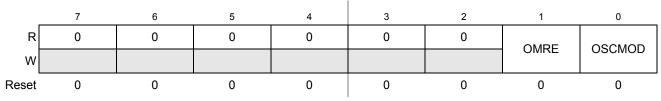

# 9.5.2.2 ADC Control Register 1 (ADCCTL\_1)

Module Base + 0x0001

Read: Anytime

Write:

- Bit CSL\_BMOD and RVL\_BMOD writable if bit ADC\_EN clear or bit SMOD\_ACC set

- Bit SMOD\_ACC only writable in MCU Special Mode

- Bit AUT\_RSTA writable anytime

#### Table 9-5. ADCCTL\_1 Field Descriptions

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CSL_BMOD | <ul> <li>CSL Buffer Mode Select Bit — This bit defines the CSL buffer mode. This bit is only writable if ADC_EN is clear.</li> <li>0 CSL single buffer mode.</li> <li>1 CSL double buffer mode.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6<br>RVL_BMOD | <ul> <li>RVL Buffer Mode Select Bit — This bit defines the RVL buffer mode.</li> <li>0 RVL single buffer mode</li> <li>1 RVL double buffer mode</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5<br>SMOD_ACC | <ul> <li>Special Mode Access Control Bit — This bit controls register access rights in MCU Special Mode. This bit is automatically cleared when leaving MCU Special Mode.</li> <li>Note: When this bit is set also the ADCCMD register is writeable via the data bus to allow modification of the current command for debugging purpose. But this is only possible if the current command is not already processed (conversion not started).</li> <li>Please see access details given for each register.</li> <li>Care must be taken when modifying ADC registers while bit SMOD_ACC is set to not corrupt a possible ongoing conversion.</li> <li>0 Normal user access - Register write restrictions exist as specified for each bit.</li> <li>1 Special access - Register write restrictions are lifted.</li> </ul> |

| 4<br>AUT_RSTA | <ul> <li>Automatic Restart Event after exit from MCU Stop and Wait Mode (SWAI set) — This bit controls if a Restart Event is automatically generated after exit from MCU Stop Mode or Wait Mode with bit SWAI set. It can be configured for ADC conversion flow control mode "Trigger Mode" and "Restart Mode" (anytime during application runtime).</li> <li>0 No automatic Restart Event after exit from MCU Stop Mode.</li> <li>1 Automatic Restart Event occurs after exit from MCU Stop Mode.</li> </ul>                                                                                                                                                                                                                                                                                                         |

# 10.3 Memory Map and Register Definition

This section provides the detailed information of all registers for the BATS module.

# 10.3.1 Register Summary

Figure 10-2 shows the summary of all implemented registers inside the BATS module.

#### NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address Offset<br>Register Name    |        | Bit 7    | 6        | 5        | 4        | 3        | 2        | 1        | Bit 0    |  |

|------------------------------------|--------|----------|----------|----------|----------|----------|----------|----------|----------|--|

| 0x0000                             | R      | 0        | BVHS     |          | 214-01   |          | BSUSE    | 0        | 0        |  |

| BATE                               | W      |          | вина     | BVL      | 6[1:0]   | BSUAE    | BSUSE    |          |          |  |

| 0x0001<br>BATSR                    | R      | 0        | 0        | 0        | 0        | 0        | 0        | BVHC     | BVLC     |  |

|                                    | W      |          |          |          |          |          |          |          |          |  |

| 0x0002                             | R      | 0        | 0        | 0        | 0        | 0        | 0        | BVHIE    | BVLIE    |  |

| BATIE                              | W      |          |          |          |          |          |          | BVHIE    | DVLIL    |  |

| 0x0003<br>BATIF                    | R      | 0        | 0        | 0        | 0        | 0        | 0        | BVHIF    | BVLIF    |  |

| BATT                               | W      |          |          |          |          |          |          | BVIII    | DVLII    |  |

| 0x0004 - 0x0005                    | R      | 0        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |  |

| Reserved                           | W      |          |          |          |          |          |          |          |          |  |

|                                    | _      |          |          |          |          |          |          |          |          |  |

| 0x0006 - 0x0007<br>Reserved        | R<br>W | Reserved |  |

| = Unimplemented                    |        |          |          |          |          |          |          |          |          |  |

| Figure 10-2. BATS Register Summary |        |          |          |          |          |          |          |          |          |  |

# 10.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. Unused bits read back zero.

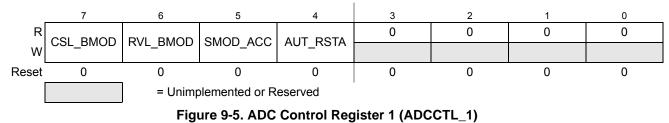

Figure 13-28. Identifier Register 2 (IDR2) — Extended Identifier Mapping

| ld |                            | Description                                                           |

|----|----------------------------|-----------------------------------------------------------------------|

| 0  | Extended Formet Identifier | The identifiant consist of 20 bits (IDI20:01) for the outended formet |

| Field    | Description                                                                                                                                                                                                                                                                                                  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ID[14:7] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

#### Module Base + 0x00X3

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | RTR |

| Reset: | х   | x   | х   | x   | x   | х   | x   | x   |

Figure 13-29. Identifier Register 3 (IDR3) — Extended Identifier Mapping

#### Table 13-29. IDR3 Register Field Descriptions — Extended

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1<br>ID[6:0] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                                      |

| 0<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the remote transmission request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul> |

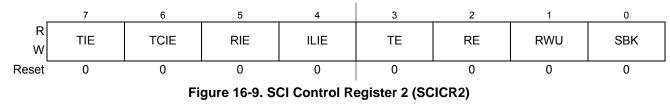

# 16.3.2.6 SCI Control Register 2 (SCICR2)

Module Base + 0x0003

#### Read: Anytime

Write: Anytime

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>TIE  | Transmitter Interrupt Enable Bit — TIE enables the transmit data register empty flag, TDRE, to generate interrupt requests.         0       TDRE interrupt requests disabled         1       TDRE interrupt requests enabled                                                                                                                                                                                                                  |

| 6<br>TCIE | Transmission Complete Interrupt Enable Bit — TCIE enables the transmission complete flag, TC, to generate interrupt requests.         0       TC interrupt requests disabled         1       TC interrupt requests enabled                                                                                                                                                                                                                    |

| 5<br>RIE  | <ul> <li>Receiver Full Interrupt Enable Bit — RIE enables the receive data register full flag, RDRF, or the overrun flag, OR, to generate interrupt requests.</li> <li>0 RDRF and OR interrupt requests disabled</li> <li>1 RDRF and OR interrupt requests enabled</li> </ul>                                                                                                                                                                 |

| 4<br>ILIE | Idle Line Interrupt Enable Bit — ILIE enables the idle line flag, IDLE, to generate interrupt requests.         0 IDLE interrupt requests disabled         1 IDLE interrupt requests enabled                                                                                                                                                                                                                                                  |

| 3<br>TE   | Transmitter Enable Bit — TE enables the SCI transmitter and configures the TXD pin as being controlled by the SCI. The TE bit can be used to queue an idle preamble.         0       Transmitter disabled         1       Transmitter enabled                                                                                                                                                                                                 |

| 2<br>RE   | Receiver Enable Bit — RE enables the SCI receiver.         0 Receiver disabled         1 Receiver enabled                                                                                                                                                                                                                                                                                                                                     |

| 1<br>RWU  | <ul> <li>Receiver Wakeup Bit — Standby state</li> <li>Normal operation.</li> <li>RWU enables the wakeup function and inhibits further receiver interrupt requests. Normally, hardware wakes the receiver by automatically clearing RWU.</li> </ul>                                                                                                                                                                                            |

| 0<br>SBK  | <ul> <li>Send Break Bit — Toggling SBK sends one break character (10 or 11 logic 0s, respectively 13 or 14 logics 0s if BRK13 is set). Toggling implies clearing the SBK bit before the break character has finished transmitting. As long as SBK is set, the transmitter continues to send complete break characters (10 or 11 bits, respectively 13 or 14 bits).</li> <li>No break characters</li> <li>Transmit break characters</li> </ul> |

Chapter 17 Serial Peripheral Interface (S12SPIV5)

## 17.4.7.5.2 SPIF

SPIF occurs when new data has been received and copied to the SPI data register. After SPIF is set, it does not clear until it is serviced. SPIF has an automatic clearing process, which is described in Section 17.3.2.4, "SPI Status Register (SPISR)".

# 17.4.7.5.3 SPTEF

SPTEF occurs when the SPI data register is ready to accept new data. After SPTEF is set, it does not clear until it is serviced. SPTEF has an automatic clearing process, which is described in Section 17.3.2.4, "SPI Status Register (SPISR)".

#### Chapter 19 LIN/HV Physical Layer (S12LINPHYV3)

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LPDTDIS      | TxD-dominant timeout disable Bit — This bit disables the TxD-dominant timeout feature. Disabling this feature is only recommended for using the LIN Physical Layer for other applications than LIN protocol. It is only writable in shutdown mode (LPE=0).<br>0 TxD-dominant timeout feature is enabled.<br>1 TxD-dominant timeout feature is disabled.                                                                                                                                                                                                                                                                                                                                                                                                          |

| 1-0<br>LPSLR[1:0] | <ul> <li>Slew-Rate Bits — Please see section 19.4.2 for details on how the slew rate control works. These bits are only writable in shutdown mode (LPE=0).</li> <li>00 Normal Slew Rate (optimized for 20 kbit/s).</li> <li>01 Slow Slew Rate (optimized for 10.4 kbit/s).</li> <li>10 Fast Mode Slew Rate (up to 250 kbit/s). This mode is not compliant with the LIN Protocol (LIN electrical characteristics like duty cycles, reference levels, etc. are not fulfilled). It is only meant to be used for fast data transmission. Please refer to section 19.4.2.2 for more details on fast mode.Please note that an external pullup resistor stronger than 1 kΩ might be necessary for the range 100 kbit/s to 250 kbit/s.</li> <li>11 Reserved .</li> </ul> |

#### Table 19-5. LPSLRM Field Description

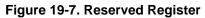

# 19.3.2.5 Reserved Register

Module Base + Address 0x0004

Access: User read/write<sup>(1)</sup>

|        | 7        | 6            | 5        | 4        | 3        | 2        | 1        | 0        |

|--------|----------|--------------|----------|----------|----------|----------|----------|----------|

| R<br>W | Reserved | Reserved     | Reserved | Reserved | Reserved | Reserved | Reserved | Reserved |

| Reset  | Х        | х            | Х        | Х        | Х        | Х        | Х        | х        |

|        |          | = Unimplemer | nted     |          |          |          |          |          |

1. Read: Anytime

Write: Only in special mode

#### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in special mode can alter the module's functionality.

#### Table 19-6. Reserved Register Field Description

| Field           | Description                                                                                               |

|-----------------|-----------------------------------------------------------------------------------------------------------|

| 7-0<br>Reserved | These reserved bits are used for test purposes. Writing to these bits can alter the module functionality. |

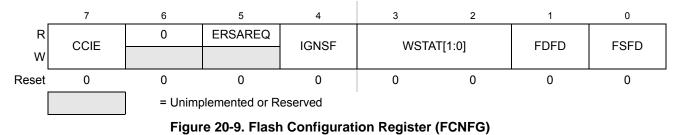

Offset Module Base + 0x0004

CCIE, IGNSF, WSTAT, FDFD, and FSFD bits are readable and writable, ERSAREQ bit is read only, and remaining bits read 0 and are not writable.

| Table 20-14. | FCNFG | Field | Descriptions |

|--------------|-------|-------|--------------|

|--------------|-------|-------|--------------|

| Field             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>CCIE         | <ul> <li>Command Complete Interrupt Enable — The CCIE bit controls interrupt generation when a Flash command has completed.</li> <li>0 Command complete interrupt disabled</li> <li>1 An interrupt will be requested whenever the CCIF flag in the FSTAT register is set (see Section 20.3.2.7)</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 5<br>ERSAREQ      | Erase All Request — Requests the Memory Controller to execute the Erase All Blocks command and release security. ERSAREQ is not directly writable but is under indirect user control. Refer to the Reference Manual for assertion of the <i>soc_erase_all_req</i> input to the FTMRZ module.<br>0 No request or request complete<br>1 Request to:<br>a) run the Erase All Blocks command<br>b) verify the erased state<br>c) program the security byte in the Flash Configuration Field to the unsecure state<br>d) release MCU security by setting the SEC field of the FSEC register to the unsecure state as defined in<br>Table 20-9 of Section 20.3.2.2.<br>The ERSAREQ bit sets to 1 when <i>soc_erase_all_req</i> is asserted, CCIF=1 and the Memory Controller starts<br>executing the sequence. ERSAREQ will be reset to 0 by the Memory Controller when the operation is completed<br>(see Section 20.4.7.7.1). |  |  |  |  |  |

| 4<br>IGNSF        | <ul> <li>Ignore Single Bit Fault — The IGNSF controls single bit fault reporting in the FERSTAT register (see Section 20.3.2.8).</li> <li>0 All single bit faults detected during array reads are reported</li> <li>1 Single bit faults detected during array reads are not reported and the single bit fault interrupt will not be generated</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| 3–2<br>WSTAT[1:0] | <b>Wait State control bits</b> — The WSTAT[1:0] bits define how many wait-states are inserted on each read access to the Flash as shown on Table 20-15. Right after reset the maximum amount of wait-states is set, to be later reconfigured by the application if needed. Depending on the system operating frequency being used the number of wait-states can be reduced or disabled, please refer to the Data Sheet for details. For additional information regarding the procedure to change this configuration please see Section 20.4.3. The WSTAT[1:0] bits should not be updated while the Flash is executing a command (CCIF=0); if that happens the value of this field will not change and no action will take place.                                                                                                                                                                                          |  |  |  |  |  |

# 20.4.5 Flash Command Operations

Flash command operations are used to modify Flash memory contents.

The next sections describe:

- How to write the FCLKDIV register that is used to generate a time base (FCLK) derived from BUSCLK for Flash program and erase command operations

- The command write sequence used to set Flash command parameters and launch execution

- Valid Flash commands available for execution, according to MCU functional mode and MCU security state.

# 20.4.5.1 Writing the FCLKDIV Register

Prior to issuing any Flash program or erase command after a reset, the user is required to write the FCLKDIV register to divide BUSCLK down to a target FCLK of 1 MHz. Table 20-8 shows recommended values for the FDIV field based on BUSCLK frequency.

### NOTE

Programming or erasing the Flash memory cannot be performed if the bus clock runs at less than 0.8 MHz. Setting FDIV too high can destroy the Flash memory due to overstress. Setting FDIV too low can result in incomplete programming or erasure of the Flash memory cells.

When the FCLKDIV register is written, the FDIVLD bit is set automatically. If the FDIVLD bit is 0, the FCLKDIV register has not been written since the last reset. If the FCLKDIV register has not been written, any Flash program or erase command loaded during a command write sequence will not execute and the ACCERR bit in the FSTAT register will set.

# 20.4.5.2 Command Write Sequence

The Memory Controller will launch all valid Flash commands entered using a command write sequence.

Before launching a command, the ACCERR and FPVIOL bits in the FSTAT register must be clear (see Section 20.3.2.7) and the CCIF flag should be tested to determine the status of the current command write sequence. If CCIF is 0, the previous command write sequence is still active, a new command write sequence cannot be started, and all writes to the FCCOB register are ignored.

### 20.4.5.2.1 Define FCCOB Contents

The FCCOB parameter fields must be loaded with all required parameters for the Flash command being executed. The CCOBIX bits in the FCCOBIX register must reflect the amount of words loaded into the FCCOB registers (see Section 20.3.2.3).

The contents of the FCCOB parameter fields are transferred to the Memory Controller when the user clears the CCIF command completion flag in the FSTAT register (writing 1 clears the CCIF to 0). The CCIF flag will remain clear until the Flash command has completed. Upon completion, the Memory Controller will return CCIF to 1 and the FCCOB register will be used to communicate any results. The flow for a generic command write sequence is shown in Figure 20-30.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 20-29)                      |

|          |           | Set if an invalid global address [23:0] is supplied see Table 20-3)                 |

|          |           | Set if a misaligned phrase address is supplied (global address [2:0] != 000)        |

|          | FPVIOL    | Set if the selected P-Flash sector is protected                                     |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 20-51. Erase P-Flash Sector Command Error Handling

# 20.4.7.10 Unsecure Flash Command

The Unsecure Flash command will erase the entire P-Flash and EEPROM memory space and, if the erase is successful, will release security.

Table 20-52. Unsecure Flash Command FCCOB Requirements

| Register | FCCOB Parameters |              |

|----------|------------------|--------------|

| FCCOB0   | 0x0B             | Not required |

Upon clearing CCIF to launch the Unsecure Flash command, the Memory Controller will erase the entire P-Flash and EEPROM memory space and verify that it is erased. If the Memory Controller verifies that the entire Flash memory space was properly erased, security will be released. If the erase verify is not successful, the Unsecure Flash operation sets MGSTAT1 and terminates without changing the security state. During the execution of this command (CCIF=0) the user must not write to any Flash module register. The CCIF flag is set after the Unsecure Flash operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 000 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 20-29)                      |

|          | FPVIOL    | Set if any area of the P-Flash or EEPROM memory is protected                        |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 20-53. Unsecure Flash Command Error Handling

# 20.4.7.11 Verify Backdoor Access Key Command

The Verify Backdoor Access Key command will only execute if it is enabled by the KEYEN bits in the FSEC register (see Table 20-10). The Verify Backdoor Access Key command releases security if user-supplied keys match those stored in the Flash security bytes of the Flash configuration field (see Table 20-

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          |           | Set if command not available in current mode (see Table 20-29)                      |

|          |           | Set if an invalid global address [23:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 20-65. Program EEPROM Command Error Handling

## 20.4.7.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

Table 20-66. Erase EEPROM Sector Command FCCOB Requirements

| Register | FCCOB Parameters                                                                                               |                                                    |

|----------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| FCCOB0   | 0x12                                                                                                           | Global address [23:16] to identify<br>EEPROM block |

| FCCOB1   | Global address [15:0] anywhere within the sector to be erased.<br>See Section 20.1.2.2 for EEPROM sector size. |                                                    |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

| FSTAT    | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |

|          |           | Set if command not available in current mode (see Table 20-29)                      |

|          |           | Set if an invalid global address [23:0] is supplied see Table 20-3                  |

|          |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 20-67. Erase EEPROM Sector Command Error Handling

# 21.5.2.5 Standby Mode

Standby is a reduced current consumption mode and is entered during RPM following a stop mode request. The transceiver and bus error diagnostics are disabled. The CPTXD-dominant timeout counter is stopped. CANH and CANL lines are pulled to VSSC via high-ohmic input resistors of the receiver. The SPLIT pin is set to high-impedance. The internal mid-point reference is set to 0V. All voltage failure and over-current monitors are disabled.

Standby is left as soon as the device returns from RPM.

# 21.5.3 Configurable Wake-Up

If the wake-up function is enabled, the CAN Physical Layer provides an asynchronous path through CPRXD to the MSCAN to support wake-up from stop mode. The CPRXD signal is switched from precision receiver to the low-power wake-up receiver as long as the device resides in RPM.

In order to avoid false wake-up after entering stop mode, a pulse filter can be enabled and configured to mask the first or first two wake-up events from the MSCAN input. The CPRXD output is held at recessive level until the selected number of wake-up events have been detected as shown in Figure 21-11.

A valid wakeup-event is defined as a dominant level with a length of min.  $t_{CPWUP}$  followed by a recessive level of length  $t_{CPWUP}$ .

The wake-up filter specification  $t_{WUP}$  of the MSCAN applies to wake-up the MSCAN from sleep mode. Refer to MSCAN chapter. After wake-up the CAN Physical Layer automatically returns to the mode where stop mode was requested.

Refer to 21.6.2, "Wake-up Mechanism" for setup information.