#### Details

#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 50MHz                                                                    |

| Connectivity               | CANbus, SCI, SPI                                                         |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 31                                                                       |

| Program Memory Size        | 128KB (128K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                               |

| Data Converters            | A/D 9x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP Exposed Pad                                                      |

| Supplier Device Package    | 64-HLQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvmc12f3wkhr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Up to one additional SCI (not connected to LIN physical layer)

- On-chip LIN physical layer transceiver fully compliant with the LIN 2.2 standard (S12ZVML versions)

- One High Voltage physical interface. (ZVM32, ZVM16 versions only)

- 4-channel timer module (TIM0) with input capture/output compare

- 2-channel timer module (TIM1) with input capture/output compare (ZVMC256 version only)

- One 8-bit, 8-channel pulse width modulator (PWM) module. (ZVMC256 version only)

- MSCAN (1 Mbit/s, CAN 2.0 A, B software compatible) module

- On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

Optional VREG ballast control output to supply an external CAN physical layer

- CAN Physical Layer, ISO 11898-2 and ISO 11898-5 compliant. (ZVMC256 version only)

- Two voltage regulator outputs to supply external loads. (ZVMC256 version only)

- Two current sense circuits for overcurrent detection or torque measurement

- Autonomous periodic interrupt (API)

- 20mA high-current output for use as Hall sensor supply

- Supply voltage sense with low battery warning

- Chip temperature sensor

- One High Voltage Input (ZVMC256 version only)

# 1.4 Module Features

The following sections provide more details of the integrated modules.

# 1.4.1 S12Z Central Processor Unit (CPU)

The S12Z CPU is a revolutionary high-speed core, with code size and execution efficiencies over the S12X CPU. The S12Z CPU also provides a linear memory map eliminating the inconvenience and performance impact of page swapping.

- Harvard Architecture parallel data and code access

- 3 stage pipeline

- 32-Bit wide instruction and databus

- 32-Bit ALU

- 24-bit addressing, of 16MB linear address space

- Instructions and Addressing modes optimized for C-Programming & Compiler

- MAC unit 32bit += 32bit\*32bit

- Hardware divider

- Single cycle multi-bit shifts (Barrel shifter)

- Special instructions for fixed point math

- Unimplemented opcode traps

## 1.13.6.3 Dead time Distortion Correction

PMSM motor control applications driven by sinusoidal voltages by default require zero crossing information of phase currents to determine the point in time to change sign of deadtime compensation value to be added to duty cycles.

The GDU phase comparator signals are connected internally to the PMF ISx inputs. This allows the dead time distortion correction to be applied directly based on the phase status.

- 1. Align rotor to stator field.

- 2. Await phase comparator status change.

- 3. Switch to alternate duty cycle register to compensate distortion.

Chapter 5 Background Debug Controller (S12ZBDCV2)

Active Background

This command is used to exit active BDM and begin (or resume) execution of CPU application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes. If enabled, an ACK is driven on exiting active BDM.

If a GO command is issued whilst the BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

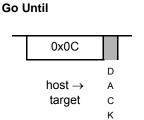

### 5.4.4.8 GO\_UNTIL

This command is used to exit active BDM and begin (or resume) execution of application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes.

After resuming application code execution, if ACK is enabled, the BDC awaits a return to active BDM before driving an ACK pulse. timeouts do not apply when awaiting a GO\_UNTIL command ACK.

If a GO\_UNTIL is not acknowledged then a SYNC command must be issued to end the pending GO\_UNTIL.

If a GO\_UNTIL command is issued whilst BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

If ACK handshaking is disabled, the GO\_UNTIL command is identical to the GO command.

### 5.4.4.9 NOP

Active Background

NOP performs no operation and may be used as a null command where required.

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

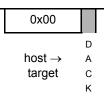

## 8.3.2.8 S12CPMU\_UHV\_V10\_V6 Interrupt Enable Register (CPMUINT)

This register enables S12CPMU\_UHV\_V10\_V6 interrupt requests.

Module Base + 0x0008

Figure 8-13. S12CPMU\_UHV\_V10\_V6 Interrupt Enable Register (CPMUINT)

Read: Anytime

Write: Anytime

#### Table 8-6. CPMUINT Field Descriptions

| Field       | Description                                                                                                                                              |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>RTIE   | Real Time Interrupt Enable Bit         0 Interrupt requests from RTI are disabled.         1 Interrupt will be requested whenever RTIF is set.           |  |  |  |  |  |

| 4<br>LOCKIE | PLL Lock Interrupt Enable Bit         0 PLL LOCK interrupt requests are disabled.         1 Interrupt will be requested whenever LOCKIF is set.          |  |  |  |  |  |

| 1<br>OSCIE  | Oscillator Corrupt Interrupt Enable Bit<br>0 Oscillator Corrupt interrupt requests are disabled.<br>1 Interrupt will be requested whenever OSCIF is set. |  |  |  |  |  |

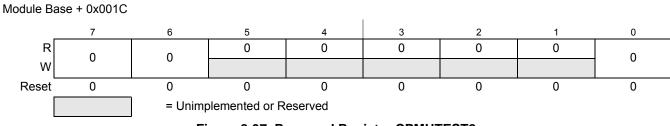

## 8.3.2.26 Reserved Register CPMUTEST2

### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV\_V10\_V6's functionality.

Figure 8-37. Reserved Register CPMUTEST2

Read: Anytime

Write: Only in Special Mode

#### Table 8-35. Reset Summary

| Reset Source                   | Local Enable                                                      |

|--------------------------------|-------------------------------------------------------------------|

| Oscillator Clock Monitor Reset | OSCE Bit in CPMUOSC register and<br>OMRE Bit in CPMUOSC2 register |

| COP Reset                      | CR[2:0] in CPMUCOP register                                       |

## 8.5.2 Description of Reset Operation

Upon detection of any reset of Table 8-35, an internal circuit drives the RESET pin low for 512 PLLCLK cycles. After 512 PLLCLK cycles the RESET pin is released. The internal reset of the MCU remains asserted while the reset generator completes the 768 PLLCLK cycles long reset sequence. In case the RESET pin is externally driven low for more than these 768 PLLCLK cycles (External Reset), the internal reset remains asserted longer.

### NOTE

While System Reset is asserted the PLLCLK runs with the frequency  $f_{\mbox{VCORST}}$

### Figure 8-45. RESET Timing

## 8.5.3 Oscillator Clock Monitor Reset

If the external oscillator is enabled (OSCE=1) and the oscillator clock monitor reset is enabled (OMRE=1), then in case of loss of oscillation or the oscillator frequency drops below the failure assert frequency  $f_{CMFA}$  (see device electrical characteristics for values), the S12CPMU\_UHV\_V10\_V6 generates an Oscillator Clock Monitor Reset. In Full Stop Mode the external oscillator and the oscillator clock monitor are disabled.

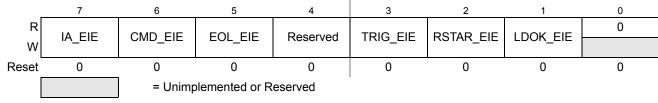

## 9.5.2.7 ADC Error Interrupt Enable Register (ADCEIE)

Module Base + 0x0006

### Figure 9-10. ADC Error Interrupt Enable Register (ADCEIE)

Read: Anytime

Write: Anytime

| Field          | Description                                                                                                                                                                                                                                                                 |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>IA_EIE    | Illegal Access Error Interrupt Enable Bit — This bit enables the illegal access error interrupt.         0 Illegal access error interrupt disabled.         1 Illegal access error interrupt enabled.                                                                       |

| 6<br>CMD_EIE   | <ul> <li>Command Value Error Interrupt Enable Bit — This bit enables the command value error interrupt.</li> <li>0 Command value interrupt disabled.</li> <li>1 Command value interrupt enabled.</li> </ul>                                                                 |

| 5<br>EOL_EIE   | <ul> <li>"End Of List" Error Interrupt Enable Bit — This bit enables the "End Of List" error interrupt.</li> <li>"End Of List" error interrupt disabled.</li> <li>"End Of List" error interrupt enabled.</li> </ul>                                                         |

| 3<br>TRIG_EIE  | <ul> <li>Conversion Sequence Trigger Error Interrupt Enable Bit — This bit enables the conversion sequence trigger error interrupt.</li> <li>Conversion sequence trigger error interrupt disabled.</li> <li>Conversion sequence trigger error interrupt enabled.</li> </ul> |

| 2<br>RSTAR_EIE | <ul> <li>Restart Request Error Interrupt Enable Bit— This bit enables the restart request error interrupt.</li> <li>0 Restart Request error interrupt disabled.</li> <li>1 Restart Request error interrupt enabled.</li> </ul>                                              |

| 1<br>LDOK_EIE  | <ul> <li>Load OK Error Interrupt Enable Bit — This bit enables the Load OK error interrupt.</li> <li>0 Load OK error interrupt disabled.</li> <li>1 Load OK error interrupt enabled.</li> </ul>                                                                             |

# 11.2 External Signal Description

The TIM16B4CV3 module has a selected number of external pins. Refer to device specification for exact number.

# 11.2.1 IOC3 - IOC0 — Input Capture and Output Compare Channel 3-0

Those pins serve as input capture or output compare for TIM16B4CV3 channel.

### NOTE

For the description of interrupts see Section 11.6, "Interrupts".

# 11.3 Memory Map and Register Definition

This section provides a detailed description of all memory and registers.

## 11.3.1 Module Memory Map

The memory map for the TIM16B4CV3 module is given below in Figure 11-3. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the TIM16B4CV3 module and the address offset for each register.

## 11.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

| Register<br>Name |        | Bit 7        | 6            | 5            | 4            | 3      | 2      | 1      | Bit 0  |

|------------------|--------|--------------|--------------|--------------|--------------|--------|--------|--------|--------|

| 0x0000<br>TIOS   | R<br>W | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | IOS3   | IOS2   | IOS1   | IOS0   |

| 0x0001           | R      | 0            | 0            | 0            | 0            | 0      | 0      | 0      | 0      |

| CFORC            | W      | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | FOC3   | FOC2   | FOC1   | FOC0   |

| 0x0004<br>TCNTH  | R<br>W | TCNT15       | TCNT14       | TCNT13       | TCNT12       | TCNT11 | TCNT10 | TCNT9  | TCNT8  |

| 0x0005<br>TCNTL  | R<br>W | TCNT7        | TCNT6        | TCNT5        | TCNT4        | TCNT3  | TCNT2  | TCNT1  | TCNT0  |

| 0x0006           | R      | TEN          | TSWAI        | TSFRZ        | TFFCA        | PRNT   | 0      | 0      | 0      |

| TSCR1            | W      |              | IOWAI        | 101112       | IIIOA        |        |        |        |        |

| 0x0007<br>TTOV   | R<br>W | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | TOV3   | TOV2   | TOV1   | TOV0   |

| 0x0008           | R      | RESERV       | RESERV       | RESERV       | RESERV       | RESERV | RESERV | RESERV | RESERV |

| TCTL1            | W      | ED           | ED           | ED           | ED           | ED     | ED     | ED     | ED     |

Only bits related to implemented channels are valid.

Figure 11-3. TIM16B4CV3 Register Summary (Sheet 1 of 2)

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>TSFRZ | <ul> <li>Timer Stops While in Freeze Mode</li> <li>Allows the timer counter to continue running while in freeze mode.</li> <li>Disables the timer counter whenever the MCU is in freeze mode. This is useful for emulation.</li> <li>TSFRZ does not stop the pulse accumulator.</li> </ul>                                                                                                                                                                                                                                                                    |

| 4<br>TFFCA | <ul> <li>Timer Fast Flag Clear All</li> <li>Allows the timer flag clearing to function normally.</li> <li>For TFLG1(0x000E), a read from an input capture or a write to the output compare channel (0x0010–0x001F) causes the corresponding channel flag, CnF, to be cleared. For TFLG2 (0x000F), any access to the TCNT register (0x0004, 0x0005) clears the TOF flag. This has the advantage of eliminating software overhead in a separate clear sequence. Extra care is required to avoid accidental flag clearing due to unintended accesses.</li> </ul> |

| 3<br>PRNT  | <ul> <li>Precision Timer</li> <li>0 Enables legacy timer. PR0, PR1, and PR2 bits of the TSCR2 register are used for timer counter prescaler selection.</li> <li>1 Enables precision timer. All bits of the PTPSR register are used for Precision Timer Prescaler Selection, and all bits.</li> <li>This bit is writable only once out of reset.</li> </ul>                                                                                                                                                                                                    |

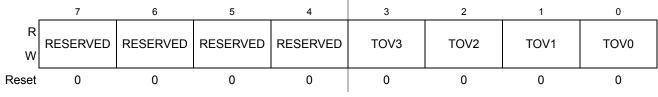

## 11.3.2.5 Timer Toggle On Overflow Register 1 (TTOV)

Module Base + 0x0007

Figure 11-9. Timer Toggle On Overflow Register 1 (TTOV)

#### Read: Anytime

Write: Anytime

#### Table 11-5. TTOV Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field           | Description                                                                                                                                                                                                                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>TOV[3:0] | <ul> <li>Toggle On Overflow Bits — TOVx toggles output compare pin on overflow. This feature only takes effect when in output compare mode. When set, it takes precedence over forced output compare</li> <li>Toggle output compare pin on overflow feature disabled.</li> <li>Toggle output compare pin on overflow feature enabled.</li> </ul> |

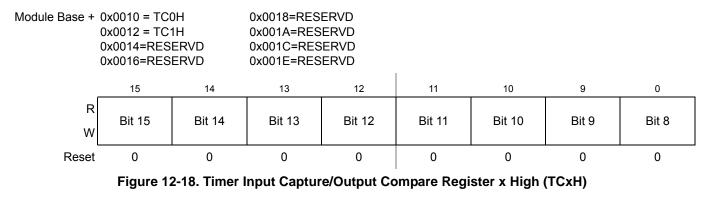

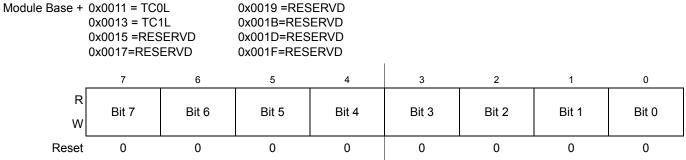

### 12.3.2.12 Timer Input Capture/Output Compare Registers High and Low 0– 1(TCxH and TCxL)

<sup>1</sup> This register is available only when the corresponding channel exists and is reserved if that channel does not exist. Writes to a reserved register have no functional effect. Reads from a reserved register return zeroes.

Depending on the TIOS bit for the corresponding channel, these registers are used to latch the value of the free-running counter when a defined transition is sensed by the corresponding input capture edge detector or to trigger an output action for output compare.

#### Read: Anytime

Write: Anytime for output compare function.Writes to these registers have no meaning or effect during input capture. All timer input capture/output compare registers are reset to 0x0000.

### NOTE

Read/Write access in byte mode for high byte should take place before low byte otherwise it will give a different result.

Chapter 13 Scalable Controller Area Network (S12MSCANV3)

Module Base + 0x000F

Access: User read/write<sup>(1)</sup>

|        | 7               | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|--------|-----------------|--------|--------|--------|--------|--------|--------|--------|

| R      | TXERR7          | TXERR6 | TXERR5 | TXERR4 | TXERR3 | TXERR2 | TXERR1 | TXERR0 |

| w      |                 |        |        |        |        |        |        |        |

| Reset: | 0               | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| [      | = Unimplemented |        |        |        |        |        |        |        |

Figure 13-19. MSCAN Transmit Error Counter (CANTXERR)

1. Read: Only when in sleep mode (SLPRQ = 1 and SLPAK = 1) or initialization mode (INITRQ = 1 and INITAK = 1) Write: Unimplemented

#### NOTE

Reading this register when in any other mode other than sleep or initialization mode, may return an incorrect value. For MCUs with dual CPUs, this may result in a CPU fault condition.

### 13.3.2.17 MSCAN Identifier Acceptance Registers (CANIDAR0-7)

On reception, each message is written into the background receive buffer. The CPU is only signalled to read the message if it passes the criteria in the identifier acceptance and identifier mask registers (accepted); otherwise, the message is overwritten by the next message (dropped).

The acceptance registers of the MSCAN are applied on the IDR0–IDR3 registers (see Section 13.3.3.1, "Identifier Registers (IDR0–IDR3)") of incoming messages in a bit by bit manner (see Section 13.4.3, "Identifier Acceptance Filter").

For extended identifiers, all four acceptance and mask registers are applied. For standard identifiers, only the first two (CANIDAR0/1, CANIDMR0/1) are applied.

| Module Base + 0x0010 to Module Base + 0x0013 Access: User read/write <sup>(1)</sup> |     |     |     |     |     |     |     | r read/write <sup>(1)</sup> |

|-------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----------------------------|

|                                                                                     | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0                           |

| R<br>W                                                                              | AC7 | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0                         |

| Reset                                                                               | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0                           |

#### Figure 13-20. MSCAN Identifier Acceptance Registers (First Bank) — CANIDAR0–CANIDAR3

1. Read: Anytime

Write: Anytime in initialization mode (INITRQ = 1 and INITAK = 1)

Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

# **15.2 Signal Descriptions**

If the signals are not used exclusively internally, the PMF has external pins named PWM0–5, FAULT0–5, and  $\overline{IS0}$ – $\overline{IS2}$ . Refer to device overview section.

## 15.2.1 PWM0–PWM5 Pins

PWM0-PWM5 are the output signals of the six PWM channels.

### NOTE

On MCUs with an integrated gate drive unit the PWM outputs are connected internally to the GDU inputs. In these cases the PWM signals may optionally be available on pins for monitoring purposes. Refer to the device overview section for routing options and pin locations.

## 15.2.2 FAULT0–FAULT5 Pins

FAULT0–FAULT5 are input signals for disabling selected PWM outputs (FAULT0-3) or drive the outputs to a configurable active/inactive state (FAULT4-5).

### NOTE

On MCUs with an integrated gate drive unit (GDU) either one or more FAULT inputs may be connected internally or/and available on an external pin. Refer to the device overview section for availability and pin locations.

# 15.2.3 IS0–IS2 Pins

ISO–IS2 are current status signals for top/bottom pulse width correction in complementary channel operation while deadtime is asserted.

### NOTE

Refer to the device overview section for signal availability on pins.

## 15.2.4 Global Load OK Signal — glb\_ldok

This device-internal PMF input signal is connected to the global load OK bit at integration level. For each of the three PWM generator time bases the use of the global load OK input can be enabled individually (GLDOKA,B,C).

## 15.2.5 Commutation Event Signal — async\_event

This device-internal PMF input signal is connected to the source of the asynchronous event generator (preferably timer output compare channel) at integration level.

The commutation event input must be enabled to take effect (ENCE=1). When this bit is set the PMFOUTC, PMFOUT, and MSKx registers switch from non-buffered to async\_event triggered double

# 16.5.2 Modes of Operation

### 16.5.2.1 Run Mode

Normal mode of operation.

To initialize a SCI transmission, see Section 16.4.5.2, "Character Transmission".

### 16.5.2.2 Wait Mode

SCI operation in wait mode depends on the state of the SCISWAI bit in the SCI control register 1 (SCICR1).

- If SCISWAI is clear, the SCI operates normally when the CPU is in wait mode.

- If SCISWAI is set, SCI clock generation ceases and the SCI module enters a power-conservation state when the CPU is in wait mode. Setting SCISWAI does not affect the state of the receiver enable bit, RE, or the transmitter enable bit, TE.

If SCISWAI is set, any transmission or reception in progress stops at wait mode entry. The transmission or reception resumes when either an internal or external interrupt brings the CPU out of wait mode. Exiting wait mode by reset aborts any transmission or reception in progress and resets the SCI.

## 16.5.2.3 Stop Mode

The SCI is inactive during stop mode for reduced power consumption. The STOP instruction does not affect the SCI register states, but the SCI bus clock will be disabled. The SCI operation resumes from where it left off after an external interrupt brings the CPU out of stop mode. Exiting stop mode by reset aborts any transmission or reception in progress and resets the SCI.

The receive input active edge detect circuit is still active in stop mode. An active edge on the receive input can be used to bring the CPU out of stop mode.

## 16.5.3 Interrupt Operation

This section describes the interrupt originated by the SCI block. The MCU must service the interrupt requests. Table 16-20 lists the eight interrupt sources of the SCI.

| Interrupt | Source    | Local Enable | Description                                                                                               |

|-----------|-----------|--------------|-----------------------------------------------------------------------------------------------------------|

| TDRE      | SCISR1[7] | TIE          | Active high level. Indicates that a byte was transferred from SCIDRH/L to the transmit shift register.    |

| TC        | SCISR1[6] | TCIE         | Active high level. Indicates that a transmit is complete.                                                 |

| RDRF      | SCISR1[5] | RIE          | Active high level. The RDRF interrupt indicates that received data is available in the SCI data register. |

| OR        | SCISR1[3] |              | Active high level. This interrupt indicates that an overrun condition has occurred.                       |

| IDLE      | SCISR1[4] | ILIE         | Active high level. Indicates that receiver input has become idle.                                         |

| Table | 16-20. | SCI | Interrupt | Sources |

|-------|--------|-----|-----------|---------|

|-------|--------|-----|-----------|---------|

| RXEDGIF | SCIASR1[7] | RXEDGIE | Active high level. Indicates that an active edge (falling for RXPOL = 0, rising for RXPOL = 1) was detected.                  |

|---------|------------|---------|-------------------------------------------------------------------------------------------------------------------------------|

| BERRIF  | SCIASR1[1] | BERRIE  | Active high level. Indicates that a mismatch between transmitted and received data in a single wire application has happened. |

| BKDIF   | SCIASR1[0] | BRKDIE  | Active high level. Indicates that a break character has been received.                                                        |

### Table 16-20. SCI Interrupt Sources

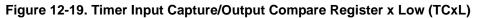

### Figure 18-21. Timing Diagram Charge Pump Connect

$t_{delon} / t_{deloff}$ : GDU propagation delay

$t_{\mbox{HGON}}$  /  $t_{\mbox{HGOFF}}$  : HS driver turn on/off time

t<sub>BLANK</sub>: Blanking Time (see GDUCTR register)

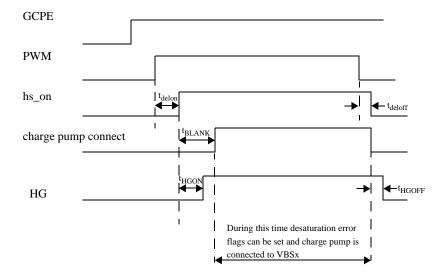

# 22.4.2 PWM Channel Timers

The main part of the PWM module are the actual timers. Each of the timer channels has a counter, a period register and a duty register (each are 8-bit). The waveform output period is controlled by a match between the period register and the value in the counter. The duty is controlled by a match between the duty register and the counter value and causes the state of the output to change during the period. The starting polarity of the output is also selectable on a per channel basis. Shown below in Figure 22-16 is the block diagram for the PWM timer.

PWMEx

Figure 22-16. PWM Timer Channel Block Diagram

# 22.4.2.1 PWM Enable

Each PWM channel has an enable bit (PWMEx) to start its waveform output. When any of the PWMEx bits are set (PWMEx = 1), the associated PWM output signal is enabled immediately. However, the actual PWM waveform is not available on the associated PWM output until its clock source begins its next cycle due to the synchronization of PWMEx and the clock source. An exception to this is when channels are concatenated. Refer to Section 22.4.2.7, "PWM 16-Bit Functions" for more detail.

### NOTE

The first PWM cycle after enabling the channel can be irregular.

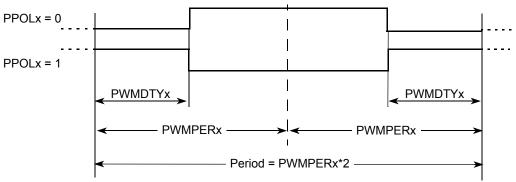

## 22.4.2.6 Center Aligned Outputs

For center aligned output mode selection, set the CAEx bit (CAEx = 1) in the PWMCAE register and the corresponding PWM output will be center aligned.

The 8-bit counter operates as an up/down counter in this mode and is set to up whenever the counter is equal to \$00. The counter compares to two registers, a duty register and a period register as shown in the block diagram in Figure 22-16. When the PWM counter matches the duty register, the output flip-flop changes state, causing the PWM waveform to also change state. A match between the PWM counter and the period register changes the counter direction from an up-count to a down-count. When the PWM counter decrements and matches the duty register again, the output flip-flop changes state causing the PWM output to also change state. When the PWM counter decrements and reaches zero, the counter direction changes from a down-count back to an up-count and a load from the double buffer period and duty registers to the associated registers is performed, as described in Section 22.4.2.3, "PWM Period and Duty". The counter counts from 0 up to the value in the period register and then back down to 0. Thus the effective period is PWMPERx\*2.

### NOTE

Changing the PWM output mode from left aligned to center aligned output (or vice versa) while channels are operating can cause irregularities in the PWM output. It is recommended to program the output mode before enabling the PWM channel.

Figure 22-19. PWM Center Aligned Output Waveform

To calculate the output frequency in center aligned output mode for a particular channel, take the selected clock source frequency for the channel (A, B, SA, or SB) and divide it by twice the value in the period register for that channel.

- PWMx Frequency = Clock (A, B, SA, or SB) / (2\*PWMPERx)

- PWMx Duty Cycle (high time as a% of period):

— Polarity = 0 (PPOLx = 0)

Duty Cycle = [(PWMPERx-PWMDTYx)/PWMPERx] \* 100%

— Polarity = 1 (PPOLx = 1)

Duty Cycle = [PWMDTYx / PWMPERx] \* 100%

As an example of a center aligned output, consider the following case:

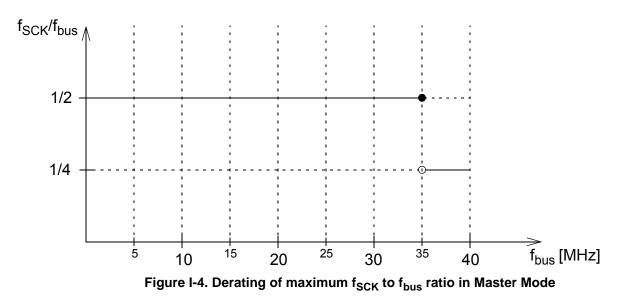

In Master Mode the allowed maximum  $f_{SCK}$  to  $f_{bus}$  ratio (= minimum Baud Rate Divisor, pls. see SPI Block Guide) derates with increasing  $f_{bus}$ , please see **Figure I-4.**

## I.1.1 Slave Mode

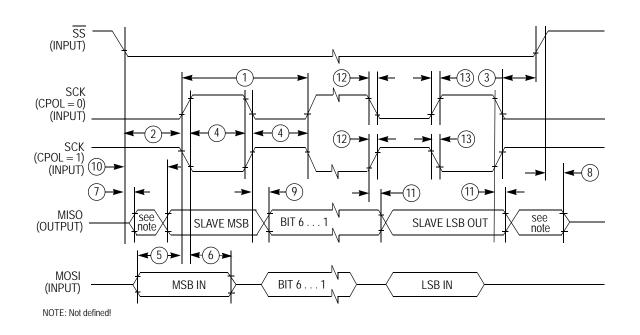

In **Figure I-1.** the timing diagram for slave mode with transmission format CPHA=0 is depicted.

In Figure I-6. the timing diagram for slave mode with transmission format CPHA=1 is depicted.

# M.4 0x0100-0x017F S12ZDBG

| Address           | Name         |        | Bit 7               | 6           | 5                  | 4                    | 3       | 2                | 1        | Bit 0  |

|-------------------|--------------|--------|---------------------|-------------|--------------------|----------------------|---------|------------------|----------|--------|

| 0x0103            | DBGTCRL      | R<br>W | 0                   | 0           | 0                  | PREND <sup>(1)</sup> | DSTAMP  | PDOE             | PROFILE  | STAMP  |

|                   | DBGTBH       | R      | Bit 15              | Bit 14      | Bit 13             | Bit 12               | Bit 11  | Bit 10           | Bit 9    | Bit 8  |

| 0x0104            | 2            | w      |                     | -           |                    | -                    | -       |                  |          |        |

| 0x0105            | DBGTBL       | R      | Bit 7               | Bit 6       | Bit 5              | Bit 4                | Bit 3   | Bit 2            | Bit 1    | Bit 0  |

|                   |              | W      | 0                   |             |                    |                      | ONT     |                  |          |        |

| 0x0106            | DBGCNT<br>2  | R<br>W | 0                   |             |                    |                      | CNT     |                  |          |        |

| 0x0107            | DBGSCR1      | R<br>W | C3SC1               | C3SC0       | C2SC1 <sup>2</sup> | C2SC0 <sup>2</sup>   | C1SC1   | C1SC0            | C0SC1    | C0SC0  |

| 0x0108            | DBGSCR2      | R<br>W | C3SC1               | C3SC0       | C2SC1 <sup>2</sup> | C2SC0 <sup>2</sup>   | C1SC1   | C1SC0            | C0SC1    | C0SC0  |

| 0x0109            | DBGSCR3      | R<br>W | C3SC1               | C3SC0       | C2SC1 <sup>2</sup> | C2SC0 <sup>2</sup>   | C1SC1   | C1SC0            | C0SC1    | C0SC0  |

| 0x010A            | DBGEFR       | R      | PTBOVF <sup>2</sup> | TRIGF       | 0                  | EEVF                 | ME3     | ME2 <sup>2</sup> | ME1      | ME0    |

|                   |              | W      | TBF <sup>2</sup>    |             |                    | PTACT <sup>2</sup>   | 0       | 0050             | 0054     | 0050   |

| 0x010B            | 0x010B DBGSR | R<br>W | IBF-                | 0           | 0                  | PIACI                | 0       | SSF2             | SSF1     | SSF0   |

| 0x010C-           | Reserved     | R      | 0                   | 0           | 0                  | 0                    | 0       | 0                | 0        | 0      |

| 0x010F            | Reserved     | W      |                     |             |                    |                      |         |                  |          |        |

| 0x0110            | DBGACTL      | R<br>W | 0                   | NDB         | INST               | 0                    | RW      | RWE              | reserved | COMPE  |

| 0x0111-<br>0x0114 | Reserved     | R      | 0                   | 0           | 0                  | 0                    | 0       | 0                | 0        | 0      |

| 0.00114           |              | W<br>R |                     |             |                    |                      |         |                  |          |        |

| 0x0115            | DBGAAH       | W      |                     |             |                    | DBGAA                | [23:16] |                  |          |        |

| 0x0116            | DBGAAM       | R<br>W |                     | DBGAA[15:8] |                    |                      |         |                  |          |        |

| 0x0117            | DBGAAL       | R<br>W |                     | DBGAA[7:0]  |                    |                      |         |                  |          |        |

| 0x0118            | DBGAD0       | R<br>W | Bit 31              | 30          | 29                 | 28                   | 27      | 26               | 25       | Bit 24 |

| 0x0119            | DBGAD1       | R<br>W | Bit 23              | 22          | 21                 | 20                   | 19      | 18               | 17       | Bit 16 |

| 0x011A            | DBGAD2       | R<br>W | Bit 15              | 14          | 13                 | 12                   | 11      | 10               | 9        | Bit 8  |

| 0x011B            | DBGAD3       | R<br>W | Bit 7               | 6           | 5                  | 4                    | 3       | 2                | 1        | Bit 0  |

# M.20 0x0780-0x0787 SPI0

| Address | Register<br>Name |        | Bit 7      | 6          | 5          | 4          | 3          | 2          | 1        | Bit 0    |

|---------|------------------|--------|------------|------------|------------|------------|------------|------------|----------|----------|

| 0x0780  | SPI0CR1          | R<br>W | SPIE       | SPE        | SPTIE      | MSTR       | CPOL       | CPHA       | SSOE     | LSBFE    |

| 0x0781  | SPI0CR2          | R<br>W | 0          | XFRW       | 0          | MODFEN     | BIDIROE    | 0          | SPISWAI  | SPC0     |

| 0x0782  | SPI0BR           | R<br>W | 0          | SPPR2      | SPPR1      | SPPR0      | 0          | SPR2       | SPR1     | SPR0     |

| 0x0783  | SPI0SR           | R<br>W | SPIF       | 0          | SPTEF      | MODF       | 0          | 0          | 0        | 0        |

| 0x0784  | SPI0DRH          | R<br>W | R15<br>T15 | R14<br>T14 | R13<br>T13 | R12<br>T12 | R11<br>T11 | R10<br>T10 | R9<br>T9 | R8<br>T8 |

| 0x0785  | SPI0DRL          | R<br>W | R7<br>T7   | R6<br>T6   | R5<br>T5   | R4<br>T4   | R3<br>T3   | R2<br>T2   | R1<br>T1 | R0<br>T0 |

| 0x0786  | Reserved         | R<br>W |            |            |            |            |            |            |          |          |

| 0x0787  | Reserved         | R<br>W |            |            |            |            |            |            |          |          |

# M.21 0x0800-0x083F CAN0

| Address         | Name          | _      | Bit 7 | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0    |

|-----------------|---------------|--------|-------|--------|---------|---------|---------|---------|---------|----------|

| 0x0800          | CAN0CTL0      | R<br>W | RXFRM | RXACT  | CSWAI   | SYNCH   | TIME    | WUPE    | SLPRQ   | INITRQ   |

| 0x0801          | CAN0CTL1      | R      | CANE  | CLKSRC | LOOPB   | LISTEN  | BORM    | WUPM    | SLPAK   | INITAK   |

|                 |               | W      |       |        |         |         |         |         |         |          |

| 0x0802          | CAN0BTR0      | R<br>W | SJW1  | SJW0   | BRP5    | BRP4    | BRP3    | BRP2    | BRP1    | BRP0     |

| 0x0803          | CAN0BTR1      | R<br>W | SAMP  | TSEG22 | TSEG21  | TSEG20  | TSEG13  | TSEG12  | TSEG11  | TSEG10   |

| 0x0804          | CANORFLG      | R      | WUPIF | CSCIF  | RSTAT1  | RSTAT0  | TSTAT1  | TSTAT0  | OVRIF   | RXF      |

| 070004          |               | W      | WOTI  | 00011  |         |         |         |         | O VIXII |          |

| 0x0805          | CAN0RIER      | R<br>W | WUPIE | CSCIE  | RSTATE1 | RSTATE0 | TSTATE1 | TSTATE0 | OVRIE   | RXFIE    |

| 0x0806          | CAN0TFLG      | R      | 0     | 0      | 0       | 0       | 0       | TXE2    | TXE1    | TXE0     |

| 000000          | OUU CANUTELG  |        |       |        |         |         |         | IVES    | IVEI    | IVEO     |

| 0x0807          | CAN0TIER      | R      | 0     | 0      | 0       | 0       | 0       | TXEIE2  | TXEIE1  | TXEIE0   |

| 0,0001          | UNUUT CANUTER |        |       |        |         |         |         |         |         | TALILO   |

| 0x0808 CAN0TARQ |               | R      | 0     | 0      | 0       | 0       | 0       | ABTRQ2  | ABTRQ1  | ABTRQ0   |

| 0,0000          |               | W      |       |        |         |         | 7.DTRQ2 | AD HOUL |         | //DIIXQU |

| 0x0809 CANOTAAK |               | R      | 0     | 0      | 0       | 0       | 0       | ABTAK2  | ABTAK1  | ABTAK0   |

|                 |               | W      |       |        |         |         |         |         |         |          |