Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 256KB (256K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 1K x 8                                                                  |

| RAM Size                   | 32K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 16x12b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 80-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 80-TQFP-EP (12x12)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvmc25f1wkk |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2 trigger input sources and software trigger source

- 2 trigger outputs

- One 16-bit delay register pre-trigger output

- Operation in One-Shot or Continuous modes

## **1.4.9** LIN physical layer transceiver (ZVML devices only)

- Compliant with LIN Physical Layer 2.2 specification.

- Compliant with the SAE J2602-2 LIN standard.

- Standby mode with glitch-filtered wake-up.

- Slew rate selection optimized for the baud rates: 10.4kBit/s, 20kBit/s and Fast Mode (up to 250kBit/s).

- Switchable  $34k\Omega/330k\Omega$  pull-ups (in shutdown mode,  $330k\Omega$  only)

- Current limitation for LIN Bus pin falling edge.

- Over-current protection.

- LIN TxD-dominant timeout feature monitoring the LPTxD signal.

- Automatic transmitter shutdown in case of an over-current or TxD-dominant timeout.

- Fulfills the OEM "Hardware Requirements for LIN (CAN and FlexRay) Interfaces in Automotive Applications" v1.3.

## **1.4.10** Serial Communication Interface Module (SCI)

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 16-bit baud rate selection

- Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wakeup

- Break detect and transmit collision detect supporting LIN

## 1.4.11 Multi-Scalable Controller Area Network (MSCAN)

- Implementation of the CAN protocol Version 2.0A/B

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter supports two full-size (32-bit) extended identifier filters, or four 16-bit filters, or either 8-bit filters

- Programmable wake-up functionality with integrated low-pass filter

## 1.9.1.2 Special Single-Chip Mode

This mode is used for debugging operation, boot-strapping, or security related operations. The background debug mode (BDM) is active on leaving reset in this mode

## 1.9.2 Debugging Modes

The background debug mode (BDM) can be activated by the BDC module or directly when resetting into Special Single-Chip mode. Detailed information can be found in the BDC module section.

Writing to internal memory locations using the debugger, whilst code is running or at a breakpoint, can change the flow of application code.

The MC9S12ZVM-Family supports BDC communication throughout the device Stop mode. During Stop mode, writes to control registers can alter the operation and lead to unexpected results. It is thus recommended not to reconfigure the peripherals during STOP using the debugger.

On the S12ZVML and S12ZVMC versions, the DBG module supports breakpoint, tracing and profiling features. At board level the profiling pins can use the same 6-pin connector typically used for the BDC BKGD pin. The connector pin mapping shown in Figure 1-7 is supported by device evaluation boards and leading development tool vendors.

Figure 1-7. Standard Debug Connector Pin Mapping

## 1.9.3 Low Power Modes

The device has two dynamic-power modes (run and wait) and two static low-power modes stop and pseudo stop). For a detailed description refer to the CPMU section.

- Dynamic power mode: Run

- Run mode is the main full performance operating mode with the entire device clocked. The user can configure the device operating speed through selection of the clock source and the phase locked loop (PLL) frequency. To save power, unused peripherals must not be enabled.

- Dynamic power mode: Wait

- This mode is entered when the CPU executes the WAI instruction. In this mode the CPU does not execute instructions. The internal CPU clock is switched off. All peripherals can be active in system wait mode. For further power consumption the peripherals can individually turn off their local clocks. Asserting RESET, XIRQ, IRQ, or any other interrupt that is not masked, either locally or globally by a CCR bit, ends system wait mode.

- Static power modes:

Static power (Stop) modes are entered following the CPU STOP instruction unless an NVM command is active. When no NVM commands are active, the Stop request is acknowledged and

#### Chapter 1 Device Overview MC9S12ZVM-Family

trigger through the control loop or can prevent propagation so the static timing of the control cycle and inter-block coherency are not affected by the trigger.

At the end of the conversion sequence the first ADC command from the new sequence is loaded and the ADC*x* waits for the next **trigger\_x**. The PTU continues to generate the **trigger\_x** events for each trigger time from the list until a new **reload** or **async\_reload** occurs.

Before the upcoming **reload** event the CPU:

- reads the ADC results from the buffered Conversion Result List

- clears the conversion complete flag

- services the **reload** by setting new duty cycle values

- sets the PTULDOK bit (corresponding to **glb\_ldok**) to signal the duty cycle coherence

The CPU actions are typically performed in an ISR triggered by the conversion complete flag.

### 1.13.3.4 Static Timing Fault Handling

The following Faults and/or errors can occur:

• Desaturation error, Overvoltage, Undervoltage, External fault

The application run-time error is handled by the GDU without CPU interaction. Firstly the FETs are disabled and the PMF signals switched to an inactive state. To re-enable the operation first the GDU fault and then PWM fault must be cleared, to automatically re-enable the FET driving at the next PWM boundary.

• PTU reload overrun error

This is an application run-time error caused by the CPU not setting PTULDOK on time. Servicing this type of error is application dependent and may range from a further reload attempt to a total shut down.

• PTU trigger generator reload error, PTU trigger generator error

Since all timing is static, this error should only occur during application debugging. This type of error occurring in a static timing configuration indicates possible data corruption. This can be serviced by a control loop shutdown.

• PTU memory access error, Memory access double bit ECC error

This type of error occurring in an application indicates data corruption. This can be serviced by a control loop shutdown.

• ADC sequence overrun, ADC command overrun, ADC command error

Since all timing is static, this error should only occur during application debugging. This type of error occurring in an application indicates possible data corruption. This can be serviced by a control loop shutdown.

## 1.13.3.5 Dynamic Timing Operation

The timing frame is dynamic if the following are modified on a cycle by cycle basis:

• PMF - duty cycle value registers (PMF\_VAL*x*), modulo registers

Chapter 6 S12Z Debug (S12ZDBG) Module

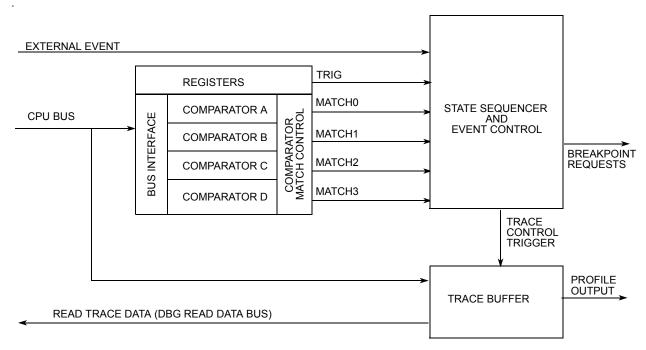

## 6.1.5 Block Diagram

Figure 6-1. Debug Module Block Diagram

## 6.2 External Signal Description

## 6.2.1 External Event Input

The DBG module features an external event input signal, DBGEEV. The mapping of this signal to a device pin is specified in the device specific documentation. This function can be enabled and configured by the EEVE field in the DBGC1 control register. This signal is input only and allows an external event to force a state sequencer transition, or trace buffer entry, or to gate trace buffer entries. With the external event function enabled, a falling edge at the external event pin constitutes an event. Rising edges have no effect. If configured for gating trace buffer entries, then a low level at the pin allows entries, but a high level suppresses entries. The maximum frequency of events is half the internal core bus frequency. The function is explained in the EEVE field description.

### NOTE

Due to input pin synchronization circuitry, the DBG module sees external events 2 bus cycles after they occur at the pin. Thus an external event occurring less than 2 bus cycles before arming the DBG module is perceived to occur whilst the DBG is armed.

When the device is in stop mode the synchronizer clocks are disabled and the external events are ignored.

Chapter 6 S12Z Debug (S12ZDBG) Module

| Address           | Name     |        | Bit 7        | 6           | 5    | 4     | 3        | 2   | 1        | Bit 0  |

|-------------------|----------|--------|--------------|-------------|------|-------|----------|-----|----------|--------|

| 0x0128-<br>0x012F | Reserved | R<br>W | 0            | 0           | 0    | 0     | 0        | 0   | 0        | 0      |

| 0x0130            | DBGCCTL  | R<br>W | 0            | NDB         | INST | 0     | RW       | RWE | reserved | COMPE  |

| 0x0131-<br>0x0134 | Reserved | R<br>W | 0            | 0           | 0    | 0     | 0        | 0   | 0        | 0      |

| 0x0135            | DBGCAH   | R<br>W |              |             |      | DBGCA | A[23:16] |     |          |        |

| 0x0136            | DBGCAM   | R<br>W |              |             |      | DBGC  | A[15:8]  |     |          |        |

| 0x0137            | DBGCAL   | R<br>W |              |             |      | DBGC  | CA[7:0]  |     |          |        |

| 0x0138            | DBGCD0   | R<br>W | Bit 31       | 30          | 29   | 28    | 27       | 26  | 25       | Bit 24 |

| 0x0139            | DBGCD1   | R<br>W | Bit 23       | 22          | 21   | 20    | 19       | 18  | 17       | Bit 16 |

| 0x013A            | DBGCD2   | R<br>W | Bit 15       | 14          | 13   | 12    | 11       | 10  | 9        | Bit 8  |

| 0x013B            | DBGCD3   | R<br>W | Bit 7        | 6           | 5    | 4     | 3        | 2   | 1        | Bit 0  |

| 0x013C            | DBGCDM0  | R<br>W | Bit 31       | 30          | 29   | 28    | 27       | 26  | 25       | Bit 24 |

| 0x013D            | DBGCDM1  | R<br>W | Bit 23       | 22          | 21   | 20    | 19       | 18  | 17       | Bit 16 |

| 0x013E            | DBGCDM2  | R<br>W | Bit 15       | 14          | 13   | 12    | 11       | 10  | 9        | Bit 8  |

| 0x013F            | DBGCDM3  | R<br>W | Bit 7        | 6           | 5    | 4     | 3        | 2   | 1        | Bit 0  |

| 0x0140            | DBGDCTL  | R<br>W | 0            | 0           | INST | 0     | RW       | RWE | reserved | COMPE  |

| 0x0141-<br>0x0144 | Reserved | R<br>W | 0            | 0           | 0    | 0     | 0        | 0   | 0        | 0      |

| 0x0145            | DBGDAH   | R<br>W | DBGDA[23:16] |             |      |       |          |     |          |        |

| 0x0146            | DBGDAM   | R<br>W |              | DBGDA[15:8] |      |       |          |     |          |        |

Figure 6-2. Quick Reference to DBG Registers

#### Chapter 6 S12Z Debug (S12ZDBG) Module

| SSF[2:0]    | Current State |

|-------------|---------------|

| 100         | Final State   |

| 101,110,111 | Reserved      |

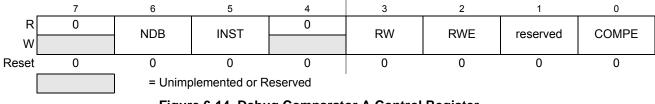

### 6.3.2.12 Debug Comparator A Control Register (DBGACTL)

Address: 0x0110

Figure 6-14. Debug Comparator A Control Register

Read: Anytime.

Write: If DBG not armed and PTACT is clear.

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>NDB   | <ul> <li>Not Data Bus — The NDB bit controls whether the match occurs when the data bus matches the comparator register value or when the data bus differs from the register value. This bit is ignored if the INST bit in the same register is set.</li> <li>0 Match on data bus equivalence to comparator register contents</li> <li>1 Match on data bus difference to comparator register contents</li> </ul> |

| 5<br>INST  | Instruction Select — This bit configures the comparator to compare PC or data access addresses.         0 Comparator compares addresses of data accesses         1 Comparator compares PC address                                                                                                                                                                                                                |

| 3<br>RW    | <ul> <li>Read/Write Comparator Value Bit — The RW bit controls whether read or write is used in compare for the associated comparator. The RW bit is ignored if RWE is clear or INST is set.</li> <li>0 Write cycle is matched</li> <li>1 Read cycle is matched</li> </ul>                                                                                                                                       |

| 2<br>RWE   | <ul> <li>Read/Write Enable Bit — The RWE bit controls whether read or write comparison is enabled for the associated comparator. This bit is ignored when INST is set.</li> <li>0 Read/Write is not used in comparison</li> <li>1 Read/Write is used in comparison</li> </ul>                                                                                                                                    |

| 0<br>COMPE | <ul> <li>Enable Bit — Determines if comparator is enabled</li> <li>0 The comparator is not enabled</li> <li>1 The comparator is enabled</li> </ul>                                                                                                                                                                                                                                                               |

Table 6-27 shows the effect for RWE and RW on the comparison conditions. These bits are ignored if INST is set, because matches based on opcodes reaching the execution stage are data independent.

### 6.4.3.1.2 Data Access Comparator Match

Data access matches are generated when an access occurs at the address contained in the comparator address register. The match can be qualified by the access data and by the access type (read/write). The breakpoint occurs a maximum of 2 instructions after the access in the CPU flow. Note, if a COF occurs between access and breakpoint, the opcode address of the breakpoint can be elsewhere in the memory map.

Opcode fetches are not classed as data accesses. Thus data access matches are not possible on opcode fetches.

## 6.4.3.2 External Event

The DBGEEV input signal can force a state sequencer transition, independent of internal comparator matches. The DBGEEV is an input signal mapped directly to a device pin and configured by the EEVE field in DBGC1. The external events can change the state sequencer state, or force a trace buffer entry, or gate trace buffer entries.

If configured to change the state sequencer state, then the external match is mapped to DBGSCRx bits C3SC[1:0]. In this configuration, internal comparator channel3 is de-coupled from the state sequencer but can still be used for timestamps. The DBGEFR bit EEVF is set when an external event occurs.

## 6.4.3.3 Setting The TRIG Bit

Independent of comparator matches it is possible to initiate a tracing session and/or breakpoint by writing the TRIG bit in DBGC1 to a logic "1". This forces the state sequencer into the Final State. If configured for End aligned tracing or for no tracing, the transition to Final State is followed immediately by a transition to State0. If configured for Begin- or Mid Aligned tracing, the state sequencer remains in Final State until tracing is complete, then it transitions to State0.

Breakpoints, if enabled, are issued on the transition to State0.

## 6.4.3.4 Profiling Trace Buffer Overflow Event

During code profiling a trace buffer overflow forces the state sequencer into the disarmed State0 and, if breakpoints are enabled, issues a breakpoint request to the CPU.

### 6.4.3.5 Event Priorities

If simultaneous events occur, the priority is resolved according to Table 6-46. Lower priority events are suppressed. It is thus possible to miss a lower priority event if it occurs simultaneously with an event of a higher priority. The event priorities dictate that in the case of simultaneous matches, the match on the higher comparator channel number (3,2,1,0) has priority.

If a write access to DBGC1 with the ARM bit position set occurs simultaneously to a hardware disarm from an internal event, then the ARM bit is cleared due to the hardware disarm.

| Priority | Source      | Action                                                                |

|----------|-------------|-----------------------------------------------------------------------|

| Highest  | TB Overflow | Immediate force to state 0, generate breakpoint and terminate tracing |

#### Table 6-46. Event Priorities

### 8.1.1 Differences between S12CPMU\_UHV\_V10 and S12CPMU\_UHV\_V6

- The following device pins exist only in V10: VDDS1, VDDS2, BCTLS1, BCTLS2, SNPS1, SNPS2,

- The feature of switching VDDS1/2 to VRH1/2 (which connects to ADC) exists only in V10

- The following register and bits exist only in V10: CPMUVREGCTL register: Bits VRH2EN, VRH1EN, EXTS1ON, EXTS2ON CPMULVCTL register: Bit VDDSIE CPMUVDDS register

- The VDDS Integrity Interrupt only exists in V10

# 8.2 Signal Description

This section lists and describes the signals that connect off chip as well as internal supply nodes and special signals.

## 8.2.1 **RESET**

Pin  $\overline{\text{RESET}}$  is an active-low bidirectional pin. As an input it initializes the MCU asynchronously to a known start-up state. As an open-drain output it indicates that an MCU-internal reset has been triggered.

## 8.2.2 EXTAL and XTAL

These pins provide the interface for a crystal to control the internal clock generator circuitry. EXTAL is the input to the crystal oscillator amplifier. XTAL is the output of the crystal oscillator amplifier. If XOSCLCP is enabled, the MCU internal OSCCLK\_LCP is derived from the EXTAL input frequency. If OSCE=0, the EXTAL pin is pulled down by an internal resistor of approximately 200 k $\Omega$  and the XTAL pin is pulled down by an internal resistor of approximately 200 k $\Omega$ .

### NOTE

NXP recommends an evaluation of the application board and chosen resonator or crystal by the resonator or crystal supplier. The loop controlled circuit (XOSCLCP) is not suited for overtone resonators and crystals.

## 8.2.3 VSUP — Regulator Power Input Pin

Pin VSUP is the power input of VREGAUTO. All currents sourced into the regulator loads flow through this pin.

A suitable reverse battery protection network can be used to connect VSUP to the car battery supply network.

## 8.2.4 VDDA, VSSA — Regulator Reference Supply Pins

Pins VDDA and VSSA are used to supply the analog parts of the regulator. Internal precision reference circuits are supplied from these signals.

An off-chip decoupling capacitor (220 nF(X7R ceramic)) between VDDA and VSSA is required and can improve the quality of this supply.

VDDA has to be connected externally to VDDX.

## 8.2.5 VDDX, VSSX— Pad Supply Pins

VDDX is the supply domain for the digital Pads.

An off-chip decoupling capacitor (10 $\mu$ F plus 220 nF(X7R ceramic)) between VDDX and VSSX is required.

### Table 12-16. PTPSR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>PTPS[7:0] | <b>Precision Timer Prescaler Select Bits</b> — These eight bits specify the division rate of the main Timer prescaler. These are effective only when the PRNT bit of TSCR1 is set to 1. Table 12-17 shows some selection examples in this case. The newly selected prescale factor will not take effect until the next synchronized edge where all prescale counter stages equal zero. |

The Prescaler can be calculated as follows depending on logical value of the PTPS[7:0] and PRNT bit:

PRNT = 1: Prescaler = PTPS[7:0] + 1

| PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 | Prescale<br>Factor |

|-------|-------|-------|-------|-------|-------|-------|-------|--------------------|

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 0     | 1     | 2                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 0     | 3                  |

| 0     | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 4                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 0     | 0     | 0     | 1     | 0     | 0     | 1     | 1     | 20                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 0     | 21                 |

| 0     | 0     | 0     | 1     | 0     | 1     | 0     | 1     | 22                 |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| -     | -     | -     | -     | -     | -     | -     | -     | -                  |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 0     | 253                |

| 1     | 1     | 1     | 1     | 1     | 1     | 0     | 1     | 254                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 0     | 255                |

| 1     | 1     | 1     | 1     | 1     | 1     | 1     | 1     | 256                |

Table 12-17. Precision Timer Prescaler Selection Examples when PRNT = 1

# 12.4 Functional Description

This section provides a complete functional description of the timer TIM16B2CV3 block. Please refer to the detailed timer block diagram in Figure 12-22 as necessary.

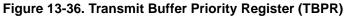

#### Chapter 13 Scalable Controller Area Network (S12MSCANV3)

• The transmission buffer with the lowest local priority field wins the prioritization.

In cases of more than one buffer having the same lowest priority, the message buffer with the lower index number wins.

Module Base + 0x00XD

Access: User read/write<sup>(1)</sup>

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | PRIO7 | PRIO6 | PRIO5 | PRIO4 | PRIO3 | PRIO2 | PRIO1 | PRIO0 |

| Reset: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

1. Read: Anytime when TXEx flag is set (see Section 13.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 13.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

Write: Anytime when TXEx flag is set (see Section 13.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 13.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)")

## 13.3.3.5 Time Stamp Register (TSRH–TSRL)

If the TIME bit is enabled, the MSCAN will write a time stamp to the respective registers in the active transmit or receive buffer right after the EOF of a valid message on the CAN bus (see Section 13.3.2.1, "MSCAN Control Register 0 (CANCTL0)"). In case of a transmission, the CPU can only read the time stamp after the respective transmit buffer has been flagged empty.

The timer value, which is used for stamping, is taken from a free running internal CAN bit clock. A timer overrun is not indicated by the MSCAN. The timer is reset (all bits set to 0) during initialization mode. The CPU can only read the time stamp registers.

Module Base + 0x00XE Access: User read/write<sup>(1)</sup> 7 6 5 3 2 0 4 1 TSR15 **TSR13** TSR10 TSR9 TSR8 R TSR14 TSR12 TSR11 W Reset: х х х х х х х х

Figure 13-37. Time Stamp Register — High Byte (TSRH)

Read: For transmit buffers: Anytime when TXEx flag is set (see Section 13.3.2.7, "MSCAN Transmitter Flag Register (CANTFLG)") and the corresponding transmit buffer is selected in CANTBSEL (see Section 13.3.2.11, "MSCAN Transmit Buffer Selection Register (CANTBSEL)"). For receive buffers: Anytime when RXF is set. Write: Unimplemented

| GCPCD[3:0] | f <sub>CP</sub>              |

|------------|------------------------------|

| 0000       | f <sub>BUS</sub> / 16        |

| 0001       | f <sub>BUS</sub> / 24        |

| 0010       | f <sub>BUS</sub> / 32        |

| 0011       | f <sub>BUS</sub> / 48        |

| 0100       | f <sub>BUS</sub> / 64        |

| 0101       | f <sub>BUS</sub> / 96        |

| 0110       | <b>f<sub>BUS</sub> / 100</b> |

| 0111       | f <sub>BUS</sub> / 128       |

| 1000       | f <sub>BUS</sub> / 192       |

| 1001       | f <sub>BUS</sub> / 200       |

| 1010       | f <sub>BUS</sub> / 256       |

| 1011       | f <sub>BUS</sub> / 384       |

| 1100       | f <sub>BUS</sub> / 400       |

| 1101       | f <sub>BUS</sub> / 512       |

| 1110       | f <sub>BUS</sub> / 768       |

| 1111       | f <sub>BUS</sub> / 800       |

Table 18-18. Charge Pump Clock Divider Factors k =  $f_{BUS} / f_{CP}$

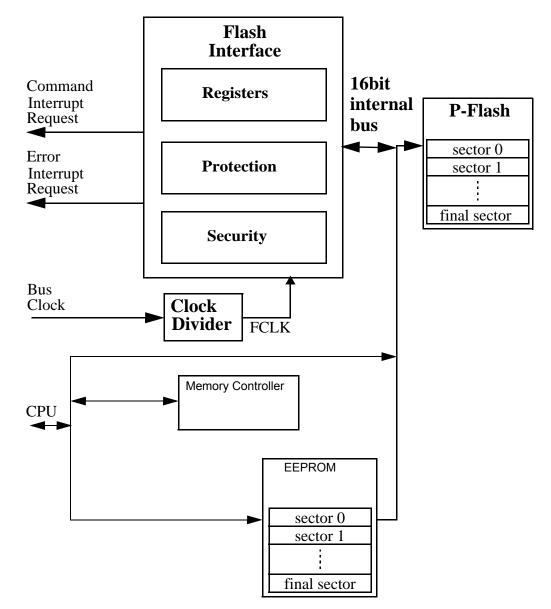

Figure 20-1. FTMRZ Block Diagram (Single P-Flash Block plus EEPROM block)

| CCOBIX[2:0] | Register | Byte | FCCOB Parameter Fields (NVM Command Mode) |

|-------------|----------|------|-------------------------------------------|

| 011         | FCCOB3   | HI   | Data 1 [15:8]                             |

| 011         | 100005   | LO   | Data 1 [7:0]                              |

| 100         | FCCOB4   | HI   | Data 2 [15:8]                             |

| 100         |          | LO   | Data 2 [7:0]                              |

| 101         | FCCOB5   | HI   | Data 3 [15:8]                             |

| 101         | FCCOB5   | LO   | Data 3 [7:0]                              |

Table 20-27. FCCOB - NVM Command Mode (Typical Usage)

## 20.4 Functional Description

### 20.4.1 Modes of Operation

The module provides the modes of operation normal and special. The operating mode is determined by module-level inputs and affects the FCLKDIV, FCNFG, and DFPROT registers (see Table 20-29).

## 20.4.2 IFR Version ID Word

The version ID word is stored in the IFR at address 0x1F\_C0B6. The contents of the word are defined in Table 20-28.

| [15:4]   | [3:0]  |  |  |  |

|----------|--------|--|--|--|

| Reserved | VERNUM |  |  |  |

Table 20-28. IFR Version ID Fields

• VERNUM: Version number. The first version is number 0b\_0001 with both 0b\_0000 and 0b\_1111 meaning 'none'.

## 20.4.3 Flash Block Read Access

If data read from the Flash block results in a double-bit fault ECC error (meaning that data is detected to be in error and cannot be corrected), the read data will be tagged as invalid during that access (please look

# Chapter 21 CAN Physical Layer (S12CANPHYV3)

| Revision<br>Number | Revision Date | Sections<br>Affected | Description of Changes                                                                                                                                                                                                                                        |

|--------------------|---------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V02.00             | 05 Nov 2012   |                      | Added CPTXD-dominant timeout feature                                                                                                                                                                                                                          |

| V03.00             | 15 Apr 2013   |                      | <ul> <li>Made transmit driver (CANH &amp; CANL) independent of CPCHVL condition</li> <li>Changed CPCLVL condition to disable CANL only</li> <li>Added mode to cover separation of CANH and CANL drivers</li> <li>Added configurable wake-up filter</li> </ul> |

#### Table 21-1. Revision History Table

### NOTE

The information given in this section are preliminary and should be used as a guide only. Values in this section cannot be guaranteed and are subject to change without notice.

## 21.1 Introduction

The CAN Physical Layer provides a physical layer for high speed CAN area network communication in automotive applications. It serves as an integrated interface to the CAN bus lines for the internally connected MSCAN controller through the pins CANH, CANL and SPLIT.

The CAN Physical Layer is designed to meet the CAN Physical Layer ISO 11898-2 and ISO 11898-5 standards.

## 21.1.1 Features

The CAN Physical Layer module includes these distinctive features:

- High speed CAN interface for baud rates of up to 1 Mbit/s

- ISO 11898-2 and ISO 11898-5 compliant for 12 V battery systems

- SPLIT pin driver for bus recessive level stabilization

- Low power mode with remote CAN wake-up handled by MSCAN module

- Configurable wake-up pulse filtering

- Over-current shutdown for CANH and CANL

- Voltage monitoring on CANH and CANL

- CPTXD-dominant timeout feature monitoring the CPTXD signal

- Fulfills the OEM "Hardware Requirements for (LIN,) CAN (and FlexRay) Interfaces in Automotive Applications" v1.3

| Field            | Description                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

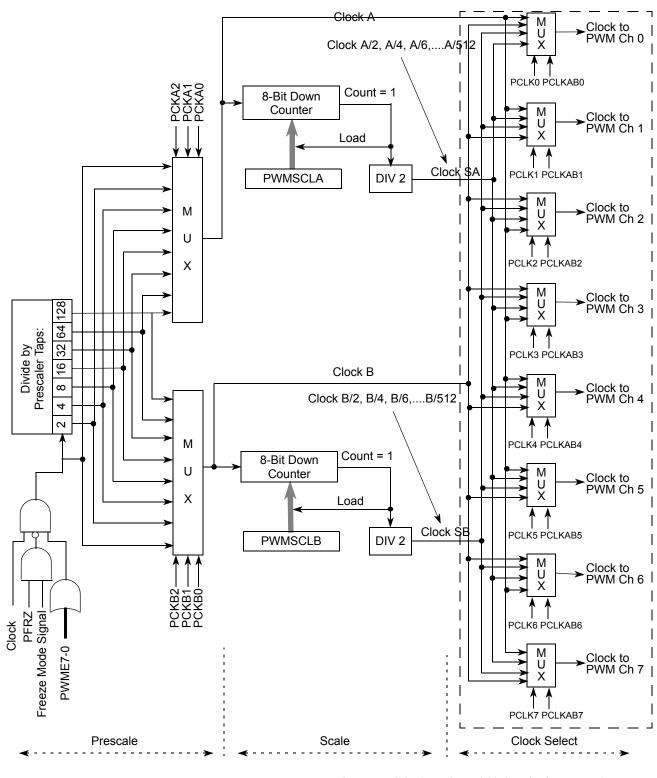

| 6–4<br>PCKB[2:0] | <b>Prescaler Select for Clock B</b> — Clock B is one of two clock sources which can be used for all channels. These three bits determine the rate of clock B, as shown in Table 22-8. |

| 2–0<br>PCKA[2:0] | <b>Prescaler Select for Clock A</b> — Clock A is one of two clock sources which can be used for all channels. These three bits determine the rate of clock A, as shown in Table 22-8. |

#### Table 22-7. PWMPRCLK Field Descriptions

#### Table 22-8. Clock A or Clock B Prescaler Selects

| PCKA/B2 | PCKA/B1 | PCKA/B0 | Value of Clock A/B |

|---------|---------|---------|--------------------|

| 0       | 0       | 0       | bus clock          |

| 0       | 0       | 1       | bus clock / 2      |

| 0       | 1       | 0       | bus clock / 4      |

| 0       | 1       | 1       | bus clock / 8      |

| 1       | 0       | 0       | bus clock / 16     |

| 1       | 0       | 1       | bus clock / 32     |

| 1       | 1       | 0       | bus clock / 64     |

| 1       | 1       | 1       | bus clock / 128    |

### 22.3.2.5 PWM Center Align Enable Register (PWMCAE)

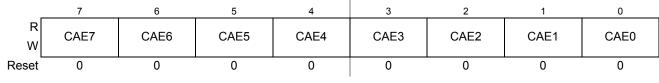

The PWMCAE register contains eight control bits for the selection of center aligned outputs or left aligned outputs for each PWM channel. If the CAEx bit is set to a one, the corresponding PWM output will be center aligned. If the CAEx bit is cleared, the corresponding PWM output will be left aligned. See Section 22.4.2.5, "Left Aligned Outputs" and Section 22.4.2.6, "Center Aligned Outputs" for a more detailed description of the PWM output modes.

Module Base + 0x0004

Figure 22-7. PWM Center Align Enable Register (PWMCAE)

Read: Anytime

Write: Anytime

#### NOTE

Write these bits only when the corresponding channel is disabled.

Chapter 22 Pulse-Width Modulator (S12PWM8B8CV2)

- – – Maximum possible channels, scalable in pairs from PWM0 to PWM7.

Figure 22-15. PWM Clock Select Block Diagram

### NOTE

Changing the PWM output mode from left aligned to center aligned output (or vice versa) while channels are operating can cause irregularities in the PWM output. It is recommended to program the output mode before enabling the PWM channel.

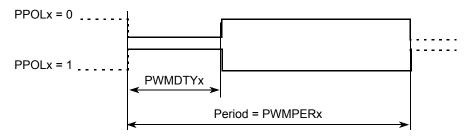

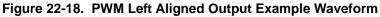

Figure 22-17. PWM Left Aligned Output Waveform

To calculate the output frequency in left aligned output mode for a particular channel, take the selected clock source frequency for the channel (A, B, SA, or SB) and divide it by the value in the period register for that channel.

- PWMx Frequency = Clock (A, B, SA, or SB) / PWMPERx

- PWMx Duty Cycle (high time as a% of period):

- Polarity = 0 (PPOLx = 0)

Duty Cycle = [(PWMPERx-PWMDTYx)/PWMPERx] \* 100%

— Polarity = 1 (PPOLx = 1)

Duty Cycle = [PWMDTYx / PWMPERx] \* 100%

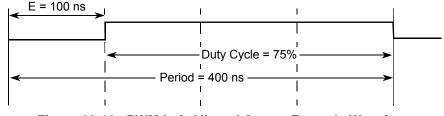

As an example of a left aligned output, consider the following case:

Clock Source = bus clock, where bus clock = 10 MHz (100 ns period)

PPOLx = 0 PWMPERx = 4 PWMDTYx = 1 PWMx Frequency = 10 MHz/4 = 2.5 MHz PWMx Period = 400 ns PWMx Duty Cycle = 3/4 \*100% = 75%

The output waveform generated is shown in Figure 22-18.

# Appendix M Detailed Register Address Map

Registers listed are a superset of all registers in the S12ZVM-Family.

The device overview section specifies module (version) assignment to individual devices.

# M.1 0x0000-0x0003 Part ID

| Address | Name    |   | Bit 7 | Bit 6 | Bit 5 | Bit 4      | Bit 3                                | Bit 2 | Bit 1 | Bit 0   |

|---------|---------|---|-------|-------|-------|------------|--------------------------------------|-------|-------|---------|

| 0x0000  | PARTID0 | R | 0     | 0     | 0     | 0          | 0                                    | 0     | 0     | 0       |

|         |         | W |       |       |       |            |                                      |       |       |         |

| 0x0001  | PARTID1 | R | 0     | 0     | 0     | 1          | Derivative Dependent (see Table 1-6) |       |       | le 1-6) |

|         |         | W |       |       |       |            |                                      |       |       |         |

| 0x0002  | PARTID2 | R | 0     | 0     | 0     | 0          | 0                                    | 0     | 0     | 0       |

|         |         | W |       |       |       |            |                                      |       |       |         |

| 0x0003  | PARTID3 | R |       |       |       | Revision [ | Dependent                            |       |       |         |

| 070000  |         | W |       |       |       |            |                                      |       |       |         |

# M.2 0x0010-0x001F S12ZINT

| Address           | Name        | Bit 7    | 6 | 5       | 4        | 3 | 2            | 1 | Bit 0 |  |

|-------------------|-------------|----------|---|---------|----------|---|--------------|---|-------|--|

| 0x0010            |             | R<br>W   |   |         |          |   |              |   |       |  |

| 0x0011            | IVBR        | R<br>W   |   |         |          |   |              |   |       |  |

| 0x0012-<br>0x0016 | Reserved    | R 0<br>W | 0 | 0       | 0        | 0 | 0            | 0 | 0     |  |

| 0x0017            | INT_CFADDR  | R 0<br>W |   | INT_CFA | DDR[6:3] |   | 0 0 0        |   |       |  |

| 0x0018            | INT_CFDATA0 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

| 0x0019            | INT_CFDATA1 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

| 0x001A            | INT_CFDATA2 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

| 0x001B            | INT_CFDATA3 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

| 0x001C            | INT_CFDATA4 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

| 0x001D            | INT_CFDATA5 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

| 0x001E            | INT_CFDATA6 | R 0<br>W | 0 | 0       | 0        | 0 | PRIOLVL[2:0] |   |       |  |

#### How to Reach Us:

Home Page:

nxp.com

Web Support

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX, EMBRACE, GREENCHIP, HITAG, I2C BUS, ICODE, JCOP, LIFE VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, C-5, CodeTEST, CodeWarrior, ColdFire, ColdFire+, C-Ware, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorIQ, QorIQ Qonverge, Ready Play, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, SMARTMOS, Tower, TurboLink, and UMEMS are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM, AMBA, ARM Powered, Artisan, Cortex, Jazelle, Keil, SecurCore, Thumb, TrustZone, and µVision are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. ARM7, ARM9, ARM11, big.LITTLE, CoreLink, CoreSight, DesignStart, Mali, mbed, NEON, POP, Sensinode, Socrates, ULINK and Versatile are trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© 2016 NXP B.V.