# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, SCI, SPI                                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 9x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-HLQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvmc64f2wkh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Chapter 2 Port Integration Module (S12ZVMPIMV3)

| Port | Pin<br>Name | ZVMC256 | ZVMC128\64 | ZVML128/64/32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ZVML31 | ZVM32/16 | Pin Function<br>& Priority <sup>1</sup> | I/O | Description                                  | Routing<br>Register Bit | Pin Function<br>after Reset |

|------|-------------|---------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|-----------------------------------------|-----|----------------------------------------------|-------------------------|-----------------------------|

| AD   | PAD7        | <       | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | ~        | AMPP1                                   | Ι   | GDU AMP1 non-inverting input (+)             | —                       | GPIO                        |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AN1_2                                   | Ι   | ADC1 analog input                            | _                       |                             |

|      |             |         |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | •      | >        | PTADL[7]/<br>KWADL[7]                   | I/O | General-purpose; with interrupt and wakeup   | —                       |                             |

|      | PAD6        | <       | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | >      | >        | AMPM1                                   | Ι   | GDU AMP1 inverting input (-)                 |                         |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | ( <u>SS0</u> )                          | I/O | SPI0 slave select                            | SPI0SSRR                |                             |

|      |             | ~       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AN1_1                                   | Ι   | ADC1 analog input                            | —                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[6]/<br>KWADL[6]                   | I/O | General-purpose; with interrupt and wakeup   | —                       |                             |

|      | PAD5        | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AMP1                                    | 0   | GDU AMP1 output                              |                         |                             |

|      |             | ~       | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AN1_0                                   | Ι   | ADC1 analog input                            | _                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[5]/<br>KWADL[5]                   | I/O | General-purpose; with interrupt and wakeup — |                         |                             |

|      | PAD4        | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •      | >        | AN0_4                                   | Ι   | ADC0 analog input                            |                         |                             |

|      |             | >       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[4]/<br>KWADL[4]                   | I/O | General-purpose; with interrupt and wakeup   | _                       |                             |

|      | PAD3        | ~       | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | ~        | AN0_3                                   | Ι   | ADC0 analog input                            | —                       |                             |

|      |             | >       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[3]/<br>KWADL[3]                   | I/O | General-purpose; with interrupt and wakeup   | —                       |                             |

|      | PAD2        | ~       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AMPP0                                   | Ι   | GDU AMP0 non-inverting input (+)             | _                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AN0_2                                   | Ι   | ADC0 analog input                            | —                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[2]/<br>KWADL[2]/                  | I/O | General-purpose; with interrupt and wakeup   | —                       |                             |

|      | PAD1        | <       | ~          | ~                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | ~        | AMPM0                                   | Ι   | GDU AMP0 inverting input (-)                 | —                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AN0_1                                   | Ι   | ADC0 analog input                            | _                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[1]/<br>KWADL[1]                   | I/O | General-purpose; with interrupt and wakeup   | —                       |                             |

|      | PAD0        | ~       | >          | Image: View of the second s |        |          |                                         |     | —                                            |                         |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | AN0_0                                   | Ι   | ADC0 analog input                            | —                       |                             |

|      |             | •       | >          | >                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ~      | >        | PTADL[0]/<br>KWADL[0]                   | I/O | General-purpose; with interrupt and wakeup   | _                       |                             |

1. Signals in parentheses denote alternative module routing pins.

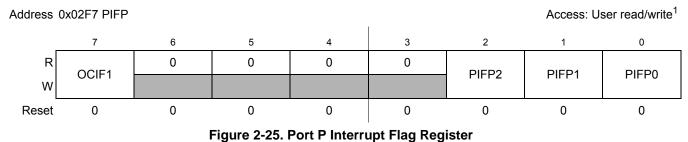

# 2.3.4.3 Port P Interrupt Flag Register (PIFP)

1. Read: Anytime

Write: Anytime, write 1 to clear

### Table 2-29. Port P Interrupt Flag Register Field Descriptions

| Field          | Description                                                                                                  |  |  |  |  |  |

|----------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 7<br>OCIF1     | Over-Current Interrupt Flag register —                                                                       |  |  |  |  |  |

|                | This flag asserts if an over-current condition is detected on PP0 (Section 2.4.5, "Over-Current Interrupt"). |  |  |  |  |  |

|                | Writing a logic "1" to the corresponding bit field clears the flag.                                          |  |  |  |  |  |

|                | 1 PP0 Over-current event occurred<br>0 No PP0 over-current event occurred                                    |  |  |  |  |  |

| 2-0<br>PIFP2-0 | See Section 2.3.3.7, "Port Interrupt Flag Register"                                                          |  |  |  |  |  |

| Field                    | Description                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-4 (MMCECL)<br>ACC[3:0] | <ul> <li>Access Type Field — The ACC[3:0] bits capture the type of memory access, which caused the access violation. The access type is captured in form of a 4 bit value which is assigned as follows:</li> <li>0: none (no error condition detected)</li> <li>1: opcode fetch</li> <li>2: vector fetch</li> <li>3: data load</li> <li>4: data store</li> <li>5-15: reserved</li> </ul> |

| 3-0 (MMCECL)<br>ERR[3:0] | <ul> <li>Error Type Field — The EC[3:0] bits capture the type of the access violation. The type is captured in form of a 4 bit value which is assigned as follows:</li> <li>0: none (no error condition detected)</li> <li>1: access to an illegal access</li> <li>2: uncorrectable ECC error</li> <li>3-15:reserved</li> </ul>                                                          |

The MMCEC register captures debug information about access violations. It is set to a non-zero value if a S12ZCPU access violation or an uncorrectable ECC error has occurred. At the same time this register is set to a non-zero value, access information is captured in the MMCPCn and MMCCCRn registers. The MMCECn, the MMCPCn and the MMCCCRn registers are not updated if the MMCECn registers contain a non-zero value. The MMCECn registers are cleared by writing the value 0xFFFF.

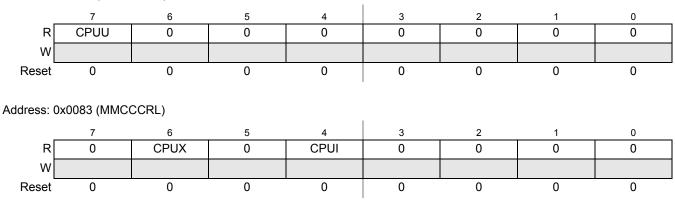

### 3.3.2.3 Captured S12ZCPU Condition Code Register (MMCCCRH, MMCCCRL)

Address: 0x0082 (MMCCCRH)

Read: Anytime

Write: Never

| Table 6-9. DBGTCRH | <b>Field Descriptions</b> |

|--------------------|---------------------------|

|--------------------|---------------------------|

| Field         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>TSOURCE  | Trace Control Bits — The TSOURCE enables the tracing session.         0 No CPU tracing/profiling selected         1 CPU tracing/profiling selected                                                                                                                                                                                                                                                                                                          |

| 5–4<br>TRANGE | <b>Trace Range Bits</b> — The TRANGE bits allow filtering of trace information from a selected address range when tracing from the CPU in Detail mode. These bits have no effect in other tracing modes. To use a comparator for range filtering, the corresponding COMPE bit must remain cleared. If the COMPE bit is set then the comparator is used to generate events and the TRANGE bits have no effect. See Table 6-10 for range boundary definition. |

| 3–2<br>TRCMOD | <b>Trace Mode Bits</b> — See Section 6.4.5.2 for detailed Trace Mode descriptions. In Normal Mode, change of flow information is stored. In Loop1 Mode, change of flow information is stored but redundant entries into trace memory are inhibited. In Detail Mode, address and data for all memory and register accesses is stored. See Table 6-11.                                                                                                        |

| 1–0<br>TALIGN | <b>Trigger Align Bits</b> — These bits control whether the trigger is aligned to the beginning, end or the middle of a tracing or profiling session. See Table 6-12.                                                                                                                                                                                                                                                                                        |

### Table 6-10. TRANGE Trace Range Encoding

| TRANGE | Tracing Range                                             |  |  |  |  |  |

|--------|-----------------------------------------------------------|--|--|--|--|--|

| 00     | Trace from all addresses (No filter)                      |  |  |  |  |  |

| 01     | Trace only in address range from \$00000 to Comparator D  |  |  |  |  |  |

| 10     | Trace only in address range from Comparator C to \$FFFFFF |  |  |  |  |  |

| 11     | 11 Trace only in range from Comparator C to Comparator D  |  |  |  |  |  |

#### Table 6-11. TRCMOD Trace Mode Bit Encoding

| TRCMOD | Description |

|--------|-------------|

| 00     | Normal      |

| 01     | Loop1       |

| 10     | Detail      |

| 11     | Pure PC     |

### Table 6-12. TALIGN Trace Alignment Encoding

| TALIGN            | Description                           |

|-------------------|---------------------------------------|

| 00                | Trigger ends data trace               |

| 01                | Trigger starts data trace             |

| 10                | 32 lines of data trace follow trigger |

| 11 <sup>(1)</sup> | Reserved                              |

1. Tracing/Profiling disabled.

#### Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

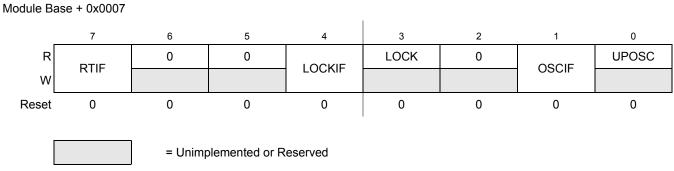

### Figure 8-12. S12CPMU\_UHV\_V10\_V6 Flags Register (CPMUIFLG)

### Read: Anytime

Write: Refer to each bit for individual write conditions

Table 8-5. CPMUIFLG Field Descriptions

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>RTIF   | Real Time Interrupt Flag — RTIF is set to 1 at the end of the RTI period. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (RTIE=1), RTIF causes an interrupt request.         0       RTI time-out has not yet occurred.         1       RTI time-out has occurred.                                                                                                                                                                   |

| 4<br>LOCKIF | <ul> <li>PLL Lock Interrupt Flag — LOCKIF is set to 1 when LOCK status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (LOCKIE=1), LOCKIF causes an interrupt request.</li> <li>0 No change in LOCK bit.</li> <li>1 LOCK bit has changed.</li> </ul>                                                                                                                                                                     |

| 3<br>LOCK   | Lock Status Bit — LOCK reflects the current state of PLL lock condition. Writes have no effect. While PLL is<br>unlocked (LOCK=0) $f_{PLL}$ is $f_{VCO}$ / 4 to protect the system from high core clock frequencies during the PLL<br>stabilization time $t_{lock}$ .0VCOCLK is not within the desired tolerance of the target frequency.<br>$f_{PLL} = f_{VCO}/4$ .1VCOCLK is within the desired tolerance of the target frequency.<br>$f_{PLL} = f_{VCO}/(POSTDIV+1)$ . |

| 1<br>OSCIF  | <ul> <li>Oscillator Interrupt Flag — OSCIF is set to 1 when UPOSC status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (OSCIE=1), OSCIF causes an interrupt request.</li> <li>0 No change in UPOSC bit.</li> <li>1 UPOSC bit has changed.</li> </ul>                                                                                                                                                                   |

| 0<br>UPOSC  | <ul> <li>Oscillator Status Bit — UPOSC reflects the status of the oscillator. Writes have no effect. Entering Full Stop Mode UPOSC is cleared.</li> <li>0 The oscillator is off or oscillation is not qualified by the PLL.</li> <li>1 The oscillator is qualified by the PLL.</li> </ul>                                                                                                                                                                                 |

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

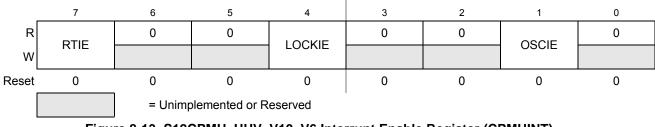

### 8.3.2.8 S12CPMU\_UHV\_V10\_V6 Interrupt Enable Register (CPMUINT)

This register enables S12CPMU\_UHV\_V10\_V6 interrupt requests.

Module Base + 0x0008

Figure 8-13. S12CPMU\_UHV\_V10\_V6 Interrupt Enable Register (CPMUINT)

Read: Anytime

Write: Anytime

### Table 8-6. CPMUINT Field Descriptions

| Field       | Description                                                                                                                                              |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 7<br>RTIE   | Real Time Interrupt Enable Bit         0 Interrupt requests from RTI are disabled.         1 Interrupt will be requested whenever RTIF is set.           |  |  |  |  |  |  |

| 4<br>LOCKIE | PLL Lock Interrupt Enable Bit         0 PLL LOCK interrupt requests are disabled.         1 Interrupt will be requested whenever LOCKIF is set.          |  |  |  |  |  |  |

| 1<br>OSCIE  | Oscillator Corrupt Interrupt Enable Bit<br>0 Oscillator Corrupt interrupt requests are disabled.<br>1 Interrupt will be requested whenever OSCIF is set. |  |  |  |  |  |  |

|            | RTR[6:4] =                  |                             |                             |                              |                              |                              |                               |                               |  |  |  |

|------------|-----------------------------|-----------------------------|-----------------------------|------------------------------|------------------------------|------------------------------|-------------------------------|-------------------------------|--|--|--|

| RTR[3:0]   | 000<br>(1x10 <sup>3</sup> ) | 001<br>(2x10 <sup>3</sup> ) | 010<br>(5x10 <sup>3</sup> ) | 011<br>(10x10 <sup>3</sup> ) | 100<br>(20x10 <sup>3</sup> ) | 101<br>(50x10 <sup>3</sup> ) | 110<br>(100x10 <sup>3</sup> ) | 111<br>(200x10 <sup>3</sup> ) |  |  |  |

| 0000 (÷1)  | 1x10 <sup>3</sup>           | 2x10 <sup>3</sup>           | 5x10 <sup>3</sup>           | 10x10 <sup>3</sup>           | 20x10 <sup>3</sup>           | 50x10 <sup>3</sup>           | 100x10 <sup>3</sup>           | 200x10 <sup>3</sup>           |  |  |  |

| 0001 (÷2)  | 2x10 <sup>3</sup>           | 4x10 <sup>3</sup>           | 10x10 <sup>3</sup>          | 20x10 <sup>3</sup>           | 40x10 <sup>3</sup>           | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>           | 400x10 <sup>3</sup>           |  |  |  |

| 0010 (÷3)  | 3x10 <sup>3</sup>           | 6x10 <sup>3</sup>           | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>           | 60x10 <sup>3</sup>           | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>           | 600x10 <sup>3</sup>           |  |  |  |

| 0011 (÷4)  | 4x10 <sup>3</sup>           | 8x10 <sup>3</sup>           | 20x10 <sup>3</sup>          | 40x10 <sup>3</sup>           | 80x10 <sup>3</sup>           | 200x10 <sup>3</sup>          | 400x10 <sup>3</sup>           | 800x10 <sup>3</sup>           |  |  |  |

| 0100 (÷5)  | 5x10 <sup>3</sup>           | 10x10 <sup>3</sup>          | 25x10 <sup>3</sup>          | 50x10 <sup>3</sup>           | 100x10 <sup>3</sup>          | 250x10 <sup>3</sup>          | 500x10 <sup>3</sup>           | 1x10 <sup>6</sup>             |  |  |  |

| 0101 (÷6)  | 6x10 <sup>3</sup>           | 12x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 60x10 <sup>3</sup>           | 120x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 600x10 <sup>3</sup>           | 1.2x10 <sup>6</sup>           |  |  |  |

| 0110 (÷7)  | 7x10 <sup>3</sup>           | 14x10 <sup>3</sup>          | 35x10 <sup>3</sup>          | 70x10 <sup>3</sup>           | 140x10 <sup>3</sup>          | 350x10 <sup>3</sup>          | 700x10 <sup>3</sup>           | 1.4x10 <sup>6</sup>           |  |  |  |

| 0111 (÷8)  | 8x10 <sup>3</sup>           | 16x10 <sup>3</sup>          | 40x10 <sup>3</sup>          | 80x10 <sup>3</sup>           | 160x10 <sup>3</sup>          | 400x10 <sup>3</sup>          | 800x10 <sup>3</sup>           | 1.6x10 <sup>6</sup>           |  |  |  |

| 1000 (÷9)  | 9x10 <sup>3</sup>           | 18x10 <sup>3</sup>          | 45x10 <sup>3</sup>          | 90x10 <sup>3</sup>           | 180x10 <sup>3</sup>          | 450x10 <sup>3</sup>          | 900x10 <sup>3</sup>           | 1.8x10 <sup>6</sup>           |  |  |  |

| 1001 (÷10) | 10 x10 <sup>3</sup>         | 20x10 <sup>3</sup>          | 50x10 <sup>3</sup>          | 100x10 <sup>3</sup>          | 200x10 <sup>3</sup>          | 500x10 <sup>3</sup>          | 1x10 <sup>6</sup>             | 2x10 <sup>6</sup>             |  |  |  |

| 1010 (÷11) | 11 x10 <sup>3</sup>         | 22x10 <sup>3</sup>          | 55x10 <sup>3</sup>          | 110x10 <sup>3</sup>          | 220x10 <sup>3</sup>          | 550x10 <sup>3</sup>          | 1.1x10 <sup>6</sup>           | 2.2x10 <sup>6</sup>           |  |  |  |

| 1011 (÷12) | 12x10 <sup>3</sup>          | 24x10 <sup>3</sup>          | 60x10 <sup>3</sup>          | 120x10 <sup>3</sup>          | 240x10 <sup>3</sup>          | 600x10 <sup>3</sup>          | 1.2x10 <sup>6</sup>           | 2.4x10 <sup>6</sup>           |  |  |  |

| 1100 (÷13) | 13x10 <sup>3</sup>          | 26x10 <sup>3</sup>          | 65x10 <sup>3</sup>          | 130x10 <sup>3</sup>          | 260x10 <sup>3</sup>          | 650x10 <sup>3</sup>          | 1.3x10 <sup>6</sup>           | 2.6x10 <sup>6</sup>           |  |  |  |

| 1101 (÷14) | 14x10 <sup>3</sup>          | 28x10 <sup>3</sup>          | 70x10 <sup>3</sup>          | 140x10 <sup>3</sup>          | 280x10 <sup>3</sup>          | 700x10 <sup>3</sup>          | 1.4x10 <sup>6</sup>           | 2.8x10 <sup>6</sup>           |  |  |  |

| 1110 (÷15) | 15x10 <sup>3</sup>          | 30x10 <sup>3</sup>          | 75x10 <sup>3</sup>          | 150x10 <sup>3</sup>          | 300x10 <sup>3</sup>          | 750x10 <sup>3</sup>          | 1.5x10 <sup>6</sup>           | 3x10 <sup>6</sup>             |  |  |  |

| 1111 (÷16) | 16x10 <sup>3</sup>          | 32x10 <sup>3</sup>          | 80x10 <sup>3</sup>          | 160x10 <sup>3</sup>          | 320x10 <sup>3</sup>          | 800x10 <sup>3</sup>          | 1.6x10 <sup>6</sup>           | 3.2x10 <sup>6</sup>           |  |  |  |

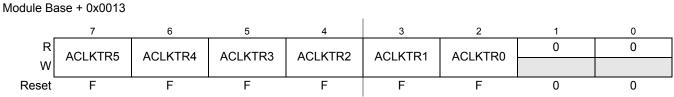

### 8.3.2.19 Autonomous Clock Trimming Register (CPMUACLKTR)

The CPMUACLKTR register configures the trimming of the Autonomous Clock (ACLK - trimmable internal RC-Oscillator) which can be selected as clock source for some CPMU features.

After de-assert of System Reset a value is automatically loaded from the Flash memory.

### Figure 8-26. Autonomous Clock Trimming Register (CPMUACLKTR)

Read: Anytime

Write: Anytime

### Table 8-20. CPMUACLKTR Field Descriptions

| Field       | Description                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------|

| 7–2         | Autonomous Clock Period Trimming Bits — See Table 8-21 for trimming effects. The ACLKTR[5:0] value |

| ACLKTR[5:0] | represents a signed number influencing the ACLK period time.                                       |

### Table 8-21. Trimming Effect of ACLKTR[5:0]

| ACLKTR[5:0] | Decimal | ACLK frequency |

|-------------|---------|----------------|

| 100000      | -32     | lowest         |

| 100001      | -31     |                |

|             |         | increasing     |

| 111111      | -1      |                |

| 000000      | 0       | mid            |

| 000001      | +1      |                |

|             |         | increasing     |

| 011110      | +30     |                |

| 011111      | +31     | highest        |

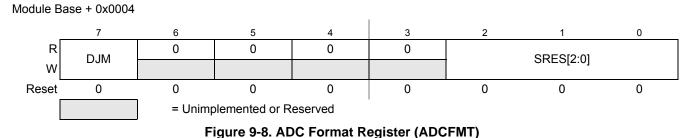

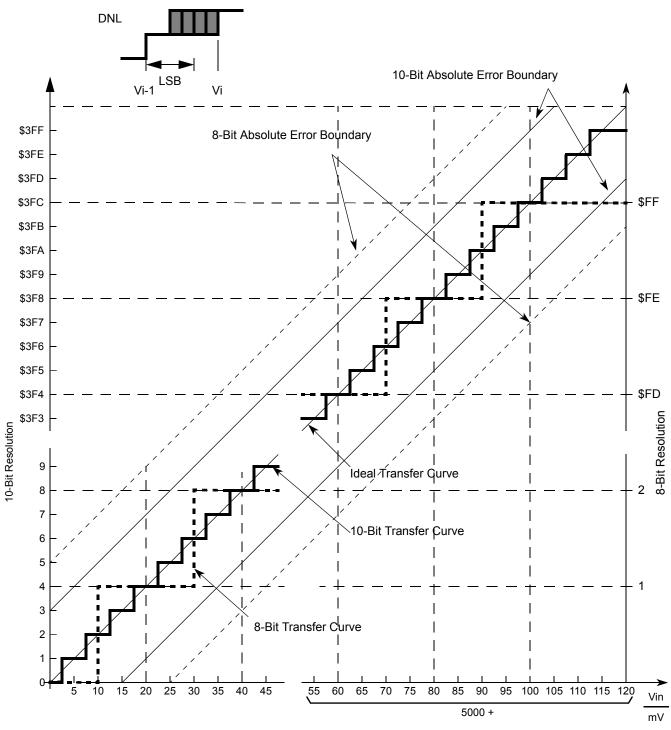

### 9.5.2.5 ADC Format Register (ADCFMT)

Read: Anytime

Write: Bits DJM and SRES[2:0] are writable if bit ADC\_EN clear or bit SMOD\_ACC set

### Table 9-8. ADCFMT Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>DJM         | <ul> <li>Result Register Data Justification — Conversion result data format is always unsigned. This bit controls justification of conversion result data in the conversion result list.</li> <li>0 Left justified data in the conversion result list.</li> <li>1 Right justified data in the conversion result list.</li> </ul> |

| 2-0<br>SRES[2:0] | <b>ADC Resolution Select</b> — These bits select the resolution of conversion results. See Table 9-9 for coding.                                                                                                                                                                                                                 |

### Table 9-9. Selectable Conversion Resolution

| SRES[2] | SRES[1] | SRES[0] | ADC Resolution  |

|---------|---------|---------|-----------------|

| 0       | 0       | 0       | 8-bit data      |

| 0       | 0       | 1       | 1.<br>Reserved  |

| 0       | 1       | 0       | 10-bit data     |

| 0       | 1       | 1       | 1.<br>Reserved  |

| 1       | 0       | 0       | 12-bit data     |

| 1       | x       | x       | (1)<br>Reserved |

1. Reserved settings cause a severe error at ADC conversion start whereby the CMD\_EIF flag is set and ADC ceases operation

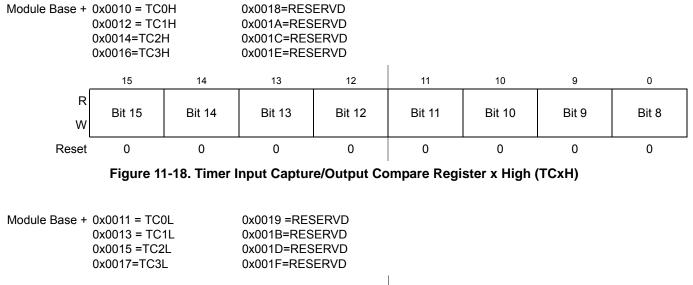

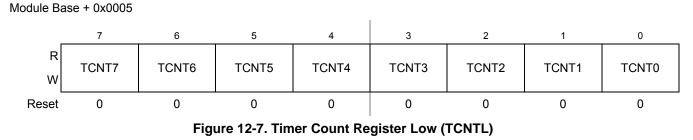

### 11.3.2.12 Timer Input Capture/Output Compare Registers High and Low 0– 3(TCxH and TCxL)

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| R<br>W | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |