# E·XFL

What is "Embedded - Microcontrollers"?

#### Details

# "Embedded - Microcontrollers" refer to small, integrated

Welcome to E-XFL.COM

circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | LINbus, SCI, SPI                                                        |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 9x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-HLQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvml12f3wkh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 1.8.7          | FTMRZ Connectivity                                 |      |

|------|----------------|----------------------------------------------------|------|

| 1.0  |                | CPMU Connectivity                                  |      |

| 1.9  |                | of Operation                                       |      |

|      | 1.9.1<br>1.9.2 | Chip Configuration Modes                           |      |

|      |                | Debugging Modes                                    |      |

| 1 10 |                | Low Power Modes                                    |      |

| 1.10 |                | Features                                           |      |

|      |                | Securing the Microcontroller                       |      |

|      |                | Operation of the Secured Microcontroller           |      |

|      |                | Unsecuring the Microcontroller                     |      |

|      |                | Reprogramming the Security Bits                    |      |

|      |                | Complete Memory Erase                              |      |

| 1.11 |                | Ind Interrupts                                     |      |

|      | 1.11.1         | Reset                                              | . 71 |

|      | 1.11.2         | Interrupt Vectors                                  | . 71 |

|      | 1.11.3         | Effects of Reset                                   | . 74 |

| 1.12 | Module         | device level dependencies                          | . 75 |

|      |                | CPMU COP and GDU Configuration                     |      |

|      |                | CPMU High Temperature Trimming                     |      |

|      |                | CPMU VDDC enable                                   |      |

|      |                | Flash IFR Mapping                                  |      |

| 1.13 |                | tion Information                                   |      |

|      |                | ADC Calibration                                    |      |

|      |                | SCI Baud Rate Detection                            |      |

|      |                | Motor Control Application Overview                 |      |

|      |                | BDCM Complementary Mode Operation                  |      |

|      |                | BLDC Six-Step Commutation                          |      |

|      |                | PMSM Control                                       |      |

|      |                | Power Domain Overview (All devices except ZVMC256) |      |

|      | 1.13.8         | Power Domain Overview (ZVMC256)                    | . 98 |

# Chapter 2 Port Integration Module (S12ZVMPIMV3)

| 104<br>107 |

|------------|

| 107        |

|            |

| 108        |

| 115        |

| 116        |

| 122        |

| 133        |

| 140        |

| 147        |

| 147        |

|            |

Chapter 1 Device Overview MC9S12ZVM-Family

### **1.2.3** Functional Differences Between Masksets

The parts ZVML128, ZVMC128, ZVML64, ZVMC64 and ZVML32 have the following mask set options.

### Table 1-19

| Feature                                           | 0N95G <sup>(1)</sup> | 1N95G | 2N95G | 3N95G |

|---------------------------------------------------|----------------------|-------|-------|-------|

| LINPHY supply pin                                 | HD                   | HD    | VSUP  | HD    |

| BST pin function available                        | Yes                  | Yes   | No    | Yes   |

| GDU low side driver state in HD over-voltage case | on                   | GOCA1 | GOCA1 | GOCA1 |

#### Table 1-4. N95G Option Table

1. 0N95G is not a production mask set

# 1.3 Chip-Level Features

On-chip modules available within the family include the following features:

- S12Z CPU core

- 256, 128, 64, 32 or 16KB on-chip flash with ECC

- 1K, 512 or 128 byte EEPROM with ECC

- 32, 8, 4 or 2 KB on-chip SRAM with ECC

- Phase locked loop (IPLL) frequency multiplier with internal filter

- 1 MHz internal RC oscillator with +/-1.3% accuracy over rated temperature range

- 4-20MHz amplitude controlled pierce oscillator

- Internal COP (watchdog) module

- 6-channel, 15-bit pulse width modulator with fault protection (PMF)

- Low side and high side FET pre-drivers for each phase

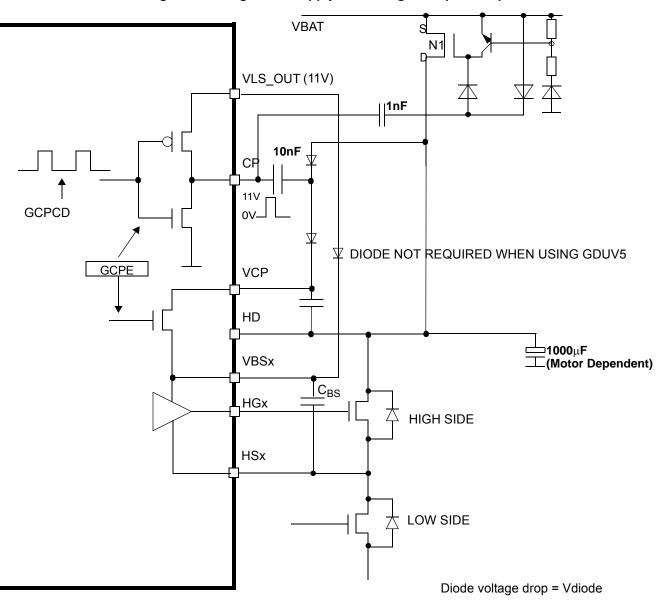

- Gate drive pre-regulator

- LDO (Low Dropout Voltage Regulator) (typically 11V)

- High side gate supply generated using bootstrap circuit with external diode and capacitor

- Sustaining charge pump with two external capacitors and diodes

- High side drain (HD) monitoring on internal ADC channel using HD/5 voltage

- Two parallel analog-to-digital converters (ADC) with 12-bit resolution and up to 16 channels available on external pins

- Programmable Trigger Unit (PTU) for synchronization of PMF and ADC

- One serial peripheral interface (SPI) module

- One serial communication interface (SCI) module with interface to internal LIN physical layer transceiver (with RX connected to a timer channel for frequency calibration purposes, if desired)

Chapter 1 Device Overview MC9S12ZVM-Family

| Pin | Pin        |              | Function<br>(Priority and routing options defined in PIM chapter) |              |              |              |              |              |                  |                       | al Pull<br>stor |

|-----|------------|--------------|-------------------------------------------------------------------|--------------|--------------|--------------|--------------|--------------|------------------|-----------------------|-----------------|

| #   | Name       | 1st<br>Func. | 2nd<br>Func.                                                      | 3rd<br>Func. | 4th<br>Func. | 5th<br>Func. | 6th<br>Func. | 7th<br>Func. | Supply           | CTRL                  | Reset<br>State  |

| 11  | BCTLS<br>1 | —            | _                                                                 | _            | —            | _            | _            |              | —                | _                     | _               |

| 12  | VDDS1      | VRH0_1       | VRH1_1                                                            | _            |              |              |              |              | —                | _                     | —               |

| 13  | SNPS2      | —            | —                                                                 | _            | —            | —            | —            |              | —                | —                     | —               |

| 14  | BCTLS<br>2 | —            | —                                                                 | _            | —            | —            | —            |              | —                | —                     | _               |

| 15  | VDDS2      | VRH0_2       | VRH1_2                                                            | _            | _            | _            | _            |              | _                | —                     | —               |

| 16  | LD0        |              |                                                                   |              |              |              |              |              | —                |                       | _               |

| 17  | LD1        | —            |                                                                   | _            | _            | —            | _            |              | —                | —                     | —               |

| 18  | LD2        | —            |                                                                   | _            | _            | _            | _            |              | _                |                       | _               |

| 19  | PAD0       | KWAD0        | AN0_0                                                             | AMP0         | _            | _            | _            |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 20  | PAD1       | KWAD1        | AN0_1                                                             | AMPM0        | —            | —            | —            |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 21  | PAD2       | KWAD2        | AN0_2                                                             | AMPP0        | _            | _            | _            |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 22  | PAD3       | KWAD3        | AN0_3                                                             |              |              |              |              |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 23  | PAD4       | KWAD4        | AN0_4                                                             | _            | _            | _            | _            |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 24  | PAD5       | KWAD5        | AN1_0                                                             | AMP1         | _            | _            | _            |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 25  | PAD6       | KWAD6        | AN1_1                                                             | SS0          | AMPM1        |              |              |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 26  | PAD7       | KWAD7        | AN1_2                                                             | AMPP1        | _            | _            | _            |              | V <sub>DDA</sub> | PERAD<br>L/PPSA<br>DL | Off             |

| 27  | PAD8       | KWAD8        | AN1_3                                                             | _            | _            | _            | _            |              | V <sub>DDA</sub> | PERAD<br>H/PPS<br>ADH | Off             |

Table 1-9. Pin Summary For 80-Pin Package Option (ZVMC256 Only) (Sheet 2 of 5)

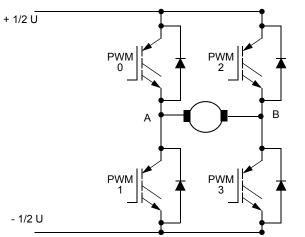

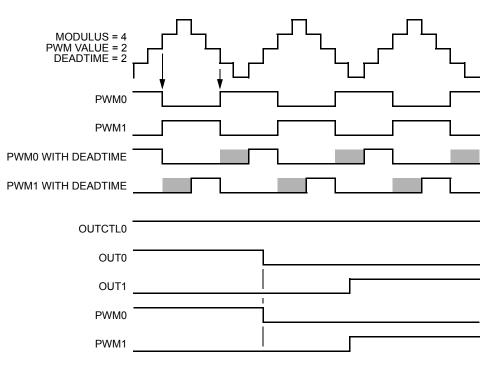

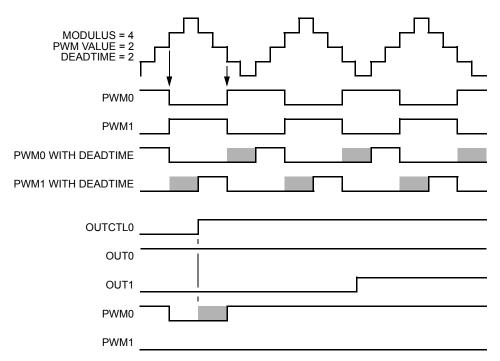

The DC Brushed motor power stage topology is a classical full bridge as shown in Figure 1-11. The DC Brushed motor is driven by the DC voltage source. A rotational field is created by means of commutator and brushes on the motor. These drives are still very popular because sophisticated calculations and algorithms such as commutation, waveform generation, or space vector modulation are not required.

Usually the control consists of an outer, speed control loop with inner current (torque) control loop. The inner loop controls DC voltage applied onto the motor winding. The control loop is calculated regularly within a given period. In most cases, this period matches the PWM reload period.

Driving the DC motor from a DC voltage source, the motor can work in all four quadrants. The complementary mode of operation with deadtime insertion is needed for smooth reversal of the motor

Figure 1-20. High Side Supply and Charge Pump Concept

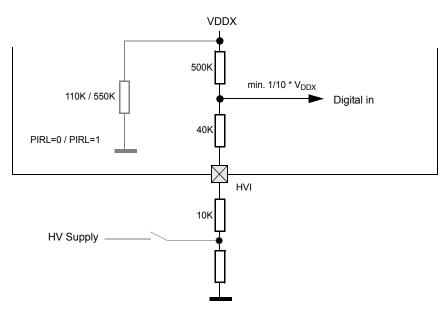

External pulldown device (Figure 2-38):

- 1. Enable analog function on HVI in non-direct mode (PTAENL[PTAENL0]=1, PTAENL[PTADIRL0]=0)

- 2. Select internal pullup device on HVI (PTPSL[PTPSL0]=1)

- 3. Enable function to force input buffer active on HVI in analog mode (PTTEL[PTTEL0]=1)

- 4. Verify PTIL=0 for a connected external pulldown device; read PTIL=1 for an open input

Figure 2-38. Digital Input Read with Pullup Enabled

External pullup device (Figure 2-39):

- 1. Enable analog function on HVI in non-direct mode (PTAENL[PTAENL0]=1, PTADIRL[PTADIRL0]=0)

- 2. Select internal pulldown device on HVI (PTPSL[PTPSL0]=0)

- 3. Enable function to force input buffer active on HVI in analog mode (PTTEL[PTTEL0]=1)

- 4. Verify PTIL0=1 for a connected external pullup device; read PTIL0=0 for an open input

#### Chapter 3 Memory Mapping Control (S12ZMMCV1)

• All illegal accesses performed by an ADC or PTU module trigger error interrupts. See ADC and PTU section for details.

### NOTE

Illegal accesses caused by S12ZCPU opcode prefetches will also trigger machine exceptions, even if those opcodes might not be executed in the program flow. To avoid these machine exceptions, S12ZCPU instructions must not be executed from the last (high addresses) 8 bytes of RAM, EEPROM, and Flash.

### 3.4.3 Uncorrectable ECC Faults

RAM and flash use error correction codes (ECC) to detect and correct memory corruption. Each uncorrectable memory corruption, which is detected during a S12ZCPU, ADC or PTU access triggers a machine exception. Uncorrectable memory corruptions which are detected during a S12ZBDC access, are captured in the RAMWF or the RDINV bit of the BDCCSRL register.

- Initialize the interrupt processing level configuration data registers (INT\_CFADDR, INT\_CFDATA0-7) for all interrupt vector requests with the desired priority levels. It might be a good idea to disable unused interrupt requests.

- Enable I-bit maskable interrupts by clearing the I-bit in the CCW.

- Enable the X-bit maskable interrupt by clearing the X-bit in the CCW (if required).

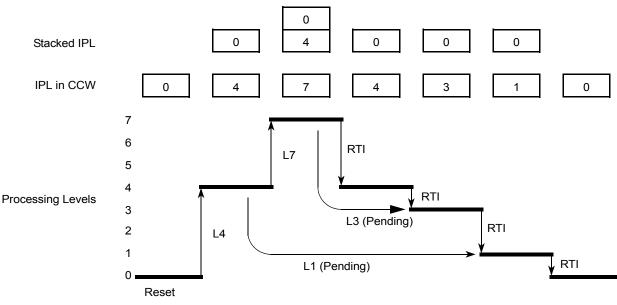

### 4.5.2 Interrupt Nesting

The interrupt request priority level scheme makes it possible to implement priority based interrupt request nesting for the I-bit maskable interrupt requests.

• I-bit maskable interrupt requests can be interrupted by an interrupt request with a higher priority, so that there can be up to seven nested I-bit maskable interrupt requests at a time (refer to Figure 4-14 for an example using up to three nested interrupt requests).

I-bit maskable interrupt requests cannot be interrupted by other I-bit maskable interrupt requests per default. In order to make an interrupt service routine (ISR) interruptible, the ISR must explicitly clear the I-bit in the CCW (CLI). After clearing the I-bit, I-bit maskable interrupt requests with higher priority can interrupt the current ISR.

An ISR of an interruptible I-bit maskable interrupt request could basically look like this:

- Service interrupt, e.g., clear interrupt flags, copy data, etc.

- Clear I-bit in the CCW by executing the CPU instruction CLI (thus allowing interrupt requests with higher priority)

- Process data

- Return from interrupt by executing the instruction RTI

Figure 4-14. Interrupt Processing Example

Chapter 6 S12Z Debug (S12ZDBG) Module

| Address           | Name     |        | Bit 7  | 6            | 5    | 4     | 3        | 2   | 1        | Bit 0  |

|-------------------|----------|--------|--------|--------------|------|-------|----------|-----|----------|--------|

| 0x0128-<br>0x012F | Reserved | R<br>W | 0      | 0            | 0    | 0     | 0        | 0   | 0        | 0      |

| 0x0130            | DBGCCTL  | R<br>W | 0      | NDB          | INST | 0     | RW       | RWE | reserved | COMPE  |

| 0x0131-<br>0x0134 | Reserved | R<br>W | 0      | 0            | 0    | 0     | 0        | 0   | 0        | 0      |

| 0x0135            | DBGCAH   | R<br>W |        |              |      | DBGCA | A[23:16] |     |          |        |

| 0x0136            | DBGCAM   | R<br>W |        |              |      | DBGC  | A[15:8]  |     |          |        |

| 0x0137            | DBGCAL   | R<br>W |        |              |      | DBGC  | CA[7:0]  |     |          |        |

| 0x0138            | DBGCD0   | R<br>W | Bit 31 | 30           | 29   | 28    | 27       | 26  | 25       | Bit 24 |

| 0x0139            | DBGCD1   | R<br>W | Bit 23 | 22           | 21   | 20    | 19       | 18  | 17       | Bit 16 |

| 0x013A            | DBGCD2   | R<br>W | Bit 15 | 14           | 13   | 12    | 11       | 10  | 9        | Bit 8  |

| 0x013B            | DBGCD3   | R<br>W | Bit 7  | 6            | 5    | 4     | 3        | 2   | 1        | Bit 0  |

| 0x013C            | DBGCDM0  | R<br>W | Bit 31 | 30           | 29   | 28    | 27       | 26  | 25       | Bit 24 |

| 0x013D            | DBGCDM1  | R<br>W | Bit 23 | 22           | 21   | 20    | 19       | 18  | 17       | Bit 16 |

| 0x013E            | DBGCDM2  | R<br>W | Bit 15 | 14           | 13   | 12    | 11       | 10  | 9        | Bit 8  |

| 0x013F            | DBGCDM3  | R<br>W | Bit 7  | 6            | 5    | 4     | 3        | 2   | 1        | Bit 0  |

| 0x0140            | DBGDCTL  | R<br>W | 0      | 0            | INST | 0     | RW       | RWE | reserved | COMPE  |

| 0x0141-<br>0x0144 | Reserved | R<br>W | 0      | 0            | 0    | 0     | 0        | 0   | 0        | 0      |

| 0x0145            | DBGDAH   | R<br>W |        | DBGDA[23:16] |      |       |          |     |          |        |

| 0x0146            | DBGDAM   | R<br>W |        | DBGDA[15:8]  |      |       |          |     |          |        |

Figure 6-2. Quick Reference to DBG Registers

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

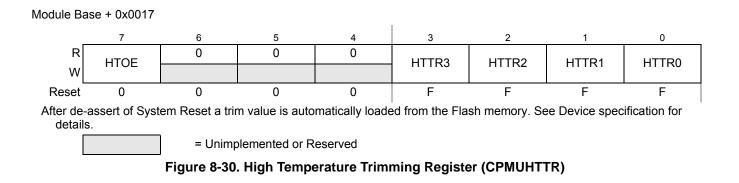

### 8.3.2.22 High Temperature Trimming Register (CPMUHTTR)

The CPMUHTTR register configures the trimming of the S12CPMU\_UHV\_V10\_V6 temperature sense.

Read: Anytime

Write: Anytime

#### Table 8-25. CPMUHTTR Field Descriptions

| Field            | Description                                                                                                                                                                                                                                                                           |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>HTOE        | <ul> <li>High Temperature Offset Enable Bit — If set the temperature sense offset is enabled.</li> <li>0 The temperature sense offset is disabled. HTTR[3:0] bits don't care.</li> <li>1 The temperature sense offset is enabled. HTTR[3:0] select the temperature offset.</li> </ul> |

| 3–0<br>HTTR[3:0] | High Temperature Trimming Bits — See Table 8-26 for trimming effects.                                                                                                                                                                                                                 |

#### Table 8-26. Trimming Effect of HTTR

| HTTR[3:0] | Temperature<br>sensor voltage V <sub>HT</sub> | Interrupt threshold<br>temperatures T <sub>HTIA</sub> and T <sub>HTID</sub> |  |  |  |

|-----------|-----------------------------------------------|-----------------------------------------------------------------------------|--|--|--|

| 0000      | lowest                                        | highest                                                                     |  |  |  |

| 0001      |                                               |                                                                             |  |  |  |

|           | increasing                                    | decreasing                                                                  |  |  |  |

| 1110      |                                               |                                                                             |  |  |  |

| 1111      | highest                                       | lowest                                                                      |  |  |  |

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

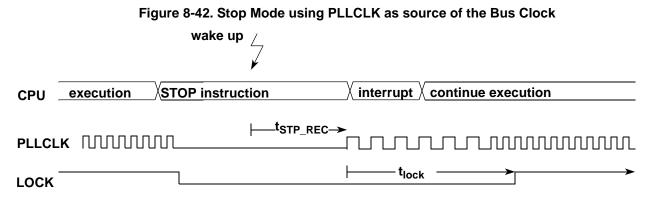

# 8.4.3 Stop Mode using PLLCLK as source of the Bus Clock

An example of what happens going into Stop Mode and exiting Stop Mode after an interrupt is shown in Figure 8-42. Disable PLL Lock interrupt (LOCKIE=0) before going into Stop Mode.

Depending on the COP configuration there might be an additional significant latency time until COP is active again after exit from Stop Mode due to clock domain crossing synchronization. This latency time occurs if COP clock source is ACLK and the CSAD bit is set (please refer to CSAD bit description for details).

### 8.4.4 Full Stop Mode using Oscillator Clock as source of the Bus Clock

An example of what happens going into Full Stop Mode and exiting Full Stop Mode after an interrupt is shown in Figure 8-43.

Disable PLL Lock interrupt (LOCKIE=0) and oscillator status change interrupt (OSCIE=0) before going into Full Stop Mode.

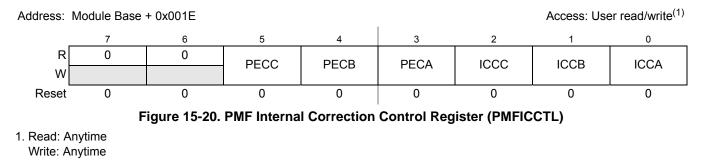

### 15.3.2.17 PMF Internal Correction Control Register (PMFICCTL)

This register is used to control PWM pulse generation for various applications, such as a power-supply phase-shifting application.

ICC*x* bits apply only in center-aligned operation during complementary mode. These control bits determine whether values set in the IPOL*x* bits control or the whether PWM count direction controls which PWM value register is used.

### NOTE

The ICCx bits are buffered. The value written does not take effect until the next PWM load cycle begins regardless of the state of the LDOK bit or global load OK. Reading ICCx returns the value in a buffer and not necessarily the value the PWM generator is currently using.

The PECx bits apply in edge-aligned and center-aligned operation during complementary mode. Setting the PECx bits overrides the ICCx settings. This allows the PWM pulses generated by both the odd and even PWM value registers to be ANDed together prior to the complementary logic and deadtime insertion.

### NOTE

The PECx bits are buffered. The value written does not take effect until the related LDOK bit or global load OK is set and the next PWM load cycle begins. Reading PECn returns the value in a buffer and not necessarily the value the PWM generator is currently using.

| Field     | Description                                                                                                                                                                        |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>PECC | Pulse Edge Control — This bit controls PWM4/PWM5 pair.<br>0 Normal operation<br>1 Allow one of PMFVAL4 and PMFVAL5 to activate the PWM pulse and the other to deactivate the pulse |

| 4<br>PECB | Pulse Edge Control — This bit controls PWM2/PWM3 pair.<br>0 Normal operation<br>1 Allow one of PMFVAL2 and PMFVAL3 to activate the PWM pulse and the other to deactivate the pulse |

| 3<br>PECA | Pulse Edge Control — This bit controls PWM0/PWM1 pair.<br>0 Normal operation<br>1 Allow one of PMFVAL0 and PMFVAL1 to activate the PWM pulse and the other to deactivate the pulse |

Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

Figure 15-69. Clearing OUT0 with OUTCTL Set in Complementary Mode

Figure 15-70. Setting OUTCTL with OUT0 Set in Complementary Mode

Chapter 17 Serial Peripheral Interface (S12SPIV5)

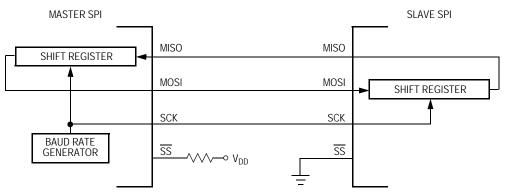

### 17.2.2 MISO — Master In/Slave Out Pin

This pin is used to transmit data out of the SPI module when it is configured as a slave and receive data when it is configured as master.

# 17.2.3 SS — Slave Select Pin

This pin is used to output the select signal from the SPI module to another peripheral with which a data transfer is to take place when it is configured as a master and it is used as an input to receive the slave select signal when the SPI is configured as slave.

### 17.2.4 SCK — Serial Clock Pin

In master mode, this is the synchronous output clock. In slave mode, this is the synchronous input clock.

# 17.3 Memory Map and Register Definition

This section provides a detailed description of address space and registers used by the SPI.

### 17.3.1 Module Memory Map

The memory map for the SPI is given in Figure 17-2. The address listed for each register is the sum of a base address and an address offset. The base address is defined at the SoC level and the address offset is defined at the module level. Reads from the reserved bits return zeros and writes to the reserved bits have no effect.

| Register<br>Name |        | Bit 7 | 6          | 5            | 4      | 3       | 2    | 1       | Bit 0 |

|------------------|--------|-------|------------|--------------|--------|---------|------|---------|-------|

| 0x0000<br>SPICR1 | R<br>W | SPIE  | SPE        | SPTIE        | MSTR   | CPOL    | CPHA | SSOE    | LSBFE |

| 0x0001<br>SPICR2 | R<br>W | 0     | XFRW       | 0            | MODFEN | BIDIROE | 0    | SPISWAI | SPC0  |

| 0x0002<br>SPIBR  | R<br>W | 0     | SPPR2      | SPPR1        | SPPR0  | 0       | SPR2 | SPR1    | SPR0  |

| 0x0003           | R      | SPIF  | 0          | SPTEF        | MODF   | 0       | 0    | 0       | 0     |

| SPISR            | W      |       |            |              |        |         |      |         |       |

| 0x0004           | R      | R15   | R14        | R13          | R12    | R11     | R10  | R9      | R8    |

| SPIDRH           | W      | T15   | T14        | T13          | T12    | T11     | T10  | Т9      | T8    |

| 0x0005           | R      | R7    | R6         | R5           | R4     | R3      | R2   | R1      | R0    |

| SPIDRL           | W      | Τ7    | T6         | T5           | T4     | T3      | T2   | T1      | Т0    |

| 0x0006           | R      |       |            |              |        |         |      |         |       |

| Reserved         | W      |       |            |              |        |         |      |         |       |

|                  |        |       | = Unimplem | ented or Res | erved  |         |      |         |       |

Figure 17-2. SPI Register Summary

#### Chapter 17 Serial Peripheral Interface (S12SPIV5)

As long as no more than one slave device drives the system slave's serial data output line, it is possible for several slaves to receive the same transmission from a master, although the master would not receive return information from all of the receiving slaves.

If the CPHA bit in SPI control register 1 is clear, odd numbered edges on the SCK input cause the data at the serial data input pin to be latched. Even numbered edges cause the value previously latched from the serial data input pin to shift into the LSB or MSB of the SPI shift register, depending on the LSBFE bit.

If the CPHA bit is set, even numbered edges on the SCK input cause the data at the serial data input pin to be latched. Odd numbered edges cause the value previously latched from the serial data input pin to shift into the LSB or MSB of the SPI shift register, depending on the LSBFE bit.

When CPHA is set, the first edge is used to get the first data bit onto the serial data output pin. When CPHA is clear and the  $\overline{SS}$  input is low (slave selected), the first bit of the SPI data is driven out of the serial data output pin. After the nth<sup>1</sup> shift, the transfer is considered complete and the received data is transferred into the SPI data register. To indicate transfer is complete, the SPIF flag in the SPI status register is set.

### NOTE

A change of the bits CPOL, CPHA, SSOE, LSBFE, MODFEN, SPC0, or BIDIROE with SPC0 set in slave mode will corrupt a transmission in progress and must be avoided.

### 17.4.3 Transmission Formats

During an SPI transmission, data is transmitted (shifted out serially) and received (shifted in serially) simultaneously. The serial clock (SCK) synchronizes shifting and sampling of the information on the two serial data lines. A slave select line allows selection of an individual slave SPI device; slave devices that are not selected do not interfere with SPI bus activities. Optionally, on a master SPI device, the slave select line can be used to indicate multiple-master bus contention.

Figure 17-11. Master/Slave Transfer Block Diagram

### 17.4.3.1 Clock Phase and Polarity Controls

Using two bits in the SPI control register 1, software selects one of four combinations of serial clock phase and polarity.

1. n depends on the selected transfer width, please refer to Section 17.3.2.2, "SPI Control Register 2 (SPICR2)

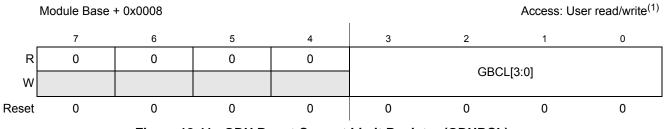

### 18.3.2.9 GDU Boost Current Limit Register (GDUBCL)

Figure 18-11. GDU Boost Current Limit Register (GDUBCL)

1. Read: Anytime

Write: Anytime if GWP=0

#### Table 18-12. GDU Boost Current Limit Register Field Descriptions

| Field     | Description                                                                                                                                                                                                          |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GBCL[3:0] | GDU Boost Current Limit Register— These bits are used to adjust the boost coil current limit <sub>ICOIL0,16</sub> on the BST pin. These bits cannot be modified after GWP bit is set. See GDU electrical parameters. |

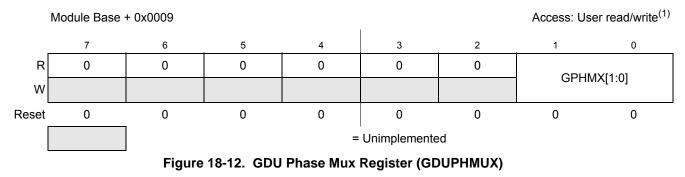

### 18.3.2.10 GDU Phase Mux Register (GDUPHMUX)

1. Read: Anytime Write: Anytime

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| [1:0]<br>GPHMUX | GDU Phase Multiplexer — These buffered bits are used to select the voltage which is routed to internal ADC channel. The value written to the GDUPHMUX register does not take effect until the LDOK bit is set and the next PWM reload cycle begins. Reading GDUPHMUX register reads the value in the buffer. It is not necessary the value which is currently used.<br>00 Pin HD selected , $V_{HD}$ / 12 connected to ADC channel<br>01 Pin HS0 selected , $V_{HS0}$ / 6 connected to ADC channel<br>10 Pin HS1 selected , $V_{HS1}$ / 6 connected to ADC channel<br>11 Pin HS2 selected, $V_{HS2}$ / 6 connected to ADC channel |  |  |  |  |  |  |  |

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 2<br>RSVD | <b>Reserved Bit</b> — This bit is reserved and always reads 0.                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|           | <b>Memory Controller Command Completion Status Flag</b> — One or more MGSTAT flag bits are set if an error is detected during execution of a Flash command or during the Flash reset sequence. The MGSTAT bits are cleared automatically at the start of the execution of a Flash command. See Section 20.4.7, "Flash Command Description," and Section 20.6, "Initialization" for details. |  |  |  |  |  |

#### Table 20-17. FSTAT Field Descriptions (continued)

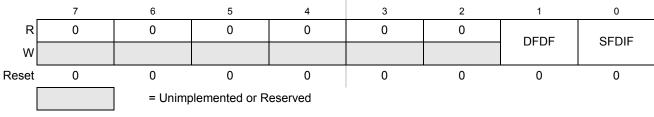

### 20.3.2.8 Flash Error Status Register (FERSTAT)

The FERSTAT register reflects the error status of internal Flash operations.

Offset Module Base + 0x0007

#### Figure 20-12. Flash Error Status Register (FERSTAT)

All flags in the FERSTAT register are readable and only writable to clear the flag.

Table 20-18. FERSTAT Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>DFDF  | <ul> <li>Double Bit Fault Detect Flag — The setting of the DFDF flag indicates that a double bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation.<sup>(1)</sup> The DFDF flag is cleared by writing a 1 to DFDF. Writing a 0 to DFDF has no effect on DFDF.<sup>(2)</sup></li> <li>0 No double bit fault detected</li> <li>1 Double bit fault detected or a Flash array read operation returning invalid data was attempted while command running. See Section 20.4.3, "Flash Block Read Access" for details</li> </ul>            |

| 0<br>SFDIF | <ul> <li>Single Bit Fault Detect Interrupt Flag — With the IGNSF bit in the FCNFG register clear, the SFDIF flag indicates that a single bit fault was detected in the stored parity and data bits during a Flash array read operation or that a Flash array read operation returning invalid data was attempted on a Flash block that was under a Flash command operation. The SFDIF flag is cleared by writing a 1 to SFDIF. Writing a 0 to SFDIF has no effect on SFDIF.</li> <li>0 No single bit fault detected</li> <li>1 Single bit fault detected and corrected or a Flash array read operation returning invalid data was attempted operation returning invalid data was attempted operation.</li> </ul> |

1. In case of ECC errors the corresponding flag must be cleared for the proper setting of any further error, i.e. any new error will only be indicated properly when DFDF and/or SFDIF are clear at the time the error condition is detected.

2. There is a one cycle delay in storing the ECC DFDF and SFDIF fault flags in this register. At least one NOP is required after a flash memory read before checking FERSTAT for the occurrence of ECC errors.

Module Base + 0x00006

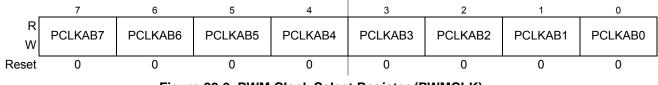

Figure 22-9. PWM Clock Select Register (PWMCLK)

Read: Anytime

Write: Anytime

### NOTE

Register bits PCLKAB0 to PCLKAB7 can be written anytime. If a clock select is changed while a PWM signal is being generated, a truncated or stretched pulse can occur during the transition.

#### Table 22-11. PWMCLK Field Descriptions

**Note:** Bits related to available channels have functional significance. Writing to unavailable bits has no effect. Read from unavailable bits return a zero

| Field        | Description                                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 7<br>PCLKAB7 | <ul> <li>Pulse Width Channel 7 Clock A/B Select</li> <li>0 Clock B or SB is the clock source for PWM channel 7, as shown in Table 22-6.</li> <li>1 Clock A or SA is the clock source for PWM channel 7, as shown in Table 22-6.</li> </ul> |  |  |  |  |  |  |  |

| 6<br>PCLKAB6 | Pulse Width Channel 6 Clock A/B Select<br>Clock B or SB is the clock source for PWM channel 6, as shown in Table 22-6.<br>Clock A or SA is the clock source for PWM channel 6, as shown in Table 22-6.                                     |  |  |  |  |  |  |  |

| 5<br>PCLKAB5 | <ul> <li>Pulse Width Channel 5 Clock A/B Select</li> <li>0 Clock A or SA is the clock source for PWM channel 5, as shown in Table 22-5.</li> <li>1 Clock B or SB is the clock source for PWM channel 5, as shown in Table 22-5.</li> </ul> |  |  |  |  |  |  |  |

| 4<br>PCLKAB4 | <ul> <li>Pulse Width Channel 4 Clock A/B Select</li> <li>0 Clock A or SA is the clock source for PWM channel 4, as shown in Table 22-5.</li> <li>1 Clock B or SB is the clock source for PWM channel 4, as shown in Table 22-5.</li> </ul> |  |  |  |  |  |  |  |

| 3<br>PCLKAB3 | <ul> <li>Pulse Width Channel 3 Clock A/B Select</li> <li>0 Clock B or SB is the clock source for PWM channel 3, as shown in Table 22-6.</li> <li>1 Clock A or SA is the clock source for PWM channel 3, as shown in Table 22-6.</li> </ul> |  |  |  |  |  |  |  |

| 2<br>PCLKAB2 | <ul> <li>Pulse Width Channel 2 Clock A/B Select</li> <li>0 Clock B or SB is the clock source for PWM channel 2, as shown in Table 22-6.</li> <li>1 Clock A or SA is the clock source for PWM channel 2, as shown in Table 22-6.</li> </ul> |  |  |  |  |  |  |  |

| 1<br>PCLKAB1 | <ul> <li>Pulse Width Channel 1 Clock A/B Select</li> <li>0 Clock A or SA is the clock source for PWM channel 1, as shown in Table 22-5.</li> <li>1 Clock B or SB is the clock source for PWM channel 1, as shown in Table 22-5.</li> </ul> |  |  |  |  |  |  |  |

| 0<br>PCLKAB0 | <ul> <li>Pulse Width Channel 0 Clock A/B Select</li> <li>0 Clock A or SA is the clock source for PWM channel 0, as shown in Table 22-5.</li> <li>1 Clock B or SB is the clock source for PWM channel 0, as shown in Table 22-5.</li> </ul> |  |  |  |  |  |  |  |

| Conditions are: V <sub>SUP</sub> =12V, API, COP & RTI enabled |   |                                                   |                    |     |            |            |      |  |

|---------------------------------------------------------------|---|---------------------------------------------------|--------------------|-----|------------|------------|------|--|

| Num                                                           | С | Rating                                            | Symbol             | Min | Тур        | Max        | Unit |  |

| 1                                                             |   | T <sub>J</sub> = 25°C<br>ZVMC256<br>Other devices | I <sub>SUPPS</sub> |     | 430<br>265 | 660<br>300 | μA   |  |

#### Table A-20. Pseudo Stop Current Characteristics

# A.4 ADC Calibration Configuration

The reference voltage  $V_{BG}$  is measured under the conditions shown in Table A-21. The values stored in the IFR are the average of eight consecutive conversions at Tj=150 °C and eight consecutive conversions at Tj=-40 °C. The code is executed from RAM. The result is programmed to the IFR, otherwise there is no flash activity.

| Description                      | Symbol              | Value       | Unit             |

|----------------------------------|---------------------|-------------|------------------|

| Regulator Supply Voltage at VSUP | V <sub>SUP</sub>    | 5           | V                |

| Supply Voltage at VDDX and VDDA  | V <sub>DDX,A</sub>  | 5           | V                |

| ADC reference voltage high       | V <sub>RH</sub>     | 5           | V                |

| ADC reference voltage low        | V <sub>RL</sub>     | 0           | V                |

| ADC clock                        | f <sub>ATDCLK</sub> | 2           | MHz              |

| ADC sample time                  | t <sub>SMP</sub>    | 4           | ADC clock cycles |

| Bus clock frequency              | f <sub>bus</sub>    | 48          | MHz              |

| Junction temperature             | Тj                  | -40 and 150 | °C               |

Table A-21. Measurement Conditions

# M.10 0x0500-x053F PMF15B6C

| Address | Name    |        | Bit 7 6 5    |           | 5   | 4                 | 3                  | 2      | 1     | Bit 0   |  |

|---------|---------|--------|--------------|-----------|-----|-------------------|--------------------|--------|-------|---------|--|

| 0x0529  | PMFFQCB | R<br>W |              | LDF       | FQB |                   | HALFB PRSCB PWMRFB |        |       |         |  |

| 0x052A  | PMFCNTB | R<br>W | 0            | 0 PMFCNTB |     |                   |                    |        |       |         |  |

| 0x052B  | PMFCNTB | R<br>W |              | PMFCNTB   |     |                   |                    |        |       |         |  |

| 0x052C  | PMFMODB | R<br>W | 0            | 0 PMFMODB |     |                   |                    |        |       |         |  |

| 0x052D  | PMFMODB | R<br>W |              | PMFMODB   |     |                   |                    |        |       |         |  |

| 0x052E  | PMFDTMB | R<br>W | 0 0 0 0 PMFC |           |     |                   |                    | DTMB   |       |         |  |

| 0x052F  | PMFDTMB | R<br>W |              | PMFDTMB   |     |                   |                    |        |       |         |  |

| 0x0530  | PMFENCC | R<br>W | PWMENC       | GLDOKC    | 0   | 0                 | 0                  | RSTRTC | LDOKC | PWMRIEC |  |

| 0x0531  | PMFFQCC | R<br>W | LDFQC        |           |     |                   | HALFC PRSCC PWMRFC |        |       |         |  |

| 0x0532  | PMFCNTC | R<br>W | 0            | 0         |     |                   |                    |        |       |         |  |

| 0x0533  | PMFCNTC | R<br>W |              | PMFCNTC   |     |                   |                    |        |       |         |  |

| 0x0534  | PMFMODC | R<br>W | 0            | 0 PMFMODC |     |                   |                    |        |       |         |  |

| 0x0535  | PMFMODC | R<br>W | PMFMODC      |           |     |                   |                    |        |       |         |  |

| 0x0536  | PMFDTMC |        | 0            | 0         | 0   | 0                 |                    | PMFD   | DTMC  |         |  |

| 0x0537  | PMFDTMC | R<br>W |              | PMFDTMC   |     |                   |                    |        |       |         |  |

| 0x0538  | PMFDMP0 | R<br>W | DM           | P05       | DM  | DMP04 DMP03 DMP02 |                    | DMP01  | DMP00 |         |  |

| 0x0539  | PMFDMP1 | R<br>W | DM           | P15       | DM  | P14               | DMP13              | DMP12  | DMP11 | DMP10   |  |