# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 9x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-HLQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvml64f1wkh |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.4.2.3 EEPROM

- Up to 1K byte EEPROM

- 16 data bits plus 6 syndrome ECC (error correction code) bits allow single bit error correction and double fault detection

- Erase sector size 4 bytes

- Automated program and erase algorithm

- User margin level setting for reads

## 1.4.2.4 SRAM

- Up to 32 KB of general-purpose RAM with ECC

- Single bit error correction and double bit error detection

## 1.4.3 Clocks, Reset & Power Management Unit (CPMU)

- Real time interrupt (RTI)

- Clock monitor, supervising the correct function of the oscillator (CM)

- Computer operating properly (COP) watchdog

- Configurable as window COP for enhanced failure detection

- Can be initialized out of reset using option bits located in flash memory

- System reset generation

- Autonomous periodic interrupt (API) (combination with cyclic, watchdog)

- Low Power Operation

- RUN mode is the main full performance operating mode with the entire device clocked.

- WAIT mode when the internal CPU clock is switched off, so the CPU does not execute instructions.

- Pseudo STOP system clocks are stopped but the oscillator the RTI, the COP, and API modules can be enabled

- STOP the oscillator is stopped in this mode, all clocks are switched off and all counters and dividers remain frozen, with the exception of the COP and API which can optionally run from ACLK.

## 1.4.3.1 Internal Phase-Locked Loop (IPLL)

- Phase-locked-loop clock frequency multiplier

- No external components required

- Reference divider and multiplier allow large variety of clock rates

- Automatic bandwidth control mode for low-jitter operation

- Automatic frequency lock detector

- Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

- Reference clock sources:

| Port | Pin<br>Name | ZVMC256 | ZVMC128\64 | ZVML128/64/32 | ZVML31 | ZVM32/16 | Pin Function<br>& Priority <sup>1</sup> | I/O | Description                                | Routing<br>Register Bit | Pin Function<br>after Reset |

|------|-------------|---------|------------|---------------|--------|----------|-----------------------------------------|-----|--------------------------------------------|-------------------------|-----------------------------|

| AD   | PAD15       | >       |            |               |        |          | PDOCLK                                  | 0   | DBG profiling clock                        | —                       | GPIO                        |

|      |             | >       |            |               |        |          | AN0_7                                   | Ι   | ADC0 analog input                          | _                       |                             |

|      |             | ~       |            |               |        |          | PTADH[7]/<br>KWADH[7]                   | I/O | General-purpose; with interrupt and wakeup | _                       |                             |

|      | PAD14       | ~       |            |               |        |          | PDO                                     | 0   | DBG profiling data output                  | —                       |                             |

|      |             | >       |            |               |        |          | AN0_6                                   | Ι   | ADC0 analog input                          |                         |                             |

|      |             | •       |            |               |        |          | PTADH[6]/<br>KWADH[6]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

|      | PAD13       | ~       |            |               |        |          | PTURE                                   | 0   | PTU reload event                           | —                       |                             |

|      |             | >       |            |               |        |          | AN0_5                                   | Ι   | ADC0 analog input                          | _                       |                             |

|      |             | •       |            |               |        |          | PTADH[5]/<br>KWADH[5]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

|      | PAD12       | >       |            |               |        |          | AN1_7                                   | Ι   | ADC1 analog input                          | _                       |                             |

|      |             | >       |            |               |        |          | PTADH[4]/<br>KWADH[4]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

|      | PAD11       | ~       |            |               |        |          | AN1_6                                   | Ι   | ADC1 analog input                          | —                       |                             |

|      |             | >       |            |               |        |          | PTADH[3]/<br>KWADH[3]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

|      | PAD10       | >       |            |               |        |          | AN1_5                                   | Ι   | ADC1 analog input                          | _                       |                             |

|      |             | >       |            |               |        |          | PTADH[2]/<br>KWADH[2]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

|      | PAD9        | ~       |            |               |        |          | AN1_4                                   | Ι   | ADC1 analog input                          | —                       |                             |

|      |             | >       |            |               |        |          | PTADH[1]/<br>KWADH[1]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

|      | PAD8        |         | ~          | >             | ~      | ~        | VRH                                     | Ι   | ADC0&1 voltage reference high              | _                       |                             |

|      |             | ~       | ~          | >             | ~      | ~        | AN1_3                                   | Ι   | ADC1 analog input                          | —                       |                             |

|      |             | >       | •          | >             | •      | •        | PTADH[0]/<br>KWADH[0]                   | I/O | General-purpose; with interrupt and wakeup | —                       |                             |

Table 2-4. Port AD Pin Functions and Priorities

| Field          | Description                                                                                                                                                                                                                                                                                                |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PERx7-0 | Pull Enable — Activate pull device on input pin                                                                                                                                                                                                                                                            |

|                | This bit controls whether a pull device on the associated port input or open-drain output pin is active. If a pin is used as push-pull output this bit has no effect. The polarity is selected by the related polarity select register bit. On open-drain output pins only a pullup device can be enabled. |

|                | 1 Pull device enabled<br>0 Pull device disabled                                                                                                                                                                                                                                                            |

#### Table 2-20. Pull Device Enable Register Field Descriptions

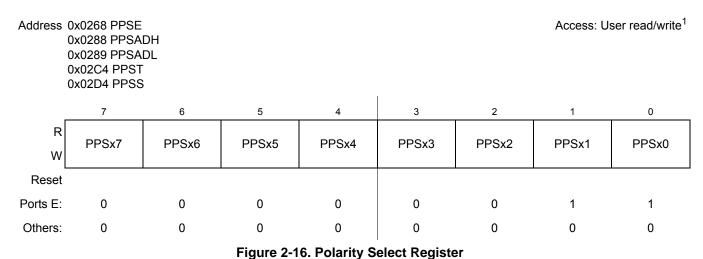

## 2.3.3.5 Polarity Select Register

1. Read: Anytime

5.0

Write: Anytime

This is a generic description of the standard polarity select registers. Refer to Table 2-39 to determine the implemented bits in the respective register. Unimplemented bits read zero.

#### Table 2-21. Polarity Select Register Field Descriptions

| Field          | Description                                                                                                                                                                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>PPSx7-0 | Pull Polarity Select — Configure pull device and pin interrupt edge polarity on input pin                                                                                                                                                                                                                                           |

|                | This bit selects a pullup or a pulldown device if enabled on the associated port input pin.<br>If a port has interrupt functionality this bit also selects the polarity of the active edge.<br>If MSCAN is active a pullup device can be activated on the RXCAN input; attempting to select a pulldown disables<br>the pull-device. |

|                | 1 Pulldown device selected; rising edge selected<br>0 Pullup device selected; falling edge selected                                                                                                                                                                                                                                 |

Chapter 5 Background Debug Controller (S12ZBDCV2)

Active Background

This command is used to exit active BDM and begin (or resume) execution of CPU application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes. If enabled, an ACK is driven on exiting active BDM.

If a GO command is issued whilst the BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

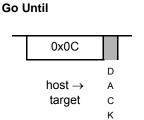

## 5.4.4.8 GO\_UNTIL

This command is used to exit active BDM and begin (or resume) execution of application code. The CPU pipeline is flushed and refilled before normal instruction execution resumes. Prefetching begins at the current address in the PC. If any register (such as the PC) is altered by a BDC command whilst in BDM, the updated value is used when prefetching resumes.

After resuming application code execution, if ACK is enabled, the BDC awaits a return to active BDM before driving an ACK pulse. timeouts do not apply when awaiting a GO\_UNTIL command ACK.

If a GO\_UNTIL is not acknowledged then a SYNC command must be issued to end the pending GO\_UNTIL.

If a GO\_UNTIL command is issued whilst BDM is inactive, an illegal command response is returned and the ILLCMD bit is set.

If ACK handshaking is disabled, the GO\_UNTIL command is identical to the GO command.

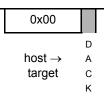

## 5.4.4.9 NOP

Active Background

NOP performs no operation and may be used as a null command where required.

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

## 8.1.3 Modes of Operation

This subsection lists and briefly describes all operating modes supported by the S12CPMU\_UHV\_V10\_V6.

## 8.1.3.1 Run Mode

The voltage regulator is in Full Performance Mode (FPM).

## NOTE

The voltage regulator is active, providing the nominal supply voltages with full current sourcing capability (see also Appendix for VREG electrical parameters). The features ACLK clock source, Low Voltage Interrupt (LVI), Low Voltage Reset (LVR) and Power-On Reset (POR) are available.

The Phase Locked Loop (PLL) is on.

The Internal Reference Clock (IRC1M) is on.

The API is available.

- PLL Engaged Internal (PEI)

- This is the default mode after System Reset and Power-On Reset.

- The Bus Clock is based on the PLLCLK.

- After reset the PLL is configured for 50MHz VCOCLK operation.

Post divider is 0x03, so PLLCLK is VCOCLK divided by 4, that is 12.5MHz and Bus Clock is

- 6.25MHz.

- The PLL can be re-configured for other bus frequencies.

- The reference clock for the PLL (REFCLK) is based on internal reference clock IRC1M.

- PLL Engaged External (PEE)

- The Bus Clock is based on the PLLCLK.

- This mode can be entered from default mode PEI by performing the following steps:

- Configure the PLL for desired bus frequency.

- Program the reference divider (REFDIV[3:0] bits) to divide down oscillator frequency if necessary.

- Enable the external oscillator (OSCE bit).

- Wait for oscillator to start up (UPOSC=1) and PLL to lock (LOCK=1).

- PLL Bypassed External (PBE)

- The Bus Clock is based on the Oscillator Clock (OSCCLK).

- The PLLCLK is always on to qualify the external oscillator clock. Therefore it is necessary to make sure a valid PLL configuration is used for the selected oscillator frequency.

- This mode can be entered from default mode PEI by performing the following steps:

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

## 8.3.2 Register Descriptions

This section describes all the S12CPMU\_UHV\_V10\_V6 registers and their individual bits. Address order is as listed in Figure 8-5

## 8.3.2.1 Reserved Register CPMUVREGTRIM0

#### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV\_V10\_V6's functionality.

Module Base + 0x0001

|                   | 7 | 6 | 5 | 4 | 3 | 2   | 1 | 0 |

|-------------------|---|---|---|---|---|-----|---|---|

| R                 | 0 | 0 | 0 | 0 |   | 1   | 1 |   |

| W                 |   |   |   |   |   | L L | ) |   |

| Reset             | 0 | 0 | 0 | 0 | F | F   | F | F |

| Power<br>on Reset | 0 | 0 | 0 | 0 | 0 | 0   | 0 | 0 |

Note: After de-assert of System Reset a value is automatically loaded from the Flash memory.

Figure 8-6. Reserved Register (CPMUVREGTRIM0)

Read: Anytime

Write: Only in Special Mode

## 8.3.2.2 Reserved Register CPMUVREGTRIM1

#### NOTE

This reserved register is designed for factory test purposes only, and is not intended for general user access. Writing to this register when in Special Mode can alter the S12CPMU\_UHV\_V10\_V6's functionality.

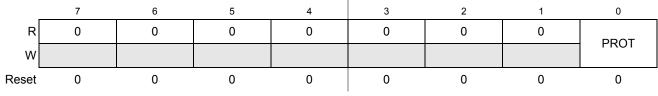

## 8.3.2.25 S12CPMU\_UHV\_V10\_V6 Protection Register (CPMUPROT)

This register protects the clock configuration registers from accidental overwrite:

## CPMUSYNR, CPMUREFDIV, CPMUCLKS, CPMUPLL, CPMUIRCTRIMH/L, CPMUOSC and CPMUOSC2

Module Base + 0x001B

Figure 8-36. S12CPMU\_UHV\_V10\_V6 Protection Register (CPMUPROT)

#### Read: Anytime

Write: Anytime

| Field | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROT  | <ul> <li>Clock Configuration Registers Protection Bit — This bit protects the clock configuration registers from accidental overwrite (see list of protected registers above): Writing 0x26 to the CPMUPROT register clears the PROT bit, other write accesses set the PROT bit.</li> <li>Protection of clock configuration registers is disabled.</li> <li>Protection of clock configuration registers is enabled. (see list of protected registers above).</li> </ul> |

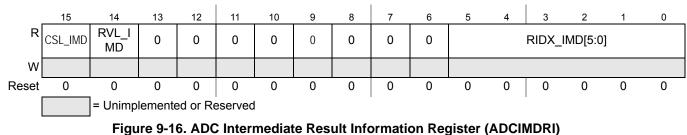

## 9.5.2.13 ADC Intermediate Result Information Register (ADCIMDRI)

This register is cleared when bit ADC\_SR is set or bit ADC\_EN is clear.

Module Base + 0x000E

Read: Anytime

Write: Never

| Field                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15<br>CSL_IMD        | <ul> <li>Active CSL At Intermediate Event — This bit indicates the active (used) CSL at the occurrence of a conversion interrupt flag (CON_IF[15:1]) (occurrence of an intermediate result buffer fill event) or when a Sequence Abort Event gets executed.</li> <li>0 CSL_0 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.</li> <li>1 CSL_1 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                |

| 14<br>RVL_IMD        | <ul> <li>Active RVL At Intermediate Event — This bit indicates the active (used) RVL buffer at the occurrence of a conversion interrupt flag (CON_IF[15:1]) (occurrence of an intermediate result buffer fill event) or when a Sequence Abort Event gets executed.</li> <li>0 RVL_0 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.</li> <li>1 RVL_1 active (used) when a conversion interrupt flag (CON_IF[15:1]) got set.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                         |

| 5-0<br>RIDX_IMD[5:0] | <b>RES_IDX Value At Intermediate Event</b> — These bits indicate the result index (RES_IDX) value at the occurrence of a conversion interrupt flag (CON_IF[15:1]) (occurrence of an intermediate result buffer fill event) or occurrence of EOL_IF flag or when a Sequence Abort Event gets executed to abort an ongoing conversion (the result index RES_IDX is captured at the occurrence of a result data store).                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                      | <ul> <li>When a Sequence Abort Event has been processed flag SEQAD_IF is set and the RES_IDX value of the last stored result is provided. Hence in case an ongoing conversion is aborted the RES_IDX value captured in RIDX_IMD bits depends on bit STORE_SEQA:</li> <li>STORE_SEQA =1: The result index of the aborted conversion is provided</li> <li>STORE_SEQA =0: The result index of the last stored result at abort execution time is provided</li> <li>In case a CSL is aborted while no conversion is ongoing (ADC waiting for a Trigger Event) the last captured result index is provided.</li> <li>In case a Sequence Abort Event was initiated by hardware due to MCU entering Stop Mode or Wait Mode with bit SWAI set, the result index of the last stored result is captured by bits RIDX_IMD but flag SEQAD_IF is not set.</li> </ul> |

#### Table 9-18. ADCIMDRI Field Descriptions

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>TSFRZ | <ul> <li>Timer Stops While in Freeze Mode</li> <li>Allows the timer counter to continue running while in freeze mode.</li> <li>Disables the timer counter whenever the MCU is in freeze mode. This is useful for emulation.</li> <li>TSFRZ does not stop the pulse accumulator.</li> </ul>                                                                                                                                                                                                                                                                    |

| 4<br>TFFCA | <ul> <li>Timer Fast Flag Clear All</li> <li>Allows the timer flag clearing to function normally.</li> <li>For TFLG1(0x000E), a read from an input capture or a write to the output compare channel (0x0010–0x001F) causes the corresponding channel flag, CnF, to be cleared. For TFLG2 (0x000F), any access to the TCNT register (0x0004, 0x0005) clears the TOF flag. This has the advantage of eliminating software overhead in a separate clear sequence. Extra care is required to avoid accidental flag clearing due to unintended accesses.</li> </ul> |

| 3<br>PRNT  | <ul> <li>Precision Timer</li> <li>0 Enables legacy timer. PR0, PR1, and PR2 bits of the TSCR2 register are used for timer counter prescaler selection.</li> <li>1 Enables precision timer. All bits of the PTPSR register are used for Precision Timer Prescaler Selection, and all bits.</li> <li>This bit is writable only once out of reset.</li> </ul>                                                                                                                                                                                                    |

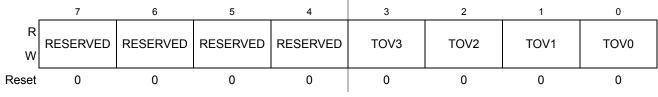

## 11.3.2.5 Timer Toggle On Overflow Register 1 (TTOV)

Module Base + 0x0007

Figure 11-9. Timer Toggle On Overflow Register 1 (TTOV)

#### Read: Anytime

Write: Anytime

#### Table 11-5. TTOV Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field           | Description                                                                                                                                                                                                                                                                                                                                      |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3:0<br>TOV[3:0] | <ul> <li>Toggle On Overflow Bits — TOVx toggles output compare pin on overflow. This feature only takes effect when in output compare mode. When set, it takes precedence over forced output compare</li> <li>Toggle output compare pin on overflow feature disabled.</li> <li>Toggle output compare pin on overflow feature enabled.</li> </ul> |

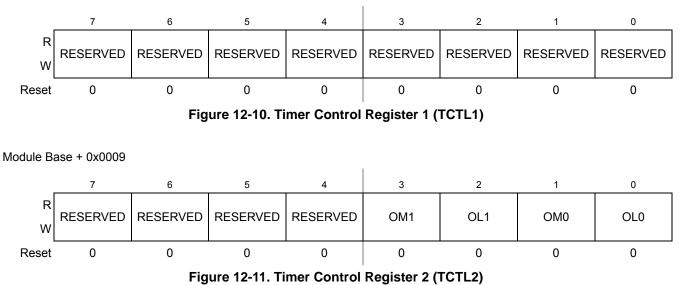

## 12.3.2.6 Timer Control Register 1/Timer Control Register 2 (TCTL1/TCTL2)

Module Base + 0x0008

Read: Anytime

Write: Anytime

#### Table 12-6. TCTL1/TCTL2 Field Descriptions

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero

| Field      | Description                                                                                                                                                                                                                                                                                                        |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0<br>OMx | Output Mode — These two pairs of control bits are encoded to specify the output action to be taken as a result<br>of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output<br>tied to OCx.Note:For an output line to be driven by an OCx the OCPDx must be cleared. |

| 1:0<br>OLx | Output Level — These two pairs of control bits are encoded to specify the output action to be taken as a result of a successful OCx compare. When either OMx or OLx is 1, the pin associated with OCx becomes an output tied to OCx.<br>Note: For an output line to be driven by an OCx the OCPDx must be cleared. |

| Table 12-7. Compare Result Output Action |

|------------------------------------------|

|------------------------------------------|

| ОМх | OLx | Action                                                 |

|-----|-----|--------------------------------------------------------|

| 0   | 0   | No output compare<br>action on the timer output signal |

| 0   | 1   | Toggle OCx output line                                 |

| 1   | 0   | Clear OCx output line to zero                          |

| 1   | 1   | Set OCx output line to one                             |

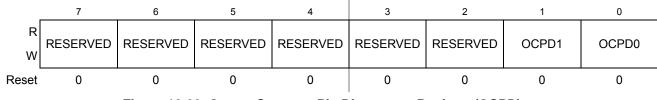

## 12.3.2.13 Output Compare Pin Disconnect Register(OCPD)

Module Base + 0x002C

#### Figure 12-20. Output Compare Pin Disconnect Register (OCPD)

#### Read: Anytime

Write: Anytime

All bits reset to zero.

#### Table 12-15. OCPD Field Description

Note: Writing to unavailable bits has no effect. Reading from unavailable bits return a zero.

| Field   | Description                                                                                                                                                                                                                                                                 |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1:0     | Output Compare Pin Disconnect Bits                                                                                                                                                                                                                                          |

| OCPD[1: | <ul> <li>0 Enables the timer channel port. Output Compare action will occur on the channel pin. These bits do not affect the input capture .</li> <li>1 Disables the timer channel port. Output Compare action will not occur on the channel pin, but the output</li> </ul> |

|         | compare flag still become set.                                                                                                                                                                                                                                              |

## 12.3.2.14 Precision Timer Prescaler Select Register (PTPSR)

Module Base + 0x002E

| _     | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| R     | PTPS7 | PTPS6 | PTPS5 | PTPS4 | PTPS3 | PTPS2 | PTPS1 | PTPS0 |

| w     | FIF3/ | FIF30 | FIFOD | F1F34 | FIF33 | FIF32 | FIFSI | FIFOU |

| Reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

Read: Anytime

Write: Anytime

All bits reset to zero.

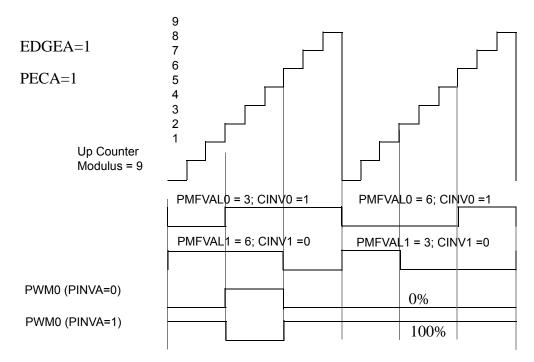

Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

Figure 15-64. Variable Edge Placement Waveform - Phase Shift PWM Output (Edge-Aligned)

## 15.4.9 Double Switching PWM Output

By using the AND function in Figure 15-63 in complementary center-aligned mode, the PWM output can be configured for double switching operation (Figure 15-65, Figure 15-66). By setting the non-inverted value register greater or equal to the PWM modulus the output function can be switched to single pulse generation on PWM reload cycle basis.

When transmitting in 9-bit data format and using 8-bit write instructions, write first to SCI data register high (SCIDRH), then SCIDRL.

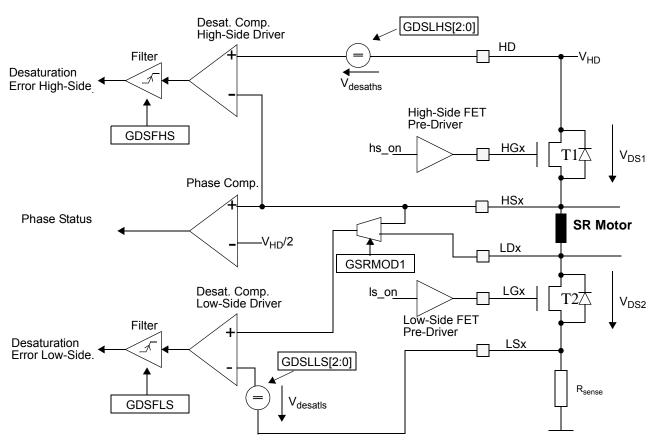

## 18.4.6 Phase Comparators

The GDU module includes three phase comparators. The phase comparators compares the voltage on the HS[2:0] pins with one half voltage on HD pin. If  $V_{HSx}$  is greater than 0.5  $V_{HD}$  the associated phase status bit GPHS[2:0] is set. (see Figure 18-7) If the  $V_{HSx}$  is less than 0.5  $V_{HD}$  the associated phase status bit GPHS[2:0] is cleared. If a desaturation error is detected the state of the phase status bit GPHS[2:0] are copied to the GDUPHL register. The phase flags get unlocked when the associated desaturation interrupt flag is cleared.

1. LDx pins and the routing option of HSx or LDx to the desaturation comparator of the low-side driver controlled by GSRMOD1 is only available on GDUV6.

## Chapter 19 LIN/HV Physical Layer (S12LINPHYV3)

| Rev. No.<br>(Item No.) | Date<br>(Submitted By) | Sections<br>Affected                                                 | Substantial Change(s)                                                                                      |  |

|------------------------|------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--|

| V02.09                 | 27 Jun 2013            | Feature list                                                         | - Added the SAE J2602-2 LIN compliance.                                                                    |  |

| V02.10                 | 21 Aug 2013            | Overcurrent and<br>TxD-dominant<br>timeout interrupt<br>descriptions | - Specified the time after which the interrupt flags are set again after having                            |  |

| V02.11                 | 19 Sep 2013            | All                                                                  | <ul> <li>Removed preliminary note.</li> <li>Fixed grammar and spelling throughout the document.</li> </ul> |  |

| V02.12                 | 20 Sep 2013            | Standby Mode                                                         | e - Clarified Standby mode behavior.                                                                       |  |

| V02.13                 | 8 Oct 2013             | All                                                                  | - More grammar, spelling, and formating fixes throughout the document.                                     |  |

| V03.01                 | 08 May 2014            | All                                                                  | - Added HV PHY feature.                                                                                    |  |

Table 19-1. Revision History Table

## 19.1 Introduction

# This chapter provides information for both the LIN physical interface and the HV interface. Devices may include either a LINPHY or HVPHY module. The device overview section specifies the LINPHY/HVPHY to device mapping.

The LIN (Local Interconnect Network) bus pin provides a physical layer for single-wire communication in automotive applications. The LIN Physical Layer is designed to meet the LIN Physical Layer 2.2 specification from LIN consortium.

The HV physical interface provides a physical layer for single-wire communication. It can be used, among other examples, for PWM applications since it can be connected to an internal timer.

## NOTE

All references to LIN (e.g. names of bits, registers, signals, pins, interrupts, etc.) apply to the HV physical interface as well. The same names have been kept to highlight and facilitate the hardware and software compatibility between both versions. Nevertheless, cases where particular LIN features do not apply to the HV physical interface version are specifically mentioned.

#### Chapter 19 LIN/HV Physical Layer (S12LINPHYV3)

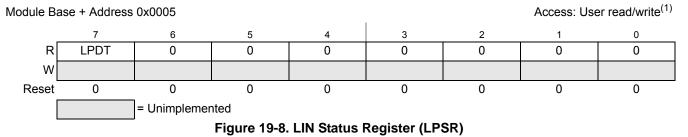

## 19.3.2.6 LIN Status Register (LPSR)

#### 1. Read: Anytime

Write: Never, writes to this register have no effect

#### Table 19-7. LPSR Field Description

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LPDT | <ul> <li>LIN Transmitter TxD-dominant timeout Status Bit — This read-only bit signals that the LPTxD pin is still dominant after a TxD-dominant timeout. As long as the LPTxD is dominant after the timeout the LIN transmitter is shut down and the LPTDIF is set again after attempting to clear it.</li> <li>If there was a TxD-dominant timeout, LPTxD has ceased to be dominant after the timeout.</li> <li>LPTxD is still dominant after a TxD-dominant timeout.</li> </ul> |

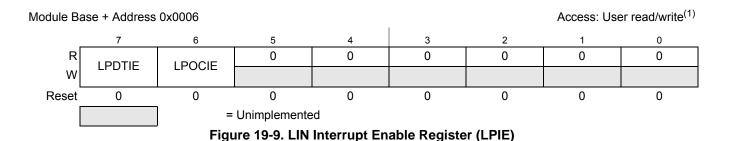

## **19.3.2.7** LIN Interrupt Enable Register (LPIE)

1. Read: Anytime

Write: Anytime

The FCLKDIV register should never be written while a Flash command is executing (CCIF=0).

| Field            | Description                                                                                                                                                                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>FDIVLD      | Clock Divider Loaded<br>0 FCLKDIV register has not been written since the last reset<br>1 FCLKDIV register has been written since the last reset                                                                                                                                                                                   |

| 6<br>FDIVLCK     | <ul> <li>Clock Divider Locked</li> <li>FDIV field is open for writing</li> <li>FDIV value is locked and cannot be changed. Once the lock bit is set high, only reset can clear this bit and restore writability to the FDIV field in normal mode.</li> </ul>                                                                       |

| 5–0<br>FDIV[5:0] | <b>Clock Divider Bits</b> — FDIV[5:0] must be set to effectively divide BUSCLK down to 1 MHz to control timed events during Flash program and erase algorithms. Table 20-8 shows recommended values for FDIV[5:0] based on the BUSCLK frequency. Please refer to Section 20.4.5, "Flash Command Operations," for more information. |

#### Table 20-7. FCLKDIV Field Descriptions

| BUSCLK Frequency<br>(MHz) |                    | FDIV[5:0] |  | BUSCLK<br>(M     | FDIV[5:0]        |      |

|---------------------------|--------------------|-----------|--|------------------|------------------|------|

| MIN <sup>(1)</sup>        | MAX <sup>(2)</sup> |           |  | MIN <sup>1</sup> | MAX <sup>2</sup> |      |

| 1.0                       | 1.6                | 0x00      |  | 26.6             | 27.6             | 0x1A |

| 1.6                       | 2.6                | 0x01      |  | 27.6             | 28.6             | 0x1B |

| 2.6                       | 3.6                | 0x02      |  | 28.6             | 29.6             | 0x1C |

| 3.6                       | 4.6                | 0x03      |  | 29.6             | 30.6             | 0x1D |

| 4.6                       | 5.6                | 0x04      |  | 30.6             | 31.6             | 0x1E |

| 5.6                       | 6.6                | 0x05      |  | 31.6             | 32.6             | 0x1F |

| 6.6                       | 7.6                | 0x06      |  | 32.6             | 33.6             | 0x20 |

| 7.6                       | 8.6                | 0x07      |  | 33.6             | 34.6             | 0x21 |

| 8.6                       | 9.6                | 0x08      |  | 34.6             | 35.6             | 0x22 |

| 9.6                       | 10.6               | 0x09      |  | 35.6             | 36.6             | 0x23 |

| 10.6                      | 11.6               | 0x0A      |  | 36.6             | 37.6             | 0x24 |

| 11.6                      | 12.6               | 0x0B      |  | 37.6             | 38.6             | 0x25 |

| 12.6                      | 13.6               | 0x0C      |  | 38.6             | 39.6             | 0x26 |

| 13.6                      | 14.6               | 0x0D      |  | 39.6             | 40.6             | 0x27 |

| 14.6                      | 15.6               | 0x0E      |  | 40.6             | 41.6             | 0x28 |

| 15.6                      | 16.6               | 0x0F      |  | 41.6             | 42.6             | 0x29 |

| 16.6                      | 17.6               | 0x10      |  | 42.6             | 43.6             | 0x2A |

| 17.6                      | 18.6               | 0x11      |  | 43.6             | 44.6             | 0x2B |

#### Table 20-8. FDIV values for various BUSCLK Frequencies

Chapter 20 Flash Module (S12ZFTMRZ)

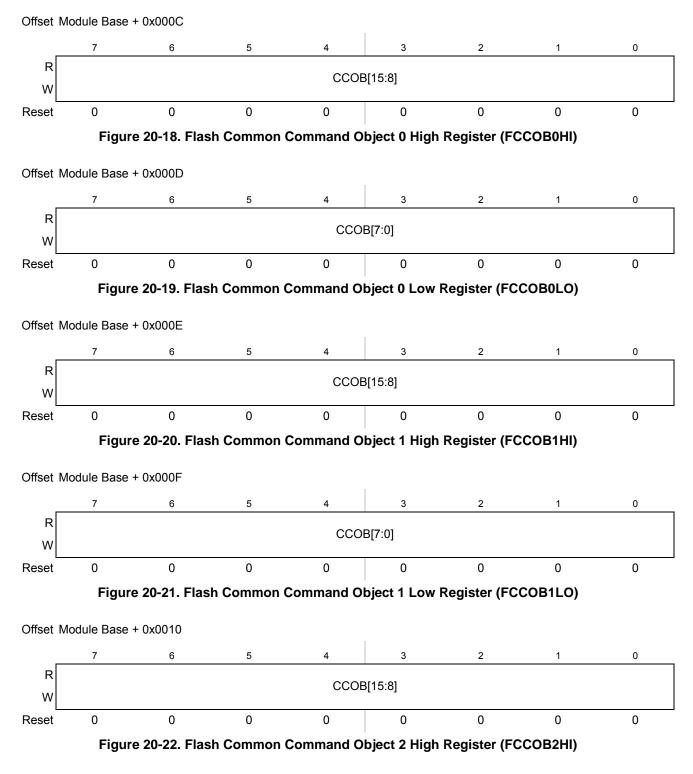

## 20.3.2.13 Flash Common Command Object Registers (FCCOB)

The FCCOB is an array of six words. Byte wide reads and writes are allowed to the FCCOB registers.

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          | ACCERR    | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          |           | Set if command not available in current mode (see Table 20-29)                      |

|          |           | Set if an invalid global address [23:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 20-65. Program EEPROM Command Error Handling

## 20.4.7.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

Table 20-66. Erase EEPROM Sector Command FCCOB Requirements

| Register | FCCOB Parameters                                                                                               |                                                    |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| FCCOB0   | 0x12                                                                                                           | Global address [23:16] to identify<br>EEPROM block |  |  |  |

| FCCOB1   | Global address [15:0] anywhere within the sector to be erased.<br>See Section 20.1.2.2 for EEPROM sector size. |                                                    |  |  |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|

|          | ACCERR    | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |

|          |           | Set if command not available in current mode (see Table 20-29)                      |  |  |

|          |           | Set if an invalid global address [23:0] is supplied see Table 20-3                  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |

Table 20-67. Erase EEPROM Sector Command Error Handling

## Appendix F NVM Electrical Parameters

## F.1 NVM Timing Parameters

The time base for all NVM program or erase operations is derived from the bus clock using the FCLKDIV register. The frequency of this derived clock must be set within the limits specified as  $f_{NVMOP}$ . The NVM module does not have any means to monitor the frequency and will not prevent program or erase operation at frequencies above or below the specified minimum. When attempting to program or erase the NVM module at a lower frequency, a full program or erase transition is not assured.

The device bus frequency, below which the flash wait states can be disabled,  $f_{WSTAT}$ , is specified in the device operating conditions table in Table A-6.

The following sections provide equations which can be used to determine the time required to execute specific flash commands. All timing parameters are a function of the bus clock frequency,  $f_{NVMBUS}$ . All program and erase times are also a function of the NVM operating frequency,  $f_{NVMOP}$

Timing parameters for the ZVMC128, ZVML128, ZVMC64, ZVML64 and ZVML32 devices are specified in Table F-1 and Table F-2.

Timing parameters for the ZVML31, ZVM32 and ZVM16 are specified in Table F-3 and Table F-4.

Timing parameters for the ZVMC256 are specified in Table F-5