#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 50MHz                                                                    |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 31                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                               |

| Data Converters            | A/D 9x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP Exposed Pad                                                      |

| Supplier Device Package    | 64-HLQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvml64f2mkhr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 22.6 | Interrupts |  | 87 | 3 |

|------|------------|--|----|---|

|------|------------|--|----|---|

### Appendix A MCU Electrical Specifications

| A.1 | General                             | . 875 |

|-----|-------------------------------------|-------|

| A.2 | General Purpose I/O Characteristics | . 888 |

| A.3 | Supply Currents                     | . 890 |

| A.4 | ADC Calibration Configuration       | . 893 |

## Appendix B

## **CPMU Electrical Specifications (VREG, OSC, IRC, PLL)**

| <b>B</b> .1 | VREG Electrical Specifications        | 895   |

|-------------|---------------------------------------|-------|

| B.2         | Reset and Stop Timing Characteristics | 897   |

| B.3         | IRC and OSC Electrical Specifications | 898   |

| <b>B</b> .4 | Phase Locked Loop                     | . 898 |

## Appendix C ADC Electrical Specifications

| C.1 | ADC Operating Characteristics | 901 |

|-----|-------------------------------|-----|

|-----|-------------------------------|-----|

# Appendix D

## **LIN/HV PHY Electrical Specifications**

| D.1 | Static Electrical Characteristics. | 907 |

|-----|------------------------------------|-----|

| D.2 | Dynamic Electrical Characteristics | 908 |

# Appendix E

### **GDU Electrical Specifications**

| E.1 | GDU specifications for devices featuring GDU V4 or V6       | 911 |

|-----|-------------------------------------------------------------|-----|

| E.2 | Preliminary GDU specifications for devices featuring GDU V5 | 914 |

# Appendix F

## **NVM Electrical Parameters**

| F.1 | NVM Timing Parameters          | . 919 |

|-----|--------------------------------|-------|

| F.2 | NVM Reliability Parameters     | . 926 |

| F.3 | NVM Factory Shipping Condition | . 926 |

## Appendix G BATS Electrical Specifications

| G.1 | Static Electrical Characteristics  | 927 |

|-----|------------------------------------|-----|

| G.2 | Dynamic Electrical Characteristics | 928 |

| Address            | Module                                                    | Size<br>(Bytes) |

|--------------------|-----------------------------------------------------------|-----------------|

| 0x06E0-0x06EF      | Reserved                                                  | 16              |

| 0x06F0-0x06F7      | BATS                                                      | 8               |

| 0x06F8-0x06FF      | Reserved                                                  | 8               |

| 0x0700–0x0707      | SCI0                                                      | 8               |

| 0x0708–0x070F      | Reserved                                                  | 8               |

| 0x0710–0x0717      | SCI1                                                      | 8               |

| 0x0718–0x077F      | Reserved                                                  | 104             |

| 0x0780–0x0787 SPI0 |                                                           | 8               |

| 0x0788–0x07FF      | Reserved                                                  | 120             |

| 0x0800-0x083F      | CAN0                                                      | 64              |

| 0x0840–0x097F      | Reserved                                                  | 320             |

| 0x0980-0x0987      | LINPHY (S12ZVML derivatives)                              | 8               |

| 0x0980–0x0987      | HV Physical Interface<br>(S12ZVM32, S12ZVM16 derivatives) | 8               |

| 0x0988–0x098F      | Reserved                                                  | 8               |

| 0x0990-0x0997      | CANPHY (ZVMC256 only)                                     | 8               |

| 0x0998-0x0FFF      | Reserved                                                  | 1640            |

#### Table 1-5. Module Register Address Ranges

1. Reading from the first 16 locations in this reserved range returns undefined data

2. Address range = 0x0690-0x069F on Maskset N06E

### NOTE

Reserved register space shown above is not allocated to any module. This register space is reserved for future use. Writing to these locations has no effect. Read access to these locations returns zero.

### 1.6.1 Flash Module

This device family instantiates different flash modules, depending on derivative. The flash documentation for the all devices is featured in the FTMRZ section.

#### Chapter 4 Interrupt (S12ZINTV0)

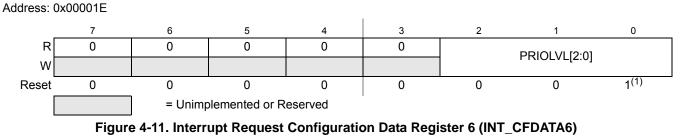

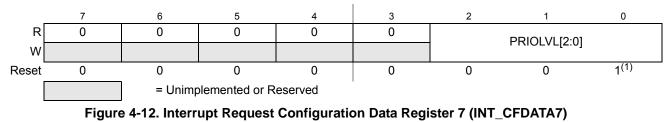

1. Please refer to the notes following the PRIOLVL[2:0] description below.

#### Address: 0x00001F

1. Please refer to the notes following the PRIOLVL[2:0] description below.

### Read: Anytime

Write: Anytime

#### Table 4-6. INT\_CFDATA0-7 Field Descriptions

| Field               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 2–0<br>PRIOLVL[2:0] | <ul> <li>Interrupt Request Priority Level Bits — The PRIOLVL[2:0] bits configure the interrupt request priority level of the associated interrupt request. Out of reset all interrupt requests are enabled at the lowest active level ("1"). Please also refer to Table 4-7 for available interrupt request priority levels.</li> <li>Note: Write accesses to configuration data registers of unused interrupt channels are ignored and read accesses return all 0s. For information about what interrupt channels are used in a specific MCU, please refer to the Device Reference Manual for that MCU.</li> </ul> |  |  |  |

|                     | Note: When non I-bit maskable request vectors are selected, writes to the corresponding INT_CFDATA registers are ignored and read accesses return all 0s. The corresponding vectors do not have configuration data registers associated with them.                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                     | Note: Write accesses to the configuration register for the spurious interrupt vector request (vector base + 0x0001DC) are ignored and read accesses return 0x07 (request is handled by the CPU, PRIOLVL = 7).                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Table 4-7. | Interrupt | Priority | v Levels |

|------------|-----------|----------|----------|

|            | micriupi  | THOM     |          |

| Priority | PRIOLVL2 | PRIOLVL1 | PRIOLVL0 | Meaning                       |  |

|----------|----------|----------|----------|-------------------------------|--|

|          | 0        | 0        | 0        | Interrupt request is disabled |  |

| low      | 0        | 0        | 1        | Priority level 1              |  |

|          | 0        | 1        | 0        | Priority level 2              |  |

|          | 0        | 1        | 1        | Priority level 3              |  |

| Field      | Description                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PORF  | <ul> <li>Power on Reset Flag — PORF is set to 1 when a power on reset occurs. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Power on reset has not occurred.</li> <li>1 Power on reset has occurred.</li> </ul>                                                                                                                                                            |

| 5<br>LVRF  | <ul> <li>Low Voltage Reset Flag — LVRF is set to 1 when a low voltage reset occurs on the VDD, VDDF or VDDX domain. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Low voltage reset has not occurred.</li> <li>1 Low voltage reset has occurred.</li> </ul>                                                                                                                |

| 3<br>COPRF | <ul> <li>COP Reset Flag — COPRF is set to 1 when a COP (Computer Operating Properly) reset occurs. Refer to 8.5.5, "Computer Operating Properly Watchdog (COP) Reset and 8.3.2.12, "S12CPMU_UHV_V10_V6 COP Control Register (CPMUCOP) for details. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 COP reset has not occurred.</li> <li>1 COP reset has occurred.</li> </ul> |

| 1<br>OMRF  | Oscillator Clock Monitor Reset Flag — OMRF is set to 1 when a loss of oscillator (crystal) clock occurs. Refer to8.5.3, "Oscillator Clock Monitor Reset for details. This flag can only be cleared by writing a 1. Writing a 0 has no effect.<br>0 Loss of oscillator clock reset has not occurred.<br>1 Loss of oscillator clock reset has occurred.                                                            |

| 0<br>PMRF  | <ul> <li>PLL Clock Monitor Reset Flag — PMRF is set to 1 when a loss of PLL clock occurs. This flag can only be cleared by writing a 1. Writing a 0 has no effect.</li> <li>0 Loss of PLL clock reset has not occurred.</li> <li>1 Loss of PLL clock reset has occurred.</li> </ul>                                                                                                                              |

### Table 8-2. CPMURFLG Field Descriptions

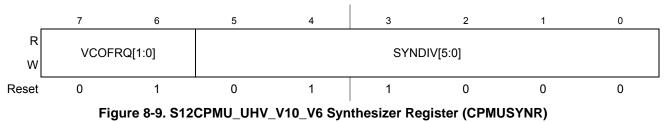

## 8.3.2.4 S12CPMU\_UHV\_V10\_V6 Synthesizer Register (CPMUSYNR)

The CPMUSYNR register controls the multiplication factor of the PLL and selects the VCO frequency range.

Module Base + 0x0004

### Read: Anytime

Write: If PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register), then write anytime. Else write has no effect.

### NOTE

Writing to this register clears the LOCK and UPOSC status bits.

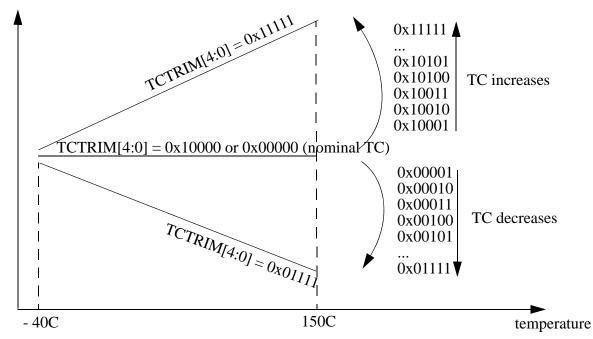

Figure 8-34. Influence of TCTRIM[4:0] on the Temperature Coefficient

### NOTE

The frequency is not necessarily linear with the temperature (in most cases it will not be). The above diagram is meant only to give the direction (positive or negative) of the variation of the TC, relative to the nominal TC.

Setting TCTRIM[4:0] at 0x00000 or 0x10000 does not mean that the temperature coefficient will be zero. These two combinations basically switch off the TC compensation module, which results in the nominal TC of the IRC1M.

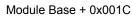

## 9.5.2.19 ADC Command Index Register (ADCCIDX)

It is important to note that these bits do not represent absolute addresses instead it is a sample index (object size 32bit).

Read: Anytime

Write: NA

| Field                   | Description                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-0<br>CMD_IDX<br>[5:0] | ADC Command Index Bits — These bits represent the command index value for the conversion commands relative to the two CSL start addresses in the memory map. These bits do not represent absolute addresses instead it is a sample index (object size 32bit). See also Section 9.6.3.2.2, "Introduction of the two Command Sequence Lists (CSLs) for more details. |

# 11.2 External Signal Description

The TIM16B4CV3 module has a selected number of external pins. Refer to device specification for exact number.

# 11.2.1 IOC3 - IOC0 — Input Capture and Output Compare Channel 3-0

Those pins serve as input capture or output compare for TIM16B4CV3 channel.

### NOTE

For the description of interrupts see Section 11.6, "Interrupts".

# 11.3 Memory Map and Register Definition

This section provides a detailed description of all memory and registers.

## 11.3.1 Module Memory Map

The memory map for the TIM16B4CV3 module is given below in Figure 11-3. The address listed for each register is the address offset. The total address for each register is the sum of the base address for the TIM16B4CV3 module and the address offset for each register.

## 11.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order.

| Register<br>Name |        | Bit 7        | 6            | 5            | 4            | 3      | 2      | 1      | Bit 0  |

|------------------|--------|--------------|--------------|--------------|--------------|--------|--------|--------|--------|

| 0x0000<br>TIOS   | R<br>W | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | IOS3   | IOS2   | IOS1   | IOS0   |

| 0x0001           | R      | 0            | 0            | 0            | 0            | 0      | 0      | 0      | 0      |

| CFORC            | W      | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | FOC3   | FOC2   | FOC1   | FOC0   |

| 0x0004<br>TCNTH  | R<br>W | TCNT15       | TCNT14       | TCNT13       | TCNT12       | TCNT11 | TCNT10 | TCNT9  | TCNT8  |

| 0x0005<br>TCNTL  | R<br>W | TCNT7        | TCNT6        | TCNT5        | TCNT4        | TCNT3  | TCNT2  | TCNT1  | TCNT0  |

| 0x0006           | R      | TEN          | TSWAI        | TSFRZ        | TFFCA        | PRNT   | 0      | 0      | 0      |

| TSCR1            | W      |              | IOWAI        | 101112       | IIIOA        |        |        |        |        |

| 0x0007<br>TTOV   | R<br>W | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | RESERV<br>ED | TOV3   | TOV2   | TOV1   | TOV0   |

| 0x0008           | R      | RESERV       | RESERV       | RESERV       | RESERV       | RESERV | RESERV | RESERV | RESERV |

| TCTL1            | W      | ED           | ED           | ED           | ED           | ED     | ED     | ED     | ED     |

Only bits related to implemented channels are valid.

Figure 11-3. TIM16B4CV3 Register Summary (Sheet 1 of 2)

| Offset<br>Address | Register                                                |     |  |  |  |

|-------------------|---------------------------------------------------------|-----|--|--|--|

| 0x00X0            | IDR0 — Identifier Register 0                            | R/W |  |  |  |

| 0x00X1            | IDR1 — Identifier Register 1                            | R/W |  |  |  |

| 0x00X2            | IDR2 — Identifier Register 2                            | R/W |  |  |  |

| 0x00X3            | IDR3 — Identifier Register 3                            | R/W |  |  |  |

| 0x00X4            | DSR0 — Data Segment Register 0                          | R/W |  |  |  |

| 0x00X5            | DSR1 — Data Segment Register 1                          | R/W |  |  |  |

| 0x00X6            | DSR2 — Data Segment Register 2                          | R/W |  |  |  |

| 0x00X7            | DSR3 — Data Segment Register 3                          | R/W |  |  |  |

| 0x00X8            | DSR4 — Data Segment Register 4                          | R/W |  |  |  |

| 0x00X9            | DSR5 — Data Segment Register 5                          | R/W |  |  |  |

| 0x00XA            | DSR6 — Data Segment Register 6                          | R/W |  |  |  |

| 0x00XB            | DSR7 — Data Segment Register 7                          | R/W |  |  |  |

| 0x00XC            | DLR — Data Length Register                              | R/W |  |  |  |

| 0x00XD            | TBPR — Transmit Buffer Priority Register <sup>(1)</sup> | R/W |  |  |  |

| 0x00XE            | TSRH — Time Stamp Register (High Byte)                  | R   |  |  |  |

| 0x00XF            | TSRL — Time Stamp Register (Low Byte)                   | R   |  |  |  |

1. Not applicable for receive buffers

Figure 13-24 shows the common 13-byte data structure of receive and transmit buffers for extended identifiers. The mapping of standard identifiers into the IDR registers is shown in Figure 13-25.

All bits of the receive and transmit buffers are 'x' out of reset because of RAM-based implementation<sup>1</sup>. All reserved or unused bits of the receive and transmit buffers always read 'x'.

1. Exception: The transmit buffer priority registers are 0 out of reset.

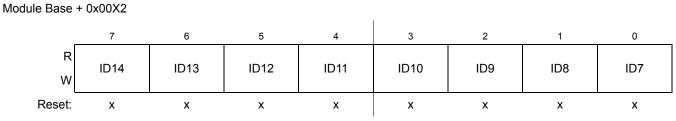

Figure 13-28. Identifier Register 2 (IDR2) — Extended Identifier Mapping

| Table 13-28. | IDR2 Register | Field Descr | iptions — Ex | tended |

|--------------|---------------|-------------|--------------|--------|

|              |               |             |              |        |

| Field           | Description                                                                                                                                                                                                                                                                                                  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0<br>ID[14:7] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number. |

#### Module Base + 0x00X3

|        | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|--------|-----|-----|-----|-----|-----|-----|-----|-----|

| R<br>W | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | RTR |

| Reset: | х   | x   | х   | x   | х   | х   | х   | x   |

Figure 13-29. Identifier Register 3 (IDR3) — Extended Identifier Mapping

#### Table 13-29. IDR3 Register Field Descriptions — Extended

| Field          | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-1<br>ID[6:0] | <b>Extended Format Identifier</b> — The identifiers consist of 29 bits (ID[28:0]) for the extended format. ID28 is the most significant bit and is transmitted first on the CAN bus during the arbitration procedure. The priority of an identifier is defined to be highest for the smallest binary number.                                                                                                                      |

| 0<br>RTR       | <ul> <li>Remote Transmission Request — This flag reflects the status of the remote transmission request bit in the CAN frame. In the case of a receive buffer, it indicates the status of the received frame and supports the transmission of an answering frame in software. In the case of a transmit buffer, this flag defines the setting of the RTR bit to be sent.</li> <li>0 Data frame</li> <li>1 Remote frame</li> </ul> |

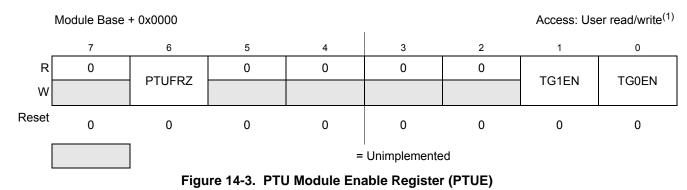

# 14.3.2.1 PTU Module Enable Register (PTUE)

<sup>1.</sup> Read: Anytime

Write: Anytime

#### Table 14-3. PTUE Register Field Description

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6<br>PTUFRZ | <ul> <li>PTU Stop in Freeze Mode — In freeze mode, there is an option to disable the input clock to the PTU time base counter. If this bit is set, whenever the MCU is in freeze mode, the input clock to the time base counter is disabled. In this way, the counters can be stopped while in freeze mode so that once normal program flow is continued, the counter is re-enabled.</li> <li>0 Allow time base counter to continue while in freeze mode</li> <li>1 Disable time base counter clock whenever the part is in freeze mode</li> </ul> |

| 1<br>TG1EN  | <ul> <li>Trigger Generator 1 Enable — This bit enables trigger generator 1.</li> <li>0 Trigger generator 1 is disabled</li> <li>1 Trigger generator 1 is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

| 0<br>TG0EN  | <ul> <li>Trigger Generator 0 Enable — This bit enables trigger generator 0.</li> <li>0 Trigger generator 0 is disabled</li> <li>1 Trigger generator 0 is enabled</li> </ul>                                                                                                                                                                                                                                                                                                                                                                        |

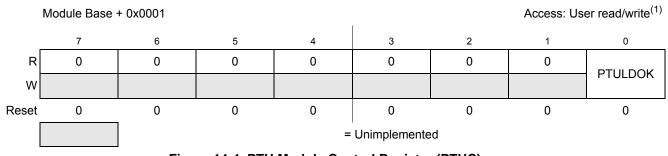

# 14.3.2.2 PTU Module Control Register (PTUC)

#### Figure 14-4. PTU Module Control Register (PTUC)

1. Read: Anytime

Write: write 1 anytime, write 0 if TG0EN and TG1EN is cleared

Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

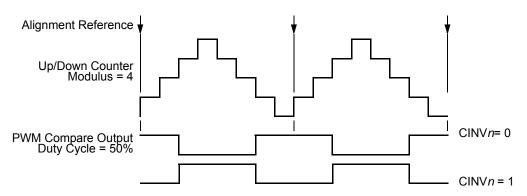

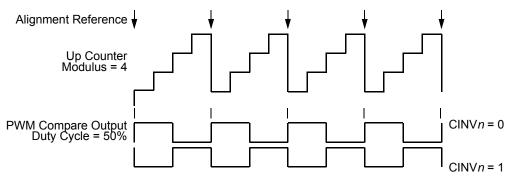

Figure 15-42. Center-Aligned PWM Output

Figure 15-43. Edge-Aligned PWM Output

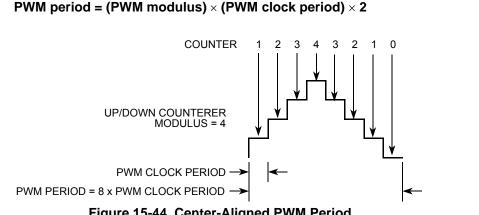

#### 15.4.3.2 Period

A PWM period is determined by the value written to the PWM counter modulo registers PMFMODx.

The PWM counter is an up/down counter in center-aligned mode. In this mode the PWM highest output resolution is two core clock cycles.

Figure 15-44. Center-Aligned PWM Period

MC9S12ZVM Family Reference Manual Rev. 2.11

Eqn. 15-4

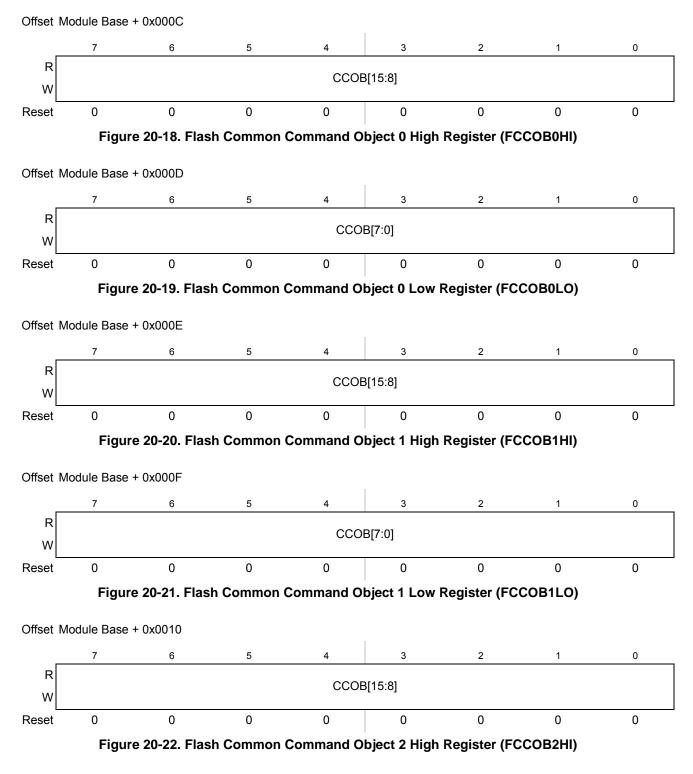

Chapter 20 Flash Module (S12ZFTMRZ)

## 20.3.2.13 Flash Common Command Object Registers (FCCOB)

The FCCOB is an array of six words. Byte wide reads and writes are allowed to the FCCOB registers.

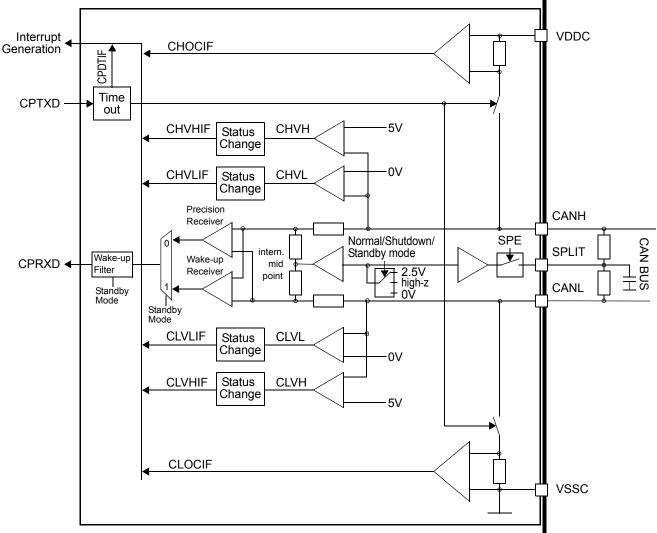

Figure 21-1. CAN Physical Layer Block Diagram

# 21.2 External Signal Description

Table 21-2 shows the external pins associated with the CAN Physical Layer.

| Name  | Function                          |

|-------|-----------------------------------|

| CANH  | CAN Bus High Pin                  |

| SPLIT | 2.5 V Termination Pin             |

| CANL  | CAN Bus Low Pin                   |

| VDDC  | Supply Pin for CAN Physical Layer |

| VSSC  | Ground Pin for CAN Physical Layer |

Table 21-2. CAN Physical Layer Signal Properties

Chapter 22 Pulse-Width Modulator (S12PWM8B8CV2)

| Register<br>Name                   | Bit 7 | 6                           | 5 | 4 | 3 | 2 | 1 | Bit 0 |  |  |

|------------------------------------|-------|-----------------------------|---|---|---|---|---|-------|--|--|

| 0x0023 R<br>PWMDTY7 <sup>2</sup> W | Bit 7 | 6                           | 5 | 4 | 3 | 2 | 1 | Bit 0 |  |  |

| 0x0024 R                           | 0     | 0                           | 0 | 0 | 0 | 0 | 0 | 0     |  |  |

| RESERVED W                         | /     |                             |   |   |   |   |   |       |  |  |

| 0x0025 R                           | 0     | 0                           | 0 | 0 | 0 | 0 | 0 | 0     |  |  |

| RESERVED W                         | /     |                             |   |   |   |   |   |       |  |  |

| 0x0026 R                           | 0     | 0                           | 0 | 0 | 0 | 0 | 0 | 0     |  |  |

| RESERVED W                         | /     |                             |   |   |   |   |   |       |  |  |

| 0x0027 R                           | 0     | 0                           | 0 | 0 | 0 | 0 | 0 | 0     |  |  |

| RESERVED W                         |       |                             |   |   |   |   |   |       |  |  |

|                                    |       | = Unimplemented or Reserved |   |   |   |   |   |       |  |  |

#### Figure 22-2. The scalable PWM Register Summary (Sheet 4 of 4)

1. The related bit is available only if corresponding channel exists.

2. The register is available only if corresponding channel exists.

### 22.3.2.1 PWM Enable Register (PWME)

Each PWM channel has an enable bit (PWMEx) to start its waveform output. When any of the PWMEx bits are set (PWMEx = 1), the associated PWM output is enabled immediately. However, the actual PWM waveform is not available on the associated PWM output until its clock source begins its next cycle due to the synchronization of PWMEx and the clock source.

#### NOTE

The first PWM cycle after enabling the channel can be irregular.

An exception to this is when channels are concatenated. Once concatenated mode is enabled (CONxx bits set in PWMCTL register), enabling/disabling the corresponding 16-bit PWM channel is controlled by the low order PWMEx bit. In this case, the high order bytes PWMEx bits have no effect and their corresponding PWM output lines are disabled.

While in run mode, if all existing PWM channels are disabled (PWMEx-0=0), the prescaler counter shuts off for power savings.

Module Base + 0x0000

|        | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|--------|-------|-------|-------|-------|-------|-------|-------|-------|--|--|--|

| R<br>W | PWME7 | PWME6 | PWME5 | PWME4 | PWME3 | PWME2 | PWME1 | PWME0 |  |  |  |

| Reset  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

|        |       |       |       |       |       |       |       |       |  |  |  |

Figure 22-3. PWM Enable Register (PWME)

Read: Anytime

#### Chapter 22 Pulse-Width Modulator (S12PWM8B8CV2)

The clock source of each PWM channel is determined by PCLKx bits in PWMCLK (see Section 22.3.2.3, "PWM Clock Select Register (PWMCLK)) and PCLKABx bits in PWMCLKAB as shown in Table 22-5 and Table 22-6.

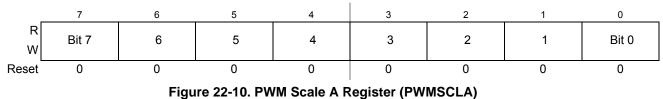

### 22.3.2.8 PWM Scale A Register (PWMSCLA)

PWMSCLA is the programmable scale value used in scaling clock A to generate clock SA. Clock SA is generated by taking clock A, dividing it by the value in the PWMSCLA register and dividing that by two.

Clock SA = Clock A / (2 \* PWMSCLA)

### NOTE

When PWMSCLA = 00, PWMSCLA value is considered a full scale value of 256. Clock A is thus divided by 512.

Any value written to this register will cause the scale counter to load the new scale value (PWMSCLA).

Module Base + 0x0008

Read: Anytime

Write: Anytime (causes the scale counter to load the PWMSCLA value)

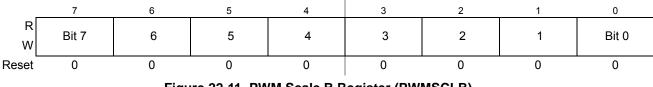

### 22.3.2.9 PWM Scale B Register (PWMSCLB)

PWMSCLB is the programmable scale value used in scaling clock B to generate clock SB. Clock SB is generated by taking clock B, dividing it by the value in the PWMSCLB register and dividing that by two.

Clock SB = Clock B / (2 \* PWMSCLB)

### NOTE

When PWMSCLB = \$00, PWMSCLB value is considered a full scale value of 256. Clock B is thus divided by 512.

Any value written to this register will cause the scale counter to load the new scale value (PWMSCLB).

Module Base + 0x0009

Figure 22-11. PWM Scale B Register (PWMSCLB)

#### Read: Anytime

Write: Anytime (causes the scale counter to load the PWMSCLB value).

|                | freescale                                                                | <ul> <li>PREESCALE SEMICONDUCTOR, NC. ALL RIGHTS RESERVED.<br/>ELECTRONC VERSIONS ARE UNCONTROLLED EXCEPT WHEN<br/>ACCESSED DIRECTLY TRAIL INCODECURENT CONTROL REPOSITORY.<br/>PRINTED VERSION TRAIL TO DOCUMENT CONTROL REPOSITORY.<br/>"CONTROLLED COPY" IN RED.</li> </ul> | MECHANICAL OUTLINE<br>DO NOT SCALE THIS DRAWING                                                                                                                             |         |

|----------------|--------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| N(<br>1.<br>2. | INTERPRET DI                                                             | RE IN MILLIMETERS.<br>Mensions and tolerances<br>And d to be determined a                                                                                                                                                                                                      | AT DATUM PLANE H.                                                                                                                                                           |         |

| <u></u>        | , DIMENSION DC<br>Shall Not C<br>Than 0.08 M                             | AUSE THE LEAD WIDTH TO E<br>M. DAMBAR CANNOT BE LOC.                                                                                                                                                                                                                           | G PLANE C.<br>ROTRUSION. ALLOWABLE DAMBAR PROTRUSIO<br>XCEED THE MAXIMUM DIMENSION BY MORE<br>ATED ON THE LOWER RADIUS OR THE FOOT.<br>D ADJACENT LEAD OR PROTRUSION 0.07 M |         |

|                | PER SIDE. DIM<br>MISMATCH.<br>EXACT SHAPE<br>THESE DIMENS<br>0.25 MM FRC | MENSIONS ARE MAXIMUM PLA<br>OF EACH CORNER IS OPTION                                                                                                                                                                                                                           | ECTION OF THE LEAD BETWEEN 0.10 MM AN                                                                                                                                       | .D      |

|                |                                                                          |                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |         |

| TITLE:         | 0.5 F                                                                    | X 12 X 1.4 PKG,<br>Pitch, 80LD,<br>6 exposed pad                                                                                                                                                                                                                               | DOCUMENT NO: 98ASA00505D R<br>STANDARD: NON-JEDEC<br>SHEET:                                                                                                                 | REV: X2 |

# M.6 0x0380-0x039F FTMRZ128K512 (continued)

| Address | Name     |        | 7      | 6      | 5       | 4      | 3      | 2      | 1       | 0       |

|---------|----------|--------|--------|--------|---------|--------|--------|--------|---------|---------|

| 0x0384  | FCNFG    | R<br>W | CCIE   | 0      | ERSAREQ | IGNSF  | WSTA   | T[1:0] | FDFD    | FSFD    |

| 0x0385  | FERCNFG  | R<br>W | 0      | 0      | 0       | 0      | 0      | 0      | 0       | SFDIE   |

| 0x0386  | FSTAT    | R<br>W | CCIF   | 0      | ACCERR  | FPVIOL | MGBUSY | RSVD   | MGSTAT1 | MGSTAT0 |

| 0x0387  | FERSTAT  | R<br>W | 0      | 0      | 0       | 0      | 0      | 0      | DFDF    | SFDIF   |

| 0x0388  | FPROT    | R<br>W | FPOPEN | RNV6   | FPHDIS  | FPHS1  | FPHS0  | FPLDIS | FPLS1   | FPLS0   |

| 0x0389  | DFPROT   | R<br>W | DPOPEN | 0      | 0       | 0      | DPS3   | DPS2   | DPS1    | DPS0    |

| 0x038A  | FOPT     | R<br>W | NV7    | NV6    | NV5     | NV4    | NV3    | NV2    | NV1     | NV0     |

| 0x038B  | FRSV1    | R<br>W | 0      | 0      | 0       | 0      | 0      | 0      | 0       | 0       |

| 0x038C  | FCCOB0HI | R<br>W | CCOB15 | CCOB14 | CCOB13  | CCOB12 | CCOB11 | CCOB10 | CCOB9   | CCOB8   |

| 0x038D  | FCCOB0LO | R<br>W | CCOB7  | CCOB6  | CCOB5   | CCOB4  | CCOB3  | CCOB2  | CCOB1   | CCOB0   |

| 0x038E  | FCCOB1HI | R<br>W | CCOB15 | CCOB14 | CCOB13  | CCOB12 | CCOB11 | CCOB10 | CCOB9   | CCOB8   |

| 0x038F  | FCCOB1LO | R<br>W | CCOB7  | CCOB6  | CCOB5   | CCOB4  | CCOB3  | CCOB2  | CCOB1   | CCOB0   |

| 0x0390  | FCCOB2HI | R<br>W | CCOB15 | CCOB14 | CCOB13  | CCOB12 | CCOB11 | CCOB10 | CCOB9   | CCOB8   |

| 0x0391  | FCCOB2LO | R<br>W | CCOB7  | CCOB6  | CCOB5   | CCOB4  | CCOB3  | CCOB2  | CCOB1   | CCOB0   |

| 0x0392  | FCCOB3HI | R<br>W | CCOB15 | CCOB14 | CCOB13  | CCOB12 | CCOB11 | CCOB10 | CCOB9   | CCOB8   |

| 0x0393  | FCCOB3LO | R<br>W | CCOB7  | CCOB6  | CCOB5   | CCOB4  | CCOB3  | CCOB2  | CCOB1   | CCOB0   |

| 0x0394  | FCCOB4HI | R<br>W | CCOB15 | CCOB14 | CCOB13  | CCOB12 | CCOB11 | CCOB10 | CCOB9   | CCOB8   |

| 0x0395  | FCCOB4LO | R<br>W | CCOB7  | CCOB6  | CCOB5   | CCOB4  | CCOB3  | CCOB2  | CCOB1   | CCOB0   |

# M.12 0x05C0-0x05FF TIM0

| Address           | Name      | Bit 7         | 6      | 5      | 4      | 3      | 2      | 1     | Bit 0 |

|-------------------|-----------|---------------|--------|--------|--------|--------|--------|-------|-------|

| 0x05D2            | TIM0TC1H  | R<br>W Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| 0x05D3            | TIM0TC1L  | R<br>W Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 0x05D4            | TIM0TC2H  | R<br>W Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| 0x05D5            | TIM0TC2L  | R<br>W Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 0x05D6            | TIM0TC3H  | R<br>W Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 |

| 0x05D7            | TIM0TC3L  | R<br>W Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0 |

| 0x05D8–<br>0x05DF | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05E0            | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05E1            | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05E2            | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05E3            | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05E4–<br>0x05EB | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05EC            | TIM0OCPD  | R<br>W        |        |        |        | OCPD3  | OCPD2  | OCPD1 | OCPD0 |

| 0x05ED            | Reserved  | R<br>W        |        |        |        |        |        |       |       |

| 0x05EE            | TIM0PTPSR | R<br>W PTPS7  | PTPS6  | PTPS5  | PTPS4  | PTPS3  | PTPS2  | PTPS1 | PTPS0 |

| 0x05EF            | Reserved  | R<br>W        |        |        |        |        |        |       |       |

# M.17 0x06F0-0x06F7 BATS

| Address            | Name     | Bit 7           | 6        | 5        | 4        | 3        | 2        | 1        | Bit 0    |

|--------------------|----------|-----------------|----------|----------|----------|----------|----------|----------|----------|

| 0x06F0             | BATE     | R 0<br>W        | BVHS     | BVLS     | 6[1:0]   | BSUAE    | BSUSE    | 0        | 0        |

| 0x06F1             | BATSR    | R 0<br>W        | 0        | 0        | 0        | 0        | 0        | BVHC     | BVLC     |

| 0x06F2             | BATIE    | R 0<br>W        | 0        | 0        | 0        | 0        | 0        | BVHIE    | BVLIE    |

| 0x06F3             | BATIF    | R 0<br>W        | 0        | 0        | 0        | 0        | 0        | BVHIF    | BVLIF    |

| 0x06F4 -<br>0x06F5 | Reserved | R 0<br>W        | 0        | 0        | 0        | 0        | 0        | 0        | 0        |

| 0x06F6 -<br>0x06F7 | Reserved | R<br>W Reserved | Reserved |

# M.18 0x0700-0x0707 SCI0

| Address | Name                  | -      | Bit 7   | 6       | 5     | 4     | 3     | 2      | 1      | Bit 0 |

|---------|-----------------------|--------|---------|---------|-------|-------|-------|--------|--------|-------|

| 0x0700  | SCI0BDH <sup>1</sup>  | R<br>W | SBR15   | SBR14   | SBR13 | SBR12 | SBR11 | SBR10  | SBR9   | SBR8  |

| 0x0701  | SCI0BDL <sup>1</sup>  | R<br>W | SBR7    | SBR6    | SBR5  | SBR4  | SBR3  | SBR2   | SBR1   | SBR0  |

| 0x0702  | SCI0CR1 <sup>1</sup>  | R<br>W | LOOPS   | SCISWAI | RSRC  | М     | WAKE  | ILT    | PE     | PT    |

| 0x0700  | SCI0ASR1 <sup>2</sup> | R<br>W | RXEDGIF | 0       | 0     | 0     | 0     | BERRV  | BERRIF | BKDIF |

| 0x0701  | SCI0ACR1 <sup>2</sup> | R<br>W | RXEDGIE | 0       | 0     | 0     | 0     | 0      | BERRIE | BKDIE |

| 0x0702  | SCI0ACR2 <sup>2</sup> | R<br>W | IREN    | TNP1    | TNP0  | 0     | 0     | BERRM1 | BERRM0 | BKDFE |

| 0x0703  | SCI0CR2               | R<br>W | TIE     | TCIE    | RIE   | ILIE  | TE    | RE     | RWU    | SBK   |

| 0x0704  | SCI0SR1               | R<br>W | TDRE    | TC      | RDRF  | IDLE  | OR    | NF     | FE     | PF    |

| 0x0705  | SCI0SR2               | R<br>W | AMAP    | 0       | 0     | TXPOL | RXPOL | BRK13  | TXDIR  | RAF   |