#### Welcome to <u>E-XFL.COM</u>

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | S12Z                                                                     |

| Core Size                  | 16-Bit                                                                   |

| Speed                      | 50MHz                                                                    |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                 |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 31                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 512 x 8                                                                  |

| RAM Size                   | 4K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                               |

| Data Converters            | A/D 9x12b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-LQFP Exposed Pad                                                      |

| Supplier Device Package    | 64-HLQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvml64f3mkhr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2 trigger input sources and software trigger source

- 2 trigger outputs

- One 16-bit delay register pre-trigger output

- Operation in One-Shot or Continuous modes

### **1.4.9** LIN physical layer transceiver (ZVML devices only)

- Compliant with LIN Physical Layer 2.2 specification.

- Compliant with the SAE J2602-2 LIN standard.

- Standby mode with glitch-filtered wake-up.

- Slew rate selection optimized for the baud rates: 10.4kBit/s, 20kBit/s and Fast Mode (up to 250kBit/s).

- Switchable  $34k\Omega/330k\Omega$  pull-ups (in shutdown mode,  $330k\Omega$  only)

- Current limitation for LIN Bus pin falling edge.

- Over-current protection.

- LIN TxD-dominant timeout feature monitoring the LPTxD signal.

- Automatic transmitter shutdown in case of an over-current or TxD-dominant timeout.

- Fulfills the OEM "Hardware Requirements for LIN (CAN and FlexRay) Interfaces in Automotive Applications" v1.3.

### **1.4.10** Serial Communication Interface Module (SCI)

- Full-duplex or single-wire operation

- Standard mark/space non-return-to-zero (NRZ) format

- Selectable IrDA 1.4 return-to-zero-inverted (RZI) format with programmable pulse widths

- 16-bit baud rate selection

- Programmable character length

- Programmable polarity for transmitter and receiver

- Active edge receive wakeup

- Break detect and transmit collision detect supporting LIN

### 1.4.11 Multi-Scalable Controller Area Network (MSCAN)

- Implementation of the CAN protocol Version 2.0A/B

- Five receive buffers with FIFO storage scheme

- Three transmit buffers with internal prioritization using a "local priority" concept

- Flexible maskable identifier filter supports two full-size (32-bit) extended identifier filters, or four 16-bit filters, or either 8-bit filters

- Programmable wake-up functionality with integrated low-pass filter

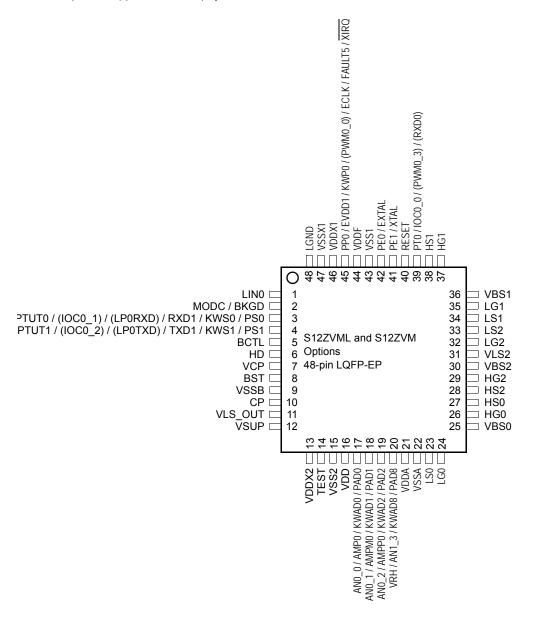

The exposed pad on the package bottom must be connected to a grounded contact pad on the PCB.

The LIN0 pin is mapped to the HV physical interface

Figure 1-6. S12ZVM, S12ZVML Option 48-pin LQFP

| Priority | PRIOLVL2 | PRIOLVL1 | PRIOLVL0 | Meaning          |

|----------|----------|----------|----------|------------------|

|          | 1        | 0        | 0        | Priority level 4 |

|          | 1        | 0        | 1        | Priority level 5 |

|          | 1        | 1        | 0        | Priority level 6 |

| high     | 1        | 1        | 1        | Priority level 7 |

Table 4-7. Interrupt Priority Levels

# 4.4 Functional Description

The INT module processes all exception requests to be serviced by the CPU module. These exceptions include interrupt vector requests and reset vector requests. Each of these exception types and their overall priority level is discussed in the subsections below.

## 4.4.1 S12Z Exception Requests

The CPU handles both reset requests and interrupt requests. The INT module contains registers to configure the priority level of each I-bit maskable interrupt request which can be used to implement an interrupt priority scheme. This also includes the possibility to nest interrupt requests. A priority decoder is used to evaluate the relative priority of pending interrupt requests.

## 4.4.2 Interrupt Prioritization

After system reset all I-bit maskable interrupt requests are configured to be enabled, are set up to be handled by the CPU and have a pre-configured priority level of 1. Exceptions to this rule are the non-maskable interrupt requests and the spurious interrupt vector request at (vector base + 0x0001DC) which cannot be disabled, are always handled by the CPU and have a fixed priority levels. A priority level of 0 effectively disables the associated I-bit maskable interrupt request.

If more than one interrupt request is configured to the same interrupt priority level the interrupt request with the higher vector address wins the prioritization.

The following conditions must be met for an I-bit maskable interrupt request to be processed.

- 1. The local interrupt enabled bit in the peripheral module must be set.

- 2. The setup in the configuration register associated with the interrupt request channel must meet the following conditions:

- a) The priority level must be set to non zero.

- b) The priority level must be greater than the current interrupt processing level in the condition code register (CCW) of the CPU (PRIOLVL[2:0] > IPL[2:0]).

- 3. The I-bit in the condition code register (CCW) of the CPU must be cleared.

- 4. There is no access violation interrupt request pending.

- 5. There is no SYS, SWI, SPARE, TRAP, Machine Exception or  $\overline{\text{XIRQ}}$  request pending.

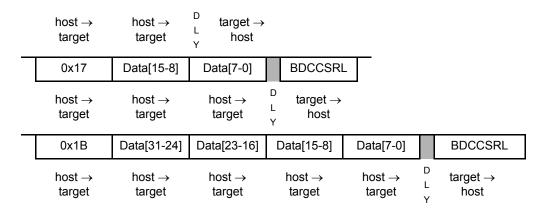

FILL\_MEM.sz\_WS

FILL\_MEM{\_WS} is used with the WRITE\_MEM{\_WS} command to access large blocks of memory. An initial WRITE\_MEM{\_WS} is executed to set up the starting address of the block and write the first datum. If an initial WRITE\_MEM{\_WS} is not executed before the first FILL\_MEM{\_WS}, an illegal command response is returned. The FILL\_MEM{\_WS} command stores subsequent operands. The initial address is incremented by the operand size (1, 2, or 4) and saved in a temporary register. Subsequent FILL\_MEM{\_WS} commands use this address, perform the memory write, increment it by the current operand size, and store the updated address in the temporary register. If the with-status option is specified, the BDCCSRL status byte is returned after the write data. This status byte reflects the state after the memory write was performed. If enabled an ACK pulse is generated after the internal write access has been completed or aborted. The effect of the access size and alignment on the next address to be accessed is explained in more detail in Section 5.4.5.2"

#### NOTE

FILL\_MEM{\_WS} is a valid command only when preceded by SYNC, NOP, WRITE\_MEM{\_WS}, or another FILL\_MEM{\_WS} command. Otherwise, an illegal command response is returned, setting the ILLCMD bit. NOP can be used for inter command padding without corrupting the address pointer.

The size field (sz) is examined each time a FILL\_MEM{\_WS} command is processed, allowing the operand size to be dynamically altered. The examples show the FILL\_MEM.B{\_WS}, FILL\_MEM.W{\_WS} and FILL\_MEM.L{\_WS} commands.

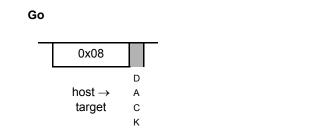

#### 5.4.4.7 GO

Non-intrusive

- Frequency trimming (A factory trim value for 1MHz is loaded from Flash Memory into the IRCTRIM register after reset, which can be overwritten by application if required)

- Temperature Coefficient (TC) trimming. (A factory trim value is loaded from Flash Memory into the IRCTRIM register to turn off TC trimming after reset. Application can trim the TC if required by overwriting the IRCTRIM register).

Other features of the S12CPMU\_UHV\_V10\_V6 include

- Oscillator clock monitor to detect loss of crystal

- Autonomous periodical interrupt (API)

- Bus Clock Generator

- Clock switch to select either PLLCLK or external crystal/resonator based Bus Clock

- PLLCLK divider to adjust system speed

- System Reset generation from the following possible sources:

- Power-on reset (POR)

- Low-voltage reset (LVR)

- COP system watchdog, COP reset on time-out, windowed COP

- Loss of oscillation (Oscillator clock monitor fail)

- Loss of PLL clock (PLL clock monitor fail)

- External pin RESET

$\label{eq:rescaled} \begin{array}{ll} \mbox{If XOSCLCP is enabled (OSCE=1)} & f_{REF} = \frac{f_{OSC}}{(REFDIV+1)} \end{array}$   $\mbox{If XOSCLCP is disabled (OSCE=0)} & f_{REF} = f_{IRC1M} \end{array}$

The REFFRQ[1:0] bits are used to configure the internal PLL filter for optimal stability and lock time. For correct PLL operation the REFFRQ[1:0] bits have to be selected according to the actual REFCLK frequency as shown in Table 8-4.

If IRC1M is selected as REFCLK (OSCE=0) the PLL filter is fixed configured for the 1MHz  $\leq f_{REF} \leq 2MHz$  range. The bits can still be written but will have no effect on the PLL filter configuration.

For OSCE=1, setting the REFFRQ[1:0] bits incorrectly can result in a non functional PLL (no locking and/or insufficient stability).

| REFCLK Frequency Ranges<br>(OSCE=1) | REFFRQ[1:0] |

|-------------------------------------|-------------|

| 1MHz <= f <sub>REF</sub> <= 2MHz    | 00          |

| 2MHz < f <sub>REF</sub> <= 6MHz     | 01          |

| 6MHz < f <sub>REF</sub> <= 12MHz    | 10          |

| f <sub>REF</sub> >12MHz             | 11          |

Table 8-4. Reference Clock Frequency Selection if OSC\_LCP is enabled

Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

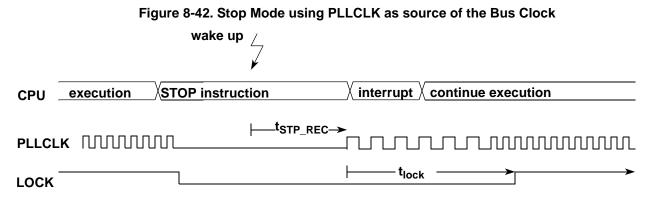

## 8.4.3 Stop Mode using PLLCLK as source of the Bus Clock

An example of what happens going into Stop Mode and exiting Stop Mode after an interrupt is shown in Figure 8-42. Disable PLL Lock interrupt (LOCKIE=0) before going into Stop Mode.

Depending on the COP configuration there might be an additional significant latency time until COP is active again after exit from Stop Mode due to clock domain crossing synchronization. This latency time occurs if COP clock source is ACLK and the CSAD bit is set (please refer to CSAD bit description for details).

## 8.4.4 Full Stop Mode using Oscillator Clock as source of the Bus Clock

An example of what happens going into Full Stop Mode and exiting Full Stop Mode after an interrupt is shown in Figure 8-43.

Disable PLL Lock interrupt (LOCKIE=0) and oscillator status change interrupt (OSCIE=0) before going into Full Stop Mode.

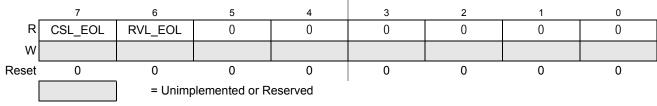

## 9.5.2.14 ADC End Of List Result Information Register (ADCEOLRI)

This register is cleared when bit ADC\_SR is set or bit ADC\_EN is clear.

Module Base + 0x0010

Figure 9-17. ADC End Of List Result Information Register (ADCEOLRI)

Read: Anytime

Write: Never

#### Table 9-19. ADCEOLRI Field Descriptions

| Field        | Description                                                                                                                                                                                                                                                                                                                                         |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>CSL_EOL | <ul> <li>Active CSL When "End Of List" Command Type Executed — This bit indicates the active (used) CSL when a "End Of List" command type has been executed and related data has been stored to RAM.</li> <li>0 CSL_0 active when "End Of List" command type executed.</li> <li>1 CSL_1 active when "End Of List" command type executed.</li> </ul> |

| 6<br>RVL_EOL | <ul> <li>Active RVL When "End Of List" Command Type Executed — This bit indicates the active (used) RVL when a "End Of List" command type has been executed and related data has been stored to RAM.</li> <li>0 RVL_0 active when "End Of List" command type executed.</li> <li>1 RVL_1 active when "End Of List" command type executed.</li> </ul> |

#### NOTE

The conversion interrupt EOL\_IF occurs and simultaneously the register ADCEOLRI is updated when the "End Of List" conversion command type has been processed and related data has been stored to RAM.

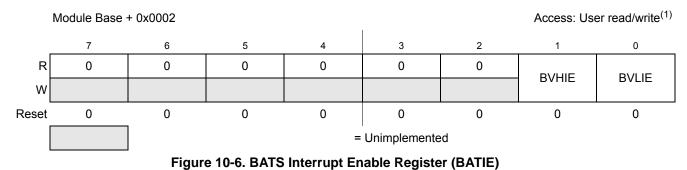

## **10.3.2.3 BATS Interrupt Enable Register (BATIE)**

1. Read: Anytime Write: Anytime

| Field      | Description                                                                                                                                       |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>BVHIE | BATS Interrupt Enable High — Enables High Voltage Interrupt .                                                                                     |

|            | <ol> <li>No interrupt will be requested whenever BVHIF flag is set .</li> <li>Interrupt will be requested whenever BVHIF flag is set</li> </ol>   |

| 0<br>BVLIE | BATS Interrupt Enable Low — Enables Low Voltage Interrupt .                                                                                       |

|            | <ol> <li>No interrupt will be requested whenever BVLIF flag is set .</li> <li>Interrupt will be requested whenever BVLIF flag is set .</li> </ol> |

#### Table 10-4. BATIE Register Field Descriptions

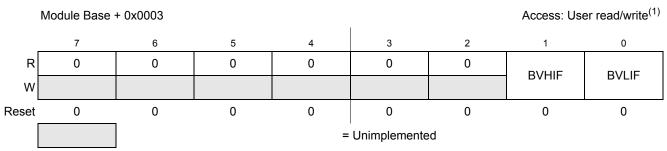

## 10.3.2.4 BATS Interrupt Flag Register (BATIF)

#### Figure 10-7. BATS Interrupt Flag Register (BATIF)

1. Read: Anytime

Write: Anytime, write 1 to clear

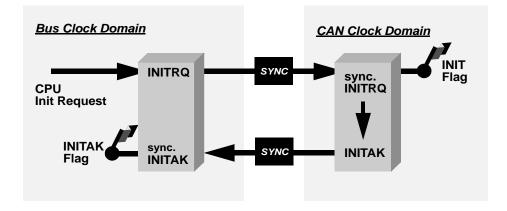

Figure 13-45. Initialization Request/Acknowledge Cycle

Due to independent clock domains within the MSCAN, INITRQ must be synchronized to all domains by using a special handshake mechanism. This handshake causes additional synchronization delay (see Figure 13-45).

If there is no message transfer ongoing on the CAN bus, the minimum delay will be two additional bus clocks and three additional CAN clocks. When all parts of the MSCAN are in initialization mode, the INITAK flag is set. The application software must use INITAK as a handshake indication for the request (INITRQ) to go into initialization mode.

#### NOTE

The CPU cannot clear INITRQ before initialization mode (INITRQ = 1 and INITAK = 1) is active.

### 13.4.5 Low-Power Options

If the MSCAN is disabled (CANE = 0), the MSCAN clocks are stopped for power saving.

If the MSCAN is enabled (CANE = 1), the MSCAN has two additional modes with reduced power consumption, compared to normal mode: sleep and power down mode. In sleep mode, power consumption is reduced by stopping all clocks except those to access the registers from the CPU side. In power down mode, all clocks are stopped and no power is consumed.

Table 13-37 summarizes the combinations of MSCAN and CPU modes. A particular combination of modes is entered by the given settings on the CSWAI and SLPRQ/SLPAK bits.

| Field        | Description                                                                                                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5<br>TG1TEIE | <ul> <li>Trigger Generator 1 Timing Error Interrupt Enable — Enables trigger generator timing error interrupt.</li> <li>0 No interrupt will be requested whenever TG1TEIF is set</li> <li>1 Interrupt will be requested whenever TG1TEIF is set</li> </ul>               |

| 4<br>TG1DIE  | <ul> <li>Trigger Generator 1 Done Interrupt Enable — Enables trigger generator done interrupt.</li> <li>0 No interrupt will be requested whenever TG1DIF is set</li> <li>1 Interrupt will be requested whenever TG1DIF is set</li> </ul>                                 |

| 3<br>TG0AEIE | <ul> <li>Trigger Generator 0 Memory Access Error Interrupt Enable — Enables trigger generator memory access error interrupt.</li> <li>0 No interrupt will be requested whenever TG0AEIF is set</li> <li>1 Interrupt will be requested whenever TG0AEIF is set</li> </ul> |

| 2<br>TG0REIE | <ul> <li>Trigger Generator 0 Reload Error Interrupt Enable — Enables trigger generator reload error interrupt.</li> <li>0 No interrupt will be requested whenever TG0REIF is set</li> <li>1 Interrupt will be requested whenever TG0REIF is set</li> </ul>               |

| 1<br>TG0TEIE | <ul> <li>Trigger Generator 0 Timing Error Interrupt Enable — Enables trigger generator timing error interrupt.</li> <li>0 No interrupt will be requested whenever TG0TEIF is set</li> <li>1 Interrupt will be requested whenever TG0TEIF is set</li> </ul>               |

| 0<br>TG0DIE  | <ul> <li>Trigger Generator 0 Done Interrupt Enable — Enables trigger generator done interrupt.</li> <li>0 No interrupt will be requested whenever TG0DIF is set</li> <li>1 Interrupt will be requested whenever TG0DIF is set</li> </ul>                                 |

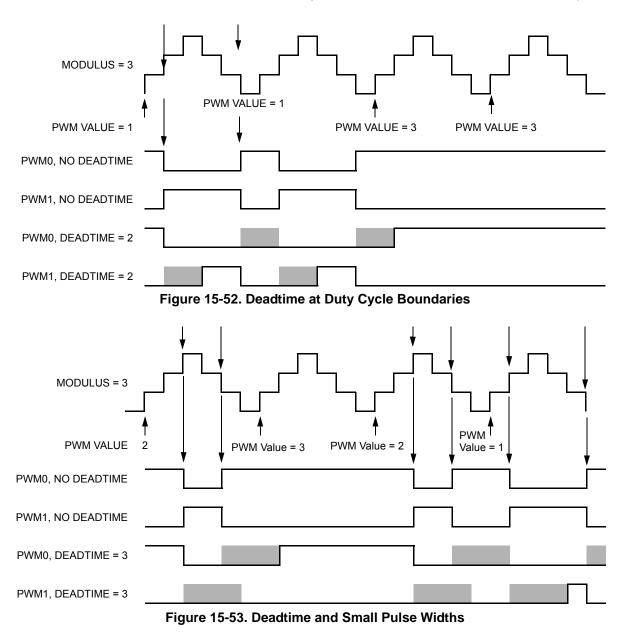

Chapter 15 Pulse Width Modulator with Fault Protection (PMF15B6CV4)

#### NOTE

The waveform at the output is delayed by two core clock cycles for deadtime insertion.

## 15.4.6 Top/Bottom Correction

In complementary mode, either the top or the bottom transistor controls the output voltage. However, deadtime has to be inserted to avoid overlap of conducting interval between the top and bottom transistor. Both transistors in complementary mode are off during deadtime, allowing the output voltage to be determined by the current status of the load and introduce distortion in the output voltage. See Figure 15-54. On AC induction motors running open-loop, the distortion typically manifests itself as poor low-speed performance, such as torque ripple and rough operation.

A stronger external pullup resistor might be necessary to sustain communication speeds up to **250 kbit/s.** The signal on the LIN pin and the LPRxD signal might not be symmetrical for high baud rates with high loads on the bus.

Please note that if the bit time is smaller than the parameter t<sub>OCLIM</sub> (please refer to electricals), then no overcurrent is reported nor does an overcurrent shutdown occur. However, the current limitation is always engaged in case of a failure.

## 19.4.3 Modes

Figure 19-11 shows the possible mode transitions depending on control bits, stop mode, and error conditions.

## 19.4.3.1 Shutdown Mode

The LIN/HV Physical Layer is fully disabled. No wake-up functionality is available. The internal pullup resistor is high ohmic only (330 k $\Omega$ ) to maintain the LIN pin in the recessive state. LPTxD is not monitored in this mode for a TxD-dominant timeout. All the registers are accessible.

Setting LPE causes the module to leave the shutdown mode and to enter the normal mode or receive only mode (if RXONLY bit is set).

Clearing LPE causes the module to leave the normal or receive only modes and go back to shutdown mode.

### 19.4.3.2 Normal Mode

The full functionality is available. Both receiver and transmitter are enabled. The internal pullup resistor can be chosen to be high ohmic (330 k $\Omega$ ) if LPPUE = 0, or LIN compliant (34 k $\Omega$ ) if LPPUE = 1.

If RXONLY is set, the module leaves normal mode to enter receive only mode.

If the MCU enters stop mode, the LIN/HV Physical Layer enters standby mode.

## 19.4.3.3 Receive Only Mode

Entering this mode disables the transmitter and immediately stops any on-going transmission. LPTxD is not monitored in this mode for a TxD-dominant timeout.

The receiver is running in full performance mode in all cases.

To return to normal mode, the RXONLY bit must be cleared.

If the device enters stop mode, the module leaves receive only mode to enter standby mode.

### 19.4.3.4 Standby Mode with Wake-Up Feature

The transmitter of the LIN/HV Physical Layer is disabled and the receiver enters a low power mode.

### NOTE

Before entering standby mode, please ensure that no transmission is ongoing.

Chapter 19 LIN/HV Physical Layer (S12LINPHYV3)

## 19.4.4 Interrupts

The interrupt vector requested by the LIN/HV Physical Layer is listed in Table 19-10. Vector address and interrupt priority is defined at the MCU level.

The module internal interrupt sources are combined into a single interrupt request at the device level.

| Module Interrupt Source | Module Internal Interrupt<br>Source            | Local Enable |

|-------------------------|------------------------------------------------|--------------|

| LIN Interrupt (LPI)     | LIN Txd-Dominant Timeout<br>Interrupt (LPDTIF) | LPDTIE = 1   |

|                         | LIN Overcurrent Interrupt<br>(LPOCIF)          | LPOCIE = 1   |

Table 19-10. Interrupt Vectors

### **19.4.4.1 Overcurrent Interrupt**

The transmitter is protected against overcurrent. In case of an overcurrent condition occurring within a time frame called  $t_{OCLIM}$  starting from LPTxD falling edge, the current through the transmitter is limited (the transmitter is not shut down). The masking of an overcurrent event within the time frame  $t_{OCLIM}$  is meant to avoid "false" overcurrent conditions that can happen during the discharging of the LIN bus. If an overcurrent event occurs out of this time frame, the transmitter is disabled and the LPOCIF flag is set.

In order to re-enable the transmitter again, the following prerequisites must be met:

1) Overcurrent condition is over

2) LPTxD is recessive or the LIN/HV Physical Layer is in shutdown or receive only mode for a minimum of a transmit bit time.

To re-enable the transmitter then, the LPOCIF flag must be cleared (by writing a 1).

#### NOTE

Please make sure that LPOCIF=1 before trying to clear it. It is not allowed to try to clear LPOCIF if LPOCIF=0 already.

After clearing LPOCIF, if the overcurrent condition is still present or the LPTxD pin is dominant while being in normal mode, the transmitter remains disabled and the LPOCIF flag is set again after a time to indicate that the attempt to re-enable has failed. This time is equal to:

- minimum 1 IRC period (1 us) + 2 bus periods

- maximum 2 IRC periods (2 us) + 3 bus periods

If the bit LPOCIE is set in the LPIE register, an interrupt is requested.

Figure 19-12 shows the different scenarios for overcurrent interrupt handling.

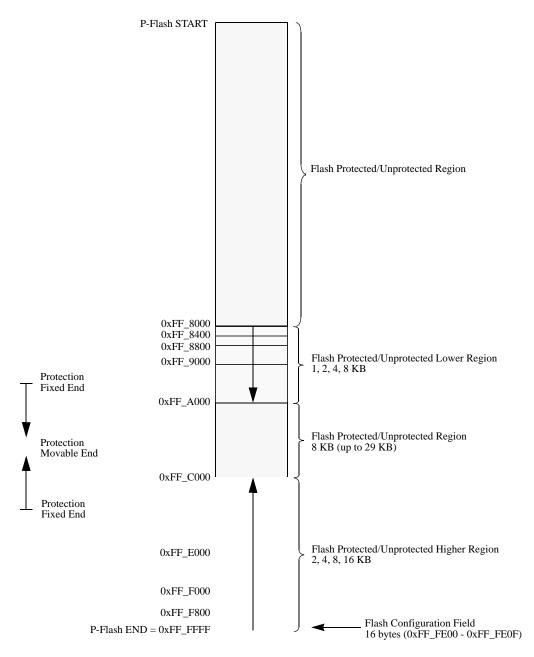

Figure 20-2. P-Flash Memory Map With Protection Alignment

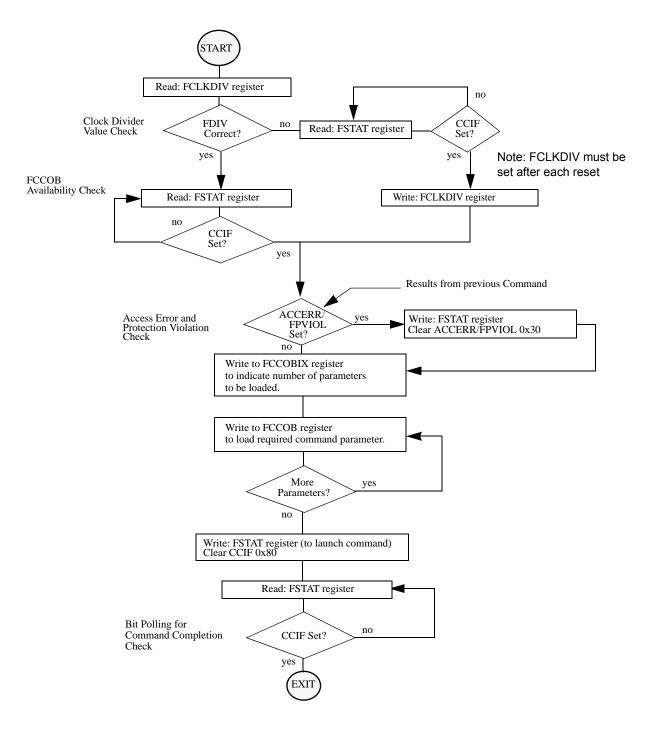

Chapter 20 Flash Module (S12ZFTMRZ)

Figure 20-30. Generic Flash Command Write Sequence Flowchart

| Register | Error Bit | Error Condition                                                                     |

|----------|-----------|-------------------------------------------------------------------------------------|

|          |           | Set if CCOBIX[2:0] < 010 at command launch                                          |

|          |           | Set if CCOBIX[2:0] > 101 at command launch                                          |

|          | ACCERR    | Set if command not available in current mode (see Table 20-29)                      |

|          | ACCERK    | Set if an invalid global address [23:0] is supplied                                 |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |

|          |           | Set if the requested group of words breaches the end of the EEPROM block            |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |

Table 20-65. Program EEPROM Command Error Handling

### 20.4.7.16 Erase EEPROM Sector Command

The Erase EEPROM Sector operation will erase all addresses in a sector of the EEPROM block.

Table 20-66. Erase EEPROM Sector Command FCCOB Requirements

| Register | FCCOB Parameters                                                                                               |                                                    |  |  |  |

|----------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|

| FCCOB0   | 0x12                                                                                                           | Global address [23:16] to identify<br>EEPROM block |  |  |  |

| FCCOB1   | Global address [15:0] anywhere within the sector to be erased.<br>See Section 20.1.2.2 for EEPROM sector size. |                                                    |  |  |  |

Upon clearing CCIF to launch the Erase EEPROM Sector command, the Memory Controller will erase the selected Flash sector and verify that it is erased. The CCIF flag will set after the Erase EEPROM Sector operation has completed.

| Register | Error Bit | Error Condition                                                                     |  |  |  |

|----------|-----------|-------------------------------------------------------------------------------------|--|--|--|

|          |           | Set if CCOBIX[2:0] != 001 at command launch                                         |  |  |  |

|          | ACCERR    | Set if command not available in current mode (see Table 20-29)                      |  |  |  |

|          | ACCERK    | Set if an invalid global address [23:0] is supplied see Table 20-3                  |  |  |  |

| FSTAT    |           | Set if a misaligned word address is supplied (global address [0] != 0)              |  |  |  |

|          | FPVIOL    | Set if the selected area of the EEPROM memory is protected                          |  |  |  |

|          | MGSTAT1   | Set if any errors have been encountered during the verify operation                 |  |  |  |

|          | MGSTAT0   | Set if any non-correctable errors have been encountered during the verify operation |  |  |  |

Table 20-67. Erase EEPROM Sector Command Error Handling

#### Appendix E GDU Electrical Specifications

Appendix M Detailed Register Address Map

# M.3 0x0070-0x00FF S12ZMMC

| Address | Name       |        | Bit 7 | 6    | 5    | 4         | 3   | 2   | 1     | Bit 0 |

|---------|------------|--------|-------|------|------|-----------|-----|-----|-------|-------|

| 0x0070  | MODE       | R      | MODC  | 0    | 0    | 0         | 0   | 0   | 0     | 0     |

|         |            | W      | MODO  |      |      |           |     |     |       |       |

| 0x0071- | Reserved   | R      | 0     | 0    | 0    | 0         | 0   | 0   | 0     | 0     |

| 0x007F  |            | W      |       |      |      |           |     |     |       |       |

| 0x0080  | MMCECH     | R<br>W |       | ITR[ | 3:0] |           |     | TGT | [3:0] |       |

| 0x0081  | MMCECL     | R<br>W |       | ACC[ | 3:0] |           |     | ERR | [3:0] |       |

| 0x0082  | MMCCCRH    | R      | CPUU  | 0    | 0    | 0         | 0   | 0   | 0     | 0     |

|         |            | w      |       |      |      |           |     | -   |       |       |

| 0x0083  | MMCCCRL    | R      | 0     | CPUX | 0    | CPUI      | 0   | 0   | 0     | 0     |

|         | MINIOCOILE | W      |       |      |      |           |     |     |       |       |

|         |            |        |       |      |      |           |     |     |       |       |

| 0x0084  | Reserved   | R      | 0     | 0    | 0    | 0         | 0   | 0   | 0     | 0     |

|         |            | W      |       |      |      |           |     |     |       |       |

| 0x0085  | MMCPCH     | R      |       |      |      | CPUPC[23: | 16] |     |       |       |

|         |            | W      |       |      |      |           |     |     |       |       |

| 0x0086  | MMCPCM     | R      |       |      |      | CPUPC[15  | :8] |     |       |       |

|         |            | W      |       |      |      |           |     |     |       |       |

| 0x0087  | MMCPCL     | R      |       |      |      | CPUPC[7:  | 0]  |     |       |       |

|         |            | w      |       |      |      |           |     |     |       |       |

| 0x0088- | Reserved   | R      | 0     | 0    | 0    | 0         | 0   | 0   | 0     | 0     |

| 0x00FF  |            | w      |       |      |      |           |     |     |       |       |

# M.4 0x0100-0x017F S12ZDBG

| Address | Name         |          | Bit 7    | 6       | 5        | 4     | 3                 | 2        | 1      | Bit 0              |

|---------|--------------|----------|----------|---------|----------|-------|-------------------|----------|--------|--------------------|

| 0x0100  | DBGC1        | R<br>W   | ARM      | 0       | reserved | BDMBP | BRKCPU            | reserved | EEVE1  | EEVE0 <sup>2</sup> |

|         |              |          |          | TRIG    |          |       |                   |          |        |                    |

| 0x0101  | DBGC2        | 2 R<br>W | 0        | 0       | 0        | 0     | CDCM <sup>2</sup> |          | ABCM   |                    |

|         |              |          |          |         |          |       |                   |          |        |                    |

|         |              | -        |          |         |          |       | 1                 |          |        |                    |

| 0x0102  | DBGTCRH<br>2 | R<br>W   | reserved | TSOURCE | TRANGE   |       | TRCMOD            |          | TALIGN |                    |

|         |              |          |          |         |          |       |                   |          |        |                    |

# M.10 0x0500-x053F PMF15B6C

| Address | Name     |        | Bit 7     | 6         | 5     | 4     | 3       | 2            | 1            | Bit 0        |  |  |

|---------|----------|--------|-----------|-----------|-------|-------|---------|--------------|--------------|--------------|--|--|

| 0x0518  | PMFVAL4  | R<br>W | PMFVAL4   |           |       |       |         |              |              |              |  |  |

| 0x0519  | PMFVAL4  | R<br>W | PMFVAL4   |           |       |       |         |              |              |              |  |  |

| 0x051A  | PMFVAL5  | R<br>W | PMFVAL5   |           |       |       |         |              |              |              |  |  |

| 0x051B  | PMFVAL5  | R<br>W | PMFVAL5   |           |       |       |         |              |              |              |  |  |

| 0x051C  | PMFROIE  | R<br>W | 0         | 0         | 0     | 0     | 0       | PMFROIE<br>C | PMFROIE<br>B | PMFROIE<br>A |  |  |

| 0x051D  | PMFROIF  | R<br>W | 0         | 0         | 0     | 0     | 0       | PMFROIF<br>C | PMFROIF<br>B | PMFROIF<br>A |  |  |

| 0x051E  | PMFICCTL | R<br>W | 0         | 0         | PECC  | PECB  | PECA    | ICCC         | ICCB         | ICCA         |  |  |

| 0x051F  | PMFCINV  | R<br>W | 0         | 0         | CINV5 | CINV4 | CINV3   | CINV2        | CINV1        | CINV0        |  |  |

| 0x0520  | PMFENCA  | R<br>W | PWMENA    | GLDOKA    | 0     | 0     | 0       | RSTRTA       | LDOKA        | PWMRIEA      |  |  |

| 0x0521  | PMFFQCA  | R<br>W | LDFQA     |           |       |       | HALFA   | PR           | PWMRFA       |              |  |  |

| 0x0522  | PMFCNTA  | R<br>W | 0         | 0 PMFCNTA |       |       |         |              |              |              |  |  |

| 0x0523  | PMFCNTA  | R<br>W |           | PMFCNTA   |       |       |         |              |              |              |  |  |

| 0x0524  | PMFMODA  | R<br>W | 0 PMFMODA |           |       |       |         |              |              |              |  |  |

| 0x0525  | PMFMODA  | R<br>W | PMFMODA   |           |       |       |         |              |              |              |  |  |

| 0x0526  | PMFDTMA  | R<br>W | 0         | 0         | 0     | 0     | PMFDTMA |              |              |              |  |  |

| 0x0527  | PMFDTMA  | R<br>W | PMFDTMA   |           |       |       |         |              |              |              |  |  |

| 0x0528  | PMFENCB  | R<br>W | PWMENB    | GLDOKB    | 0     | 0     | 0       | RSTRTB       | LDOKB        | PWMRIEB      |  |  |