Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | S12Z                                                                    |

| Core Size                  | 16-Bit                                                                  |

| Speed                      | 50MHz                                                                   |

| Connectivity               | CANbus, LINbus, SCI, SPI                                                |

| Peripherals                | DMA, POR, PWM, WDT                                                      |

| Number of I/O              | 31                                                                      |

| Program Memory Size        | 64KB (64K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 4K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3.5V ~ 40V                                                              |

| Data Converters            | A/D 9x12b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP Exposed Pad                                                     |

| Supplier Device Package    | 64-HLQFP (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/s912zvml64f3vkh |

## Table 0-1. Revision History

| Date        | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19 APR 2016 | 2.8      | Added PAD pin leakage specification at 125°C Table A-12 Updated t <sub>HGON</sub> , t <sub>HGOFF</sub> parameter values Table E-1 Specified VRH drop when using VDDS1 or VDDS2 as VRH on ZVMC256 Section C.1.1.5 Added min. and max. desaturation comparator filter times to electrical spec. Table E-1 Updated 64LQFP-EP thermal parameters Table A-9, Table A-10                                                                                                                                                                                                                                                                                                                                                                  |

| 06 JUN 2016 | 2.9      | Fixed corrupted symbol fonts Table A-3, Table A-5 Corrected wrong IFR reference Section 20.3.2.10 Clarified PAD8 leakage better Table A-12 Added I <sub>SUPR</sub> and I <sub>SUPW</sub> maximum values at T <sub>J</sub> = 175°C for ZVMC256 Table A-18 Added Pseudo STOP maximum current for ZVMC256 Table A-20 Removed bandgap temperature dependency footnote, Table B-1 Changed ZVMC256 SNPS monitor threshold min/max values Table B-2 Changed VLS current limit threshold to 112mA Table E-1, Table E-2 Removed desaturation comparator filter times from GDU chapter. Added desaturation comparator levels to Table E-1, Table E-2 Added low side desaturation comparator functional range as footnote Table E-1, Table E-2 |

| 29 JUN 2016 | 2.10     | Updated GDU VBS filter Figure 18-20 Removed incorrect reference to temperature sensor influencing GDU outputs Section 1.13.3.4 Changed Stop IDD (ISUPS) specifications for ZVMC256 Table A-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 28 OCT 2016 | 2.11     | Added IOC0 signal mapping to 48LQFP package Figure 1-6 Fixed corrupted symbol fonts in PIM chapter Added diode to VDDC pin Figure 1-18 Updated Stop mode current ISUPS maximum values Table A-19 Updated tdelon, tdeloff values Table E-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Global<br>Address | Register<br>Name   | Bit 7 | 6 | 5 | 4 | 3 | 2 | 1     | Bit 0   |

|-------------------|--------------------|-------|---|---|---|---|---|-------|---------|

| 0x02F8-           | Reserved           | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | 0       |

| 0x02FC            | Reserved           | W     |   |   |   |   |   |       |         |

| 0x02FD            | RDRP               | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | RDRP0   |

| OXOZI B NDNI      | W                  |       |   |   |   |   |   | KDKF0 |         |

| 0x02FE-           | Decembed           | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | 0       |

| 0x0330            | Reserved           | W     |   |   |   |   |   |       |         |

| 00004             | PTIL <sup>2</sup>  | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | PTIL0   |

| 0x0331            | PIIL-              | W     |   |   |   |   |   |       |         |

| 00000             | Danamad            | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | 0       |

| 0x0332            | Reserved           | W     |   |   |   |   |   |       |         |

| 0.0000            | PTPSL <sup>2</sup> | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | DTDOL 6 |

| 0x0333            | PIPSL-             | W     |   |   |   |   |   |       | PTPSL0  |

| 0.0004            | PPSL <sup>2</sup>  | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | DDO! 0  |

| 0x0334            | PPSL-              | W     |   |   |   |   |   |       | PPSL0   |

| 00005             | Danamad            | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | 0       |

| 0x0335            | Reserved           | W     |   |   |   |   |   |       |         |

| 0x0336            | PIEL <sup>2</sup>  | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | DIEL 0  |

|                   | PIEL-              | W     |   |   |   |   |   |       | PIEL0   |

| 0.0207            | PIFL <sup>2</sup>  | R 0   | 0 | 0 | 0 | 0 | 0 | 0     | DIE! 0  |

| 0x0337            | PIFL <sup>+</sup>  | W     |   |   |   |   |   |       | PIFL0   |

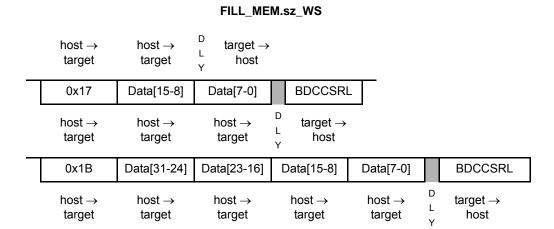

FILL\_MEM{\_WS} is used with the WRITE\_MEM{\_WS} command to access large blocks of memory. An initial WRITE\_MEM{\_WS} is executed to set up the starting address of the block and write the first datum. If an initial WRITE\_MEM{\_WS} is not executed before the first FILL\_MEM{\_WS}, an illegal command response is returned. The FILL\_MEM{\_WS} command stores subsequent operands. The initial address is incremented by the operand size (1, 2, or 4) and saved in a temporary register. Subsequent FILL\_MEM{\_WS} commands use this address, perform the memory write, increment it by the current operand size, and store the updated address in the temporary register. If the with-status option is specified, the BDCCSRL status byte is returned after the write data. This status byte reflects the state after the memory write was performed. If enabled an ACK pulse is generated after the internal write access has been completed or aborted. The effect of the access size and alignment on the next address to be accessed is explained in more detail in Section 5.4.5.2"

#### NOTE

FILL\_MEM{\_WS} is a valid command only when preceded by SYNC, NOP, WRITE\_MEM{\_WS}, or another FILL\_MEM{\_WS} command. Otherwise, an illegal command response is returned, setting the ILLCMD bit. NOP can be used for inter command padding without corrupting the address pointer.

The size field (sz) is examined each time a FILL\_MEM{\_WS} command is processed, allowing the operand size to be dynamically altered. The examples show the FILL\_MEM.B{\_WS}, FILL\_MEM.W{\_WS} and FILL\_MEM.L{\_WS} commands.

#### 5.4.4.7 GO

MC9S12ZVM Family Reference Manual Rev. 2.11

## 5.4.7 Serial Interface Hardware Handshake (ACK Pulse) Protocol

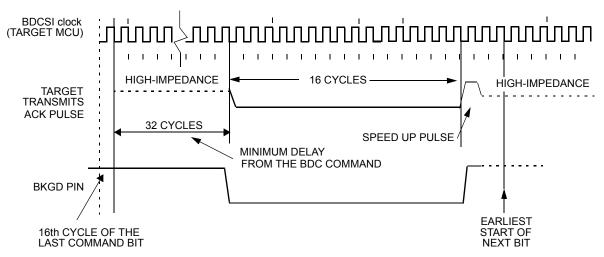

BDC commands are processed internally at the device core clock rate. Since the BDCSI clock can be asynchronous relative to the bus frequency, a handshake protocol is provided so the host can determine when an issued command has been executed. This section describes the hardware handshake protocol.

The hardware handshake protocol signals to the host controller when a BDC command has been executed by the target. This protocol is implemented by a low pulse (16 BDCSI clock cycles) followed by a brief speedup pulse on the BKGD pin, generated by the target MCU when a command, issued by the host, has been successfully executed (see Figure 5-9). This pulse is referred to as the ACK pulse. After the ACK pulse has finished, the host can start the bit retrieval if the last issued command was a read command, or start a new command if the last command was a write command or a control command.

Figure 5-9. Target Acknowledge Pulse (ACK)

The handshake protocol is enabled by the ACK\_ENABLE command. The BDC sends an ACK pulse when the ACK\_ENABLE command has been completed. This feature can be used by the host to evaluate if the target supports the hardware handshake protocol. If an ACK pulse is issued in response to this command, the host knows that the target supports the hardware handshake protocol.

Unlike the normal bit transfer, where the host initiates the transmission by issuing a negative edge on the BKGD pin, the serial interface ACK handshake pulse is initiated by the target MCU by issuing a negative edge on the BKGD pin. Figure 5-9 specifies the timing when the BKGD pin is being driven. The host must follow this timing constraint in order to avoid the risk of an electrical conflict at the BKGD pin.

When the handshake protocol is enabled, the STEAL bit in BDCCSR selects if bus cycle stealing is used to gain immediate access. If STEAL is cleared, the BDC is configured for low priority bus access using free cycles, without stealing cycles. This guarantees that BDC accesses remain truly non-intrusive to not affect the system timing during debugging. If STEAL is set, the BDC gains immediate access, if necessary stealing an internal bus cycle.

#### **NOTE**

If bus steals are disabled then a loop with no free cycles cannot allow access. In this case the host must recognize repeated NORESP messages and then issue a BACKGROUND command to stop the target and access the data.

MC9S12ZVM Family Reference Manual Rev. 2.11

## **NOTE**

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address Offset<br>Register Name |        | Bit 7         | 6           | 5            | 4            | 3       | 2 | 1     | Bit 0      |

|---------------------------------|--------|---------------|-------------|--------------|--------------|---------|---|-------|------------|

| 0x0000                          | R      | 0             | 0           | 0            | 0            | 0       | 0 | 0     | RDY        |

| ECCSTAT                         | W      |               |             |              |              |         |   |       |            |

| 0x0001<br>ECCIE                 | R      | 0             | 0           | 0            | 0            | 0       | 0 | 0     | SBEEIE     |

| ECCIE                           | W      |               |             |              |              |         |   |       | <b>322</b> |

| 0x0002<br>ECCIF                 | R      | 0             | 0           | 0            | 0            | 0       | 0 | 0     | SBEEIF     |

| ECCIF                           | W      |               |             |              |              |         |   |       | <b>33</b>  |

| 0x0003 - 0x0006<br>Reserved     | R      | 0             | 0           | 0            | 0            | 0       | 0 | 0     | 0          |

| Reserved                        | W      |               |             |              |              |         |   |       |            |

| 0x0007<br>ECCDPTRH              | R<br>W |               | DPTR[23:16] |              |              |         |   |       |            |

| 0x0008<br>ECCDPTRM              | R<br>W |               | DPTR[15:8]  |              |              |         |   |       |            |

| 0x0009<br>ECCDPTRL              | R<br>W |               |             |              | DPTR[7:1]    |         |   |       | 0          |

| 0x000A - 0x000B                 | R      | 0             | 0           | 0            | 0            | 0       | 0 | 0     | 0          |

| Reserved                        | W      |               |             |              |              |         |   |       |            |

| 0x000C<br>ECCDDH                | R<br>W |               |             |              | DDATA        | A[15:8] |   |       |            |

| 0x000D<br>ECCDDL                | R<br>W | DDATA[7:0]    |             |              |              |         |   |       |            |

| 0x000E<br>ECCDE                 | R<br>W | 0 0 DECC[5:0] |             |              |              |         |   |       |            |

| 0x000F<br>ECCDCMD               | R<br>W | ECCDRR        | 0           | 0            | 0            | 0       | 0 | ECCDW | ECCDR      |

|                                 |        |               | = Unimplem  | ented, Reser | ved, Read as | s zero  |   |       |            |

Figure 7-1. SRAM\_ECC Register Summary

#### Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

Module Base + 0x0007

= Unimplemented or Reserved

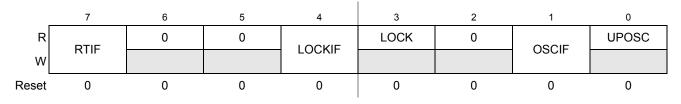

Figure 8-12. S12CPMU\_UHV\_V10\_V6 Flags Register (CPMUIFLG)

Read: Anytime

Write: Refer to each bit for individual write conditions

**Table 8-5. CPMUIFLG Field Descriptions**

| Field                                                                                                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 7<br>RTIF                                                                                                                                                                                                                                           | Real Time Interrupt Flag — RTIF is set to 1 at the end of the RTI period. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (RTIE=1), RTIF causes an interrupt request.  O RTI time-out has not yet occurred.  1 RTI time-out has occurred.                                                                                                                                                                                                                                            |  |  |  |  |

| PLL Lock Interrupt Flag — LOCKIF is set to 1 when LOCK status bit changes. This flag can o writing a 1. Writing a 0 has no effect. If enabled (LOCKIE=1), LOCKIF causes an interrupt requipment of the change in LOCK bit.  1 LOCK bit has changed. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 3<br>LOCK                                                                                                                                                                                                                                           | Lock Status Bit — LOCK reflects the current state of PLL lock condition. Writes have no effect. While PLL is unlocked (LOCK=0) f <sub>PLL</sub> is f <sub>VCO</sub> / 4 to protect the system from high core clock frequencies during the PLL stabilization time t <sub>lock</sub> .  0 VCOCLK is not within the desired tolerance of the target frequency. f <sub>PLL</sub> = f <sub>VCO</sub> /4.  1 VCOCLK is within the desired tolerance of the target frequency. f <sub>PLL</sub> = f <sub>VCO</sub> /(POSTDIV+1). |  |  |  |  |

| 1<br>OSCIF                                                                                                                                                                                                                                          | Oscillator Interrupt Flag — OSCIF is set to 1 when UPOSC status bit changes. This flag can only be cleared by writing a 1. Writing a 0 has no effect. If enabled (OSCIE=1), OSCIF causes an interrupt request.  0 No change in UPOSC bit.  1 UPOSC bit has changed.                                                                                                                                                                                                                                                      |  |  |  |  |

| 0<br>UPOSC                                                                                                                                                                                                                                          | Oscillator Status Bit — UPOSC reflects the status of the oscillator. Writes have no effect. Entering Full Stop Mode UPOSC is cleared.  O The oscillator is off or oscillation is not qualified by the PLL.  The oscillator is qualified by the PLL.                                                                                                                                                                                                                                                                      |  |  |  |  |

MC9S12ZVM Family Reference Manual Rev. 2.11 310 **NXP Semiconductors**

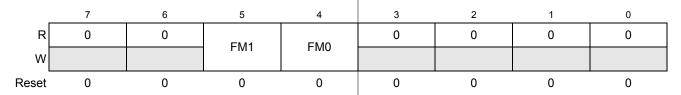

## 8.3.2.10 S12CPMU\_UHV\_V10\_V6 PLL Control Register (CPMUPLL)

This register controls the PLL functionality.

Module Base + 0x000A

Figure 8-15. S12CPMU\_UHV\_V10\_V6 PLL Control Register (CPMUPLL)

Read: Anytime

Write: Anytime if PROT=0 (CPMUPROT register) and PLLSEL=1 (CPMUCLKS register). Else write has no effect.

## **NOTE**

Write to this register clears the LOCK and UPOSC status bits.

## **NOTE**

Care should be taken to ensure that the bus frequency does not exceed the specified maximum when frequency modulation is enabled.

**Table 8-9. CPMUPLL Field Descriptions**

| Field | Description                                                                                                                                                                                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | PLL <b>Frequency Modulation Enable Bits</b> — FM1 and FM0 enable frequency modulation on the VCOCLK. This is to reduce noise emission. The modulation frequency is $f_{ref}$ divided by 16. See Table 8-10 for coding. |

Table 8-10. FM Amplitude selection

| FM1 | FM0 | FM Amplitude / f <sub>VCO</sub> Variation |

|-----|-----|-------------------------------------------|

| 0   | 0   | FM off                                    |

| 0   | 1   | ±1%                                       |

| 1   | 0   | ±2%                                       |

| 1   | 1   | ±4%                                       |

MC9S12ZVM Family Reference Manual Rev. 2.11

#### Chapter 8 S12 Clock, Reset and Power Management Unit (V10 and V6)

Several examples of PLL divider settings are shown in Table 8-34. The following rules help to achieve optimum stability and shortest lock time:

- Use lowest possible  $f_{VCO}$  /  $f_{REF}$  ratio (SYNDIV value).

- Use highest possible REFCLK frequency f<sub>REF</sub>.

Table 8-34. Examples of PLL Divider Settings

| f <sub>osc</sub> | REFDIV[3:0] | f <sub>REF</sub> | REFFRQ[1:0] | SYNDIV[5:0] | f <sub>VCO</sub> | VCOFRQ[1:0] | POSTDIV[4:0] | f <sub>PLL</sub> | f <sub>bus</sub> |

|------------------|-------------|------------------|-------------|-------------|------------------|-------------|--------------|------------------|------------------|

| off              | \$00        | 1MHz             | 00          | \$18        | 50MHz            | 01          | \$03         | 12.5MHz          | 6.25MHz          |

| off              | \$00        | 1MHz             | 00          | \$18        | 50MHz            | 01          | \$00         | 50MHz            | 25MHz            |

| 4MHz             | \$00        | 4MHz             | 01          | \$05        | 48MHz            | 00          | \$00         | 48MHz            | 24MHz            |

The phase detector inside the PLL compares the feedback clock (FBCLK = VCOCLK/(SYNDIV+1)) with the reference clock (REFCLK = (IRC1M or OSCCLK)/(REFDIV+1)). Correction pulses are generated based on the phase difference between the two signals. The loop filter alters the DC voltage on the internal filter capacitor, based on the width and direction of the correction pulse which leads to a higher or lower VCO frequency.

The user must select the range of the REFCLK frequency (REFFRQ[1:0] bits) and the range of the VCOCLK frequency (VCOFRQ[1:0] bits) to ensure that the correct PLL loop bandwidth is set.

The lock detector compares the frequencies of the FBCLK and the REFCLK. Therefore the speed of the lock detector is directly proportional to the reference clock frequency. The circuit determines the lock condition based on this comparison. So e.g. a failure in the reference clock will cause the PLL not to lock.

If PLL LOCK interrupt requests are enabled, the software can wait for an interrupt request and for instance check the LOCK bit. If interrupt requests are disabled, software can poll the LOCK bit continuously (during PLL start-up) or at periodic intervals. In either case, only when the LOCK bit is set, the VCOCLK will have stabilized to the programmed frequency.

- The LOCK bit is a read-only indicator of the locked state of the PLL.

- The LOCK bit is set when the VCO frequency is within the tolerance,  $\Delta_{Lock}$ , and is cleared when the VCO frequency is out of the tolerance,  $\Delta_{unl}$ .

Interrupt requests can occur if enabled (LOCKIE = 1) when the lock condition changes, toggling the LOCK bit.In case of loss of reference clock (e.g. IRCCLK) the PLL will not lock or if already locked, then it will unlock. The frequency of the VCOCLK will be very low and will depend on the value of the VCOFRQ[1:0] bits.

## 8.4.6.3 PLL Bypassed External Mode (PBE)

In this mode, the Bus Clock is based on the external oscillator clock. The reference clock for the PLL is based on the external oscillator.

The clock sources for COP and RTI can be based on the internal reference clock generator or on the external oscillator clock or the RC-Oscillator (ACLK).

This mode can be entered from default mode PEI by performing the following steps:

- 1. Make sure the PLL configuration is valid.

- 2. Enable the external Oscillator (OSCE bit)

- 3. Wait for the oscillator to start-up and the PLL being locked (LOCK = 1) and (UPOSC =1)

- 4. Clear all flags in the CPMUIFLG register to be able to detect any status bit change.

- 5. Optionally status interrupts can be enabled (CPMUINT register).

- 6. Select the Oscillator clock as source of the Bus clock (PLLSEL=0)

Loosing PLL lock status (LOCK=0) means loosing the oscillator status information as well (UPOSC=0).

The impact of loosing the oscillator status (UPOSC=0) in PBE mode is as follows:

- PLLSEL is set automatically and the Bus clock source is switched back to the PLL clock.

- The PLLCLK is derived from the VCO clock (with its actual frequency) divided by four until the PLL locks again.

## NOTEApplication software needs to be prepared to deal with the impact of loosing the oscillator status at any time.

When using the oscillator clock as system clock (write PLLSEL = 0) it is highly recommended to enable the oscillator clock monitor reset feature (write OMRE = 1 in CPMUOSC2 register). If the oscillator monitor reset feature is disabled (OMRE = 0) and the oscillator clock is used as system clock, the system might stall in case of loss of oscillation.

## 8.5 Resets

#### 8.5.1 General

All reset sources are listed in Table 8-35. There is only one reset vector for all these reset sources. Refer to MCU specification for reset vector address.

Reset Source

Local Enable

Power-On Reset (POR)

None

Low Voltage Reset (LVR)

None

External pin RESET

None

PLL Clock Monitor Reset

None

**Table 8-35. Reset Summary**

MC9S12ZVM Family Reference Manual Rev. 2.11

# Chapter 11 Timer Module (TIM16B4CV3) Block Description

#### Table 11-1. Revision History

| V03.03 | Jan,14,2013 | -single source generate different channel guide |

|--------|-------------|-------------------------------------------------|

|        |             | -single source generate unicrent channel guide  |

## 11.1 Introduction

The basic scalable timer consists of a 16-bit, software-programmable counter driven by a flexible programmable prescaler.

This timer can be used for many purposes, including input waveform measurements while simultaneously generating an output waveform.

This timer could contain up to 4 input capture/output compare channels. The input capture function is used to detect a selected transition edge and record the time. The output compare function is used for generating output signals or for timer software delays.

A full access for the counter registers or the input capture/output compare registers should take place in one clock cycle. Accessing high byte and low byte separately for all of these registers may not yield the same result as accessing them in one word.

#### **11.1.1** Features

The TIM16B4CV3 includes these distinctive features:

- Up to 4 channels available. (refer to device specification for exact number)

- All channels have same input capture/output compare functionality.

- Clock prescaling.

- 16-bit counter.

## 11.1.2 Modes of Operation

Stop: Timer is off because clocks are stopped.

Freeze: Timer counter keeps on running, unless TSFRZ in TSCR1 is set to 1.

Wait: Counters keeps on running, unless TSWAI in TSCR1 is set to 1.

Normal: Timer counter keep on running, unless TEN in TSCR1 is cleared to 0.

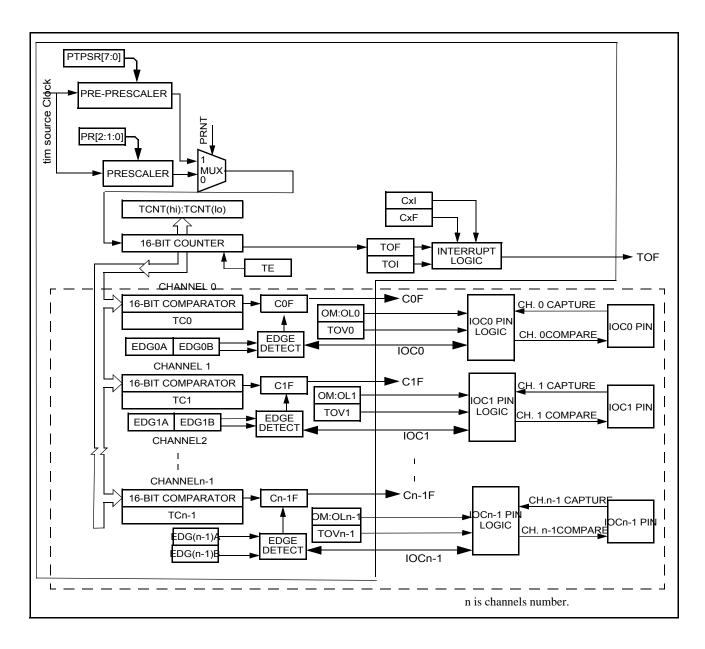

Figure 11-22. Detailed Timer Block Diagram

## 11.4.1 Prescaler

The prescaler divides the Bus clock by 1, 2, 4, 8, 16, 32, 64 or 128. The prescaler select bits, PR[2:0], select the prescaler divisor. PR[2:0] are in timer system control register 2 (TSCR2).

The prescaler divides the Bus clock by a prescalar value. Prescaler select bits PR[2:0] of in timer system control register 2 (TSCR2) are set to define a prescalar value that generates a divide by 1, 2, 4, 8, 16, 32, 64 and 128 when the PRNT bit in TSCR1 is disabled.

MC9S12ZVM Family Reference Manual Rev. 2.11

## 14.2.3 PTURE — PTUE Reload Event

If enabled (PTUREPE is set) this pin shows the internal reload event.

## 14.3 Memory Map and Register Definition

This section provides the detailed information of all registers for the PTU module.

## 14.3.1 Register Summary

Figure 14-2 shows the summary of all implemented registers inside the PTU module.

#### NOTE

Register Address = Module Base Address + Address Offset, where the Module Base Address is defined at the MCU level and the Address Offset is defined at the module level.

| Address Offset<br>Register Name |        | Bit 7   | 6          | 5       | 4      | 3       | 2          | 1       | Bit 0   |

|---------------------------------|--------|---------|------------|---------|--------|---------|------------|---------|---------|

| 0x0000<br>PTUE                  | R<br>W | 0       | PTUFRZ     | 0       | 0      | 0       | 0          | TG1EN   | TG0EN   |

| 0x0001                          | R      | 0       | 0          | 0       | 0      | 0       | 0          | 0       | PTULDOK |

| PTUC                            | W      |         |            |         |        |         |            |         | TTOLDOK |

| 0x0002                          | R      | 0       | 0          | 0       | 0      | 0       | 0          | 0       | PTUROIE |

| PTUIEH                          | W      |         |            |         |        |         |            |         | TOROL   |

| 0x0003<br>PTUIEL                | R<br>W | TG1AEIE | TG1REIE    | TG1TEIE | TG1DIE | TG0AEIE | TG0REIE    | TG0TEIE | TG0DIE  |

| 0x0004                          | R      | 0       | 0          | 0       | 0      | 0       | 0          | PTUDEEF | PTUROIF |

| PTUIFH                          | W      |         |            |         |        |         |            | TODELI  | TTOROII |

| 0x0005<br>PTUIFL                | R<br>W | TG1AEIF | TG1REIF    | TG1TEIF | TG1DIF | TG0AEIF | TG0REIF    | TG0TEIF | TG0DIF  |

| 0x0006                          | R      | 0       | 0          | 0       | 0      | 0       | 0          | 0       | TG0LIST |

| TG0LIST                         | W      |         |            |         |        |         |            |         | TGULIST |

| 0x0007                          | R      | 0       | 0          | 0       |        | Т       | G0TNUM[4:0 | )]      |         |

| TG0TNUM                         | W      |         |            |         |        |         |            |         |         |

| 0x0008<br>TG0TVH                | R      |         |            |         | TG0T\  | /[15:8] |            |         |         |

| IGUIVII                         | W      |         |            |         |        |         |            |         |         |

|                                 |        |         | = Unimplem | ented   |        |         |            |         |         |

Figure 14-2. PTU Register Summary

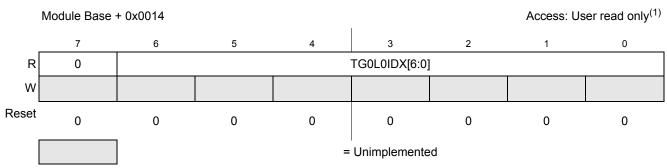

## 14.3.2.15 Trigger Generator 0 List 0 Index (TG0L0IDX)

Figure 14-17. Trigger Generator 0 List 0 Index (TG0L0IDX)

Read: Anytime Write: Never

Table 14-17. TG0L0IDX Register Field Descriptions

| Field                    | Description                                                                                                                                                                                                                                                                                                                           |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>TG0L0IDX<br>[6:0] | Trigger Generator 0 List 0 Index Register — This register defines offset of the start point for the trigger event list 0 used by trigger generator 0. This register is read only, so the list 0 for trigger generator 0 will start at the PTUPTR address. For more information see Section 14.4.2, "Memory based trigger event list". |

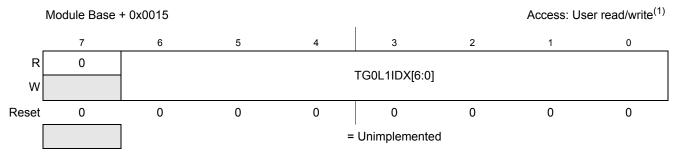

## 14.3.2.16 Trigger Generator 0 List 1 Index (TG0L1IDX)

Figure 14-18. Trigger Generator 0 List 1 Index (TG0L1IDX)

1. Read: Anytime

Write: Anytime, if TG0EN bit is cleared

Table 14-18. TG0L1IDX Register Field Descriptions

| Field                    | Description                                                                                                                                                                                                                                                                                    |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6:0<br>TG0L1IDX<br>[6:0] | Trigger Generator 0 List 1 Index Register — This register cannot be modified after the TG0EN bit is set. This register defines offset of the start point for the trigger event list 1 used by trigger generator 0. For more information see Section 14.4.2, "Memory based trigger event list". |

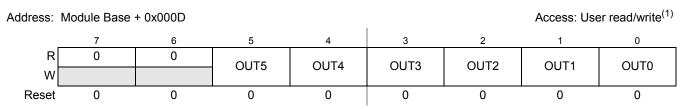

## **Table 15-16. PMFOUTC Field Descriptions**

| Field              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5–0<br>OUTCTL[5:0] | OUTCTLn Bits — These bits enable software control of their corresponding PWM output. When OUTCTLn is set, the OUTn bit takes over the directly controls the level of the PWMn output.  Note: OUTCTLn is buffered if ENCE is set. If ENCE is set, then the value written does not take effect until the next commutation cycle begins. Reading OUTCTLn returns the value in the buffer and not necessarily the value the output control is currently using. If ENCE is not set, then the OUTn bits take immediately effect when OUTCTLn bit is set. If the OUTCTLn bit is cleared then the OUTn control is disabled at the next PMF cycle start. |

|                    | When operating the PWM in complementary mode, these bits must be switched in pairs for proper operation. That is OUTCTL0 and OUTCTL1 must have the same value; OUTCTL2 and OUTCTL3 must have the same value; and OUTCTL4 and OUTCTL5 must have the same value. Otherwise see the behavior described on chapter Section 15.8.2, "BLDC 6-Step Commutation".  0 Software control disabled 1 Software control enabled n is 0, 1, 2, 3, 4 and 5.                                                                                                                                                                                                     |

## 15.3.2.11 PMF Output Control Bit Register (PMFOUTB)

Figure 15-14. PMF Output Control Bit Register (PMFOUTB)

1. Read: Anytime Write: Anytime

## **Table 15-17. PMFOUTB Field Descriptions**

| Field           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5–0<br>OUT[5:0] | OUT n Bits — If the corresponding OUTCTLn bit is set, these bits control the PWM outputs, illustrated in Table 15-18.  If the related OUTCTLn=1 a read returns the register contents OUTn else the current PWM output states are returned <sup>(1)</sup> On module version V3 the read returns always the register value.  Note: OUTn is buffered if ENCE is set. The value written does not take effect until the next commutation cycle begins. Reading OUTn (with OUTCTLn=1) returns the value in the buffer and not necessarily the value the output control is currently using.  n is 0. 1. 2. 3. 4 and 5. |  |  |

1. only valid for module version V4

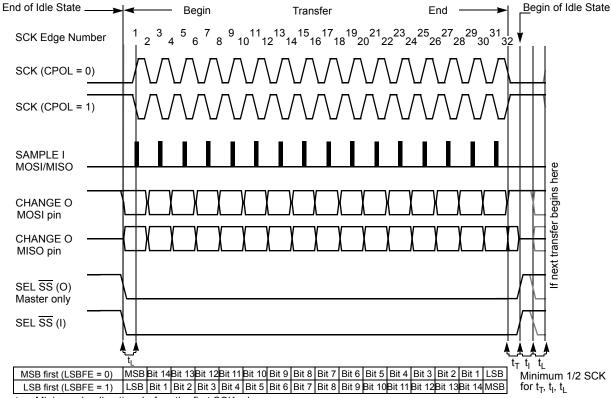

$t_L$  = Minimum leading time before the first SCK edge

Figure 17-13. SPI Clock Format 0 (CPHA = 0), with 16-Bit Transfer Width selected (XFRW = 1)

In slave mode, if the  $\overline{SS}$  line is not deasserted between the successive transmissions then the content of the SPI data register is not transmitted; instead the last received data is transmitted. If the  $\overline{SS}$  line is deasserted for at least minimum idle time (half SCK cycle) between successive transmissions, then the content of the SPI data register is transmitted.

In master mode, with slave select output enabled the  $\overline{SS}$  line is always deasserted and reasserted between successive transfers for at least minimum idle time.

#### 17.4.3.3 CPHA = 1 Transfer Format

Some peripherals require the first SCK edge before the first data bit becomes available at the data out pin, the second edge clocks data into the system. In this format, the first SCK edge is issued by setting the CPHA bit at the beginning of the n<sup>1</sup>-cycle transfer operation.

The first edge of SCK occurs immediately after the half SCK clock cycle synchronization delay. This first edge commands the slave to transfer its first data bit to the serial data input pin of the master.

A half SCK cycle later, the second edge appears on the SCK pin. This is the latching edge for both the master and slave.

1. n depends on the selected transfer width, please refer to Section 17.3.2.2, "SPI Control Register 2 (SPICR2)

MC9S12ZVM Family Reference Manual Rev. 2.11

t<sub>T</sub> = Minimum trailing time after the last SCK edge

$t_1$  = Minimum idling time between transfers (minimum  $\overline{SS}$  high time)

t<sub>1</sub>, t<sub>T</sub>, and t<sub>1</sub> are guaranteed for the master mode and required for the slave mode.

| Address Offset<br>Register Name  |   | Bit 7       | 6            | 5                       | 4           | 3                         | 2                  | 1          | Bit 0   |  |

|----------------------------------|---|-------------|--------------|-------------------------|-------------|---------------------------|--------------------|------------|---------|--|

| 0x0008                           | R | 0           | 0            | 0                       | 0           |                           | GBC                | I [3·0]    |         |  |

| GDUBCL                           | W |             |              |                         |             | - GBCL[3:0]               |                    |            |         |  |

| 0x0009                           | R | 0           | 0            | 0                       | 0           | 0                         | 0                  | CDU        | 1X[1:0] |  |

| GDUPHMUX                         | W |             |              |                         |             |                           |                    | GFIII      | 1/[1.0] |  |

| 0x000A                           | R | 0           |              | 00004[0:0]              |             | 0                         | 0.000010-01        |            |         |  |

| GDUCSO                           | W |             | - GCSO1[2:0] |                         |             |                           | - GCSO0[2:0]       |            |         |  |

| 0x000B                           | R | GDSFHS      |              | CDSI HSI3·0.            | 11010-01    |                           | GDSFLS GDS/L G/G G |            |         |  |

| GDUDSLVL                         | W | (2)         |              | GDSLHS[2:0] GDSLLS[2:0] |             |                           |                    |            |         |  |

| 0x000C                           | R | 0           | 0            | 0                       | 0           | 0                         |                    | GPHL[2:0]  |         |  |

| GDUPHL                           | W |             |              |                         |             |                           |                    |            |         |  |

| 0x000D                           | R | 0           | 0            | 0                       | 0           |                           | CCDC               | יסינטיט    |         |  |

| GDUCLK2                          | W |             |              |                         |             |                           | GCPC               | CD[3:0]    |         |  |

| 0x000E                           | R | 00040       | 00050        | 0                       |             | 0007                      | 2007014.01         | FOLA-03(2) |         |  |

| GDUOC0                           | W | GOCA0       | GOCE0        |                         |             | GOCT0[4:0] <sup>(2)</sup> |                    |            |         |  |

| 0x000F                           | R |             | 22251        | 0                       | 22271121(3) |                           |                    |            |         |  |

| GDUOC1                           | W | GOCA1       | GOCE1        |                         |             | GOCT1[4:0] <sup>(3)</sup> |                    |            |         |  |

| 0x0010<br>GDUCTR1 <sup>(4)</sup> | R | GSRMOD[1:0] | OD[1:0]      | 0                       | 0           | 0                         | 0                  | 0          | TDEL    |  |

|                                  | W |             | []           |                         |             |                           |                    |            |         |  |

| 0x0011-<br>0x001F                | ŀ |             |              |                         |             |                           |                    |            |         |  |

|                                  | [ |             |              |                         |             |                           |                    |            |         |  |

|                                  |   |             | = Unimplem   | ented                   |             |                           |                    |            |         |  |

Figure 18-2. GDU Register Summary

- 1. Not available on GDUV4

- 2. On GDUV4 only GOCT0[3:0] available

- 3. On GDUV4 only GOCT1[3:0] available

- 4. GDUCTR1 register availability is defined at device level.

## 18.3.2 Register Descriptions

This section consists of register descriptions in address order. Each description includes a standard register diagram with an associated figure number. Details of register bit and field function follow the register diagrams, in bit order. Unused bits read back zero.

Chapter 19 LIN/HV Physical Layer (S12LINPHYV3)

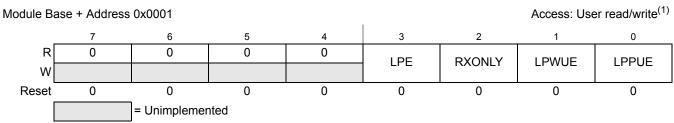

## 19.3.2.2 LIN Control Register (LPCR)

Figure 19-4. LIN Control Register (LPCR)

Read: Anytime

Write: Anytime,

**Table 19-3. LPCR Field Description**

| Field       | Description                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3<br>LPE    | <ul> <li>LIN Enable Bit — If set, this bit enables the LIN Physical Layer.</li> <li>The LIN Physical Layer is in shutdown mode. None of the LIN Physical Layer functions are available, except that the bus line is held in its recessive state by a high ohmic (330kΩ) resistor. All registers are normally accessible.</li> <li>The LIN Physical Layer is not in shutdown mode.</li> </ul> |  |  |

| 2<br>RXONLY | Receive Only Mode bit — This bit controls RXONLY mode.  0 The LIN Physical Layer is not in receive only mode.  1 The LIN Physical Layer is in receive only mode.                                                                                                                                                                                                                             |  |  |

| 1<br>LPWUE  | LIN Wake-Up Enable — This bit controls the wake-up feature in standby mode.  0 In standby mode the wake-up feature is disabled.  1 In standby mode the wake-up feature is enabled.                                                                                                                                                                                                           |  |  |

| 0<br>LPPUE  | LIN Pullup Resistor Enable — Selects pullup resistor. 0 The pullup resistor is high ohmic (330 k $\Omega$ ). 1 The 34 k $\Omega$ pullup is switched on (except if LPE=0 or when in standby mode with LPWUE=0).                                                                                                                                                                               |  |  |

**Table 20-9. FSEC Field Descriptions**

| Field           | Description                                                                                                                                                                                      |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                 | <b>Backdoor Key Security Enable Bits</b> — The KEYEN[1:0] bits define the enabling of backdoor key access to the Flash module as shown in Table 20-10.                                           |  |

| 5–2<br>RNV[5:2] | Reserved Nonvolatile Bits — The RNV bits should remain in the erased state for future enhancements.                                                                                              |  |

|                 | Flash Security Bits — The SEC[1:0] bits define the security state of the MCU as shown in Table 20-11. If the Flash module is unsecured using backdoor key access, the SEC bits are forced to 10. |  |

Table 20-10, Flash KEYEN States

| KEYEN[1:0] | Status of Backdoor Key Access |

|------------|-------------------------------|

| 00         | DISABLED                      |

| 01         | DISABLED <sup>(1)</sup>       |

| 10         | ENABLED                       |

| 11         | DISABLED                      |

<sup>1.</sup> Preferred KEYEN state to disable backdoor key access.

Table 20-11. Flash Security States

| SEC[1:0]   | Status of Security     |  |  |

|------------|------------------------|--|--|

| 00         | SECURED                |  |  |

| 01         | SECURED <sup>(1)</sup> |  |  |

| 10         | UNSECURED              |  |  |

| 11 SECURED |                        |  |  |

<sup>1.</sup> Preferred SEC state to set MCU to secured state.

The security function in the Flash module is described in Section 20.5.

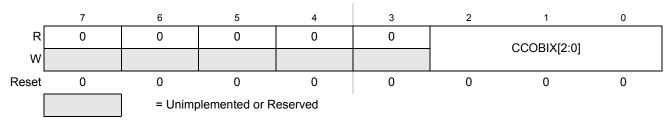

## 20.3.2.3 Flash CCOB Index Register (FCCOBIX)

The FCCOBIX register is used to indicate the amount of parameters loaded into the FCCOB registers for Flash memory operations.

Offset Module Base + 0x0002

Figure 20-7. FCCOB Index Register (FCCOBIX)

CCOBIX bits are readable and writable while remaining bits read 0 and are not writable.

MC9S12ZVM Family Reference Manual Rev. 2.11

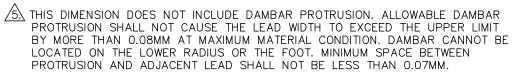

#### **Appendix K Package Information**

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

- 2. DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.

- 3. DATUMS A, B AND D TO BE DETERMINED AT DATUM PLANE H.

THIS DIMENSION DOES NOT INCLUDE MOLD PROTRUSION. ALLOWABLE PROTRUSION IS 0.25MM PER SIDE. THIS DIMENSION IS MAXIMUM PLASTIC BODY SIZE DIMENSION INCLUDING MOLD MISMATCH.

A EXACT SHAPE OF EACH CORNER IS OPTIONAL.

AND 0.25MM FROM THE LEAD TIP.

$\underline{\hat{igwedge}}$  hatched area to be keep out zone for PCB routing.

| FREESCALE SEMICONDUCTOR, INC.<br>ALL RIGHTS RESERVED. | MECHANICAL OUTLI | NE PRINT VERSION NOT TO SCALE   |  |  |

|-------------------------------------------------------|------------------|---------------------------------|--|--|

| TITLE: LQFP, 7 X 7 X 1.                               | 4 PKG,           | OCUMENT NO: 98ASAOO945D REV: XO |  |  |

| 0.5 PITCH, 48                                         |                  | STANDARD: NON-JEDEC             |  |  |

| 4.4 X 4.4 EXPOS                                       | ED PAD           | 02 NOV 2015                     |  |  |