Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                      |

|----------------------------|----------------------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                             |

| Core Processor             | ARM® Cortex®-M3                                                      |

| Core Size                  | 32-Bit Single-Core                                                   |

| Speed                      | 32MHz                                                                |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                           |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 64KB (64K x 8)                                                       |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 16K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                         |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                 |

| Oscillator Type            | Internal                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-VQFN Exposed Pad                                                  |

| Supplier Device Package    | 32-QFN (6x6)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g200f64-qfn32 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2.2 EFM32G210

The features of the EFM32G210 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

| Module    | Configuration                            | Pin Connections                               |

|-----------|------------------------------------------|-----------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                            |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                 |

| MSC       | Full configuration                       | NA                                            |

| DMA       | Full configuration                       | NA                                            |

| RMU       | Full configuration                       | NA                                            |

| EMU       | Full configuration                       | NA                                            |

| CMU       | Full configuration                       | CMU_OUT0, CMU_OUT1                            |

| WDOG      | Full configuration                       | NA                                            |

| PRS       | Full configuration                       | NA                                            |

| 12C0      | Full configuration                       | 12C0_SDA, 12C0_SCL                            |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS               |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS               |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                              |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                  |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                  |

| RTC       | Full configuration                       | NA                                            |

| LETIMER0  | Full configuration                       | LET0_0[1:0]                                   |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                  |

| ACMP0     | Full configuration                       | ACMP0_CH[1:0], ACMP0_O                        |

| ACMP1     | Full configuration                       | ACMP1_CH[7:5], ACMP1_O                        |

| VCMP      | Full configuration                       | NA                                            |

| ADC0      | Full configuration                       | ADC0_CH[7:4]                                  |

| DAC0      | Full configuration                       | DAC0_OUT[0]                                   |

| AES       | Full configuration                       | NA                                            |

| GPIO      | 24 pins                                  | Available pins are shown in Table 4.3 (p. 57) |

## Table 3.2. EFM32G210 Configuration Summary

### 3.2.3 EFM32G222

The features of the EFM32G222 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

| Module    | Configuration                            | Pin Connections                               |

|-----------|------------------------------------------|-----------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                            |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                 |

| MSC       | Full configuration                       | NA                                            |

| DMA       | Full configuration                       | NA                                            |

| RMU       | Full configuration                       | NA                                            |

| EMU       | Full configuration                       | NA                                            |

| CMU       | Full configuration                       | CMU_OUT0, CMU_OUT1                            |

| WDOG      | Full configuration                       | NA                                            |

| PRS       | Full configuration                       | NA                                            |

| 12C0      | Full configuration                       | 12C0_SDA, 12C0_SCL                            |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS               |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS               |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                              |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                  |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                  |

| TIMER2    | Full configuration                       | TIM2_CC[2:0]                                  |

| RTC       | Full configuration                       | NA                                            |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                   |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                  |

| PCNT1     | Full configuration, 8-bit count register | PCNT1_S[1:0]                                  |

| ACMP0     | Full configuration                       | ACMP0_CH[4:0], ACMP0_O                        |

| ACMP1     | Full configuration                       | ACMP1_CH[7:0], ACMP1_O                        |

| VCMP      | Full configuration                       | NA                                            |

| ADC0      | Full configuration                       | ADC0_CH[7:4]                                  |

| DAC0      | Full configuration                       | DAC0_OUT[1]                                   |

| AES       | Full configuration                       | NA                                            |

| GPIO      | 37 pins                                  | Available pins are shown in Table 4.3 (p. 57) |

## Table 3.3. EFM32G222 Configuration Summary

### 3.2.7 EFM32G290

The features of the EFM32G290 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

| Module    | Configuration                            | Pin Connections                                                   |

|-----------|------------------------------------------|-------------------------------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                                                |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                                     |

| MSC       | Full configuration                       | NA                                                                |

| DMA       | Full configuration                       | NA                                                                |

| RMU       | Full configuration                       | NA                                                                |

| EMU       | Full configuration                       | NA                                                                |

| CMU       | Full configuration                       | CMU_OUT0, CMU_OUT1                                                |

| WDOG      | Full configuration                       | NA                                                                |

| PRS       | Full configuration                       | NA                                                                |

| EBI       | Full configuration                       | EBI_ARDY, EBI_ALE, EBI_WEn, EBI_REn,<br>EBI_CS[3:0], EBI_AD[15:0] |

| 12C0      | Full configuration                       | 12C0_SDA, 12C0_SCL                                                |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS                                   |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS                                   |

| USART2    | Full configuration                       | US2_TX, US2_RX, US2_CLK, US2_CS                                   |

| UART0     | Full configuration                       | U0_TX, U0_RX                                                      |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                                                  |

| LEUART1   | Full configuration                       | LEU1_TX, LEU1_RX                                                  |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                                      |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                                      |

| TIMER2    | Full configuration                       | TIM2_CC[2:0]                                                      |

| RTC       | Full configuration                       | NA                                                                |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                                       |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                                      |

| PCNT1     | Full configuration, 8-bit count register | PCNT1_S[1:0]                                                      |

| PCNT2     | Full configuration, 8-bit count register | PCNT2_S[1:0]                                                      |

| ACMP0     | Full configuration                       | ACMP0_CH[7:0], ACMP0_O                                            |

| ACMP1     | Full configuration                       | ACMP1_CH[7:0], ACMP1_O                                            |

| VCMP      | Full configuration                       | NA                                                                |

| ADC0      | Full configuration                       | ADC0_CH[7:0]                                                      |

| DAC0      | Full configuration                       | DAC0_OUT[1:0]                                                     |

| AES       | Full configuration                       | NA                                                                |

| GPIO      | 90 pins                                  | Available pins are shown in Table 4.3 (p. 57)                     |

## Table 3.7. EFM32G290 Configuration Summary

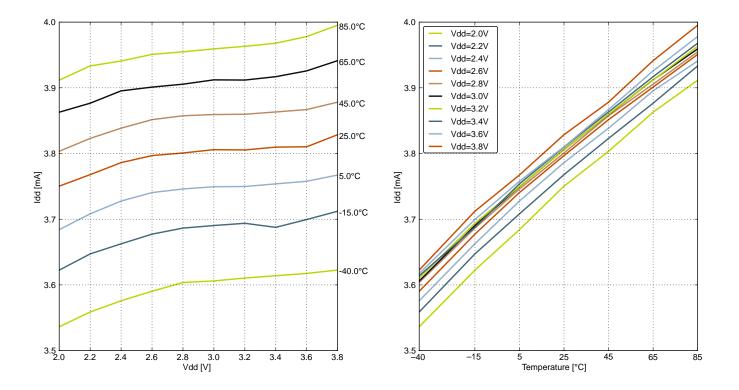

Figure 4.2. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 21 MHz

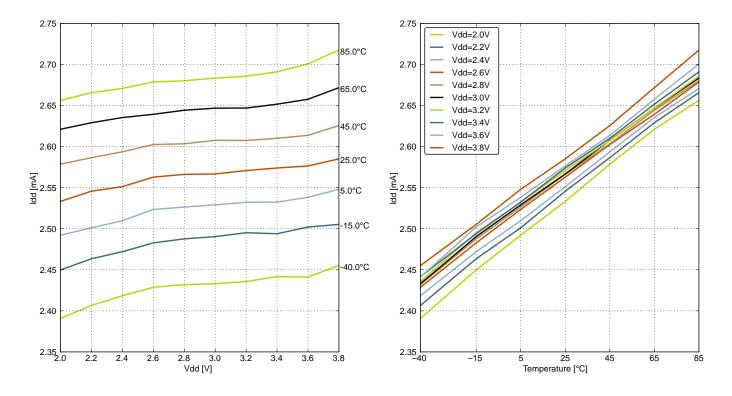

Figure 4.3. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 14 MHz

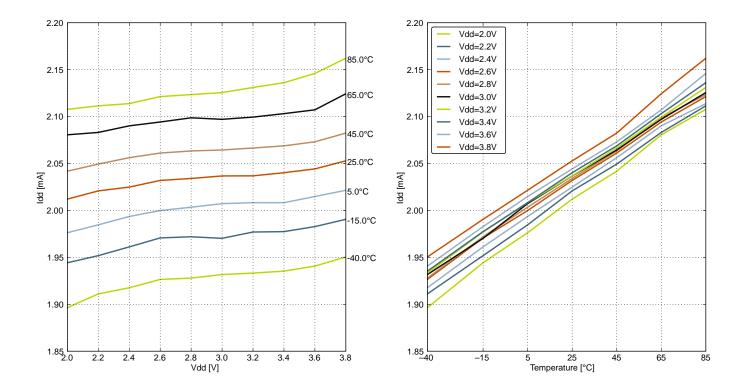

Figure 4.4. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 11 MHz

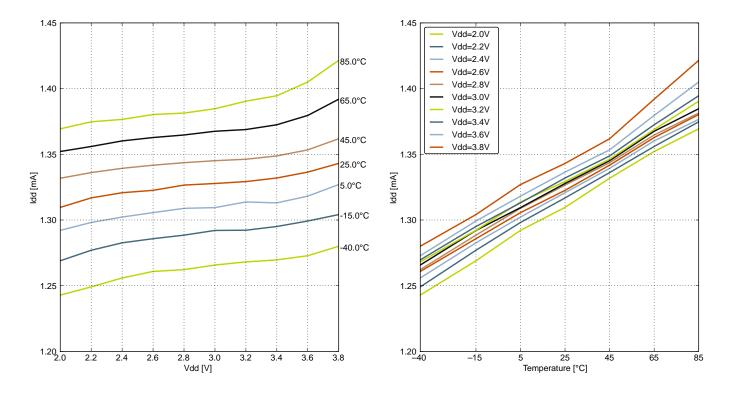

Figure 4.5. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 7 MHz

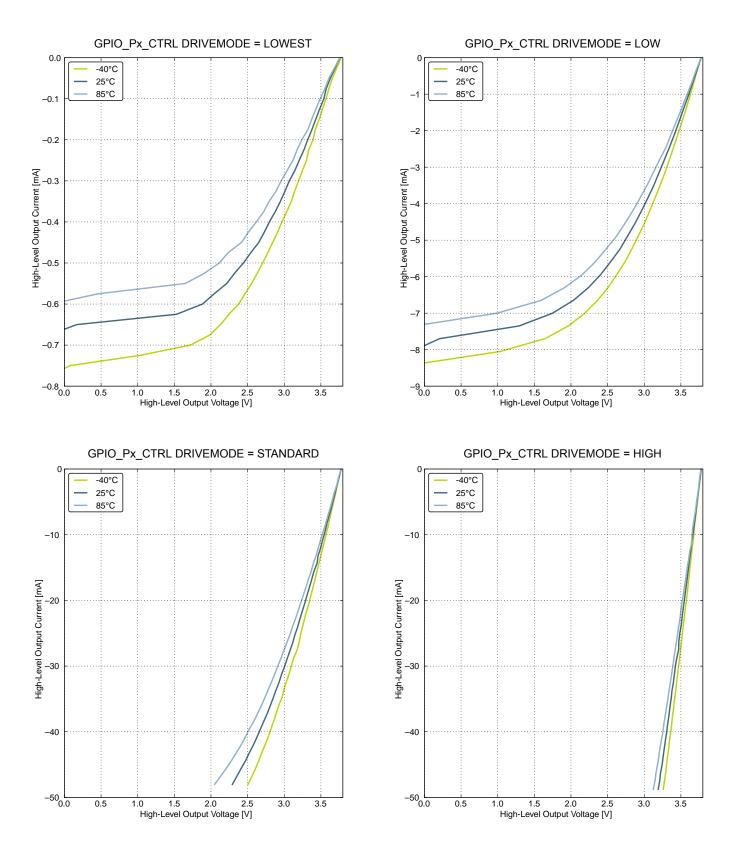

Figure 4.19. Typical High-Level Output Current, 3.8V Supply Voltage

| Parameter                                     | Symbol                      | Test Condition                              | Min   | Тур              | Max   | Unit   |

|-----------------------------------------------|-----------------------------|---------------------------------------------|-------|------------------|-------|--------|

|                                               |                             | 28 MHz frequency band                       | 27.16 | 28               | 28.84 | MHz    |

|                                               |                             | 21 MHz frequency band                       | 20.37 | 21               | 21.63 | MHz    |

| Oscillation frequency, V <sub>DD</sub> = 3.0  | £                           | 14 MHz frequency band                       | 13.58 | 14               | 14.42 | MHz    |

| V, T <sub>AMB</sub> =25 °C                    | fHFRCO                      | 11 MHz frequency band                       | 10.67 | 11               | 11.33 | MHz    |

|                                               |                             | 7 MHz frequency band                        | 6.402 | 6.6 <sup>1</sup> | 6.798 | MHz    |

|                                               |                             | 1 MHz frequency band                        | 1.164 | 1.2 <sup>2</sup> | 1.236 | MHz    |

| Settling time                                 | turnee w                    | After start-up, f <sub>HFRCO</sub> = 14 MHz | —     | 0.6              | —     | Cycles |

|                                               | t <sub>HFRCO_settling</sub> | After band switch                           | _     | 25               | —     | Cycles |

|                                               | IHFRCO                      | f <sub>HFRCO</sub> = 28 MHz                 | _     | 158              | 190   | μA     |

|                                               |                             | f <sub>HFRCO</sub> = 21 MHz                 |       | 125              | 155   | μA     |

| Current consumption (Produc-                  |                             | f <sub>HFRCO</sub> = 14 MHz                 | —     | 99               | 120   | μA     |

| tion test condition = 14 MHz)                 |                             | f <sub>HFRCO</sub> = 11 MHz                 | —     | 88               | 110   | μA     |

|                                               |                             | f <sub>HFRCO</sub> = 6.6 MHz                | —     | 72               | 90    | μA     |

|                                               |                             | f <sub>HFRCO</sub> = 1.2 MHz                | —     | 24               | 32    | μA     |

| Duty cycle                                    | DC <sub>HFRCO</sub>         | f <sub>HFRCO</sub> = 14 MHz                 | 48.5  | 50               | 51    | %      |

| Frequency step for LSB change in TUNING value | TUNESTEP <sub>HFRCO</sub>   |                                             | —     | 0.3 <sup>3</sup> | —     | %      |

#### Table 4.11. HFRCO

#### Note:

1. For devices with prod. rev. < 19, Typ = 7 MHz and Min/Max values not applicable.

2. For devices with prod. rev. < 19, Typ = 1 MHz and Min/Max values not applicable.

3. The TUNING field in the CMU\_HFRCOCTRL register may be used to adjust the HFRCO frequency. There is enough adjustment range to ensure that the frequency bands above 7 MHz will always have some overlap across supply voltage and temperature. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the HFRCO frequency at any arbitrary value between 7 MHz and 28 MHz across operating conditions.

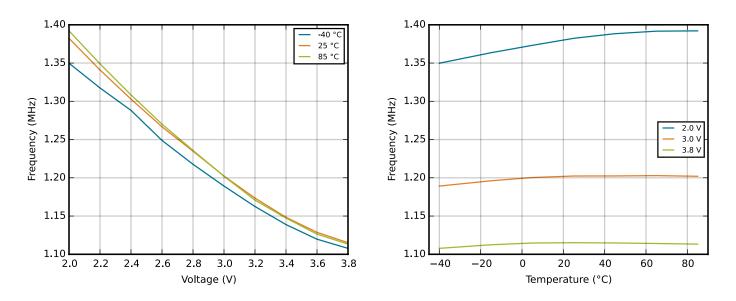

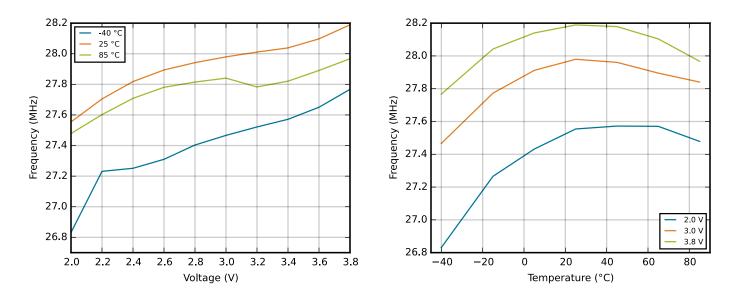

Figure 4.21. Calibrated HFRCO 1 MHz Band Frequency vs Supply Voltage and Temperature

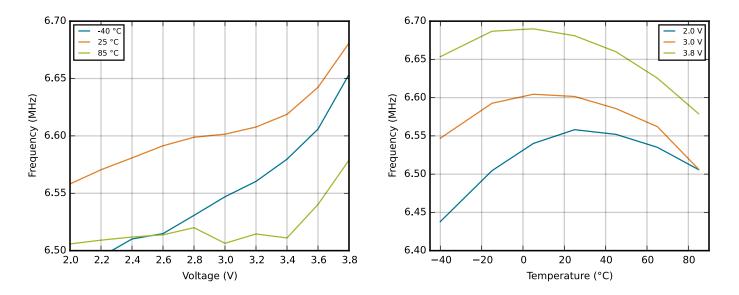

Figure 4.22. Calibrated HFRCO 7 MHz Band Frequency vs Supply Voltage and Temperature

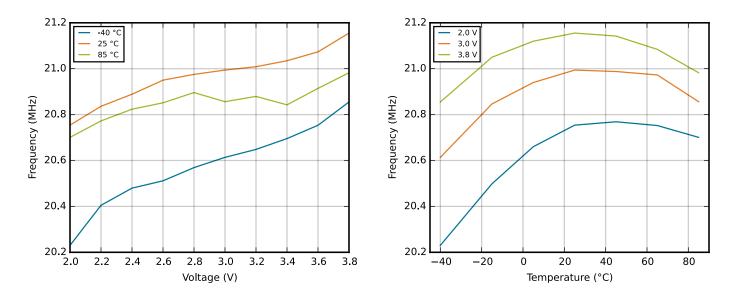

Figure 4.25. Calibrated HFRCO 21 MHz Band Frequency vs Supply Voltage and Temperature

Figure 4.26. Calibrated HFRCO 28 MHz Band Frequency vs Supply Voltage and Temperature

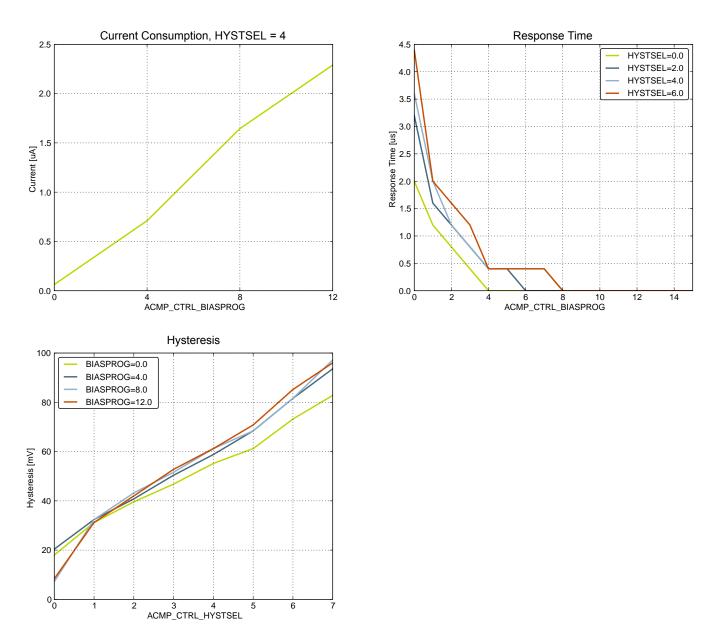

Figure 4.34. ACMP Characteristics, VDD = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1

| QFN32 P | in# and Name |        | Pin Alternate | Functionality / Description |            |

|---------|--------------|--------|---------------|-----------------------------|------------|

| Pin #   | Pin Name     | Analog | Timers        | Communication               | Other      |

| 31      | PE12         |        | TIM1_CC2 #1   | US0_CLK #0                  |            |

| 32      | PE13         |        |               | US0_CS #0                   | ACMP0_O #0 |

#### 5.10.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      |   |   | LOCATION                                                  |

|---------------|------|------|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                               |

| ACMP0_CH0     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                       |

| ACMP0_CH1     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                       |

| ACMP0_CH2     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                       |

| ACMP0_CH3     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                       |

| ACMP0_CH4     | PC4  |      |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |      |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |      |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |      |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 | PE2  |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                       |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP1, channel 1.                       |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP1, channel 2.                       |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP1, channel 3.                       |

| ACMP1_CH4     | PC12 |      |   |   | Analog comparator ACMP1, channel 4.                       |

| ACMP1_CH5     | PC13 |      |   |   | Analog comparator ACMP1, channel 5.                       |

| ACMP1_CH6     | PC14 |      |   |   | Analog comparator ACMP1, channel 6.                       |

| ACMP1_CH7     | PC15 |      |   |   | Analog comparator ACMP1, channel 7.                       |

| ACMP1_O       | PF2  | PE3  |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                            |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.             |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.             |

#### Table 5.29. Alternate functionality overview

| DIM | MIN      | NOM      | MAX  | DIM | MIN  | NOM  | MAX |

|-----|----------|----------|------|-----|------|------|-----|

| b   | 0.17     | 0.22     | 0.27 | S   | 0.20 | _    | —   |

| b1  | 0.17     | 0.20     | 0.23 | θ   | 0°   | 3.5° | 7°  |

| с   | 0.09     |          | 0.20 | θ1  | 0°   |      | _   |

| C1  | 0.09     |          | 0.16 | θ2  | 11°  | 12°  | 13° |

| D   | 12.0 BSC |          |      | θ3  | 11°  | 12°  | 13° |

| D1  | 10.0 BSC |          |      |     |      |      |     |

| е   |          | 0.50 BS( | 0    |     |      |      |     |

| E   | 12.0 BSC |          |      |     |      |      |     |

| E1  |          | 10.0 BS( | 0    |     |      |      |     |

| L   | 0.45     | 0.60     | 0.75 |     |      |      |     |

The TQFP64 Package is 10 by 10 mm in size and has a 0.5 mm pin pitch.

The TQFP64 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx.

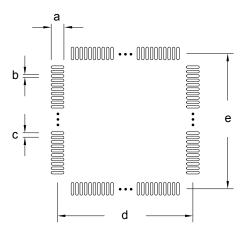

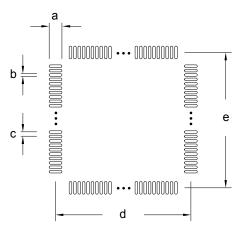

Figure 8.4. TQFP64 PCB Stencil Design

### Table 8.4. TQFP64 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.50      |

| b      | 0.20      |

| с      | 0.50      |

| d      | 11.50     |

| e      | 11.50     |

#### Note:

- 1. The drawings are not to scale.

- 2. All dimensions are in millimeters.

- 3. All drawings are subject to change without notice.

- 4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

- 5. Stencil thickness 0.125 mm.

- 6. For detailed pin-positioning, see Pin Definitions.

#### 9.2 TQFP48 PCB Layout

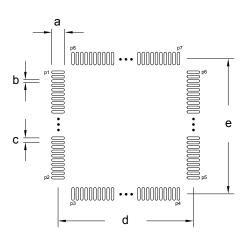

Figure 9.2. TQFP48 PCB Land Pattern

| Symbol | Dim. (mm) | Symbol | Pin Number | Symbol | Pin Number |

|--------|-----------|--------|------------|--------|------------|

| а      | 1.60      | P1     | 1          | P6     | 36         |

| b      | 0.30      | P2     | 12         | P7     | 37         |

| с      | 0.50      | P3     | 13         | P8     | 48         |

| d      | 8.50      | P4     | 24         |        |            |

| е      | 8.50      | P5     | 25         |        |            |

Figure 9.3. TQFP48 PCB Solder Mask

#### Table 9.3. TQFP48 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.72      |

| b      | 0.42      |

| с      | 0.50      |

| d      | 8.50      |

| e      | 8.50      |

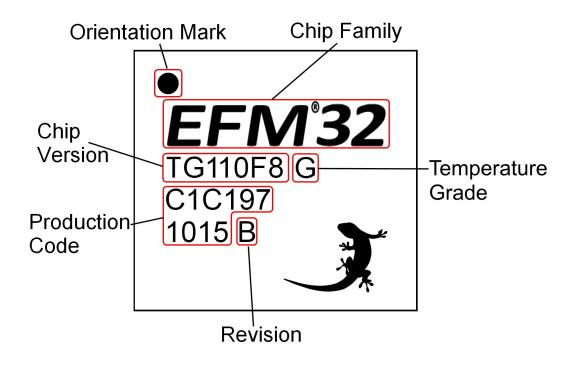

#### 9.3 TQFP48 Package Marking

In the illustration below package fields and position are shown.

## 10. QFN64 Package Specifications

### 10.1 QFN64 Package Dimensions

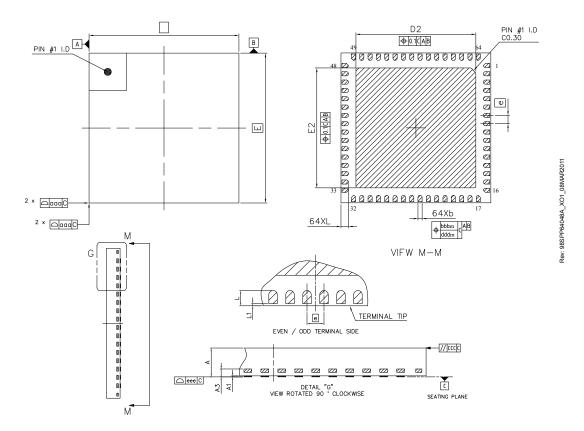

Figure 10.1. QFN64

#### Note:

- 1. Dimensioning & tolerancing confirm to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Dimension 'b' applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from the terminal tip. Dimension L1 represents terminal full back from package edge up to 0.1 mm isacceptable.

- 4. Coplanarity applies to the exposed heat slug as well as the terminal.

- 5. Radius on terminal is optional.

| Table 10.1. | QFN64 | (Dimensions in mm) |

|-------------|-------|--------------------|

|-------------|-------|--------------------|

| Symbol | Min       | Nom  | Мах  |

|--------|-----------|------|------|

| A      | 0.80      | 0.85 | 0.90 |

| A1     | 0.00      | _    | 0.05 |

| A3     | 0.203 REF |      |      |

| b      | 0.25      | 0.30 | 0.35 |

| D      | 9.00 BSC  |      |      |

| E      | 9.00 BSC  |      |      |

| D2     | 7.10      | 7.20 | 7.30 |

| E2     | 7.10      | 7.20 | 7.30 |

# 13. Revision History

## 13.1 Revision 2.10

July 19, 2017

In 4.8 General Purpose Input Output:

Added missing multiply symbols.

## In 4.10 Analog Digital Converter (ADC):

- Updated average active current.

- Updated SNR.

- Updated SINAD.

- Updated SFDR.

- Renamed VREF Output Voltage to VREF Voltage.

## In 4.11 Digital Analog Converter (DAC):

• Renamed VREF Output Voltage to VREF Voltage.

#### 13.9 Revision 1.40

February 27th, 2012

Updated Power Management section.

Corrected operating voltage from 1.8 V to 1.85 V.

Corrected TGRAD<sub>ADCTH</sub> parameter.

Corrected package drawing.

Updated PCB land pattern, solder mask and stencil design.

For LQFP48 devices, corrected available Pulse Counters from 3 to 2.

For LQFP48 devices, corrected available LEUARTs from 2 to 1.

For LQFP64 devices, corrected ordering codes in the ordering information table.

#### 13.10 Revision 1.30

May 20th, 2011

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

Updated LFXO load capacitance section.

## 13.13 Revision 1.10

September 13th, 2010

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

For LQFP100 devices, corrected number of GPIO pins.

Added typical values for  $\mathsf{R}_{\mathsf{ADCFILT}}$  and  $\mathsf{C}_{\mathsf{ADCFILT}}.$

Added two conditions for DAC clock frequency; one for sample/hold and one for sample/off.

Added RoHS information and specified leadframe/solderballs material.

Added Serial Bootloader to feature list and system summary.

Updated ADC characterization data.

Updated DAC characterization data.

Updated RCO characterization data.

Updated ACMP characterization data.

Updated VCMP characterization data.

#### 13.14 Revision 1.00

April 23rd, 2010

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880EFM32G890

ADC VCM line removed.

Added pinout illustration and additional pinout table.

Changed "Errata" chapter. Errata description moved to separate document.

Document changed status from "Preliminary".

Updated "Electrical Characteristics" chapter.

For EFM32G222

May 20th, 2011

Updated LFXO load capacitance section.