Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 24                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                             |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-VQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-QFN (6x6)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g200f64g-e-qfn32r |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1.14 Universal Asynchronous Receiver/Transmitter (UART)

The Universal Asynchronous serial Receiver and Transmitter (UART) is a very flexible serial I/O module. It supports full- and half-duplex asynchronous UART communication.

#### 3.1.15 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup>, the Low Energy UART, is a UART that allows two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud/ s. The LEUART includes all necessary hardware support to make asynchronous serial communication possible with minimum of software intervention and energy consumption.

#### 3.1.16 Timer/Counter (TIMER)

The 16-bit general purpose Timer has 3 compare/capture channels for input capture and compare/Pulse-Width Modulation (PWM) output. TIMER0 also includes a Dead-Time Insertion module suitable for motor control applications.

#### 3.1.17 Real Time Counter (RTC)

The Real Time Counter (RTC) contains a 24-bit counter and is clocked either by a 32.768 kHz crystal oscillator, or a 32.768 kHz RC oscillator. In addition to energy modes EM0 and EM1, the RTC is also available in EM2. This makes it ideal for keeping track of time since the RTC is enabled in EM2 where most of the device is powered down.

#### 3.1.18 Low Energy Timer (LETIMER)

The unique LETIMER<sup>TM</sup>, the Low Energy Timer, is a 16-bit timer that is available in energy mode EM2 in addition to EM1 and EM0. Because of this, it can be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. It is also connected to the Real Time Counter (RTC), and can be configured to start counting on compare matches from the RTC.

#### 3.1.19 Pulse Counter (PCNT)

The Pulse Counter (PCNT) can be used for counting pulses on a single input or to decode quadrature encoded inputs. It runs off either the internal LFACLK or the PCNTn\_S0IN pin as external clock source. The module may operate in energy mode EM0 - EM3.

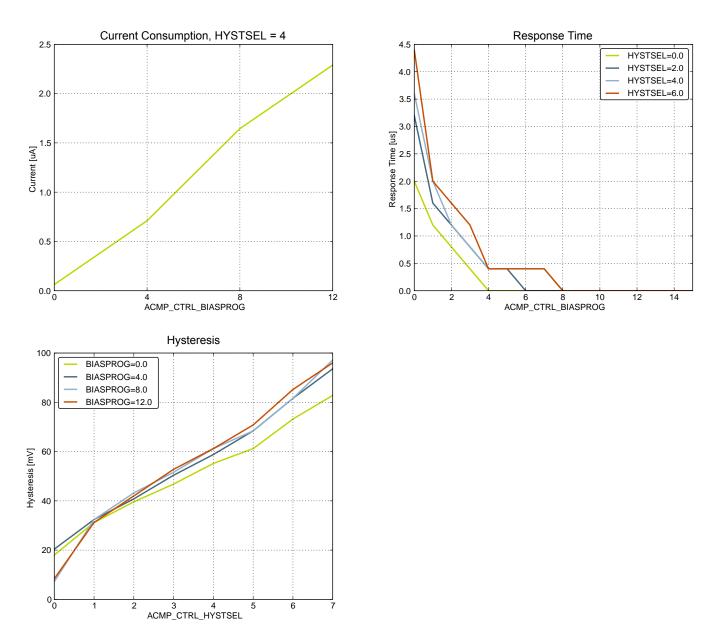

#### 3.1.20 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs can either be one of the selectable internal references or from external pins. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

#### 3.1.21 Voltage Comparator (VCMP)

The Voltage Supply Comparator is used to monitor the supply voltage from software. An interrupt can be generated when the supply falls below or rises above a programmable threshold. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

#### 3.1.22 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to one million samples per second. The integrated input mux can select inputs from 8 external pins and 6 internal signals.

#### 3.1.23 Digital to Analog Converter (DAC)

The Digital to Analog Converter (DAC) can convert a digital value to an analog output voltage. The DAC is fully differential rail-to-rail, with 12-bit resolution. It has two single-ended output buffers which can be combined into one differential output. The DAC may be used for a number of different applications such as sensor interfaces or sound output.

## 3.2.3 EFM32G222

The features of the EFM32G222 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

| Module    | Configuration                            | Pin Connections                               |

|-----------|------------------------------------------|-----------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                            |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                 |

| MSC       | Full configuration                       | NA                                            |

| DMA       | Full configuration                       | NA                                            |

| RMU       | Full configuration                       | NA                                            |

| EMU       | Full configuration                       | NA                                            |

| CMU       | Full configuration                       | CMU_OUT0, CMU_OUT1                            |

| WDOG      | Full configuration                       | NA                                            |

| PRS       | Full configuration                       | NA                                            |

| 12C0      | Full configuration                       | 12C0_SDA, 12C0_SCL                            |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS               |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS               |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                              |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                  |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                  |

| TIMER2    | Full configuration                       | TIM2_CC[2:0]                                  |

| RTC       | Full configuration                       | NA                                            |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                   |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                  |

| PCNT1     | Full configuration, 8-bit count register | PCNT1_S[1:0]                                  |

| ACMP0     | Full configuration                       | ACMP0_CH[4:0], ACMP0_O                        |

| ACMP1     | Full configuration                       | ACMP1_CH[7:0], ACMP1_O                        |

| VCMP      | Full configuration                       | NA                                            |

| ADC0      | Full configuration                       | ADC0_CH[7:4]                                  |

| DAC0      | Full configuration                       | DAC0_OUT[1]                                   |

| AES       | Full configuration                       | NA                                            |

| GPIO      | 37 pins                                  | Available pins are shown in Table 4.3 (p. 57) |

## Table 3.3. EFM32G222 Configuration Summary

### 4.4.5 EM4 Current Consumption

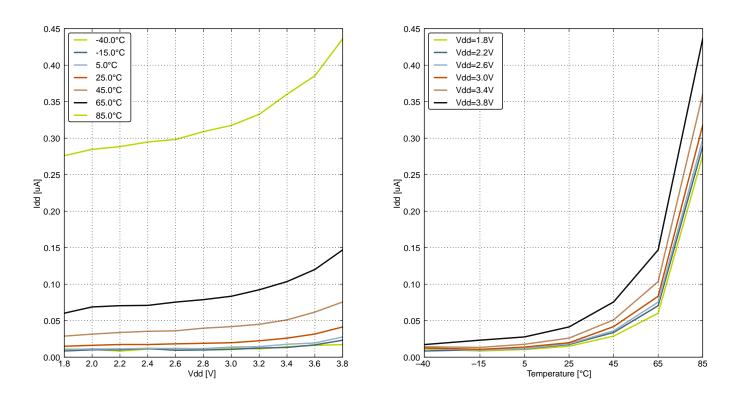

Figure 4.13. EM4 Current Consumption

### 4.5 Transition between Energy Modes

The transition times are measured from the trigger to the first clock edge in the CPU.

### Table 4.4. Energy Modes Transitions

| Parameter                       | Symbol            | Min | Тур | Max | Unit                |

|---------------------------------|-------------------|-----|-----|-----|---------------------|

| Transition time from EM1 to EM0 | t <sub>EM10</sub> | _   | 0   | —   | HFCORECLK<br>cycles |

| Transition time from EM2 to EM0 | t <sub>EM20</sub> | _   | 2   | —   | μs                  |

| Transition time from EM3 to EM0 | t <sub>EM30</sub> | _   | 2   | _   | μs                  |

| Transition time from EM4 to EM0 | t <sub>EM40</sub> | _   | 163 | _   | μs                  |

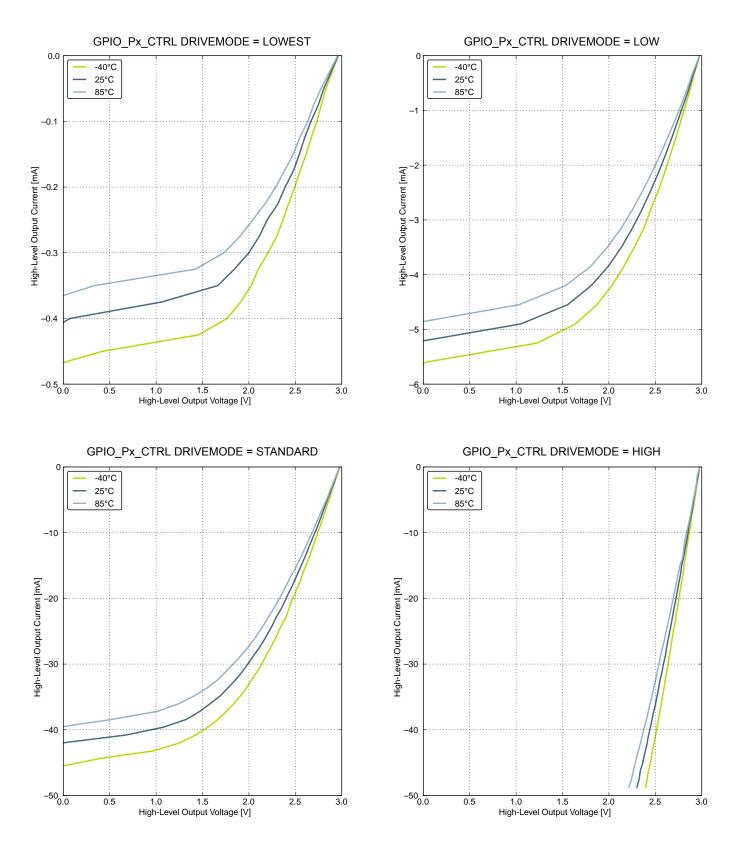

Figure 4.17. Typical High-Level Output Current, 3V Supply Voltage

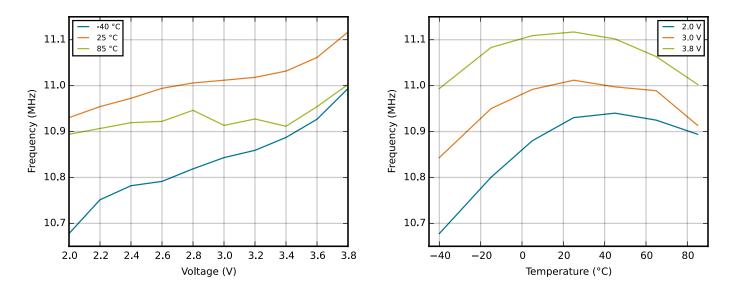

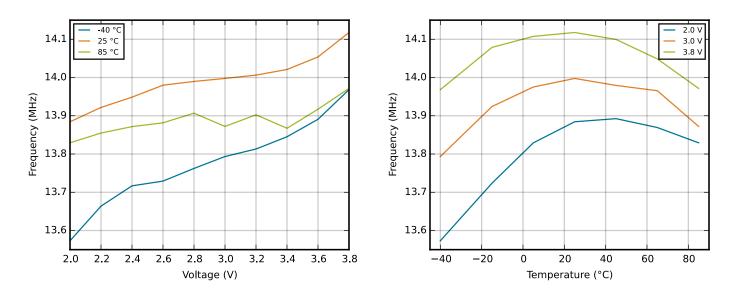

Figure 4.23. Calibrated HFRCO 11 MHz Band Frequency vs Supply Voltage and Temperature

Figure 4.24. Calibrated HFRCO 14 MHz Band Frequency vs Supply Voltage and Temperature

| Parameter                                       | Symbol               | Test Condition                                                                                                   | Min                                                                                                              | Тур | Max | Unit |

|-------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| Signal-to-Noise And Distortion<br>Ratio (SINAD) | SINAD <sub>ADC</sub> | 1 MSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 13 MHz,<br>BIASPROG = 0xF4B    |                                                                                                                  | 58  |     | dB   |

|                                                 |                      | 1 MSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B     |                                                                                                                  | 62  | _   | dB   |

|                                                 |                      | 1 MSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _                                                                                                                | 66  | _   | dB   |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B   | _                                                                                                                | 63  | _   | dB   |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _                                                                                                                | 66  | _   | dB   |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, 5 V reference, ADC_CLK =<br>13 MHz, BIASPROG = 0xF4B                    | —                                                                                                                | 66  | _   | dB   |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, V <sub>DD</sub> reference, ADC_CLK =<br>13 MHz, BIASPROG = 0xF4B        | 62                                                                                                               | 68  | _   | dB   |

|                                                 |                      |                                                                                                                  | 1 MSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B |     | 68  |      |

|                                                 |                      | 200 kSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747 | _                                                                                                                | 61  | _   | dB   |

|                                                 |                      | 200 kSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747    |                                                                                                                  | 62  | _   | dB   |

|                                                 |                      | 200 kSamples/s, 12 bit, single-<br>ended, VDD reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747               | _                                                                                                                | 66  |     | dB   |

|                                                 |                      | 200 kSamples/s, 12 bit, differen-<br>tial, internal 1.25 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747  | _                                                                                                                | 63  | _   | dB   |

|                                                 |                      | 200 kSamples/s, 12 bit, differen-<br>tial, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747   |                                                                                                                  | 66  | _   | dB   |

|                                                 |                      | 200 kSamples/s, 12 bit, differen-<br>tial, 5V reference, ADC_CLK= 7<br>MHz, BIASPROG = 0x747                     | —                                                                                                                | 66  | —   | dB   |

| Parameter                                      | Symbol                  | Test Condition                                                                                              | Min   | Тур               | Max                | Unit              |

|------------------------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------|-------|-------------------|--------------------|-------------------|

| Spurious-Free Dynamic Range<br>(SFDR)          | SFDR <sub>ADC</sub>     | 200 kSamples/s, 12 bit, differen-<br>tial, V <sub>DD</sub> reference, ADC_CLK =<br>7 MHz, BIASPROG = 0x747  | 68    | 79                | _                  | dBc               |

|                                                |                         | 200 kSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference,ADC_CLK<br>= 7 MHz, BIASPROG = 0x747 | _     | 79                |                    | dBc               |

| Offset voltage                                 | VADCOFFSET              | After calibration, single-ended                                                                             | _     | 0.3               |                    | mV                |

|                                                |                         | After calibration, differential                                                                             | -4    | 0.3               | 4                  | mV                |

| Thermometer output gradient                    | TGRAD <sub>ADCTH</sub>  |                                                                                                             | _     | -1.92             | _                  | mV/°C             |

|                                                |                         |                                                                                                             | —     | -6.3              |                    | ADC Co-<br>des/°C |

| Differential non-linearity (DNL)               | DNL <sub>ADC</sub>      | V <sub>DD</sub> = 3.0 V, external 2.5 V reference                                                           | -1    | ±0.7              | 4                  | LSB               |

| Integral non-linearity (INL), End point method | INL <sub>ADC</sub>      | V <sub>DD</sub> = 3.0 V, external 2.5 V ref-<br>erence                                                      | —     | ±1.2              | ±3                 | LSB               |

| Missing codes                                  | MC <sub>ADC</sub>       |                                                                                                             |       | _                 | 3                  | LSB               |

| Gain error drift                               | GAIN <sub>ED</sub>      | 1.25 V reference                                                                                            | _     | 0.01 <sup>2</sup> | 0.033 <sup>3</sup> | %/°C              |

|                                                |                         | 2.5 V reference                                                                                             | _     | 0.01 <sup>2</sup> | 0.03 <sup>3</sup>  | %/°C              |

| Offset error drift                             | OFFSET <sub>ED</sub>    | 1.25 V reference                                                                                            |       | 0.00 <sup>2</sup> | 0.06 <sup>3</sup>  | LSB/°C            |

|                                                |                         | 2.5 V reference                                                                                             |       | 0.00 <sup>2</sup> | 0.04 <sup>3</sup>  | LSB/°C            |

| VREF voltage                                   | V <sub>REF</sub>        | 1.25 V reference                                                                                            | 1.2   | 1.25              | 1.3                | V                 |

|                                                |                         | 2.5 V reference                                                                                             | 2.4   | 2.5               | 2.6                | V                 |

| VREF voltage drift                             | V <sub>REF_VDRIFT</sub> | 1.25 V reference                                                                                            | -12.4 | 2.9               | 18.2               | mV/V              |

|                                                |                         | 2.5 V reference, VDD > 2.5 V                                                                                | -24.6 | 5.7               | 35.2               | mV/V              |

| VREF temperature drift                         | VREF_TDRIFT             | 1.25 V reference                                                                                            | -132  | 272               | 677                | µV/°C             |

|                                                |                         | 2.5 V reference                                                                                             | -231  | 545               | 1271               | µV/°C             |

| VREF current consumption                       | I <sub>VREF</sub>       | 1.25 V reference                                                                                            | _     | 67                | 114                | μA                |

|                                                |                         | 2.5 V reference                                                                                             |       | 55                | 82                 | μA                |

| ADC and DAC VREF matching                      | V <sub>REF_MATCH</sub>  | 1.25 V reference                                                                                            | _     | 99.85             | _                  | %                 |

|                                                |                         | 2.5 V reference                                                                                             | _     | 100.01            |                    | %                 |

### Note:

1. Includes required contribution from the voltage reference.

2. Typical numbers given by abs(Mean) / (85 - 25).

3. Max number given by (abs(Mean) + 3x stddev) / (85 - 25).

The integral non-linearity (INL) and differential non-linearity parameters are explained in the following figures.

Figure 4.34. ACMP Characteristics, VDD = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1

#### 5.3.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      |   |   | LOCATION                                                  |

|---------------|------|------|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                               |

| ACMP0_CH0     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                       |

| ACMP0_CH1     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                       |

| ACMP0_CH2     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                       |

| ACMP0_CH3     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                       |

| ACMP0_CH4     | PC4  |      |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |      |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |      |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |      |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 |      |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                       |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP2, channel 1.                       |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP3, channel 2.                       |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP4, channel 3.                       |

| ACMP1_CH4     | PC12 |      |   |   | Analog comparator ACMP1, channel 4.                       |

| ACMP1_CH5     | PC13 |      |   |   | Analog comparator ACMP1, channel 5.                       |

| ACMP1_CH6     | PC14 |      |   |   | Analog comparator ACMP1, channel 6.                       |

| ACMP1_CH7     | PC15 |      |   |   | Analog comparator ACMP1, channel 7.                       |

| ACMP1_O       | PF2  |      |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                            |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.             |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.             |

### Table 5.8. Alternate functionality overview

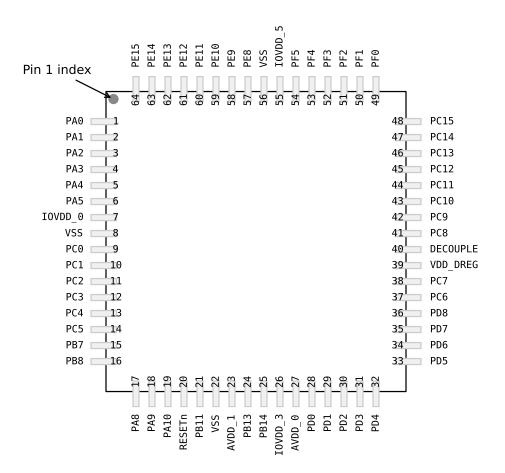

#### 5.4 EFM32G232 (TQFP64)

#### 5.4.1 Pinout

The EFM32G232 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.4. EFM32G232 Pinout (top view, not to scale)

#### Table 5.10. Device Pinout

|       | 64 Pin# and<br>Name |        | Pin Alternate | te Functionality / Description |             |  |  |

|-------|---------------------|--------|---------------|--------------------------------|-------------|--|--|

| Pin # | Pin Name            | Analog | Timers        | Communication                  | Other       |  |  |

| 1     | PA0                 |        | TIM0_CC0 #0/1 | I2C0_SDA #0                    |             |  |  |

| 2     | PA1                 |        | TIM0_CC1 #0/1 | I2C0_SCL #0                    | CMU_CLK1 #0 |  |  |

| 3     | PA2                 |        | TIM0_CC2 #0/1 |                                | CMU_CLK0 #0 |  |  |

| 4     | PA3                 |        | TIM0_CDTI0 #0 |                                |             |  |  |

| 5     | PA4                 |        | TIM0_CDTI1 #0 |                                |             |  |  |

### 5.6.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G290 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | PA15      | PA14      | PA13      | PA12      | PA11      | PA10      | PA9   | PA8   | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | PB15      | PB14      | PB13      | PB12      | PB11      | PB10      | PB9   | PB8   | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| Port C | PC15      | PC14      | PC13      | PC12      | PC11      | PC10      | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | PD15      | PD14      | PD13      | PD12      | PD11      | PD10      | PD9   | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | PE7   | PE6   | PE5   | PE4   | PE3   | PE2   | PE1   | PE0   |

| Port F | _         |           |           | _         |           |           | PF9   | PF8   | PF7   | PF6   | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

### Table 5.18. GPIO Pinout

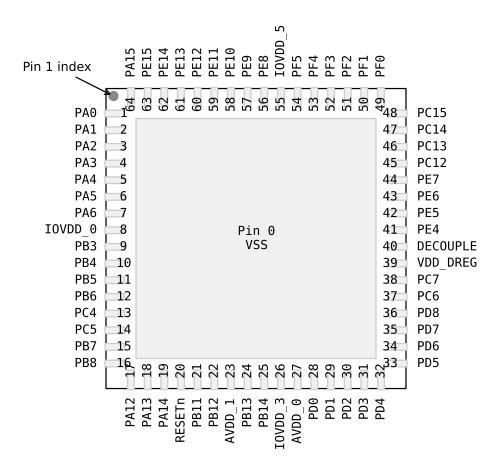

#### 5.7 EFM32G840 (QFN64)

### 5.7.1 Pinout

The EFM32G840 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.7. EFM32G840 Pinout (top view, not to scale)

#### Table 5.19. Device Pinout

| QFN64 P | in# and Name |           | Pin Alternate | Pin Alternate Functionality / Description |             |  |  |  |

|---------|--------------|-----------|---------------|-------------------------------------------|-------------|--|--|--|

| Pin #   | Pin Name     | Analog    | Timers        | Communication                             | Other       |  |  |  |

| 0       | VSS          | Ground.   |               |                                           |             |  |  |  |

| 1       | PA0          | LCD_SEG13 | TIM0_CC0 #0/1 | I2C0_SDA #0                               |             |  |  |  |

| 2       | PA1          | LCD_SEG14 | TIM0_CC1 #0/1 | I2C0_SCL #0                               | CMU_CLK1 #0 |  |  |  |

| 3       | PA2          | LCD_SEG15 | TIM0_CC2 #0/1 |                                           | CMU_CLK0 #0 |  |  |  |

| 4       | PA3          | LCD_SEG16 | TIM0_CDTI0 #0 |                                           |             |  |  |  |

| 5       | PA4          | LCD_SEG17 | TIM0_CDTI1 #0 |                                           |             |  |  |  |

| Alternate     |      |     |     |   | LOCATION                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------|-----|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1   | 2   | 3 | Description                                                                                                                                                                                                                                                                                                                                                             |

| EBI_ARDY      | PF2  |     |     |   | External Bus Interface (EBI) Hardware Ready Control input.                                                                                                                                                                                                                                                                                                              |

| EBI_CS0       | PD9  |     |     |   | External Bus Interface (EBI) Chip Select output 0.                                                                                                                                                                                                                                                                                                                      |

| EBI_CS1       | PD10 |     |     |   | External Bus Interface (EBI) Chip Select output 1.                                                                                                                                                                                                                                                                                                                      |

| EBI_CS2       | PD11 |     |     |   | External Bus Interface (EBI) Chip Select output 2.                                                                                                                                                                                                                                                                                                                      |

| EBI_CS3       | PD12 |     |     |   | External Bus Interface (EBI) Chip Select output 3.                                                                                                                                                                                                                                                                                                                      |

| EBI_REn       | PF5  |     |     |   | External Bus Interface (EBI) Read Enable output.                                                                                                                                                                                                                                                                                                                        |

| EBI_WEn       | PF4  |     |     |   | External Bus Interface (EBI) Write Enable output.                                                                                                                                                                                                                                                                                                                       |

| HFXTAL_N      | PB14 |     |     |   | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                                                                                                                                                                    |

| HFXTAL_P      | PB13 |     |     |   | High Frequency Crystal positive pin.                                                                                                                                                                                                                                                                                                                                    |

| I2C0_SCL      | PA1  | PD7 | PC7 |   | I2C0 Serial Clock Line input / output.                                                                                                                                                                                                                                                                                                                                  |

| I2C0_SDA      | PA0  | PD6 | PC6 |   | I2C0 Serial Data input / output.                                                                                                                                                                                                                                                                                                                                        |

| LCD_BCAP_N    | PA13 |     |     |   | LCD voltage booster (optional), boost capacitor, negative pin.<br>If using the LCD voltage booster, connect a 22 nF capacitor<br>between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                                                     |

| LCD_BCAP_P    | PA12 |     |     |   | LCD voltage booster (optional), boost capacitor, positive pin.<br>If using the LCD voltage booster, connect a 22 nF capacitor<br>between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                                                     |

| LCD_BEXT      | PA14 |     |     |   | <ul> <li>LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.</li> <li>An external LCD voltage may also be applied to this pin if the booster is not enabled.</li> <li>If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO.</li> </ul> |

| LCD_COM0      | PE4  |     |     |   | LCD driver common line number 0.                                                                                                                                                                                                                                                                                                                                        |

| LCD_COM1      | PE5  |     |     |   | LCD driver common line number 1.                                                                                                                                                                                                                                                                                                                                        |

| LCD_COM2      | PE6  |     |     |   | LCD driver common line number 2.                                                                                                                                                                                                                                                                                                                                        |

| LCD_COM3      | PE7  |     |     |   | LCD driver common line number 3.                                                                                                                                                                                                                                                                                                                                        |

| LCD_SEG0      | PF2  |     |     |   | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG1      | PF3  |     |     |   | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG2      | PF4  |     |     |   | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG3      | PF5  |     |     |   | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG4      | PE8  |     |     |   | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG5      | PE9  |     |     |   | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG6      | PE10 |     |     |   | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                                                    |

| Alternate     |      |      |   |   | LOCATION                                                                                           |

|---------------|------|------|---|---|----------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                                                                        |

| DAC0_OUT0     | PB11 |      |   |   | Digital to Analog Converter DAC0 output channel number 0.                                          |

| DAC0_OUT1     | PB12 |      |   |   | Digital to Analog Converter DAC0 output channel number 1.                                          |

|               |      |      |   |   | Debug-interface Serial Wire clock input.                                                           |

| DBG_SWCLK     | PF0  | PF0  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.              |

|               |      |      |   |   | Debug-interface Serial Wire data input / output.                                                   |

| DBG_SWDIO     | PF1  | PF1  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.                |

|               |      |      |   |   | Debug-interface Serial Wire viewer Output.                                                         |

| DBG_SWO       | PF2  | PC15 |   |   | Note that this function is not enabled after reset, and must be<br>enabled by software to be used. |

| EBI_AD00      | PE8  |      |   |   | External Bus Interface (EBI) address and data input / output pin 00.                               |

| EBI_AD01      | PE9  |      |   |   | External Bus Interface (EBI) address and data input / output pin 01.                               |

| EBI_AD02      | PE10 |      |   |   | External Bus Interface (EBI) address and data input / output pin 02.                               |

| EBI_AD03      | PE11 |      |   |   | External Bus Interface (EBI) address and data input / output pin 03.                               |

| EBI_AD04      | PE12 |      |   |   | External Bus Interface (EBI) address and data input / output pin 04.                               |

| EBI_AD05      | PE13 |      |   |   | External Bus Interface (EBI) address and data input / output pin 05.                               |

| EBI_AD06      | PE14 |      |   |   | External Bus Interface (EBI) address and data input / output pin 06.                               |

| EBI_AD07      | PE15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 07.                               |

| EBI_AD08      | PA15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 08.                               |

| EBI_AD09      | PA0  |      |   |   | External Bus Interface (EBI) address and data input / output pin 09.                               |

| EBI_AD10      | PA1  |      |   |   | External Bus Interface (EBI) address and data input / output pin 10.                               |

| EBI_AD11      | PA2  |      |   |   | External Bus Interface (EBI) address and data input / output pin 11.                               |

| EBI_AD12      | PA3  |      |   |   | External Bus Interface (EBI) address and data input / output pin 12.                               |

| EBI_AD13      | PA4  |      |   |   | External Bus Interface (EBI) address and data input / output pin 13.                               |

| EBI_AD14      | PA5  |      |   |   | External Bus Interface (EBI) address and data input / output pin 14.                               |

| EBI_AD15      | PA6  |      |   |   | External Bus Interface (EBI) address and data input / output pin 15.                               |

| EBI_ALE       | PF3  |      |   |   | External Bus Interface (EBI) Address Latch Enable output.                                          |

| Alternate     |      |     |     |      | LOCATION                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1   | 2   | 3    | Description                                                                                                                                                                                                                                                                                                                                                             |

| EBI_ARDY      | PF2  |     |     |      | External Bus Interface (EBI) Hardware Ready Control input.                                                                                                                                                                                                                                                                                                              |

| EBI_CS0       | PD9  |     |     |      | External Bus Interface (EBI) Chip Select output 0.                                                                                                                                                                                                                                                                                                                      |

| EBI_CS1       | PD10 |     |     |      | External Bus Interface (EBI) Chip Select output 1.                                                                                                                                                                                                                                                                                                                      |

| EBI_CS2       | PD11 |     |     |      | External Bus Interface (EBI) Chip Select output 2.                                                                                                                                                                                                                                                                                                                      |

| EBI_CS3       | PD12 |     |     |      | External Bus Interface (EBI) Chip Select output 3.                                                                                                                                                                                                                                                                                                                      |

| EBI_REn       | PF5  |     |     |      | External Bus Interface (EBI) Read Enable output.                                                                                                                                                                                                                                                                                                                        |

| EBI_WEn       | PF4  |     |     |      | External Bus Interface (EBI) Write Enable output.                                                                                                                                                                                                                                                                                                                       |

| HFXTAL_N      | PB14 |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                                                                                                                                                                    |

| HFXTAL_P      | PB13 |     |     |      | High Frequency Crystal positive pin.                                                                                                                                                                                                                                                                                                                                    |

| I2C0_SCL      | PA1  | PD7 | PC7 | PD15 | I2C0 Serial Clock Line input / output.                                                                                                                                                                                                                                                                                                                                  |

| I2C0_SDA      | PA0  | PD6 | PC6 | PD14 | I2C0 Serial Data input / output.                                                                                                                                                                                                                                                                                                                                        |

| LCD_BCAP_N    | PA13 |     |     |      | LCD voltage booster (optional), boost capacitor, negative pin.<br>If using the LCD voltage booster, connect a 22 nF capacitor<br>between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                                                     |

| LCD_BCAP_P    | PA12 |     |     |      | LCD voltage booster (optional), boost capacitor, positive pin.<br>If using the LCD voltage booster, connect a 22 nF capacitor<br>between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                                                     |

| LCD_BEXT      | PA14 |     |     |      | <ul> <li>LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.</li> <li>An external LCD voltage may also be applied to this pin if the booster is not enabled.</li> <li>If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO.</li> </ul> |

| LCD_COM0      | PE4  |     |     |      | LCD driver common line number 0.                                                                                                                                                                                                                                                                                                                                        |

| LCD_COM1      | PE5  |     |     |      | LCD driver common line number 1.                                                                                                                                                                                                                                                                                                                                        |

| LCD_COM2      | PE6  |     |     |      | LCD driver common line number 2.                                                                                                                                                                                                                                                                                                                                        |

| LCD_COM3      | PE7  |     |     |      | LCD driver common line number 3.                                                                                                                                                                                                                                                                                                                                        |

| LCD_SEG0      | PF2  |     |     |      | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG1      | PF3  |     |     |      | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG2      | PF4  |     |     |      | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG3      | PF5  |     |     |      | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG4      | PE8  |     |     |      | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG5      | PE9  |     |     |      | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG6      | PE10 |     |     |      | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                                                    |

Figure 6.4. BGA112 PCB Stencil Design

## Table 6.3. BGA112 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.33      |

| b      | 0.80      |

| d      | 8.00      |

| е      | 8.00      |

## Note:

1. The drawings are not to scale.

2. All dimensions are in millimeters.

3. All drawings are subject to change without notice.

4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

5. Stencil thickness 0.125 mm.

6. For detailed pin-positioning, see Pin Definitions.

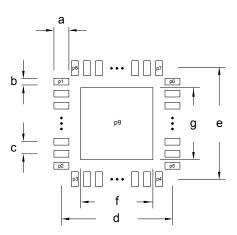

### 10.2 QFN64 PCB Layout

Figure 10.2. QFN64 PCB Land Pattern

### Table 10.2. QFN64 PCB Land Pattern Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Pin Number | Symbol | Pin Number |

|--------|-----------|--------|------------|--------|------------|

| а      | 0.85      | P1     | 1          | P8     | 64         |

| b      | 0.30      | P2     | 16         | P9     | 65         |

| С      | 0.50      | P3     | 17         |        |            |

| d      | 8.90      | P4     | 32         |        |            |

| e      | 8.90      | P5     | 33         |        |            |

| f      | 7.20      | P6     | 48         |        |            |

| g      | 7.20      | P7     | 49         |        |            |

Figure 10.3. QFN64 PCB Solder Mask

## Table 10.3. QFN64 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Dim. (mm) |

|--------|-----------|--------|-----------|

| а      | 0.97      | e      | 8.90      |

| b      | 0.42      | f      | 7.32      |

| с      | 0.50      | g      | 7.32      |

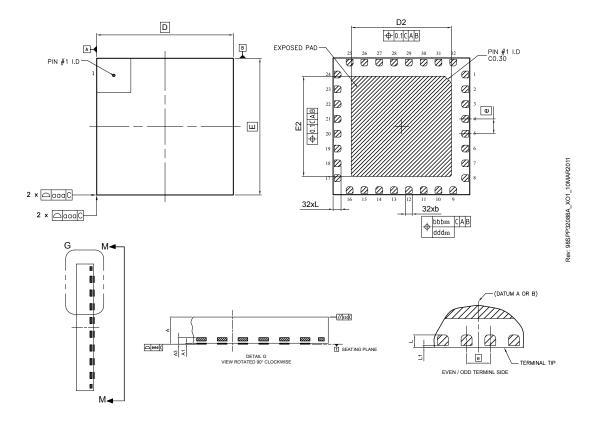

# 11. QFN32 Package Specifications

### 11.1 QFN32 Package Dimensions

Figure 11.1. QFN32

#### Note:

- 1. Dimensioning & tolerancing confirm to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Dimension 'b' applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from the terminal tip. Dimension L1 represents terminal full back from package edge up to 0.1 mm isacceptable.

- 4. Coplanarity applies to the exposed heat slug as well as the terminal.

- 5. Radius on terminal is optional.

| Symbol | А    | A1   | A3           | b    | D           | E           | D2   | E2   | е           | L    | L1   | aaa  | bbb  | ссс  | ddd  | eee  |

|--------|------|------|--------------|------|-------------|-------------|------|------|-------------|------|------|------|------|------|------|------|

| Min    | 0.80 | 0.00 |              | 0.25 |             |             | 4.30 | 4.30 |             | 0.30 | 0.00 |      |      |      |      |      |

| Nom    | 0.85 | _    | 0.203<br>REF | 0.30 | 6.00<br>BSC | 6.00<br>BSC | 4.40 | 4.40 | 0.65<br>BSC | 0.35 |      | 0.10 | 0.10 | 0.10 | 0.05 | 0.08 |

| Max    | 0.90 | 0.05 |              | 0.35 |             |             | 4.50 | 4.50 |             | 0.40 | 0.10 |      |      |      |      |      |

| Table 11.1. | QFN32 | (Dimensions | in mm) |

|-------------|-------|-------------|--------|

|-------------|-------|-------------|--------|

The QFN32 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx

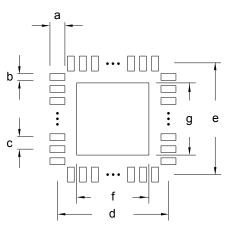

### 11.2 QFN32 PCB Layout

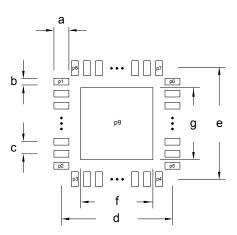

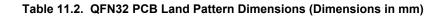

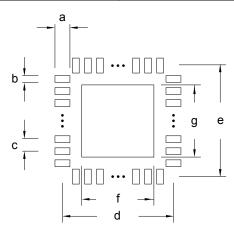

Figure 11.2. QFN32 PCB Land Pattern

| Symbol | Dim. (mm) | Symbol | Pin Number | Symbol | Pin Number |

|--------|-----------|--------|------------|--------|------------|

| а      | 0.80      | P1     | 1          | P6     | 24         |

| b      | 0.35      | P2     | 8          | P7     | 25         |

| С      | 0.65      | P3     | 9          | P8     | 32         |

| d      | 6.00      | P4     | 16         | P9     | 33         |

| е      | 6.00      | P5     | 17         |        |            |

| f      | 4.40      |        |            |        |            |

| g      | 4.40      |        |            |        |            |

Figure 11.3. QFN32 PCB Solder Mask

### Table 11.3. QFN32 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.92      |

| b      | 0.47      |

| с      | 0.65      |

#### 13.19 Revision 0.82

December 9th, 2009

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

For LQFP100 devices, incorrect pin 0 removed from pinout table.

Updated contact information.

ADC current consumption numbers updated in ADC Electrical Characteristics.

For devices with LCD, updated LCD supply voltage range in LCD Electrical Characteristics.

#### 13.20 Revision 0.81

November 20th, 2009

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

For devices without a differential DAC, System Summary updated.

Electrical Characteristics updated.

Storage temperature in Electrical Characteristics updated.

Temperature coefficient of band-gap reference in Electrical Characteristics added.

Erase times in Flash Electrical Characteristics updated.

Definitions of DNL and INL added in ADC section.

For devices with and LCD, LCD Electrical Characteristics added.

Current consumption of digital peripherals added in Electrical Characteristics.

For LQFP100 devices, package information in Pinout and Package corrected.

For BGA112 devices, pinout information in Pinout table corrected.

Updated errata section.