Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                            |

| Data Converters            | A/D 4x12b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-TQFP                                                                 |

| Supplier Device Package    | 48-TQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g222f32g-e-qfp48 |

# 3.2.5 EFM32G232

The features of the EFM32G232 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

Table 3.5. EFM32G232 Configuration Summary

| Module    | Configuration                            | Pin Connections                               |  |  |  |  |

|-----------|------------------------------------------|-----------------------------------------------|--|--|--|--|

| Cortex-M3 | Full configuration                       | NA                                            |  |  |  |  |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                 |  |  |  |  |

| MSC       | Full configuration                       | NA                                            |  |  |  |  |

| DMA       | Full configuration                       | NA                                            |  |  |  |  |

| RMU       | Full configuration                       | NA                                            |  |  |  |  |

| EMU       | Full configuration                       | NA                                            |  |  |  |  |

| СМИ       | Full configuration                       | CMU_OUT0, CMU_OUT1                            |  |  |  |  |

| WDOG      | Full configuration                       | NA                                            |  |  |  |  |

| PRS       | Full configuration                       | NA                                            |  |  |  |  |

| I2C0      | Full configuration                       | I2C0_SDA, I2C0_SCL                            |  |  |  |  |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS               |  |  |  |  |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS               |  |  |  |  |

| USART2    | Full configuration                       | US2_TX, US2_RX, US2_CLK, US2_CS               |  |  |  |  |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                              |  |  |  |  |

| LEUART1   | Full configuration                       | LEU1_TX, LEU1_RX                              |  |  |  |  |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                  |  |  |  |  |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                  |  |  |  |  |

| TIMER2    | Full configuration                       | TIM2_CC[2:0]                                  |  |  |  |  |

| RTC       | Full configuration                       | NA                                            |  |  |  |  |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                   |  |  |  |  |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                  |  |  |  |  |

| PCNT1     | Full configuration, 8-bit count register | PCNT1_S[1:0]                                  |  |  |  |  |

| PCNT2     | Full configuration, 8-bit count register | PCNT2_S[1:0]                                  |  |  |  |  |

| ACMP0     | Full configuration                       | ACMP0_CH[7:0], ACMP0_O                        |  |  |  |  |

| ACMP1     | Full configuration                       | ACMP1_CH[15:8], ACMP1_O                       |  |  |  |  |

| VCMP      | Full configuration                       | NA                                            |  |  |  |  |

| ADC0      | Full configuration                       | ADC0_CH[7:0]                                  |  |  |  |  |

| DAC0      | Full configuration                       | DAC0_OUT[0]                                   |  |  |  |  |

| AES       | Full configuration                       | NA                                            |  |  |  |  |

| GPIO      | 53 pins                                  | Available pins are shown in Table 4.3 (p. 57) |  |  |  |  |

| Module | Module             | Module                                                        |

|--------|--------------------|---------------------------------------------------------------|

| LCD    | Full configuration | LCD_SEG[39:0], LCD_COM[3:0], LCD_BCAP_P, LCD_BCAP_N, LCD_BEXT |

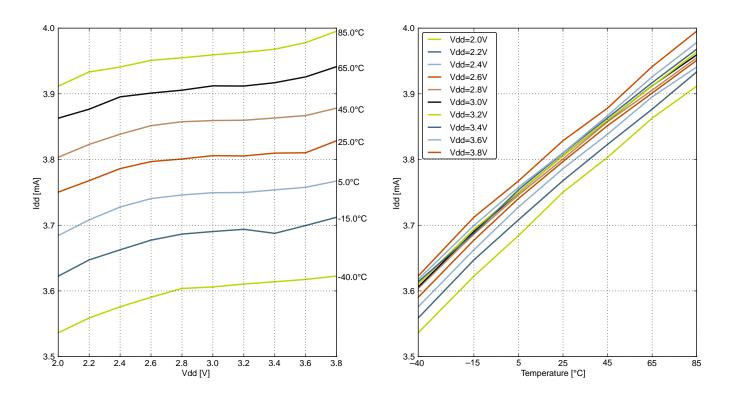

Figure 4.2. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 21 MHz

Figure 4.3. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 14 MHz

# 4.4.3 EM2 Current Consumption

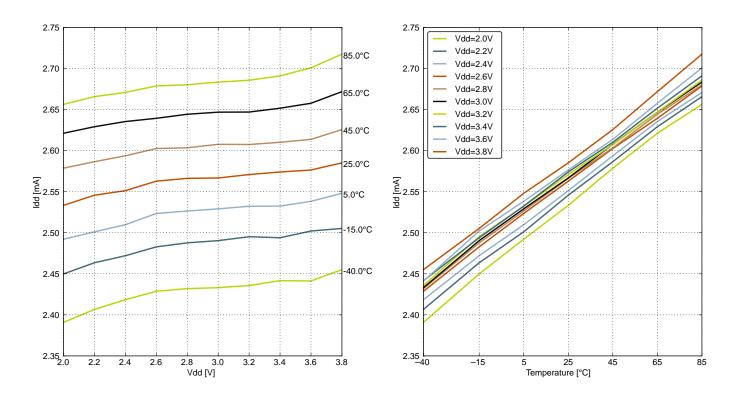

Figure 4.11. EM2 Current Consumption, RTC prescaled to 1 kHz, 32.768 kHz LFRCO

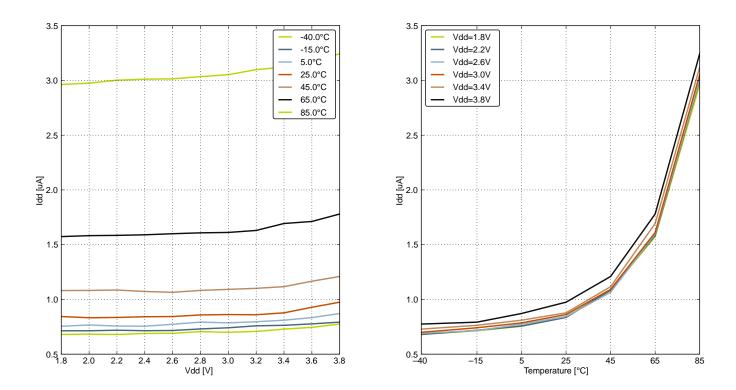

# 4.8 General Purpose Input Output

Table 4.7. GPIO

| Parameter                                          | Symbol            | Test Condition                                                                  | Min                               | Тур                  | Max                               | Unit |

|----------------------------------------------------|-------------------|---------------------------------------------------------------------------------|-----------------------------------|----------------------|-----------------------------------|------|

| Input low voltage                                  | V <sub>IOIL</sub> |                                                                                 | _                                 | _                    | 0.30×V <sub>DD</sub> <sup>1</sup> | V    |

| Input high voltage                                 | V <sub>IOIH</sub> |                                                                                 | 0.70×V <sub>DD</sub> <sup>1</sup> | _                    | _                                 | V    |

|                                                    | Vіоон             | Sourcing 0.1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST | _                                 | 0.80×V <sub>DD</sub> | _                                 | V    |

|                                                    |                   | Sourcing 0.1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST  | _                                 | 0.90×V <sub>DD</sub> | _                                 | V    |

|                                                    |                   | Sourcing 1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW      | _                                 | 0.85×V <sub>DD</sub> | _                                 | V    |

| Output high voltage (Production                    |                   | Sourcing 1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW       | _                                 | 0.90×V <sub>DD</sub> | _                                 | V    |

| test condition = 3.0 V, DRIVE-<br>MODE = STANDARD) |                   | Sourcing 6 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD | 0.75×V <sub>DD</sub>              | _                    | _                                 | V    |

|                                                    |                   | Sourcing 6 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD  | 0.85×V <sub>DD</sub>              | _                    | _                                 | V    |

|                                                    |                   | Sourcing 20 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH    | 0.60×V <sub>DD</sub>              | _                    | _                                 | V    |

|                                                    |                   | Sourcing 20 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH     | 0.80×V <sub>DD</sub>              | _                    | _                                 | V    |

Figure 4.15. Typical High-Level Output Current, 2V Supply Voltage

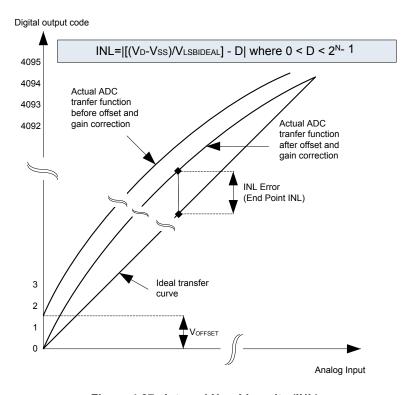

Figure 4.27. Integral Non-Linearity (INL)

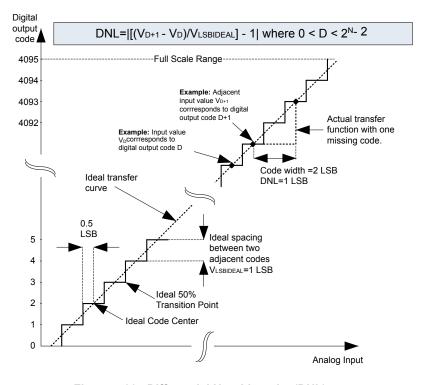

Figure 4.28. Differential Non-Linearity (DNL)

| QFN64 P | in# and Name |                  | Pin Alternate                                                                                                                                                                         | Functionality / Description |             |  |  |  |  |  |

|---------|--------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------|--|--|--|--|--|

| Pin#    | Pin Name     | Analog           | Timers                                                                                                                                                                                | Communication               | Other       |  |  |  |  |  |

| 6       | PA5          |                  | TIM0_CDTI2 #0                                                                                                                                                                         | LEU1_TX #1                  |             |  |  |  |  |  |

| 6       | PA6          |                  |                                                                                                                                                                                       | LEU1_RX #1                  |             |  |  |  |  |  |

| 8       | IOVDD_0      | Digital IO power | Digital IO power supply 0.                                                                                                                                                            |                             |             |  |  |  |  |  |

| 9       | PC0          |                  | PCNT0_S0IN #1                                                                                                                                                                         | US1_TX #0                   |             |  |  |  |  |  |

| 10      | PC1          |                  | PCNT0_S1IN #1                                                                                                                                                                         | US1_RX #0                   |             |  |  |  |  |  |

| 11      | PC2          |                  |                                                                                                                                                                                       | US2_CLK #0                  |             |  |  |  |  |  |

| 12      | PC3          |                  |                                                                                                                                                                                       | US2_CS #0                   |             |  |  |  |  |  |

| 13      | PC4          | ACMP0_CH4        | LETIM0_OUT0 #3<br>PCNT1_S0IN #0                                                                                                                                                       | US2_CLK #0                  |             |  |  |  |  |  |

| 14      | PC5          | ACMP0_CH5        | LETIM0_OUT1 #3<br>PCNT1_S1IN #0                                                                                                                                                       | US2_CS #0                   |             |  |  |  |  |  |

| 15      | PB7          | LFXTAL_P         |                                                                                                                                                                                       | US1_CLK #0                  |             |  |  |  |  |  |

| 16      | PB8          | LFXTAL_N         |                                                                                                                                                                                       | US1_CS #0                   |             |  |  |  |  |  |

| 17      | PA8          |                  | TIM2_CC0 #0                                                                                                                                                                           |                             |             |  |  |  |  |  |

| 18      | PA9          |                  | TIM2_CC1 #0                                                                                                                                                                           |                             |             |  |  |  |  |  |

| 19      | PA10         |                  | TIM2_CC2 #0                                                                                                                                                                           |                             |             |  |  |  |  |  |

| 20      | RESETn       |                  | set input, active low.To apply an external reset source to this pin, it is required to only drive this pin lov ing reset, and let the internal pull-up ensure that reset is released. |                             |             |  |  |  |  |  |

| 21      | PB11         | DAC0_OUT0        | LETIM0_OUT0 #1                                                                                                                                                                        |                             |             |  |  |  |  |  |

| 22      | PB12         | DAC0_OUT1        | LETIM0_OUT1 #1                                                                                                                                                                        |                             |             |  |  |  |  |  |

| 23      | AVDD_1       | Analog power s   | supply 1.                                                                                                                                                                             |                             |             |  |  |  |  |  |

| 24      | PB13         | HFXTAL_P         |                                                                                                                                                                                       | LEU0_TX #1                  |             |  |  |  |  |  |

| 25      | PB14         | HFXTAL_N         |                                                                                                                                                                                       | LEU0_RX #1                  |             |  |  |  |  |  |

| 26      | IOVDD_3      | Digital IO powe  | er supply 3.                                                                                                                                                                          |                             |             |  |  |  |  |  |

| 27      | AVDD_0       | Analog power s   | supply 0.                                                                                                                                                                             |                             |             |  |  |  |  |  |

| 28      | PD0          | ADC0_CH0         | PCNT2_S0IN #0                                                                                                                                                                         | US1_TX #1                   |             |  |  |  |  |  |

| 29      | PD1          | ADC0_CH1         | TIM0_CC0 #3 PCNT2_S1IN<br>#0                                                                                                                                                          | US1_RX #1                   |             |  |  |  |  |  |

| 30      | PD2          | ADC0_CH2         | TIM0_CC1 #3                                                                                                                                                                           | US1_CLK #1                  |             |  |  |  |  |  |

| 31      | PD3          | ADC0_CH3         | TIM0_CC2 #3                                                                                                                                                                           | US1_CS #1                   |             |  |  |  |  |  |

| 32      | PD4          | ADC0_CH4         |                                                                                                                                                                                       | LEU0_TX #0                  |             |  |  |  |  |  |

| 33      | PD5          | ADC0_CH5         |                                                                                                                                                                                       | LEU0_RX #0                  |             |  |  |  |  |  |

| 34      | PD6          | ADC0_CH6         | LETIM0_OUT0 #0                                                                                                                                                                        | I2C0_SDA #1                 |             |  |  |  |  |  |

| 35      | PD7          | ADC0_CH7         | LETIM0_OUT1 #0                                                                                                                                                                        | I2C0_SCL #1                 |             |  |  |  |  |  |

| 36      | PD8          |                  |                                                                                                                                                                                       |                             | CMU_CLK1 #1 |  |  |  |  |  |

| 37      | PC6          | ACMP0_CH6        |                                                                                                                                                                                       | LEU1_TX #0 I2C0_SDA #2      |             |  |  |  |  |  |

| 38      | PC7          | ACMP0_CH7        |                                                                                                                                                                                       | LEU1_RX #0 I2C0_SCL #2      |             |  |  |  |  |  |

| 39      | VDD_DREG     | Power supply f   | or on-chip voltage regulator.                                                                                                                                                         |                             |             |  |  |  |  |  |

# 5.3.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G230 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

Table 5.9. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8    | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | PA15      | _         | _         | _         | _         | PA10      | PA8   | PA8<br>— | _     | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | PB12      | PB11      | _         | _     | PB8      | PB7   | _     | _     | _     | _     | _     | _     | _     |

| Port C | PC15      | PC14      | PC13      | PC12      | PC11      | PC10      | PC9   | PC8      | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | _         | _         | _         | _         | _         | _         | _     | PD8      | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8      | _     | _     | _     | _     | _     | _     | _     | _     |

| Port F | _         | _         | _         | _         | _         | _         | _     | _        | _     | _     | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

|      | I2 Pin# and<br>Name |               | Pin Alternate Functionality / Description                                                                                                                                                 |                                 |               |       |  |  |  |  |  |  |  |

|------|---------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------|-------|--|--|--|--|--|--|--|

| Pin# | Pin Name            | Analog        | EBI                                                                                                                                                                                       | Timers                          | Communication | Other |  |  |  |  |  |  |  |

| K5   | PA11                |               |                                                                                                                                                                                           |                                 |               |       |  |  |  |  |  |  |  |

| K6   | RESETn              |               | teset input, active low.To apply an external reset source to this pin, it is required to only drive this pin low during eset, and let the internal pull-up ensure that reset is released. |                                 |               |       |  |  |  |  |  |  |  |

| K7   | AVSS_1              | Analog grou   | ind 1.                                                                                                                                                                                    |                                 |               |       |  |  |  |  |  |  |  |

| K8   | AVDD_2              | Analog pow    | er supply 2.                                                                                                                                                                              |                                 |               |       |  |  |  |  |  |  |  |

| K9   | AVDD_1              | Analog pow    | er supply 1.                                                                                                                                                                              |                                 |               |       |  |  |  |  |  |  |  |

| K10  | AVSS_0              | Analog grou   | ind 0.                                                                                                                                                                                    |                                 |               |       |  |  |  |  |  |  |  |

| K11  | PD1                 | ADC0_CH       |                                                                                                                                                                                           | TIM0_CC0 #3<br>PCNT2_S1IN #0    | US1_RX #1     |       |  |  |  |  |  |  |  |

| L1   | PB8                 | LFXTAL_N      |                                                                                                                                                                                           |                                 | US1_CS #0     |       |  |  |  |  |  |  |  |

| L2   | PC5                 | ACMP0_C<br>H5 |                                                                                                                                                                                           | LETIM0_OUT1 #3<br>PCNT1_S1IN #0 | US2_CS #0     |       |  |  |  |  |  |  |  |

| L3   | PA14                |               |                                                                                                                                                                                           | TIM2_CC2 #1                     |               |       |  |  |  |  |  |  |  |

| L4   | IOVDD_1             | Digital IO po | ower supply 1.                                                                                                                                                                            |                                 |               |       |  |  |  |  |  |  |  |

| L5   | PB11                | DAC0_OU<br>T0 |                                                                                                                                                                                           | LETIM0_OUT0 #1                  |               |       |  |  |  |  |  |  |  |

| L6   | PB12                | DAC0_OU<br>T1 |                                                                                                                                                                                           | LETIM0_OUT1 #1                  |               |       |  |  |  |  |  |  |  |

| L7   | AVSS_2              | Analog grou   | ind 2.                                                                                                                                                                                    |                                 |               |       |  |  |  |  |  |  |  |

| L8   | PB13                | HFXTAL_<br>P  |                                                                                                                                                                                           |                                 | LEU0_TX #1    |       |  |  |  |  |  |  |  |

| L9   | PB14                | HFXTAL_<br>N  |                                                                                                                                                                                           |                                 |               |       |  |  |  |  |  |  |  |

| L10  | AVDD_0              | Analog pow    | er supply 0.                                                                                                                                                                              |                                 |               |       |  |  |  |  |  |  |  |

| L11  | PD0                 | ADC0_CH       |                                                                                                                                                                                           | PCNT2_S0IN #0                   | US1_TX #1     |       |  |  |  |  |  |  |  |

# 5.6.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G290 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

Table 5.18. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | PA15      | PA14      | PA13      | PA12      | PA11      | PA10      | PA9   | PA8   | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | PB15      | PB14      | PB13      | PB12      | PB11      | PB10      | PB9   | PB8   | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| Port C | PC15      | PC14      | PC13      | PC12      | PC11      | PC10      | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | PD15      | PD14      | PD13      | PD12      | PD11      | PD10      | PD9   | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | PE7   | PE6   | PE5   | PE4   | PE3   | PE2   | PE1   | PE0   |

| Port F | _         | _         | _         | _         | _         | _         | PF9   | PF8   | PF7   | PF6   | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

| Alternate     |      |      |     |   | LOCATION                                                                                                                                                      |

|---------------|------|------|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2   | 3 | Description                                                                                                                                                   |

|               |      |      |     |   | Debug-interface Serial Wire viewer Output.                                                                                                                    |

| DBG_SWO       | PF2  | PC15 |     |   | Note that this function is not enabled after reset, and must be enabled by software to be used.                                                               |

| HFXTAL_N      | PB14 |      |     |   | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                          |

| HFXTAL_P      | PB13 |      |     |   | High Frequency Crystal positive pin.                                                                                                                          |

| I2C0_SCL      | PA1  | PD7  | PC7 |   | I2C0 Serial Clock Line input / output.                                                                                                                        |

| I2C0_SDA      | PA0  | PD6  | PC6 |   | I2C0 Serial Data input / output.                                                                                                                              |

| LCD_BCAP_N    | PA13 |      |     |   | LCD voltage booster (optional), boost capacitor, negative pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BCAP_P    | PA12 |      |     |   | LCD voltage booster (optional), boost capacitor, positive pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P. |

|               |      |      |     |   | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.                            |

| LCD_BEXT      | PA14 |      |     |   | An external LCD voltage may also be applied to this pin if the booster is not enabled.                                                                        |

|               |      |      |     |   | If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO.                                                       |

| LCD_COM0      | PE4  |      |     |   | LCD driver common line number 0.                                                                                                                              |

| LCD_COM1      | PE5  |      |     |   | LCD driver common line number 1.                                                                                                                              |

| LCD_COM2      | PE6  |      |     |   | LCD driver common line number 2.                                                                                                                              |

| LCD_COM3      | PE7  |      |     |   | LCD driver common line number 3.                                                                                                                              |

| LCD_SEG0      | PF2  |      |     |   | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG1      | PF3  |      |     |   | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG2      | PF4  |      |     |   | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG3      | PF5  |      |     |   | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG4      | PE8  |      |     |   | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG5      | PE9  |      |     |   | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG6      | PE10 |      |     |   | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG7      | PE11 |      |     |   | LCD segment line 7. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG8      | PE12 |      |     |   | LCD segment line 8. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                                                                        |

|       | P100 Pin#<br>d Name |               | Pi             | n Alternate Functionalit        | y / Description |       |

|-------|---------------------|---------------|----------------|---------------------------------|-----------------|-------|

| Pin # | Pin Name            | Analog        | EBI            | Timers                          | Communication   | Other |

| 4     | PA3                 | LCD_SEG<br>16 | EBI_AD12 #0    | TIM0_CDTI0 #0                   | U0_TX #2        |       |

| 5     | PA4                 | LCD_SEG<br>17 | EBI_AD13 #0    | TIM0_CDTI1 #0                   | U0_RX #2        |       |

| 6     | PA5                 | LCD_SEG<br>18 | EBI_AD14 #0    | TIM0_CDTI2 #0                   | LEU1_TX #1      |       |

| 7     | PA6                 | LCD_SEG<br>19 | EBI_AD15 #0    |                                 | LEU1_RX #1      |       |

| 8     | IOVDD_0             | Digital IO po | ower supply 0. |                                 |                 |       |

| 9     | PB0                 | LCD_SEG<br>32 |                | TIM1_CC0 #2                     |                 |       |

| 10    | PB1                 | LCD_SEG<br>33 |                | TIM1_CC1 #2                     |                 |       |

| 11    | PB2                 | LCD_SEG<br>34 |                | TIM1_CC2 #2                     |                 |       |

| 12    | PB3                 | LCD_SEG<br>20 |                | PCNT1_S0IN #1                   | US2_TX #1       |       |

| 13    | PB4                 | LCD_SEG<br>21 |                | PCNT1_S1IN #1                   | US2_RX #1       |       |

| 14    | PB5                 | LCD_SEG<br>22 |                |                                 | US2_CLK #1      |       |

| 15    | PB6                 | LCD_SEG<br>23 |                |                                 | US2_CS #1       |       |

| 16    | VSS                 | Ground.       |                |                                 |                 |       |

| 17    | IOVDD_1             | Digital IO po | ower supply 1. |                                 |                 |       |

| 18    | PC0                 | ACMP0_C<br>H0 |                | PCNT0_S0IN #2                   | US1_TX #0       |       |

| 19    | PC1                 | ACMP0_C<br>H1 |                | PCNT0_S1IN #2                   | US1_RX #0       |       |

| 20    | PC2                 | ACMP0_C<br>H2 |                |                                 | US2_TX #0       |       |

| 21    | PC3                 | ACMP0_C<br>H3 |                |                                 | US2_RX #0       |       |

| 22    | PC4                 | ACMP0_C<br>H4 |                | LETIM0_OUT0 #3<br>PCNT1_S0IN #0 | US2_CLK #0      |       |

| 23    | PC5                 | ACMP0_C<br>H5 |                | LETIM0_OUT1 #3<br>PCNT1_S1IN #0 | US2_CS #0       |       |

| 24    | PB7                 | LFXTAL_P      |                |                                 | US1_CLK #0      |       |

| 25    | PB8                 | LFXTAL_N      |                |                                 | US1_CS #0       |       |

| 26    | PA7                 | LCD_SEG<br>35 |                |                                 |                 |       |

| 27    | PA8                 | LCD_SEG<br>36 |                | TIM2_CC0 #0                     |                 |       |

|       | P100 Pin#<br>d Name |               |             |        |               |       |

|-------|---------------------|---------------|-------------|--------|---------------|-------|

| Pin # | Pin Name            | Analog        | EBI         | Timers | Communication | Other |

| 100   | PA15                | LCD_SEG<br>12 | EBI_AD08 #0 |        |               |       |

| Alternate     |      |   |   |   | LOCATION                                                                  |

|---------------|------|---|---|---|---------------------------------------------------------------------------|

| Functionality | 0    | 1 | 2 | 3 | Description                                                               |

| LCD_SEG7      | PE11 |   |   |   | LCD segment line 7. Segments 4, 5, 6 and 7 are controlled by SEGEN1.      |

| LCD_SEG8      | PE12 |   |   |   | LCD segment line 8. Segments 8, 9, 10 and 11 are controlled by SEGEN2.    |

| LCD_SEG9      | PE13 |   |   |   | LCD segment line 9. Segments 8, 9, 10 and 11 are controlled by SEGEN2.    |

| LCD_SEG10     | PE14 |   |   |   | LCD segment line 10. Segments 8, 9, 10 and 11 are controlled by SEGEN2.   |

| LCD_SEG11     | PE15 |   |   |   | LCD segment line 11. Segments 8, 9, 10 and 11 are controlled by SEGEN2.   |

| LCD_SEG12     | PA15 |   |   |   | LCD segment line 12. Segments 12, 13, 14 and 15 are controlled by SEGEN3. |

| LCD_SEG13     | PA0  |   |   |   | LCD segment line 13. Segments 12, 13, 14 and 15 are controlled by SEGEN3. |

| LCD_SEG14     | PA1  |   |   |   | LCD segment line 14. Segments 12, 13, 14 and 15 are controlled by SEGEN3. |

| LCD_SEG15     | PA2  |   |   |   | LCD segment line 15. Segments 12, 13, 14 and 15 are controlled by SEGEN3. |

| LCD_SEG16     | PA3  |   |   |   | LCD segment line 16. Segments 16, 17, 18 and 19 are controlled by SEGEN4. |

| LCD_SEG17     | PA4  |   |   |   | LCD segment line 17. Segments 16, 17, 18 and 19 are controlled by SEGEN4. |

| LCD_SEG18     | PA5  |   |   |   | LCD segment line 18. Segments 16, 17, 18 and 19 are controlled by SEGEN4. |

| LCD_SEG19     | PA6  |   |   |   | LCD segment line 19. Segments 16, 17, 18 and 19 are controlled by SEGEN4. |

| LCD_SEG20     | PB3  |   |   |   | LCD segment line 20. Segments 20, 21, 22 and 23 are controlled by SEGEN5. |

| LCD_SEG21     | PB4  |   |   |   | LCD segment line 21. Segments 20, 21, 22 and 23 are controlled by SEGEN5. |

| LCD_SEG22     | PB5  |   |   |   | LCD segment line 22. Segments 20, 21, 22 and 23 are controlled by SEGEN5. |

| LCD_SEG23     | PB6  |   |   |   | LCD segment line 23. Segments 20, 21, 22 and 23 are controlled by SEGEN5. |

| LCD_SEG24     | PF6  |   |   |   | LCD segment line 24. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG25     | PF7  |   |   |   | LCD segment line 25. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG26     | PF8  |   |   |   | LCD segment line 26. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG27     | PF9  |   |   |   | LCD segment line 27. Segments 24, 25, 26 and 27 are controlled by SEGEN6. |

| LCD_SEG28     | PD9  |   |   |   | LCD segment line 28. Segments 28, 29, 30 and 31 are controlled by SEGEN7. |

| LCD_SEG29     | PD10 |   |   |   | LCD segment line 29. Segments 28, 29, 30 and 31 are controlled by SEGEN7. |

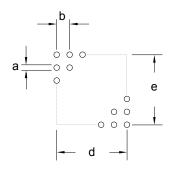

Figure 6.4. BGA112 PCB Stencil Design

Table 6.3. BGA112 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.33      |

| b      | 0.80      |

| d      | 8.00      |

| е      | 8.00      |

#### Note:

- 1. The drawings are not to scale.

- 2. All dimensions are in millimeters.

- 3. All drawings are subject to change without notice.

- 4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

- 5. Stencil thickness 0.125 mm.

- 6. For detailed pin-positioning, see Pin Definitions.

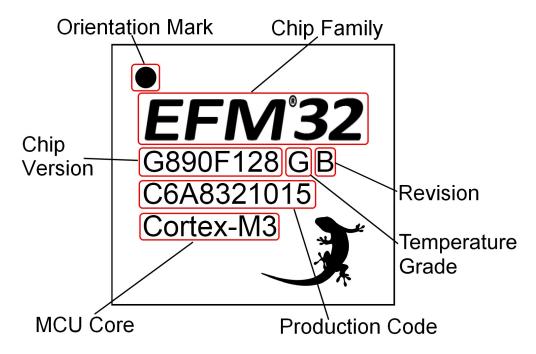

#### 10.3 QFN64 Package Marking

In the illustration below package fields and position are shown.

Figure 10.5. Example Chip Marking (Top View)

# 12. Chip Revision, Solder Information, Errata

# 12.1 Chip Revision

The revision of a chip can be determined from the "Revision" field in the package marking.

#### 12.2 Soldering Information

The latest IPC/JEDEC J-STD-020 recommendations for Pb-Free reflow soldering should be followed.

#### 12.3 Errata

Please see the errata document for description and resolution of device errata. This document is available in Simplicity Studio and online at: http://www.silabs.com/support/pages/document-library.aspx?p=MCUs--32-bit

#### 13.5 Revision 1.71

November 21st, 2013

Updated figures.

Updated errata-link.

Updated chip marking.

Added link to Environmental and Quality information.

For devices with a DAC, re-added missing DAC-data.

#### 13.6 Revision 1.70

September 30th, 2013

For devices with an I2C, added I2C characterization data.

Corrected GPIO operating voltage from 1.8 V to 1.85 V.

For devices with an ADC, corrected the ADC resolution from 12, 10 and 6 bit to 12, 8 and 6 bit.

For QFN64 devices, updated the Max V<sub>ESDCDM</sub> value to 750 V.

Updated Environmental information.

Updated trademark, disclaimer and contact information.

Other minor corrections.

#### 13.7 Revision 1.60

June 28th, 2013

For BGA devices, updated PCB Land Pattern, PCB Solder Mask and PCB Stencil Design figures.

Updated power requirements in the Power Management section.

Removed minimum load capacitance figure and table. Added reference to application note.

Other minor corrections.

#### 13.8 Revision 1.50

September 11th, 2012

Updated the HFRCO 1 MHz band typical value to 1.2 MHz.

Updated the HFRCO 7 MHz band typical value to 6.6 MHz.

For BGA devices, corrected BGA solder balls material from Sn96.5/Ag3/Cu0.5 to SAC105.

Other minor corrections.

#### 13.9 Revision 1.40

February 27th, 2012

Updated Power Management section.

Corrected operating voltage from 1.8 V to 1.85 V.

Corrected TGRAD<sub>ADCTH</sub> parameter.

Corrected package drawing.

Updated PCB land pattern, solder mask and stencil design.

For LQFP48 devices, corrected available Pulse Counters from 3 to 2.

For LQFP48 devices, corrected available LEUARTs from 2 to 1.

For LQFP64 devices, corrected ordering codes in the ordering information table.

#### 13.10 Revision 1.30

May 20th, 2011

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

Updated LFXO load capacitance section.