Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| 2 0 0 0 0 0                |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | ARM® Cortex®-M3                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 53                                                                        |

| Program Memory Size        | 128KB (128K x 8)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                              |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (10x10)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g232f128g-e-qfp64r |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

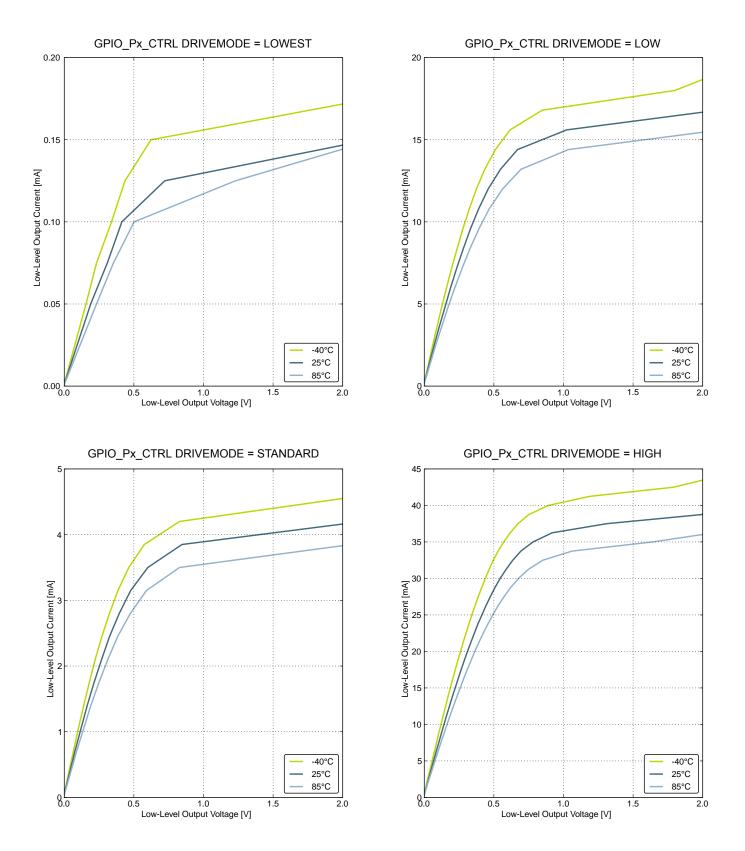

Figure 4.14. Typical Low-Level Output Current, 2V Supply Voltage

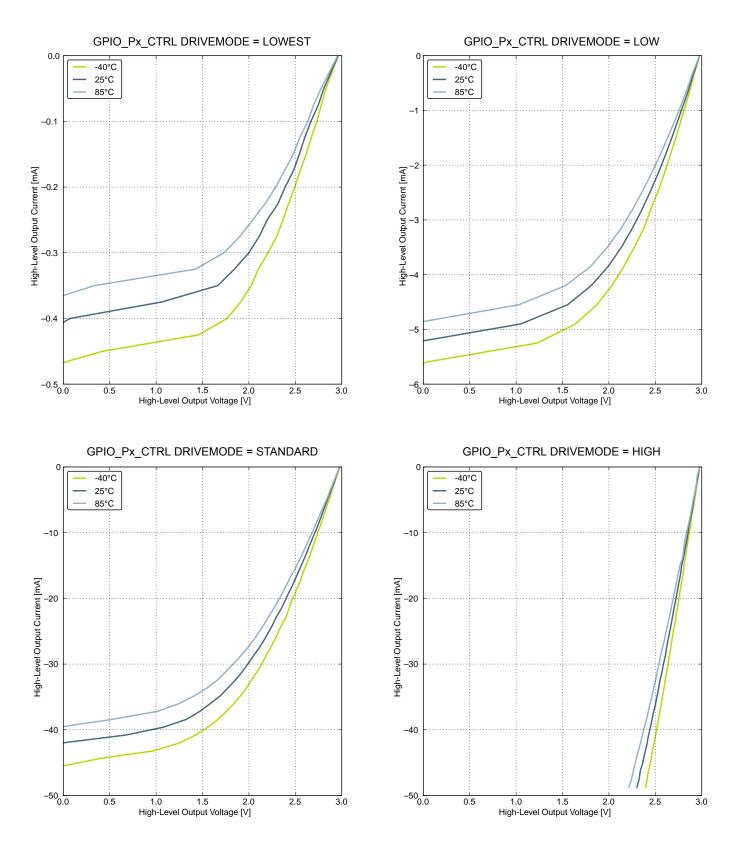

Figure 4.17. Typical High-Level Output Current, 3V Supply Voltage

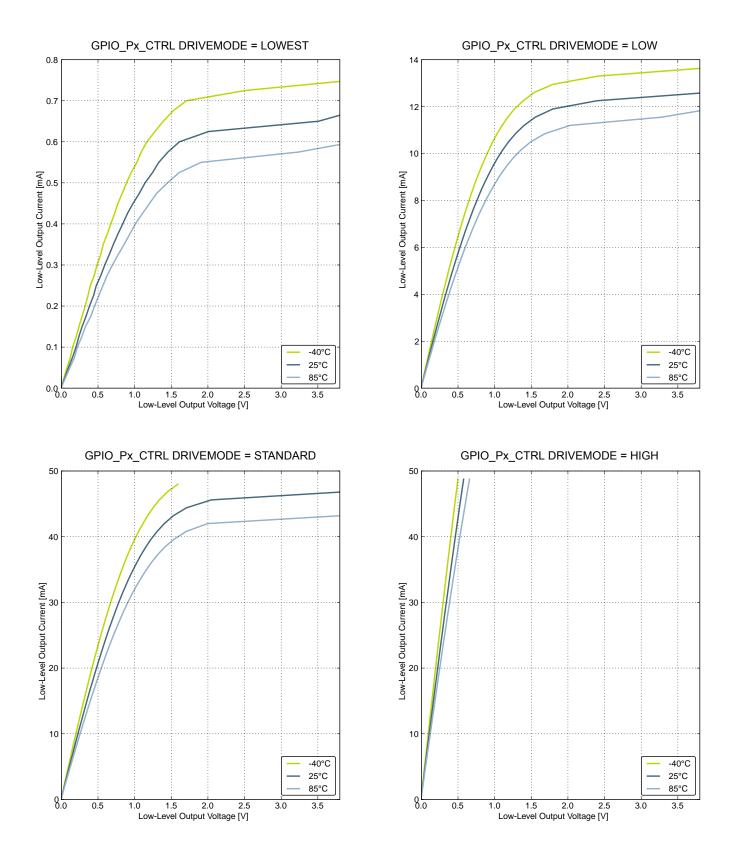

Figure 4.18. Typical Low-Level Output Current, 3.8V Supply Voltage

# Table 4.9. HFXO

| Parameter                                                            | Symbol              | Test Condition                                                                           | Min | Тур | Max  | Unit |

|----------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------|-----|-----|------|------|

| Supported nominal crystal Fre-<br>quency                             | f <sub>HFXO</sub>   |                                                                                          | 4   | —   | 32   | MHz  |

| Supported crystal equivalent ser-                                    | ESR <sub>HFXO</sub> | Crystal frequency 32 MHz                                                                 | _   | 30  | 60   | Ω    |

| ies resistance (ESR)                                                 | LOINHEXO            | Crystal frequency 4 MHz                                                                  | _   | 400 | 1500 | Ω    |

| The transconductance of the HFXO input transistor at crystal startup | 9 <sub>mHFXO</sub>  | HFXOBOOST in CMU_CTRL<br>equals 0b11                                                     | 20  |     | _    | mS   |

| Supported crystal external load range                                | C <sub>HFXOL</sub>  |                                                                                          | 5   |     | 25   | pF   |

| Current consumption for HFXO                                         | 1                   | 4 MHz: ESR=400 Ω, $C_L$ =20 pF,<br>HFXOBOOST in CMU_CTRL<br>equals 0b11                  | _   | 85  | _    | μA   |

| after startup                                                        | IHFXO               | 32 MHz: ESR=30 $\Omega$ , C <sub>L</sub> =10 pF,<br>HFXOBOOST in CMU_CTRL<br>equals 0b11 | _   | 165 | _    | μA   |

| Startup time                                                         | t <sub>HFXO</sub>   | 32 MHz: ESR=30 Ω, C <sub>L</sub> =10 pF,<br>HFXOBOOST in CMU_CTRL<br>equals 0b11         |     | 400 | _    | μs   |

| Pulse width removed by glitch de-<br>tector                          |                     |                                                                                          | 1   |     | 4    | ns   |

# 4.9.5 AUXHFRCO

# Table 4.12. AUXHFRCO

| Parameter                                                                  | Symbol                         | Test Condition                 | Min    | Тур              | Max    | Unit   |

|----------------------------------------------------------------------------|--------------------------------|--------------------------------|--------|------------------|--------|--------|

| Oscillation frequency, V <sub>DD</sub> = 3.0<br>V, T <sub>AMB</sub> =25 °C | fauxhfrco                      | 14 MHz frequency band          | 13.580 | 14.0             | 14.420 | MHz    |

| Settling time after start-up                                               | t <sub>AUXHFRCO_settling</sub> | f <sub>AUXHFRCO</sub> = 14 MHz | _      | 0.6              | —      | Cycles |

| Duty cycle                                                                 | DC <sub>AUXHFRCO</sub>         | f <sub>AUXHFRCO</sub> = 14 MHz | 48.5   | 50               | 51     | %      |

| Frequency step for LSB change in TUNING value                              | TUNESTEPAUXHFRCO               |                                | _      | 0.3 <sup>1</sup> | _      | %      |

## Note:

1. The TUNING field in the CMU\_AUXHFRCOCTRL register may be used to adjust the AUXHFRCO frequency. By using a stable frequency reference such as the LFXO or HFXO, a firmware calibration routine can vary the TUNING bits and the frequency band to maintain the AUXHFRCO frequency at any arbitrary value in the 14 MHz range across operating conditions.

# 4.9.6 ULFRCO

# Table 4.13. ULFRCO

| Parameter                  | Symbol               | Test Condition | Min | Тур   | Мах  | Unit |

|----------------------------|----------------------|----------------|-----|-------|------|------|

| Oscillation frequency      | fulfrco              | 25 °C, 3 V     | 0.7 | _     | 1.75 | kHz  |

| Temperature coefficient    | TC <sub>ULFRCO</sub> |                |     | 0.05  |      | %/°C |

| Supply voltage coefficient | VC <sub>ULFRCO</sub> |                |     | -18.2 | _    | %/V  |

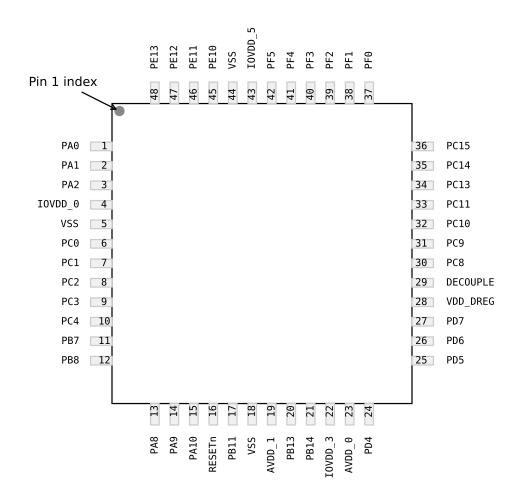

## 5.2 EFM32G222 (TQFP48)

## 5.2.1 Pinout

The EFM32G222 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.2. EFM32G222 Pinout (top view, not to scale)

#### Table 5.4. Device Pinout

|       | 48 Pin# and<br>Name | Pin Alternate Functionality / Description |                            |               |             |  |  |  |  |  |

|-------|---------------------|-------------------------------------------|----------------------------|---------------|-------------|--|--|--|--|--|

| Pin # | Pin Name            | Analog                                    | Timers                     | Communication | Other       |  |  |  |  |  |

| 1     | PA0                 |                                           | TIM0_CC0 #0/1              | I2C0_SDA #0   |             |  |  |  |  |  |

| 2     | PA1                 |                                           | TIM0_CC1 #0/1              | I2C0_SCL #0   | CMU_CLK1 #0 |  |  |  |  |  |

| 3     | PA2                 |                                           | TIM0_CC2 #0/1              |               | CMU_CLK0 #0 |  |  |  |  |  |

| 4     | IOVDD_0             | Digital IO powe                           | Digital IO power supply 0. |               |             |  |  |  |  |  |

| 5     | VSS                 | Ground.                                   |                            |               |             |  |  |  |  |  |

|       | P100 Pin#<br>d Name |        | Pi                               | n Alternate Functionalit | y / Description |            |

|-------|---------------------|--------|----------------------------------|--------------------------|-----------------|------------|

| Pin # | Pin Name            | Analog | EBI                              | Timers                   | Communication   | Other      |

| 92    | PE8                 |        | EBI_AD00 #0                      | PCNT2_S0IN #1            |                 |            |

| 93    | PE9                 |        | EBI_AD01 #0                      | PCNT2_S1IN #1            |                 |            |

| 94    | PE10                |        | EBI_AD02 #0                      | TIM1_CC0 #1              | US0_TX #0       | BOOT_TX    |

| 95    | PE11                |        | EBI_AD03 #0 TIM1_CC1 #1 US0_RX # |                          | US0_RX #0       | BOOT_RX    |

| 96    | PE12                |        | EBI_AD04 #0                      | TIM1_CC2 #1              | US0_CLK #0      |            |

| 97    | PE13                |        | EBI_AD05 #0                      |                          | US0_CS #0       | ACMP0_O #0 |

| 98    | PE14                |        | EBI_AD06 #0                      |                          | LEU0_TX #2      |            |

| 99    | PE15                |        | EBI_AD07 #0                      |                          | LEU0_RX #2      |            |

| 100   | PA15                |        | EBI_AD08 #0                      |                          |                 |            |

| Alternate     |      |      |   |   | LOCATION                                                                                        |  |  |

|---------------|------|------|---|---|-------------------------------------------------------------------------------------------------|--|--|

| Functionality | 0    | 1    | 2 | 3 | Description                                                                                     |  |  |

| DAC0_OUT0     | PB11 |      |   |   | Digital to Analog Converter DAC0 output channel number 0.                                       |  |  |

| DAC0_OUT1     | PB12 |      |   |   | Digital to Analog Converter DAC0 output channel number 1.                                       |  |  |

|               |      |      |   |   | Debug-interface Serial Wire clock input.                                                        |  |  |

| DBG_SWCLK     | PF0  | PF0  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.           |  |  |

|               |      |      |   |   | Debug-interface Serial Wire data input / output.                                                |  |  |

| DBG_SWDIO     | PF1  | PF1  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.             |  |  |

|               |      |      |   |   | Debug-interface Serial Wire viewer Output.                                                      |  |  |

| DBG_SWO       | PF2  | PC15 |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |  |  |

| EBI_AD00      | PE8  |      |   |   | External Bus Interface (EBI) address and data input / output pin 00.                            |  |  |

| EBI_AD01      | PE9  |      |   |   | External Bus Interface (EBI) address and data input / output pin 01.                            |  |  |

| EBI_AD02      | PE10 |      |   |   | External Bus Interface (EBI) address and data input / output pin 02.                            |  |  |

| EBI_AD03      | PE11 |      |   |   | External Bus Interface (EBI) address and data input / output pin 03.                            |  |  |

| EBI_AD04      | PE12 |      |   |   | External Bus Interface (EBI) address and data input / output pin 04.                            |  |  |

| EBI_AD05      | PE13 |      |   |   | External Bus Interface (EBI) address and data input / output pin 05.                            |  |  |

| EBI_AD06      | PE14 |      |   |   | External Bus Interface (EBI) address and data input / output pin 06.                            |  |  |

| EBI_AD07      | PE15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 07.                            |  |  |

| EBI_AD08      | PA15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 08.                            |  |  |

| EBI_AD09      | PA0  |      |   |   | External Bus Interface (EBI) address and data input / output pin 09.                            |  |  |

| EBI_AD10      | PA1  |      |   |   | External Bus Interface (EBI) address and data input / output pin 10.                            |  |  |

| EBI_AD11      | PA2  |      |   |   | External Bus Interface (EBI) address and data input / output pin 11.                            |  |  |

| EBI_AD12      | PA3  |      |   |   | External Bus Interface (EBI) address and data input / output pin 12.                            |  |  |

| EBI_AD13      | PA4  |      |   |   | External Bus Interface (EBI) address and data input / output pin 13.                            |  |  |

| EBI_AD14      | PA5  |      |   |   | External Bus Interface (EBI) address and data input / output pin 14.                            |  |  |

| EBI_AD15      | PA6  |      |   |   | External Bus Interface (EBI) address and data input / output pin 15.                            |  |  |

| EBI_ALE       | PF3  |      |   |   | External Bus Interface (EBI) Address Latch Enable output.                                       |  |  |

| Alternate     |      |      |      |      | LOCATION                                                                              |

|---------------|------|------|------|------|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3    | Description                                                                           |

| TIM2_CC0      | PA8  | PA12 | PC8  |      | Timer 2 Capture Compare input / output channel 0.                                     |

| TIM2_CC1      | PA9  | PA13 | PC9  |      | Timer 2 Capture Compare input / output channel 1.                                     |

| TIM2_CC2      | PA10 | PA14 | PC10 |      | Timer 2 Capture Compare input / output channel 2.                                     |

| U0_RX         | PF7  | PE1  | PA4  | PC15 | UART0 Receive input.                                                                  |

| U0_TX         | PF6  | PE0  | PA3  | PC14 | UART0 Transmit output. Also used as receive input in half duplex communication.       |

| US0_CLK       | PE12 | PE5  | PC9  |      | USART0 clock input / output.                                                          |

| US0_CS        | PE13 | PE4  | PC8  |      | USART0 chip select input / output.                                                    |

|               |      |      |      |      | USART0 Asynchronous Receive.                                                          |

| US0_RX        | PE11 | PE6  | PC10 |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               |      |      |      |      | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US0_TX        | PE10 | PE7  | PC11 |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US1_CLK       | PB7  | PD2  |      |      | USART1 clock input / output.                                                          |

| US1_CS        | PB8  | PD3  |      |      | USART1 chip select input / output.                                                    |

|               |      |      |      |      | USART1 Asynchronous Receive.                                                          |

| US1_RX        | PC1  | PD1  |      |      | USART1 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               | DOG  |      |      |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US1_TX        | PC0  | PD0  |      |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US2_CLK       | PC4  | PB5  |      |      | USART2 clock input / output.                                                          |

| US2_CS        | PC5  | PB6  |      |      | USART2 chip select input / output.                                                    |

|               |      |      |      |      | USART2 Asynchronous Receive.                                                          |

| US2_RX        | PC3  | PB4  |      |      | USART2 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               | DC2  |      |      |      | USART2 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US2_TX        | PC2  | PB3  |      |      | USART2 Synchronous mode Master Output / Slave Input (MOSI).                           |

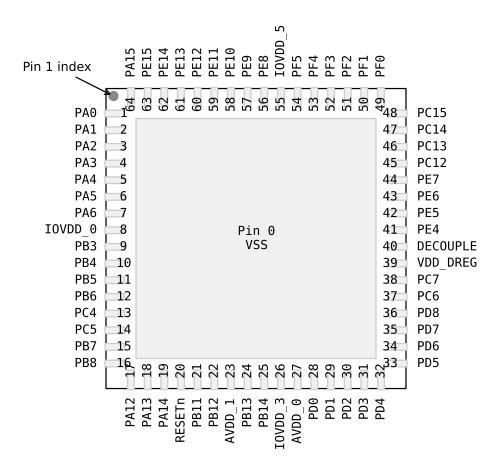

## 5.7 EFM32G840 (QFN64)

# 5.7.1 Pinout

The EFM32G840 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.7. EFM32G840 Pinout (top view, not to scale)

#### Table 5.19. Device Pinout

| QFN64 P | in# and Name |           | Pin Alternate | Functionality / Description |             |

|---------|--------------|-----------|---------------|-----------------------------|-------------|

| Pin #   | Pin Name     | Analog    | Timers        | Communication               | Other       |

| 0       | VSS          | Ground.   |               |                             |             |

| 1       | PA0          | LCD_SEG13 | TIM0_CC0 #0/1 | I2C0_SDA #0                 |             |

| 2       | PA1          | LCD_SEG14 | TIM0_CC1 #0/1 | I2C0_SCL #0                 | CMU_CLK1 #0 |

| 3       | PA2          | LCD_SEG15 | TIM0_CC2 #0/1 |                             | CMU_CLK0 #0 |

| 4       | PA3          | LCD_SEG16 | TIM0_CDTI0 #0 |                             |             |

| 5       | PA4          | LCD_SEG17 | TIM0_CDTI1 #0 |                             |             |

|       | 64 Pin# and<br>Name |                 | Pin Alternate                                                          | Functionality / Description                                       |                                |

|-------|---------------------|-----------------|------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------|

| Pin # | Pin Name            | Analog          | Timers                                                                 | Communication                                                     | Other                          |

| 6     | PA5                 | LCD_SEG18       | TIM0_CDTI2 #0                                                          | LEU1_TX #1                                                        |                                |

| 7     | IOVDD_0             | Digital IO powe | er supply 0.                                                           |                                                                   |                                |

| 8     | VSS                 | Ground.         |                                                                        |                                                                   |                                |

| 9     | PB3                 | LCD_SEG20       | PCNT1_S0IN #1                                                          | US2_TX #1                                                         |                                |

| 10    | PB4                 | LCD_SEG21       | PCNT1_S1IN #1                                                          | US2_RX #1                                                         |                                |

| 11    | PB5                 | LCD_SEG22       |                                                                        | US2_CLK #1                                                        |                                |

| 12    | PB6                 | LCD_SEG23       |                                                                        | US2_CS #1                                                         |                                |

| 13    | PC4                 | ACMP0_CH4       | LETIM0_OUT0 #3<br>PCNT1_S0IN #0                                        | US2_CLK #0                                                        |                                |

| 14    | PC5                 | ACMP0_CH5       | LETIM0_OUT1 #3<br>PCNT1_S1IN #0                                        | US2_CS #0                                                         |                                |

| 15    | PB7                 | LFXTAL_P        |                                                                        | US1_CLK #0                                                        |                                |

| 16    | PB8                 | LFXTAL_N        |                                                                        | US1_CS #0                                                         |                                |

| 17    | PA12                | LCD_BCAP_<br>P  | TIM2_CC0 #1                                                            |                                                                   |                                |

| 18    | PA13                | LCD_BCAP_<br>N  | TIM2_CC1 #1                                                            |                                                                   |                                |

| 19    | PA14                | LCD_BEXT        | TIM2_CC2 #1                                                            |                                                                   |                                |

| 20    | RESETn              |                 | tive low.To apply an external re<br>nd let the internal pull-up ensure | eset source to this pin, it is require<br>that reset is released. | red to only drive this pin low |

| 21    | PB11                | DAC0_OUT0       | LETIM0_OUT0 #1                                                         |                                                                   |                                |

| 22    | VSS                 | Ground.         |                                                                        |                                                                   |                                |

| 23    | AVDD_1              | Analog power    | supply 1.                                                              |                                                                   |                                |

| 24    | PB13                | HFXTAL_P        |                                                                        | LEU0_TX #1                                                        |                                |

| 25    | PB14                | HFXTAL_N        |                                                                        | LEU0_RX #1                                                        |                                |

| 26    | IOVDD_3             | Digital IO powe | er supply 3.                                                           |                                                                   |                                |

| 27    | AVDD_0              | Analog power    | supply 0.                                                              |                                                                   |                                |

| 28    | PD0                 | ADC0_CH0        | PCNT2_S0IN #0                                                          | US1_TX #1                                                         |                                |

| 29    | PD1                 | ADC0_CH1        | TIM0_CC0 #3 PCNT2_S1IN<br>#0                                           | US1_RX #1                                                         |                                |

| 30    | PD2                 | ADC0_CH2        | TIM0_CC1 #3                                                            | US1_CLK #1                                                        |                                |

| 31    | PD3                 | ADC0_CH3        | TIM0_CC2 #3                                                            | US1_CS #1                                                         |                                |

| 32    | PD4                 | ADC0_CH4        |                                                                        | LEU0_TX #0                                                        |                                |

| 33    | PD5                 | ADC0_CH5        |                                                                        | LEU0_RX #0                                                        |                                |

| 34    | PD6                 | ADC0_CH6        | LETIM0_OUT0 #0                                                         | I2C0_SDA #1                                                       |                                |

| 35    | PD7                 | ADC0_CH7        | LETIM0_OUT1 #0                                                         | I2C0_SCL #1                                                       |                                |

| 36    | PD8                 |                 |                                                                        |                                                                   | CMU_CLK1 #1                    |

| 37    | PC6                 | ACMP0_CH6       |                                                                        | LEU1_TX #0 I2C0_SDA #2                                            |                                |

|       | l2 Pin# and<br>Name |                | Pi                     | n Alternate Functionalit                                 | y / Description                |                             |  |  |  |  |

|-------|---------------------|----------------|------------------------|----------------------------------------------------------|--------------------------------|-----------------------------|--|--|--|--|

| Pin # | Pin Name            | Analog         | EBI                    | Timers                                                   | Communication                  | Other                       |  |  |  |  |

| H9    | PD5                 | ADC0_CH<br>5   |                        |                                                          | LEU0_RX #0                     |                             |  |  |  |  |

| H10   | PD6                 | ADC0_CH<br>6   |                        | LETIM0_OUT0 #0                                           | I2C0_SDA #1                    |                             |  |  |  |  |

| H11   | PD7                 | ADC0_CH<br>7   |                        | LETIM0_OUT1 #0                                           | I2C0_SCL #1                    |                             |  |  |  |  |

| J1    | PC1                 | ACMP0_C<br>H1  |                        | PCNT0_S1IN #2                                            | US1_RX #0                      |                             |  |  |  |  |

| J2    | PC3                 | ACMP0_C<br>H3  |                        |                                                          | US2_RX #0                      |                             |  |  |  |  |

| J3    | PD15                |                |                        |                                                          | I2C0_SCL #3                    |                             |  |  |  |  |

| J4    | PA12                | LCD_BCA<br>P_P |                        | TIM2_CC0 #1                                              |                                |                             |  |  |  |  |

| J5    | PA9                 | LCD_SEG<br>37  |                        | TIM2_CC1 #0                                              |                                |                             |  |  |  |  |

| J6    | PA10                | LCD_SEG<br>38  |                        | TIM2_CC2 #0                                              |                                |                             |  |  |  |  |

| J7    | PB9                 |                |                        |                                                          |                                |                             |  |  |  |  |

| J8    | PB10                |                |                        |                                                          |                                |                             |  |  |  |  |

| J9    | PD2                 | ADC0_CH<br>2   |                        | TIM0_CC1 #3                                              | US1_CLK #1                     |                             |  |  |  |  |

| J10   | PD3                 | ADC0_CH<br>3   |                        | TIM0_CC2 #3                                              | US1_CS #1                      |                             |  |  |  |  |

| J11   | PD4                 | ADC0_CH<br>4   |                        |                                                          | LEU0_TX #0                     |                             |  |  |  |  |

| K1    | PB7                 | LFXTAL_P       |                        |                                                          | US1_CLK #0                     |                             |  |  |  |  |

| К2    | PC4                 | ACMP0_C<br>H4  |                        | LETIM0_OUT0 #3<br>PCNT1_S0IN #0                          | US2_CLK #0                     |                             |  |  |  |  |

| К3    | PA13                | LCD_BCA<br>P_N |                        | TIM2_CC1 #1                                              |                                |                             |  |  |  |  |

| K4    | VSS                 | Ground.        |                        |                                                          |                                |                             |  |  |  |  |

| K5    | PA11                | LCD_SEG<br>39  |                        |                                                          |                                |                             |  |  |  |  |

| K6    | RESETn              |                |                        | external reset source to the ure that reset is released. | is pin, it is required to only | / drive this pin low during |  |  |  |  |

| K7    | AVSS_1              | Analog grou    | Analog ground 1.       |                                                          |                                |                             |  |  |  |  |

| K8    | AVDD_2              | Analog pow     | Analog power supply 2. |                                                          |                                |                             |  |  |  |  |

| K9    | AVDD_1              | Analog pow     | er supply 1.           |                                                          |                                |                             |  |  |  |  |

| K10   | AVSS_0              | Analog grou    | nalog ground 0.        |                                                          |                                |                             |  |  |  |  |

| K11   | PD1                 | ADC0_CH<br>1   |                        | TIM0_CC0 #3<br>PCNT2_S1IN #0                             | US1_RX #1                      |                             |  |  |  |  |

| L1    | PB8                 | LFXTAL_N       |                        |                                                          | US1_CS #0                      |                             |  |  |  |  |

#### 5.10.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      |   |   | LOCATION                                                  |

|---------------|------|------|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                               |

| ACMP0_CH0     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                       |

| ACMP0_CH1     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                       |

| ACMP0_CH2     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                       |

| ACMP0_CH3     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                       |

| ACMP0_CH4     | PC4  |      |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |      |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |      |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |      |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 | PE2  |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                       |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP1, channel 1.                       |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP1, channel 2.                       |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP1, channel 3.                       |

| ACMP1_CH4     | PC12 |      |   |   | Analog comparator ACMP1, channel 4.                       |

| ACMP1_CH5     | PC13 |      |   |   | Analog comparator ACMP1, channel 5.                       |

| ACMP1_CH6     | PC14 |      |   |   | Analog comparator ACMP1, channel 6.                       |

| ACMP1_CH7     | PC15 |      |   |   | Analog comparator ACMP1, channel 7.                       |

| ACMP1_O       | PF2  | PE3  |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                            |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.             |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.             |

### Table 5.29. Alternate functionality overview

| Alternate     |      |      |      |      | LOCATION                                                                                                      |

|---------------|------|------|------|------|---------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3    | Description                                                                                                   |

| LCD_SEG30     | PD11 |      |      |      | LCD segment line 30. Segments 28, 29, 30 and 31 are con-<br>trolled by SEGEN7.                                |

| LCD_SEG31     | PD12 |      |      |      | LCD segment line 31. Segments 28, 29, 30 and 31 are con-<br>trolled by SEGEN7.                                |

| LCD_SEG32     | PB0  |      |      |      | LCD segment line 32. Segments 32, 33, 34 and 35 are con-<br>trolled by SEGEN8.                                |

| LCD_SEG33     | PB1  |      |      |      | LCD segment line 33. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG34     | PB2  |      |      |      | LCD segment line 34. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG35     | PA7  |      |      |      | LCD segment line 35. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG36     | PA8  |      |      |      | LCD segment line 36. Segments 36, 37, 38 and 39 are con-<br>trolled by SEGEN9.                                |

| LCD_SEG37     | PA9  |      |      |      | LCD segment line 37. Segments 36, 37, 38 and 39 are con-<br>trolled by SEGEN9.                                |

| LCD_SEG38     | PA10 |      |      |      | LCD segment line 38. Segments 36, 37, 38 and 39 are con-<br>trolled by SEGEN9.                                |

| LCD_SEG39     | PA11 |      |      |      | LCD segment line 39. Segments 36, 37, 38 and 39 are con-<br>trolled by SEGEN9.                                |

| LETIM0_OUT0   | PD6  | PB11 | PF0  | PC4  | Low Energy Timer LETIM0, output channel 0.                                                                    |

| LETIM0_OUT1   | PD7  | PB12 | PF1  | PC5  | Low Energy Timer LETIM0, output channel 1.                                                                    |

| LEU0_RX       | PD5  | PB14 | PE15 |      | LEUART0 Receive input.                                                                                        |

| LEU0_TX       | PD4  | PB13 | PE14 |      | LEUART0 Transmit output. Also used as receive input in half duplex communication.                             |

| LEU1_RX       | PC7  | PA6  |      |      | LEUART1 Receive input.                                                                                        |

| LEU1_TX       | PC6  | PA5  |      |      | LEUART1 Transmit output. Also used as receive input in half duplex communication.                             |

| LFXTAL_N      | PB8  |      |      |      | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional external clock input pin. |

| LFXTAL_P      | PB7  |      |      |      | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                    |

| PCNT0_S0IN    | PC13 | PE0  | PC0  |      | Pulse Counter PCNT0 input number 0.                                                                           |

| PCNT0_S1IN    | PC14 | PE1  | PC1  |      | Pulse Counter PCNT0 input number 1.                                                                           |

| PCNT1_S0IN    | PC4  | PB3  |      |      | Pulse Counter PCNT1 input number 0.                                                                           |

| PCNT1_S1IN    | PC5  | PB4  |      |      | Pulse Counter PCNT1 input number 1.                                                                           |

| PCNT2_S0IN    | PD0  | PE8  |      |      | Pulse Counter PCNT2 input number 0.                                                                           |

| PCNT2_S1IN    | PD1  | PE9  |      |      | Pulse Counter PCNT2 input number 1.                                                                           |

| TIM0_CC0      | PA0  | PA0  | PF6  | PD1  | Timer 0 Capture Compare input / output channel 0.                                                             |

| TIM0_CC1      | PA1  | PA1  | PF7  | PD2  | Timer 0 Capture Compare input / output channel 1.                                                             |

| TIM0_CC2      | PA2  | PA2  | PF8  | PD3  | Timer 0 Capture Compare input / output channel 2.                                                             |

| TIM0_CDTI0    | PA3  | PC13 | PF3  | PC13 | Timer 0 Complimentary Deat Time Insertion channel 0.                                                          |

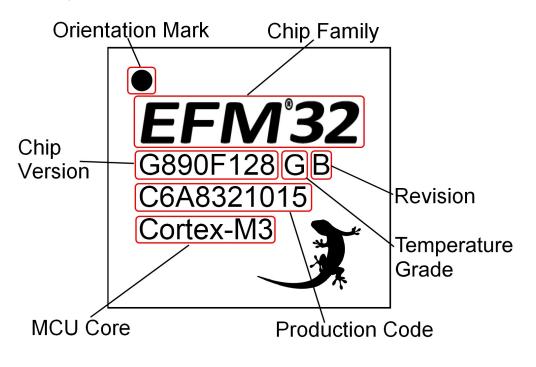

# 6.3 BGA112 Package Marking

In the illustration below package fields and position are shown.

Figure 6.5. Example Chip Marking (Top View)

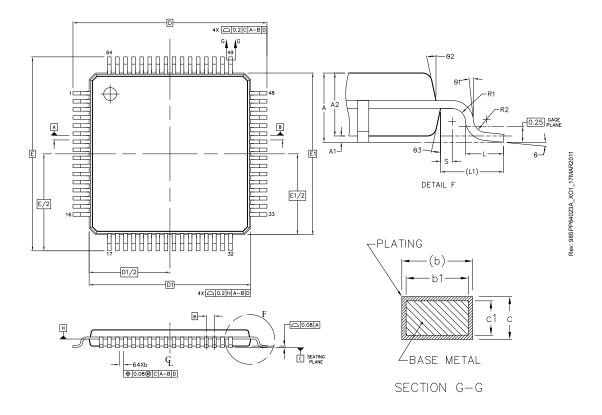

# 8. TQFP64 Package Specifications

## 8.1 TQFP64 Package Dimensions

Figure 8.1. TQFP64

#### Note:

- 1. All dimensions & tolerancing confirm to ASME Y14.5M-1994.

- 2. The top package body size may be smaller than the bottom package body size.

- 3. Datum 'A,B', and 'B' to be determined at datum plane 'H'.

- 4. To be determined at seating place 'C'.

- 5. Dimension 'D1' and 'E1' do not include mold protrusions. Allowable protrusion is 0.25mm per side.'D1' and 'E1' are maximum plastic body size dimension including mold mismatch. Dimension 'D1' and'E1' shall be determined at datum plane 'H'.

- 6. Detail of Pin 1 indicatifier are option all but must be located within the zone indicated.

- 7. Dimension 'b' does not include dambar protrusion. Allowable dambar protrusion shall not cause thelead width to exceed the maximum 'b' dimension by more than 0.08 mm. Dambar can not be locatedon the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm.

- 8. Exact shape of each corner is optional.

- 9. These dimension apply to the flat section of the lead between 0.10 mm and 0.25 mm from the lead tip.

- 10. All dimensions are in millimeters.

| DIM | MIN  | NOM  | MAX  | DIM | MIN  | NOM | MAX  |

|-----|------|------|------|-----|------|-----|------|

| A   | _    | 1.10 | 1.20 | L1  |      | —   |      |

| A1  | 0.05 | —    | 0.15 | R1  | 0.08 | —   | —    |

| A2  | 0.95 | 1.00 | 1.05 | R2  | 0.08 | _   | 0.20 |

## Table 8.1. QFP64 (Dimensions in mm)

| DIM | MIN      | NOM       | MAX   | DIM | MIN | NOM        | MAX |

|-----|----------|-----------|-------|-----|-----|------------|-----|

| D   | 0.170    | —         | 0.270 | S1  | _   | 4.500 BSC  | —   |

| E   | 0.950    | —         | 1.050 | V   |     | 9.000 BSC  | —   |

| F   | 0.170    | —         | 0.230 | V1  | _   | 4.5000 BSC | —   |

| G   | —        | 0.500 BSC |       | W   | _   | 0.200 BSC  | —   |

| Н   | 0.050    | _         | 0.150 | AA  | _   | 1.000BSC   | —   |

| J   | 0.090    | —         | 0.200 |     |     |            |     |

| К   | 0.500    | _         | 0.700 |     |     |            |     |

| L   | 0DE<br>G | _         | 7DEG  |     |     |            |     |

The TQFP48 Package is 7 by 7 mm in size and has a 0.5 mm pin pitch.

The TQFP48 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx

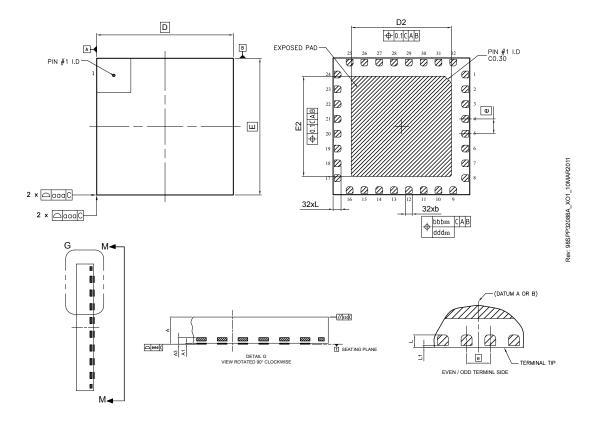

# 11. QFN32 Package Specifications

# 11.1 QFN32 Package Dimensions

Figure 11.1. QFN32

## Note:

- 1. Dimensioning & tolerancing confirm to ASME Y14.5M-1994.

- 2. All dimensions are in millimeters. Angles are in degrees.

- 3. Dimension 'b' applies to metallized terminal and is measured between 0.25 mm and 0.30 mm from the terminal tip. Dimension L1 represents terminal full back from package edge up to 0.1 mm isacceptable.

- 4. Coplanarity applies to the exposed heat slug as well as the terminal.

- 5. Radius on terminal is optional.

| Symbol | А    | A1   | A3           | b    | D           | E           | D2   | E2   | е           | L    | L1   | aaa  | bbb  | ссс  | ddd  | eee  |

|--------|------|------|--------------|------|-------------|-------------|------|------|-------------|------|------|------|------|------|------|------|

| Min    | 0.80 | 0.00 |              | 0.25 |             |             | 4.30 | 4.30 |             | 0.30 | 0.00 |      |      |      |      |      |

| Nom    | 0.85 | _    | 0.203<br>REF | 0.30 | 6.00<br>BSC | 6.00<br>BSC | 4.40 | 4.40 | 0.65<br>BSC | 0.35 |      | 0.10 | 0.10 | 0.10 | 0.05 | 0.08 |

| Max    | 0.90 | 0.05 |              | 0.35 |             |             | 4.50 | 4.50 |             | 0.40 | 0.10 |      |      |      |      |      |

| Table 11.1. | QFN32 | (Dimensions | in mm) |

|-------------|-------|-------------|--------|

|-------------|-------|-------------|--------|

The QFN32 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx

Corrected pin number for symbol P3 in Table 11.2 QFN32 PCB Land Pattern Dimensions (Dimensions in mm) on page 191.

Updated package marking figures to include temperature grade.

#### 13.3 Revision 1.90

May 22nd, 2015

For devices with an ADC, Added clarification on conditions for INL<sub>ADC</sub> and DNL<sub>ADC</sub> parameters.

Corrected EM2 current consumption condition in Electrical Characteristics section.

Added AUXHFRCO to block diagram and Electrical Characteristics.

Updated HFRCO table in the Electrical Characteristics section.

Updated EM0, EM2, EM3, and EM4 maximum current specifications in the Electrical Characteristics section.

Updated the Output Low Voltage maximum for sinking 20 mA with VDD = 3.0 V in the Electrical Characteristics section.

Updated the Input Leakage Current maximum in the Electrical Characteristics section.

Updated the minimum and maximum frequency specifications for the LFRCO, HFRCO, and AUXHFRCO in the Electrical Characteristics section.

Updated the maximum current consumption of the HFRCO in the Electrical Characteristics section.

Updated the maximum current consumption of the HFRCO in the Electrical Characteristics section.

Added some minimum ADC SNR, SNDR, and SFDR specifications in the Electrical Characteristics section.

Added some minimum and maximum ADC offset voltage, DNL, and INL specifications in the Electrical Characteristics section.

Added maximum DAC current specifications in the Electrical Characteristics section.

Added maximum ACMP current and maximum and minimum offset voltage specifications in the Electrical Characteristics section.

Added maximum VCMP current and updated typical VCMP current specifications in the Electrical Characteristics section.

Updated references to energyAware Designer to Configurator.

#### 13.4 Revision 1.80

July 2nd, 2014 Corrected single power supply voltage minimum value from 1.85V to 1.98V. Updated current consumption. Updated transition between energy modes. Updated power management data. Updated GPIO data. Updated LFXO, HFXO, HFRCO and ULFRCO data. Updated LFRCO and HFRCO plots.

For devices with an ACMP, updated ACMP data.

# 13.13 Revision 1.10

September 13th, 2010

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

For LQFP100 devices, corrected number of GPIO pins.

Added typical values for  $\mathsf{R}_{\mathsf{ADCFILT}}$  and  $\mathsf{C}_{\mathsf{ADCFILT}}.$

Added two conditions for DAC clock frequency; one for sample/hold and one for sample/off.

Added RoHS information and specified leadframe/solderballs material.

Added Serial Bootloader to feature list and system summary.

Updated ADC characterization data.

Updated DAC characterization data.

Updated RCO characterization data.

Updated ACMP characterization data.

Updated VCMP characterization data.

# 13.14 Revision 1.00

April 23rd, 2010

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880EFM32G890

ADC VCM line removed.

Added pinout illustration and additional pinout table.

Changed "Errata" chapter. Errata description moved to separate document.

Document changed status from "Preliminary".

Updated "Electrical Characteristics" chapter.

For EFM32G222

May 20th, 2011

Updated LFXO load capacitance section.