Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                              |

| Number of I/O              | 53                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                            |

| Data Converters            | A/D 8x12b; D/A 1x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-TQFP                                                                 |

| Supplier Device Package    | 64-TQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g232f32g-e-qfp64 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Supply Voltage Comparator

- · Ultra efficient Power-on Reset and Brown-Out Detector

- · 2-pin Serial Wire Debug Interface

- 1-pin Serial Wire Viewer

- Pre-Programmed USB/UART Bootloader

- Temperature range -40 to 85 °C

- Single power supply 1.98 to 3.8 V

- Packages

- BGA112

- LQFP100

- TQFP64

- TQFP48

- QFN64

- QFN32

# 3.2.2 EFM32G210

The features of the EFM32G210 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

Table 3.2. EFM32G210 Configuration Summary

| Module    | Configuration                            | Pin Connections                               |

|-----------|------------------------------------------|-----------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                            |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                 |

| MSC       | Full configuration                       | NA                                            |

| DMA       | Full configuration                       | NA                                            |

| RMU       | Full configuration                       | NA                                            |

| EMU       | Full configuration                       | NA                                            |

| СМИ       | Full configuration                       | CMU_OUT0, CMU_OUT1                            |

| WDOG      | Full configuration                       | NA                                            |

| PRS       | Full configuration                       | NA                                            |

| I2C0      | Full configuration                       | I2C0_SDA, I2C0_SCL                            |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS               |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS               |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                              |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                  |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                  |

| RTC       | Full configuration                       | NA                                            |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                   |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                  |

| ACMP0     | Full configuration                       | ACMP0_CH[1:0], ACMP0_O                        |

| ACMP1     | Full configuration                       | ACMP1_CH[7:5], ACMP1_O                        |

| VCMP      | Full configuration                       | NA                                            |

| ADC0      | Full configuration                       | ADC0_CH[7:4]                                  |

| DAC0      | Full configuration                       | DAC0_OUT[0]                                   |

| AES       | Full configuration                       | NA                                            |

| GPIO      | 24 pins                                  | Available pins are shown in Table 4.3 (p. 57) |

# 3.2.5 EFM32G232

The features of the EFM32G232 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

Table 3.5. EFM32G232 Configuration Summary

| Module    | Configuration                            | Pin Connections                               |

|-----------|------------------------------------------|-----------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                            |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                 |

| MSC       | Full configuration                       | NA                                            |

| DMA       | Full configuration                       | NA                                            |

| RMU       | Full configuration                       | NA                                            |

| EMU       | Full configuration                       | NA                                            |

| СМИ       | Full configuration                       | CMU_OUT0, CMU_OUT1                            |

| WDOG      | Full configuration                       | NA                                            |

| PRS       | Full configuration                       | NA                                            |

| I2C0      | Full configuration                       | I2C0_SDA, I2C0_SCL                            |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS               |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS               |

| USART2    | Full configuration                       | US2_TX, US2_RX, US2_CLK, US2_CS               |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                              |

| LEUART1   | Full configuration                       | LEU1_TX, LEU1_RX                              |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                  |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                  |

| TIMER2    | Full configuration                       | TIM2_CC[2:0]                                  |

| RTC       | Full configuration                       | NA                                            |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                   |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                  |

| PCNT1     | Full configuration, 8-bit count register | PCNT1_S[1:0]                                  |

| PCNT2     | Full configuration, 8-bit count register | PCNT2_S[1:0]                                  |

| ACMP0     | Full configuration                       | ACMP0_CH[7:0], ACMP0_O                        |

| ACMP1     | Full configuration                       | ACMP1_CH[15:8], ACMP1_O                       |

| VCMP      | Full configuration                       | NA                                            |

| ADC0      | Full configuration                       | ADC0_CH[7:0]                                  |

| DAC0      | Full configuration                       | DAC0_OUT[0]                                   |

| AES       | Full configuration                       | NA                                            |

| GPIO      | 53 pins                                  | Available pins are shown in Table 4.3 (p. 57) |

| Module | Configuration | Pin Connections                                               |

|--------|---------------|---------------------------------------------------------------|

| LCD    |               | LCD_SEG[39:0], LCD_COM[7:0], LCD_BCAP_P, LCD_BCAP_N, LCD_BEXT |

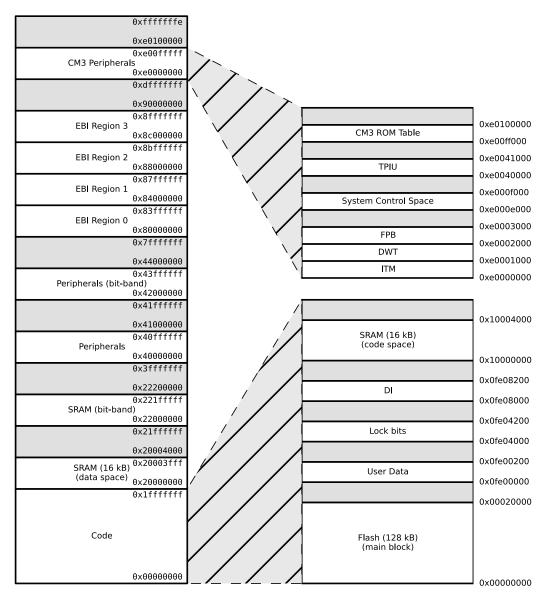

### 3.3 Memory Map

The EFM32G memory map is shown in the figure below. RAM and Flash sizes are for the largest memory configuration.

Figure 3.2. System Address Space with Core and Code Space Listing

| Parameter                                                            | Symbol              | Test Condition                                                                          | Min                  | Тур                  | Max                  | Unit |

|----------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------------------|----------------------|----------------------|----------------------|------|

|                                                                      |                     | Sinking 0.1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST          | _                    | 0.20×V <sub>DD</sub> | _                    | V    |

|                                                                      |                     | Sinking 0.1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOWEST           | _                    | 0.10×V <sub>DD</sub> | _                    | V    |

|                                                                      |                     | Sinking 1 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW               | _                    | 0.10×V <sub>DD</sub> | _                    | V    |

| Output low voltage (Production test condition = 3.0 V, DRIVE-        | V                   | Sinking 1 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= LOW                | _                    | 0.05×V <sub>DD</sub> | _                    | V    |

| MODE = STANDARD)                                                     | V <sub>IOOL</sub>   | Sinking 6 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD          | _                    | _                    | 0.30×V <sub>DD</sub> | V    |

|                                                                      |                     | Sinking 6 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= STANDARD           | _                    | _                    | 0.20×V <sub>DD</sub> | V    |

|                                                                      |                     | Sinking 20 mA, V <sub>DD</sub> =1.98 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH             | _                    | _                    | 0.35×V <sub>DD</sub> | V    |

|                                                                      |                     | Sinking 20 mA, V <sub>DD</sub> =3.0 V,<br>GPIO_Px_CTRL DRIVEMODE<br>= HIGH              | _                    | _                    | 0.25×V <sub>DD</sub> | V    |

| Input leakage current                                                | I <sub>IOLEAK</sub> | High Impedance IO connected to GROUND or V <sub>DD</sub>                                | _                    | ±0.1                 | ±40                  | nA   |

| I/O pin pull-up resistor                                             | R <sub>PU</sub>     |                                                                                         | <u> </u>             | 40                   | _                    | kΩ   |

| I/O pin pull-down resistor                                           | R <sub>PD</sub>     |                                                                                         | _                    | 40                   | _                    | kΩ   |

| Internal ESD series resistor                                         | R <sub>IOESD</sub>  |                                                                                         | _                    | 200                  | _                    | Ω    |

| Pulse width of pulses to be removed by the glitch suppression filter | tioglitch           |                                                                                         | 10                   | _                    | 50                   | ns   |

| Output fall time                                                     | 4                   | GPIO_Px_CTRL DRIVEMODE<br>= LOWEST and load capaci-<br>tance C <sub>L</sub> =12.5-25pF. | 20+0.1C <sub>L</sub> | _                    | 250                  | ns   |

| Output fall time                                                     | t <sub>IOOF</sub>   | GPIO_Px_CTRL DRIVEMODE<br>= LOW and load capacitance<br>C <sub>L</sub> =350-600pF       | 20+0.1C <sub>L</sub> | _                    | 250                  | ns   |

| I/O pin hysteresis (V <sub>IOTHR+</sub> - V <sub>IOTHR-</sub> )      | V <sub>IOHYST</sub> | V <sub>DD</sub> = 1.98 - 3.8 V                                                          | 0.1×V <sub>DD</sub>  | _                    | _                    | V    |

# Note:

1. If the GPIO input voltage is between 0.3×V $_{DD}$  and 0.7×V $_{DD}$ , the current consumption will increase.

| Parameter                   | Symbol             | Test Condition                                                                                      | Min | Тур | Max | Unit |

|-----------------------------|--------------------|-----------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Signal-to-Noise Ratio (SNR) | SNR <sub>ADC</sub> | 200 kSamples/s, 12 bit, differential, V <sub>DD</sub> reference,ADC_CLK = 7 MHz, BIASPROG = 0x747   | 63  | 69  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference,ADC_CLK = 7 MHz, BIASPROG = 0x747 | _   | 70  | _   | dB   |

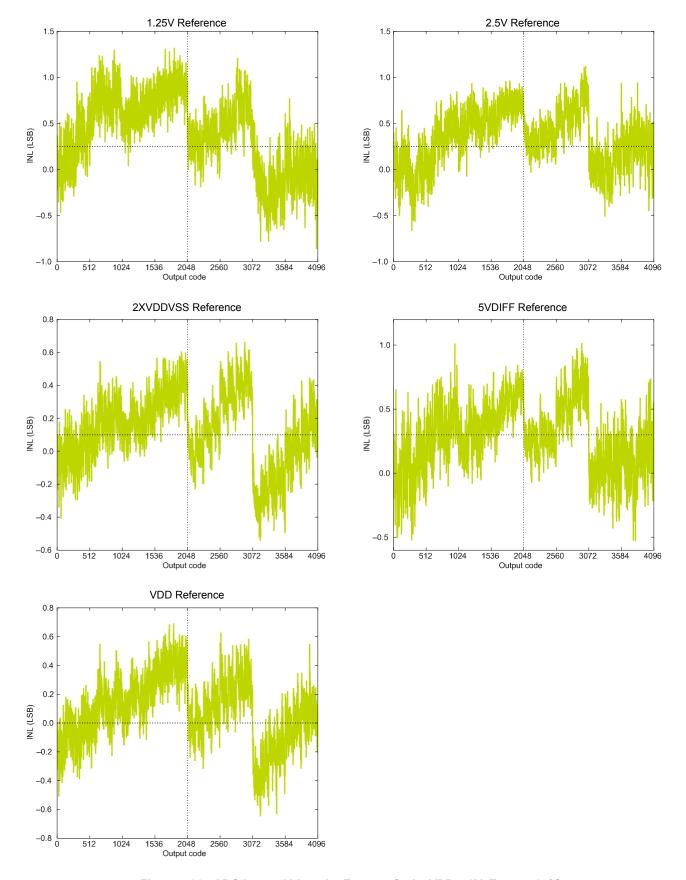

Figure 4.30. ADC Integral Linearity Error vs Code, VDD = 3V, Temp = 25°C

### 5.3 EFM32G230 (QFN64)

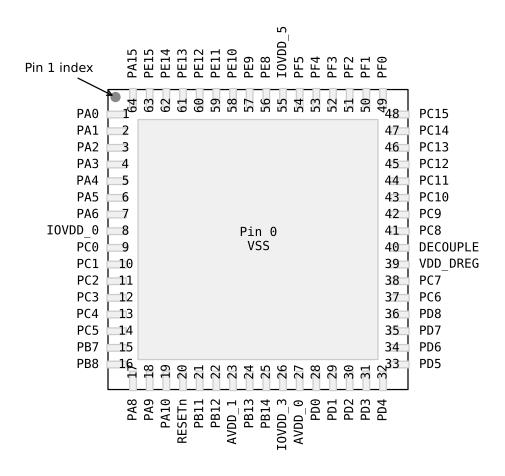

#### 5.3.1 Pinout

The EFM32G230 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \* ROUTE register in the module in question.

Figure 5.3. EFM32G230 Pinout (top view, not to scale)

Table 5.7. Device Pinout

| QFN64 P | Pin# and Name Pin Alternate Functionality / Description |         |               |               |             |

|---------|---------------------------------------------------------|---------|---------------|---------------|-------------|

| Pin#    | Pin Name                                                | Analog  | Timers        | Communication | Other       |

| 0       | VSS                                                     | Ground. |               |               |             |

| 1       | PA0                                                     |         | TIM0_CC0 #0/1 | I2C0_SDA #0   |             |

| 2       | PA1                                                     |         | TIM0_CC1 #0/1 | I2C0_SCL #0   | CMU_CLK1 #0 |

| 3       | PA2                                                     |         | TIM0_CC2 #0/1 |               | CMU_CLK0 #0 |

| 4       | PA3                                                     |         | TIM0_CDTI0 #0 |               |             |

| 5       | PA4                                                     |         | TIM0_CDTI1 #0 |               |             |

### 5.4.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

Table 5.11. Alternate functionality overview

| Alternate     |      |      |   |   | LOCATION                                                                              |

|---------------|------|------|---|---|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                                                           |

| ACMP0_CH4     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                                                   |

| ACMP0_CH5     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                                                   |

| ACMP0_CH6     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                                                   |

| ACMP0_CH7     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                                                   |

| ACMP0_O       | PE13 |      |   |   | Analog comparator ACMP0, digital output.                                              |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                                                   |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP1, channel 1.                                                   |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP1, channel 2.                                                   |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP1, channel 3.                                                   |

| ACMP1_O       | PF2  |      |   |   | Analog comparator ACMP1, digital output.                                              |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0.                             |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1.                             |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2.                             |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3.                             |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4.                             |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5.                             |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6.                             |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7.                             |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                                                        |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                                                        |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.                                         |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.                                         |

| DAC0_OUT0     | PB11 |      |   |   | Digital to Analog Converter DAC0 output channel number 0.                             |

|               |      |      |   |   | Debug-interface Serial Wire clock input.                                              |

| DBG_SWCLK     | PF0  | PF0  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down. |

|               |      |      |   |   | Debug-interface Serial Wire data input / output.                                      |

| DBG_SWDIO     | PF1  | PF1  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.   |

|      | P100 Pin#<br>d Name |        | Pi          | n Alternate Functionalit |               |            |

|------|---------------------|--------|-------------|--------------------------|---------------|------------|

| Pin# | Pin Name            | Analog | EBI         | Timers                   | Communication | Other      |

| 92   | PE8                 |        | EBI_AD00 #0 | PCNT2_S0IN #1            |               |            |

| 93   | PE9                 |        | EBI_AD01 #0 | PCNT2_S1IN #1            |               |            |

| 94   | PE10                |        | EBI_AD02 #0 | TIM1_CC0 #1              | US0_TX #0     | BOOT_TX    |

| 95   | PE11                |        | EBI_AD03 #0 | TIM1_CC1 #1              | US0_RX #0     | BOOT_RX    |

| 96   | PE12                |        | EBI_AD04 #0 | TIM1_CC2 #1              | US0_CLK #0    |            |

| 97   | PE13                |        | EBI_AD05 #0 |                          | US0_CS #0     | ACMP0_O #0 |

| 98   | PE14                |        | EBI_AD06 #0 |                          | LEU0_TX #2    |            |

| 99   | PE15                |        | EBI_AD07 #0 |                          | LEU0_RX #2    |            |

| 100  | PA15                |        | EBI_AD08 #0 |                          |               |            |

| Alternate     |      |      |   |   | LOCATION                                                                                        |

|---------------|------|------|---|---|-------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                                                                     |

| DAC0_OUT0     | PB11 |      |   |   | Digital to Analog Converter DAC0 output channel number 0.                                       |

| DAC0_OUT1     | PB12 |      |   |   | Digital to Analog Converter DAC0 output channel number 1.                                       |

|               |      |      |   |   | Debug-interface Serial Wire clock input.                                                        |

| DBG_SWCLK     | PF0  | PF0  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.           |

|               |      |      |   |   | Debug-interface Serial Wire data input / output.                                                |

| DBG_SWDIO     | PF1  | PF1  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.             |

|               |      |      |   |   | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO       | PF2  | PC15 |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |

| EBI_AD00      | PE8  |      |   |   | External Bus Interface (EBI) address and data input / output pin 00.                            |

| EBI_AD01      | PE9  |      |   |   | External Bus Interface (EBI) address and data input / output pin 01.                            |

| EBI_AD02      | PE10 |      |   |   | External Bus Interface (EBI) address and data input / output pin 02.                            |

| EBI_AD03      | PE11 |      |   |   | External Bus Interface (EBI) address and data input / output pin 03.                            |

| EBI_AD04      | PE12 |      |   |   | External Bus Interface (EBI) address and data input / output pin 04.                            |

| EBI_AD05      | PE13 |      |   |   | External Bus Interface (EBI) address and data input / output pin 05.                            |

| EBI_AD06      | PE14 |      |   |   | External Bus Interface (EBI) address and data input / output pin 06.                            |

| EBI_AD07      | PE15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 07.                            |

| EBI_AD08      | PA15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 08.                            |

| EBI_AD09      | PA0  |      |   |   | External Bus Interface (EBI) address and data input / output pin 09.                            |

| EBI_AD10      | PA1  |      |   |   | External Bus Interface (EBI) address and data input / output pin 10.                            |

| EBI_AD11      | PA2  |      |   |   | External Bus Interface (EBI) address and data input / output pin 11.                            |

| EBI_AD12      | PA3  |      |   |   | External Bus Interface (EBI) address and data input / output pin 12.                            |

| EBI_AD13      | PA4  |      |   |   | External Bus Interface (EBI) address and data input / output pin 13.                            |

| EBI_AD14      | PA5  |      |   |   | External Bus Interface (EBI) address and data input / output pin 14.                            |

| EBI_AD15      | PA6  |      |   |   | External Bus Interface (EBI) address and data input / output pin 15.                            |

| EBI_ALE       | PF3  |      |   |   | External Bus Interface (EBI) Address Latch Enable output.                                       |

### 5.7.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

Table 5.20. Alternate functionality overview

| Alternate     |      |        |   |   | LOCATION                                                                              |

|---------------|------|--------|---|---|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1      | 2 | 3 | Description                                                                           |

| ACMP0_CH4     | PC4  |        |   |   | Analog comparator ACMP0, channel 4.                                                   |

| ACMP0_CH5     | PC5  |        |   |   | Analog comparator ACMP0, channel 5.                                                   |

| ACMP0_CH6     | PC6  |        |   |   | Analog comparator ACMP0, channel 6.                                                   |

| ACMP0_CH7     | PC7  |        |   |   | Analog comparator ACMP0, channel 7.                                                   |

| ACMP0_O       | PE13 |        |   |   | Analog comparator ACMP0, digital output.                                              |

| ACMP1_CH4     | PC12 |        |   |   | Analog comparator ACMP1, channel 4.                                                   |

| ACMP1_CH5     | PC13 |        |   |   | Analog comparator ACMP1, channel 5.                                                   |

| ACMP1_CH6     | PC14 |        |   |   | Analog comparator ACMP1, channel 6.                                                   |

| ACMP1_CH7     | PC15 |        |   |   | Analog comparator ACMP1, channel 7.                                                   |

| ACMP1_O       | PF2  |        |   |   | Analog comparator ACMP1, digital output.                                              |

| ADC0_CH0      | PD0  |        |   |   | Analog to digital converter ADC0, input channel number 0.                             |

| ADC0_CH1      | PD1  |        |   |   | Analog to digital converter ADC0, input channel number 1.                             |

| ADC0_CH2      | PD2  |        |   |   | Analog to digital converter ADC0, input channel number 2.                             |

| ADC0_CH3      | PD3  |        |   |   | Analog to digital converter ADC0, input channel number 3.                             |

| ADC0_CH4      | PD4  |        |   |   | Analog to digital converter ADC0, input channel number 4.                             |

| ADC0_CH5      | PD5  |        |   |   | Analog to digital converter ADC0, input channel number 5.                             |

| ADC0_CH6      | PD6  |        |   |   | Analog to digital converter ADC0, input channel number 6.                             |

| ADC0_CH7      | PD7  |        |   |   | Analog to digital converter ADC0, input channel number 7.                             |

| BOOT_RX       | PE11 |        |   |   | Bootloader RX.                                                                        |

| BOOT_TX       | PE10 |        |   |   | Bootloader TX.                                                                        |

| CMU_CLK0      | PA2  | PC12   |   |   | Clock Management Unit, clock output number 0.                                         |

| CMU_CLK1      | PA1  | PD8    |   |   | Clock Management Unit, clock output number 1.                                         |

| DAC0_OUT0     | PB11 |        |   |   | Digital to Analog Converter DAC0 output channel number 0.                             |

| DAC0_OUT1     | PB12 |        |   |   | Digital to Analog Converter DAC0 output channel number 1.                             |

|               |      |        |   |   | Debug-interface Serial Wire clock input.                                              |

| DBG_SWCLK     | PF0  | F0 PF0 |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down. |

|               |      |        |   |   | Debug-interface Serial Wire data input / output.                                      |

| DBG_SWDIO     | PF1  | PF1    |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.   |

| Alternate     |      |      |     |   | LOCATION                                                                                                                                                      |

|---------------|------|------|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2   | 3 | Description                                                                                                                                                   |

|               |      |      |     |   | Debug-interface Serial Wire viewer Output.                                                                                                                    |

| DBG_SWO       | PF2  | PC15 |     |   | Note that this function is not enabled after reset, and must be enabled by software to be used.                                                               |

| HFXTAL_N      | PB14 |      |     |   | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                          |

| HFXTAL_P      | PB13 |      |     |   | High Frequency Crystal positive pin.                                                                                                                          |

| I2C0_SCL      | PA1  | PD7  | PC7 |   | I2C0 Serial Clock Line input / output.                                                                                                                        |

| I2C0_SDA      | PA0  | PD6  | PC6 |   | I2C0 Serial Data input / output.                                                                                                                              |

| LCD_BCAP_N    | PA13 |      |     |   | LCD voltage booster (optional), boost capacitor, negative pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P. |

| LCD_BCAP_P    | PA12 |      |     |   | LCD voltage booster (optional), boost capacitor, positive pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P. |

|               |      |      |     |   | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.                            |

| LCD_BEXT      | PA14 |      |     |   | An external LCD voltage may also be applied to this pin if the booster is not enabled.                                                                        |

|               |      |      |     |   | If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO.                                                       |

| LCD_COM0      | PE4  |      |     |   | LCD driver common line number 0.                                                                                                                              |

| LCD_COM1      | PE5  |      |     |   | LCD driver common line number 1.                                                                                                                              |

| LCD_COM2      | PE6  |      |     |   | LCD driver common line number 2.                                                                                                                              |

| LCD_COM3      | PE7  |      |     |   | LCD driver common line number 3.                                                                                                                              |

| LCD_SEG0      | PF2  |      |     |   | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG1      | PF3  |      |     |   | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG2      | PF4  |      |     |   | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG3      | PF5  |      |     |   | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                          |

| LCD_SEG4      | PE8  |      |     |   | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG5      | PE9  |      |     |   | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG6      | PE10 |      |     |   | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG7      | PE11 |      |     |   | LCD segment line 7. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                          |

| LCD_SEG8      | PE12 |      |     |   | LCD segment line 8. Segments 8, 9, 10 and 11 are controlled by SEGEN2.                                                                                        |

| Alternate     |      |      |   |   | LOCATION                                                                                        |

|---------------|------|------|---|---|-------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                                                                     |

| DAC0_OUT0     | PB11 |      |   |   | Digital to Analog Converter DAC0 output channel number 0.                                       |

| DAC0_OUT1     | PB12 |      |   |   | Digital to Analog Converter DAC0 output channel number 1.                                       |

|               |      |      |   |   | Debug-interface Serial Wire clock input.                                                        |

| DBG_SWCLK     | PF0  | PF0  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull down.           |

|               |      |      |   |   | Debug-interface Serial Wire data input / output.                                                |

| DBG_SWDIO     | PF1  | PF1  |   |   | Note that this function is enabled to pin out of reset, and has a built-in pull up.             |

|               |      |      |   |   | Debug-interface Serial Wire viewer Output.                                                      |

| DBG_SWO       | PF2  | PC15 |   |   | Note that this function is not enabled after reset, and must be enabled by software to be used. |

| EBI_AD00      | PE8  |      |   |   | External Bus Interface (EBI) address and data input / output pin 00.                            |

| EBI_AD01      | PE9  |      |   |   | External Bus Interface (EBI) address and data input / output pin 01.                            |

| EBI_AD02      | PE10 |      |   |   | External Bus Interface (EBI) address and data input / output pin 02.                            |

| EBI_AD03      | PE11 |      |   |   | External Bus Interface (EBI) address and data input / output pin 03.                            |

| EBI_AD04      | PE12 |      |   |   | External Bus Interface (EBI) address and data input / output pin 04.                            |

| EBI_AD05      | PE13 |      |   |   | External Bus Interface (EBI) address and data input / output pin 05.                            |

| EBI_AD06      | PE14 |      |   |   | External Bus Interface (EBI) address and data input / output pin 06.                            |

| EBI_AD07      | PE15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 07.                            |

| EBI_AD08      | PA15 |      |   |   | External Bus Interface (EBI) address and data input / output pin 08.                            |

| EBI_AD09      | PA0  |      |   |   | External Bus Interface (EBI) address and data input / output pin 09.                            |

| EBI_AD10      | PA1  |      |   |   | External Bus Interface (EBI) address and data input / output pin 10.                            |

| EBI_AD11      | PA2  |      |   |   | External Bus Interface (EBI) address and data input / output pin 11.                            |

| EBI_AD12      | PA3  |      |   |   | External Bus Interface (EBI) address and data input / output pin 12.                            |

| EBI_AD13      | PA4  |      |   |   | External Bus Interface (EBI) address and data input / output pin 13.                            |

| EBI_AD14      | PA5  |      |   |   | External Bus Interface (EBI) address and data input / output pin 14.                            |

| EBI_AD15      | PA6  |      |   |   | External Bus Interface (EBI) address and data input / output pin 15.                            |

| EBI_ALE       | PF3  |      |   |   | External Bus Interface (EBI) Address Latch Enable output.                                       |

|       | 12 Pin# and<br>Name | Pin Alternate Functionality / Description                                                                                     |                            |               |                           |             |  |

|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------|---------------------------|-------------|--|

| Pin # | Pin Name            | Analog                                                                                                                        | EBI                        | Timers        | Communication             | Other       |  |

| E9    | PE0                 |                                                                                                                               |                            | PCNT0_S0IN #1 | U0_TX #1                  |             |  |

| E10   | PE1                 |                                                                                                                               |                            | PCNT0_S1IN #1 | U0_RX #1                  |             |  |

| E11   | PE3                 |                                                                                                                               |                            |               |                           | ACMP1_O #1  |  |

| F1    | PB1                 | LCD_SEG<br>33                                                                                                                 |                            | TIM1_CC1 #2   |                           |             |  |

| F2    | PB2                 | LCD_SEG<br>34                                                                                                                 |                            | TIM1_CC2 #2   |                           |             |  |

| F3    | PB3                 | LCD_SEG<br>20                                                                                                                 |                            | PCNT1_S0IN #1 | US2_TX #1                 |             |  |

| F4    | PB4                 | LCD_SEG<br>21                                                                                                                 |                            | PCNT1_S1IN #1 | US2_RX #1                 |             |  |

| F8    | VDD_DRE<br>G        | Power supp                                                                                                                    | ly for on-chip voltage reg | ulator.       |                           |             |  |

| F9    | VSS_DRE<br>G        | Ground for o                                                                                                                  | on-chip voltage regulator. |               |                           |             |  |

| F10   | PE2                 |                                                                                                                               |                            |               |                           | ACMP0_O #1  |  |

| F11   | DECOU-<br>PLE       | Decouple output for on-chip voltage regulator. An external capacitance of size C <sub>DECOUPLE</sub> is required at this pin. |                            |               |                           |             |  |

| G1    | PB5                 | LCD_SEG<br>22                                                                                                                 |                            |               | US2_CLK #1                |             |  |

| G2    | PB6                 | LCD_SEG<br>23                                                                                                                 |                            |               | US2_CS #1                 |             |  |

| G3    | VSS                 | Ground.                                                                                                                       |                            |               |                           |             |  |

| G4    | IOVDD_0             | Digital IO power supply 0.                                                                                                    |                            |               |                           |             |  |

| G8    | IOVDD_4             | Digital IO power supply 4.                                                                                                    |                            |               |                           |             |  |

| G9    | VSS                 | Ground.                                                                                                                       |                            |               |                           |             |  |

| G10   | PC6                 | ACMP0_C<br>H6                                                                                                                 |                            |               | LEU1_TX #0<br>I2C0_SDA #2 |             |  |

| G11   | PC7                 | ACMP0_C<br>H7                                                                                                                 |                            |               | LEU1_RX #0<br>I2C0_SCL #2 |             |  |

| H1    | PC0                 | ACMP0_C<br>H0                                                                                                                 |                            | PCNT0_S0IN #2 | US1_TX #0                 |             |  |

| H2    | PC2                 | ACMP0_C<br>H2                                                                                                                 |                            |               | US2_TX #0                 |             |  |

| Н3    | PD14                |                                                                                                                               |                            |               | I2C0_SDA #3               |             |  |

| H4    | PA7                 | LCD_SEG<br>35                                                                                                                 |                            |               |                           |             |  |

| H5    | PA8                 | LCD_SEG<br>36                                                                                                                 |                            | TIM2_CC0 #0   |                           |             |  |

| H6    | VSS                 | Ground.                                                                                                                       |                            |               |                           |             |  |

| H7    | IOVDD_3             | Digital IO power supply 3.                                                                                                    |                            |               |                           |             |  |

| Н8    | PD8                 |                                                                                                                               |                            |               |                           | CMU_CLK1 #1 |  |

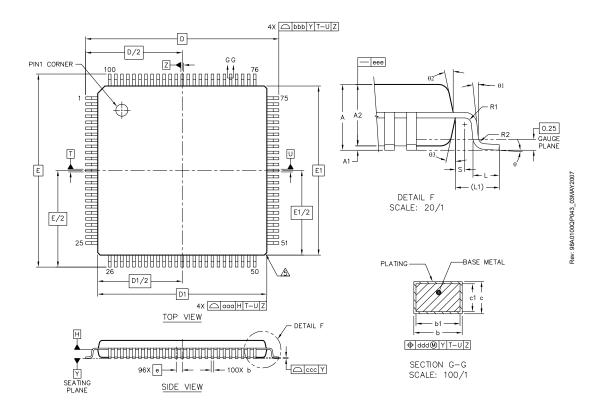

### 7. LQFP100 Package Specifications

### 7.1 LQFP100 Package Dimensions

Figure 7.1. LQFP100

#### Note:

- 1. Datum 'T', 'U' and 'Z' to be determined at datum plane 'H'

- 2. Datum 'D' and 'E' to be determined at seating plane datum 'Y'.

- 3. Dimension 'D1' and 'E1' do not include mold protrusions. Allowable protrusion is 0.25 per side. Dimensions 'D1' and 'E1' do include mold mismatch and are determined at datum plane datum 'H'.

- 4. Dimension 'b' does not include dambar protrusion. Allowable dambar protrusion shall not cause thelead width to exceed the maximum 'b' dimension by more than 0.08 mm. Dambar can not be located n the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm.

- 5. Exact shape of each corner is optional.

Table 7.1. LQFP100 (Dimensions in mm)

|                         | SYMBOL | MIN  | NOM | MAX  |

|-------------------------|--------|------|-----|------|

| total thickness         | A      | _    | _   | 1.6  |

| stand off               | A1     | 0.05 | _   | 0.15 |

| mold thickness          | A2     | 1.35 | 1.4 | 1.45 |

| lead width (plating)    | b      | 0.17 | 0.2 | 0.27 |

| lead width              | b1     | 0.17 | _   | 0.23 |

| L/F thickness (plating) | С      | 0.09 | _   | 0.2  |

| lead thickness          | c1     | 0.09 | _   | 0.16 |

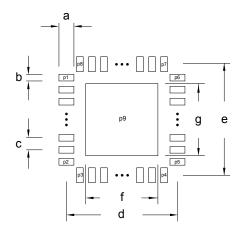

# 10.2 QFN64 PCB Layout

Figure 10.2. QFN64 PCB Land Pattern

Table 10.2. QFN64 PCB Land Pattern Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Pin Number | Symbol | Pin Number |

|--------|-----------|--------|------------|--------|------------|

| а      | 0.85      | P1     | 1          | P8     | 64         |

| b      | 0.30      | P2     | 16         | P9     | 65         |

| С      | 0.50      | P3     | 17         |        |            |

| d      | 8.90      | P4     | 32         |        |            |

| е      | 8.90      | P5     | 33         |        |            |

| f      | 7.20      | P6     | 48         |        |            |

| g      | 7.20      | P7     | 49         |        |            |

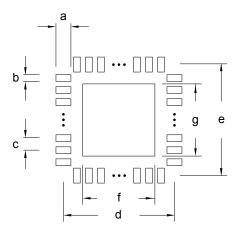

Figure 10.3. QFN64 PCB Solder Mask

Table 10.3. QFN64 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) | Symbol | Dim. (mm) |

|--------|-----------|--------|-----------|

| а      | 0.97      | е      | 8.90      |

| b      | 0.42      | f      | 7.32      |

| С      | 0.50      | g      | 7.32      |

### 13.9 Revision 1.40

February 27th, 2012

Updated Power Management section.

Corrected operating voltage from 1.8 V to 1.85 V.

Corrected TGRAD<sub>ADCTH</sub> parameter.

Corrected package drawing.

Updated PCB land pattern, solder mask and stencil design.

For LQFP48 devices, corrected available Pulse Counters from 3 to 2.

For LQFP48 devices, corrected available LEUARTs from 2 to 1.

For LQFP64 devices, corrected ordering codes in the ordering information table.

#### 13.10 Revision 1.30

May 20th, 2011

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

Updated LFXO load capacitance section.

#### 13.15 Revision 0.90

This revision applies the following devices:

• EFM32G222

Initial preliminary revision, April 14th, 2011

This revision applies the following devices:

- EFM32G232

- EFM32G842

Initial preliminary revision, June 30th, 2011

### 13.16 Revision 0.85

February 19th, 2010

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

Renamed DBG\_SWV pin to DBG\_SWO.

#### 13.17 Revision 0.84

February 11th, 2010

This revision applies the following devices:

- EFM32G230

- EFM32G840

Corrected pinout tables.

### 13.18 Revision 0.83

January 25th, 2010

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

Updated errata section.

Specified flash word width in Flash Electrical Characteristics.

Added Capacitive Sense Internal Resistor values in ACMP Electrical Characteristics.