# Silicon Labs - EFM32G280F32-QFP100 Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Discontinued at Digi-Key                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 32MHz                                                                 |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                            |

| Number of I/O              | 86                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 8K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                          |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

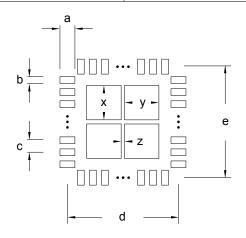

| Package / Case             | 100-LQFP                                                              |

| Supplier Device Package    | 100-LQFP (14x14)                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g280f32-qfp100 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.1.4 Direct Memory Access Controller (DMA)

The Direct Memory Access (DMA) controller performs memory operations independently of the CPU. This has the benefit of reducing the energy consumption and the workload of the CPU, and enables the system to stay in low energy modes when moving for instance data from the USART to RAM or from the External Bus Interface to a PWM-generating timer. The DMA controller uses the PL230 µDMA controller licensed from ARM.

### 3.1.5 Reset Management Unit (RMU)

The RMU is responsible for handling the reset functionality of the EFM32G.

### 3.1.6 Energy Management Unit (EMU)

The Energy Management Unit (EMU) manage all the low energy modes (EM) in EFM32G microcontrollers. Each energy mode manages if the CPU and the various peripherals are available. The EMU can also be used to turn off the power to unused SRAM blocks.

### 3.1.7 Clock Management Unit (CMU)

The Clock Management Unit (CMU) is responsible for controlling the oscillators and clocks on-board the EFM32G. The CMU provides the capability to turn on and off the clock on an individual basis to all peripheral modules in addition to enable/disable and configure the available oscillators. The high degree of flexibility enables software to minimize energy consumption in any specific application by not wasting power on peripherals and oscillators that are inactive.

### 3.1.8 Watchdog (WDOG)

The purpose of the watchdog timer is to generate a reset in case of a system failure, to increase application reliability. The failure may e.g. be caused by an external event, such as an ESD pulse, or by a software failure.

### 3.1.9 Peripheral Reflex System (PRS)

The Peripheral Reflex System (PRS) system is a network which lets the different peripheral module communicate directly with each other without involving the CPU. Peripheral modules which send out Reflex signals are called producers. The PRS routes these reflex signals to consumer peripherals which apply actions depending on the data received. The format for the Reflex signals is not given, but edge triggers and other functionality can be applied by the PRS.

#### 3.1.10 External Bus Interface (EBI)

The External Bus Interface provides access to external parallel interface devices such as SRAM, FLASH, ADCs and LCDs. The interface is memory mapped into the address bus of the Cortex-M3. This enables seamless access from software without manually manipulating the IO settings each time a read or write is performed. The data and address lines are multiplexed in order to reduce the number of pins required to interface the external devices. The timing is adjustable to meet specifications of the external devices. The interface is limited to asynchronous devices.

### 3.1.11 Inter-Integrated Circuit Interface (I2C)

The I<sup>2</sup>C module provides an interface between the MCU and a serial I<sup>2</sup>C-bus. It is capable of acting as both a master and a slave, and supports multi-master buses. Both standard-mode, fast-mode and fastmode plus speeds are supported, allowing transmission rates all the way from 10 kbit/s up to 1 Mbit/s. Slave arbitration and timeouts are also provided to allow implementation of an SMBus compliant system. The interface provided to software by the I<sup>2</sup>C module, allows both fine-grained control of the transmission process and close to automatic transfers. Automatic recognition of slave addresses is provided in all energy modes.

### 3.1.12 Universal Synchronous/Asynchronous Receiver/Transmitter (USART)

The Universal Synchronous Asynchronous serial Receiver and Transmitter (USART) is a very flexible serial I/O module. It supports full duplex asynchronous UART communication as well as RS-485, SPI, MicroWire and 3-wire. It can also interface with ISO7816 Smart-Cards, and IrDA devices.

#### 3.1.13 Pre-Programmed USB/UART Bootloader

The bootloader presented in application note AN0003 is pre-programmed in the device at factory. Autobaud and destructive write are supported. The autobaud feature, interface and commands are described further in the application note.

### 3.1.24 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

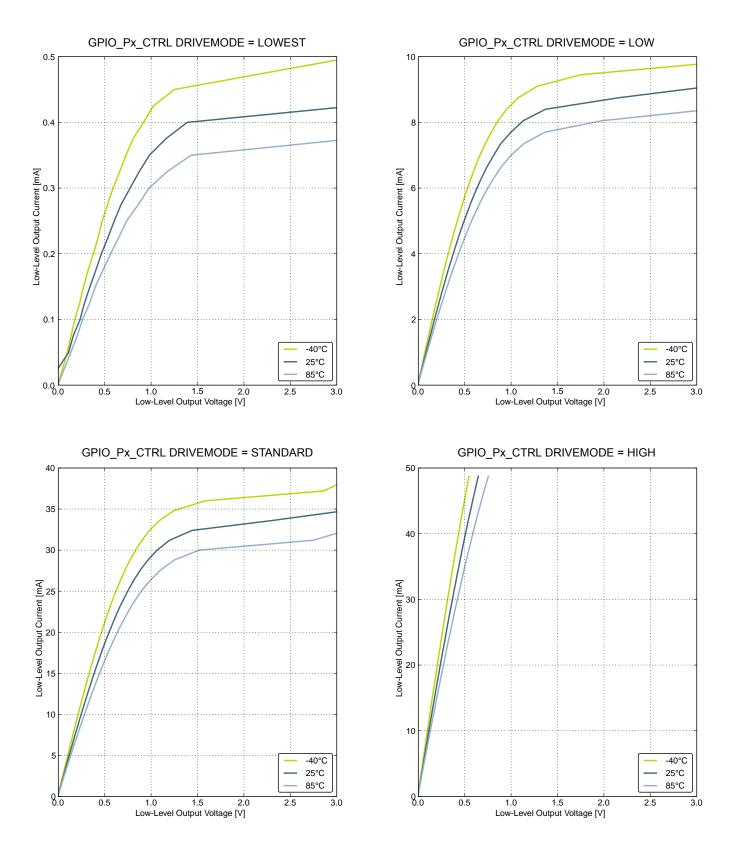

### 3.1.25 General Purpose Input/Output (GPIO)

General Purpose Input/Output (GPIO) pins are organized into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

# 3.1.26 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 4x40 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

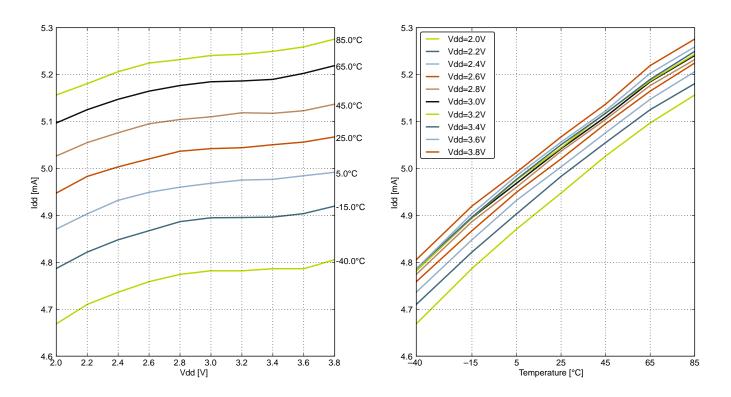

# 4.4.1 EM0 Current Consumption

Figure 4.1. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 28 MHz

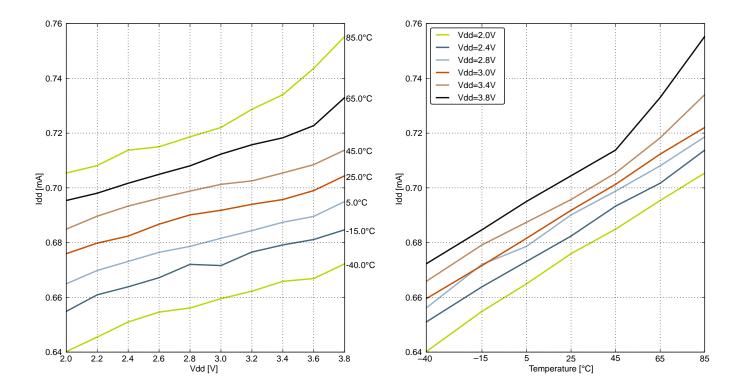

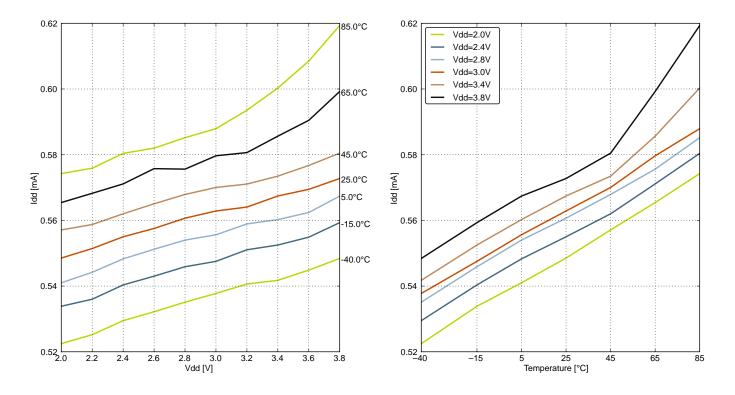

Figure 4.8. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 14 MHz

Figure 4.9. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 11 MHz

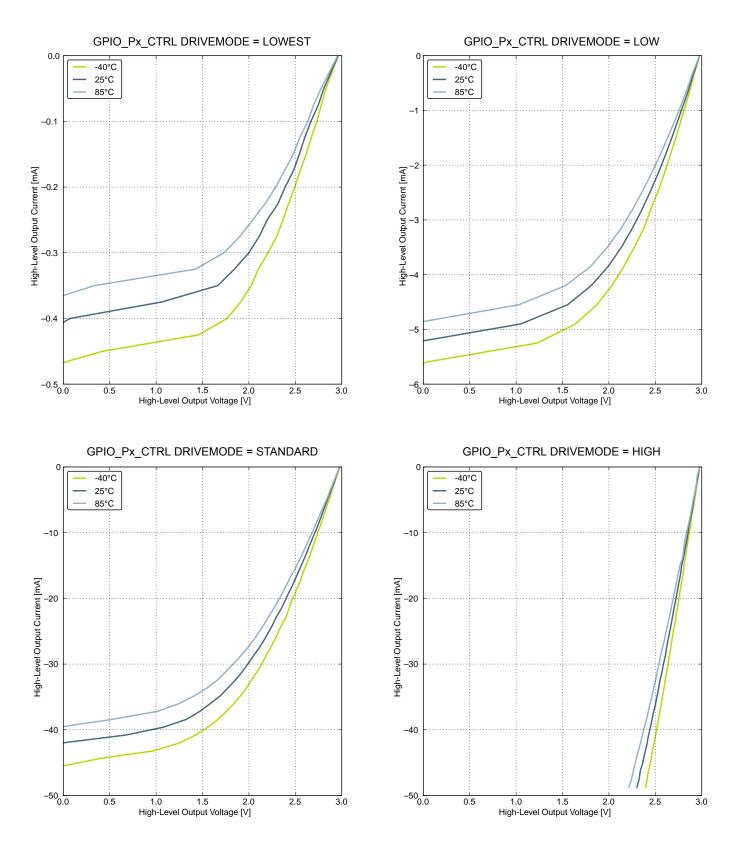

Figure 4.16. Typical Low-Level Output Current, 3V Supply Voltage

Figure 4.17. Typical High-Level Output Current, 3V Supply Voltage

# Table 4.9. HFXO

| Parameter                                                            | Symbol              | Test Condition                                                                           | Min | Тур | Max  | Unit |

|----------------------------------------------------------------------|---------------------|------------------------------------------------------------------------------------------|-----|-----|------|------|

| Supported nominal crystal Fre-<br>quency                             | f <sub>HFXO</sub>   |                                                                                          | 4   | —   | 32   | MHz  |

| Supported crystal equivalent ser-                                    | ESR <sub>HFXO</sub> | Crystal frequency 32 MHz                                                                 | _   | 30  | 60   | Ω    |

| ies resistance (ESR)                                                 | LOINHEXO            | Crystal frequency 4 MHz                                                                  | _   | 400 | 1500 | Ω    |

| The transconductance of the HFXO input transistor at crystal startup | 9 <sub>mHFXO</sub>  | HFXOBOOST in CMU_CTRL<br>equals 0b11                                                     | 20  |     | _    | mS   |

| Supported crystal external load range                                | C <sub>HFXOL</sub>  |                                                                                          | 5   |     | 25   | pF   |

| Current consumption for HFXO                                         | 1                   | 4 MHz: ESR=400 Ω, $C_L$ =20 pF,<br>HFXOBOOST in CMU_CTRL<br>equals 0b11                  | _   | 85  | _    | μA   |

| after startup                                                        | IHFXO               | 32 MHz: ESR=30 $\Omega$ , C <sub>L</sub> =10 pF,<br>HFXOBOOST in CMU_CTRL<br>equals 0b11 | _   | 165 | _    | μA   |

| Startup time                                                         | t <sub>HFXO</sub>   | 32 MHz: ESR=30 Ω, C <sub>L</sub> =10 pF,<br>HFXOBOOST in CMU_CTRL<br>equals 0b11         |     | 400 | _    | μs   |

| Pulse width removed by glitch de-<br>tector                          |                     |                                                                                          | 1   |     | 4    | ns   |

| Parameter                                          | Symbol              | Min | Тур | Max                 | Unit |

|----------------------------------------------------|---------------------|-----|-----|---------------------|------|

| SCL clock frequency                                | f <sub>SCL</sub>    | 0   | _   | 100 <sup>1</sup>    | kHz  |

| SCL clock low time                                 | t <sub>LOW</sub>    | 4.7 | _   | —                   | μs   |

| SCL clock high time                                | t <sub>HIGH</sub>   | 4.0 | _   | —                   | μs   |

| SDA set-up time                                    | t <sub>SU,DAT</sub> | 250 | _   | —                   | ns   |

| SDA hold time                                      | t <sub>HD,DAT</sub> | 8   | _   | 3450 <sup>2,3</sup> | ns   |

| Repeated START condition set-up time               | t <sub>SU,STA</sub> | 4.7 | _   | —                   | μs   |

| (Repeated) START condition hold time               | t <sub>HD,STA</sub> | 4.0 | —   | —                   | μs   |

| STOP condition set-up time                         | tsu,sto             | 4.0 | _   | _                   | μs   |

| Bus free time between a STOP and a START condition | t <sub>BUF</sub>    | 4.7 | _   | _                   | μs   |

# Table 4.19. I2C Standard-mode (Sm)

# Note:

1. For the minimum HFPERCLK frequency required in Standard-mode, see the I2C chapter in the EFM32G Reference Manual.

2. The maximum SDA hold time (t<sub>HD,DAT</sub>) needs to be met only when the device does not stretch the low time of SCL (t<sub>LOW</sub>).

3. When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((3450\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

# Table 4.20. I2C Fast-mode (Fm)

| Parameter                                          | Symbol              | Min | Тур | Max                | Unit |

|----------------------------------------------------|---------------------|-----|-----|--------------------|------|

| SCL clock frequency                                | f <sub>SCL</sub>    | 0   | _   | 400 <sup>1</sup>   | kHz  |

| SCL clock low time                                 | t <sub>LOW</sub>    | 1.3 | _   |                    | μs   |

| SCL clock high time                                | t <sub>HIGH</sub>   | 0.6 |     |                    | μs   |

| SDA set-up time                                    | t <sub>SU,DAT</sub> | 100 | _   | _                  | ns   |

| SDA hold time                                      | t <sub>HD,DAT</sub> | 8   |     | 900 <sup>2,3</sup> | ns   |

| Repeated START condition set-up time               | t <sub>SU,STA</sub> | 0.6 | _   |                    | μs   |

| (Repeated) START condition hold time               | t <sub>HD,STA</sub> | 0.6 |     |                    | μs   |

| STOP condition set-up time                         | t <sub>SU,STO</sub> | 0.6 | _   | _                  | μs   |

| Bus free time between a STOP and a START condition | t <sub>BUF</sub>    | 1.3 | _   | _                  | μs   |

# Note:

1. For the minimum HFPERCLK frequency required in Fast-mode, see the I2C chapter in the EFM32G Reference Manual.

2. The maximum SDA hold time ( $t_{HD,DAT}$ ) needs to be met only when the device does not stretch the low time of SCL ( $t_{LOW}$ ).

3. When transmitting data, this number is guaranteed only when I2Cn\_CLKDIV < ((900\*10<sup>-9</sup> [s] \* f<sub>HFPERCLK</sub> [Hz]) - 4).

|       | 18 Pin# and<br>Name |                         | Pin Alternate                                                          |                                 |                                              |

|-------|---------------------|-------------------------|------------------------------------------------------------------------|---------------------------------|----------------------------------------------|

| Pin # | Pin Name            | Analog                  | Timers                                                                 | Communication                   | Other                                        |

| 6     | PC0                 | ACMP0_CH0               | PCNT0_S0IN #2                                                          | US1_TX #0                       |                                              |

| 7     | PC1                 | ACMP0_CH1               | PCNT0_S1IN #2                                                          | US1_RX #0                       |                                              |

| 8     | PC2                 | ACMP0_CH2               |                                                                        |                                 |                                              |

| 9     | PC3                 | ACMP0_CH3               |                                                                        |                                 |                                              |

| 10    | PC4                 | ACMP0_CH4               | LETIM0_OUT0 #3<br>PCNT1_S0IN #0                                        |                                 |                                              |

| 11    | PB7                 | LFXTAL_P                |                                                                        | US1_CLK #0                      |                                              |

| 12    | PB8                 | LFXTAL_N                |                                                                        | US1_CS #0                       |                                              |

| 13    | PA8                 |                         | TIM2_CC0 #0                                                            |                                 |                                              |

| 14    | PA9                 |                         | TIM2_CC1 #0                                                            |                                 |                                              |

| 15    | PA10                |                         | TIM2_CC2 #0                                                            |                                 |                                              |

| 16    | RESETn              |                         | tive low.To apply an external re<br>nd let the internal pull-up ensure |                                 | uired to only drive this pin low             |

| 17    | PB11                | DAC0_OUT0               | LETIM0_OUT0 #1                                                         |                                 |                                              |

| 18    | VSS                 | Ground.                 |                                                                        |                                 |                                              |

| 19    | AVDD_1              | Analog power            | supply 1.                                                              |                                 |                                              |

| 20    | PB13                | HFXTAL_P                |                                                                        | LEU0_TX #1                      |                                              |

| 21    | PB14                | HFXTAL_N                |                                                                        | LEU0_RX #1                      |                                              |

| 22    | IOVDD_3             | Digital IO powe         | er supply 3.                                                           |                                 |                                              |

| 23    | AVDD_0              | Analog power            | supply 0.                                                              |                                 |                                              |

| 24    | PD4                 | ADC0_CH4                |                                                                        | LEU0_TX #0                      |                                              |

| 25    | PD5                 | ADC0_CH5                |                                                                        | LEU0_RX #0                      |                                              |

| 26    | PD6                 | ADC0_CH6                | LETIM0_OUT0 #0                                                         | I2C0_SDA #1                     |                                              |

| 27    | PD7                 | ADC0_CH7                | LETIM0_OUT1 #0                                                         | I2C0_SCL #1                     |                                              |

| 28    | VDD_DREG            | Power supply f          | or on-chip voltage regulator.                                          |                                 |                                              |

| 29    | DECOUPLE            | Decouple outpup<br>pin. | ut for on-chip voltage regulator.                                      | An external capacitance of size | ze $C_{\text{DECOUPLE}}$ is required at this |

| 30    | PC8                 | ACMP1_CH0               | TIM2_CC0 #2                                                            | US0_CS #2                       |                                              |

| 31    | PC9                 | ACMP1_CH1               | TIM2_CC1 #2                                                            | US0_CLK #2                      |                                              |

| 32    | PC10                | ACMP1_CH2               | TIM2_CC2 #2                                                            | US0_RX #2                       |                                              |

| 33    | PC11                | ACMP1_CH3               |                                                                        | US0_TX #2                       |                                              |

| 34    | PC13                | ACMP1_CH5               | TIM0_CDTI0 #1/3 TIM1_CC0<br>#0 PCNT0_S0IN #0                           |                                 |                                              |

| 35    | PC14                | ACMP1_CH6               | TIM0_CDTI1 #1/3 TIM1_CC1<br>#0 PCNT0_S1IN #0                           |                                 |                                              |

| 36    | PC15                | ACMP1_CH7               | TIM0_CDTI2 #1/3 TIM1_CC2<br>#0                                         |                                 | DBG_SWO #1                                   |

| 37    | PF0                 |                         | LETIM0_OUT0 #2                                                         |                                 | DBG_SWCLK #0/1                               |

### 5.4.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      |   |   | LOCATION                                                                                                                                |

|---------------|------|------|---|---|-----------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                                                                                                             |

| ACMP0_CH4     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                                                                                                     |

| ACMP0_CH5     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                                                                                                     |

| ACMP0_CH6     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                                                                                                     |

| ACMP0_CH7     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                                                                                                     |

| ACMP0_O       | PE13 |      |   |   | Analog comparator ACMP0, digital output.                                                                                                |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                                                                                                     |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP1, channel 1.                                                                                                     |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP1, channel 2.                                                                                                     |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP1, channel 3.                                                                                                     |

| ACMP1_O       | PF2  |      |   |   | Analog comparator ACMP1, digital output.                                                                                                |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0.                                                                               |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1.                                                                               |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2.                                                                               |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3.                                                                               |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4.                                                                               |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5.                                                                               |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6.                                                                               |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7.                                                                               |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                                                                                                          |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                                                                                                          |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.                                                                                           |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.                                                                                           |

| DAC0_OUT0     | PB11 |      |   |   | Digital to Analog Converter DAC0 output channel number 0.                                                                               |

| DBG_SWCLK     | PF0  | PF0  |   |   | Debug-interface Serial Wire clock input.<br>Note that this function is enabled to pin out of reset, and has a built-in pull down.       |

| DBG_SWDIO     | PF1  | PF1  |   |   | Debug-interface Serial Wire data input / output.<br>Note that this function is enabled to pin out of reset, and has a built-in pull up. |

### Table 5.11. Alternate functionality overview

|       | 12 Pin# and<br>Name | nd Pin Alternate Functionality / Description |                                                           |                                                             |                               |                           |  |  |  |

|-------|---------------------|----------------------------------------------|-----------------------------------------------------------|-------------------------------------------------------------|-------------------------------|---------------------------|--|--|--|

| Pin # | Pin Name            | Analog                                       | EBI                                                       | Timers                                                      | Communication                 | Other                     |  |  |  |

| K5    | PA11                |                                              |                                                           |                                                             |                               |                           |  |  |  |

| K6    | RESETn              |                                              | active low.To apply an electric the internal pull-up ensu | xternal reset source to this<br>ure that reset is released. | s pin, it is required to only | drive this pin low during |  |  |  |

| K7    | AVSS_1              | Analog grou                                  | ind 1.                                                    |                                                             |                               |                           |  |  |  |

| K8    | AVDD_2              | Analog pow                                   | er supply 2.                                              |                                                             |                               |                           |  |  |  |

| K9    | AVDD_1              | Analog pow                                   | er supply 1.                                              |                                                             |                               |                           |  |  |  |

| K10   | AVSS_0              | Analog grou                                  | ind 0.                                                    |                                                             |                               |                           |  |  |  |

| K11   | PD1                 | ADC0_CH<br>1                                 |                                                           | TIM0_CC0 #3<br>PCNT2_S1IN #0                                | US1_RX #1                     |                           |  |  |  |

| L1    | PB8                 | LFXTAL_N                                     |                                                           |                                                             | US1_CS #0                     |                           |  |  |  |

| L2    | PC5                 | ACMP0_C<br>H5                                |                                                           | LETIM0_OUT1 #3<br>PCNT1_S1IN #0                             | US2_CS #0                     |                           |  |  |  |

| L3    | PA14                |                                              |                                                           | TIM2_CC2 #1                                                 |                               |                           |  |  |  |

| L4    | IOVDD_1             | Digital IO po                                | ower supply 1.                                            |                                                             |                               |                           |  |  |  |

| L5    | PB11                | DAC0_OU<br>T0                                |                                                           | LETIM0_OUT0 #1                                              |                               |                           |  |  |  |

| L6    | PB12                | DAC0_OU<br>T1                                |                                                           | LETIM0_OUT1 #1                                              |                               |                           |  |  |  |

| L7    | AVSS_2              | Analog grou                                  | Analog ground 2.                                          |                                                             |                               |                           |  |  |  |

| L8    | PB13                | HFXTAL_<br>P                                 |                                                           |                                                             | LEU0_TX #1                    |                           |  |  |  |

| L9    | PB14                | HFXTAL_<br>N                                 |                                                           |                                                             | LEU0_RX #1                    |                           |  |  |  |

| L10   | AVDD_0              | Analog pow                                   | er supply 0.                                              |                                                             |                               |                           |  |  |  |

| L11   | PD0                 | ADC0_CH<br>0                                 |                                                           | PCNT2_S0IN #0                                               | US1_TX #1                     |                           |  |  |  |

| Alternate     |         |      |      |      | LOCATION                                                                              |

|---------------|---------|------|------|------|---------------------------------------------------------------------------------------|

| Functionality | 0       | 1    | 2    | 3    | Description                                                                           |

| TIM2_CC0      | PA8     | PA12 | PC8  |      | Timer 2 Capture Compare input / output channel 0.                                     |

| TIM2_CC1      | PA9     | PA13 | PC9  |      | Timer 2 Capture Compare input / output channel 1.                                     |

| TIM2_CC2      | PA10    | PA14 | PC10 |      | Timer 2 Capture Compare input / output channel 2.                                     |

| U0_RX         | PF7     | PE1  | PA4  | PC15 | UART0 Receive input.                                                                  |

| U0_TX         | PF6     | PE0  | PA3  | PC14 | UART0 Transmit output. Also used as receive input in half duplex communication.       |

| US0_CLK       | PE12    | PE5  | PC9  |      | USART0 clock input / output.                                                          |

| US0_CS        | PE13    | PE4  | PC8  |      | USART0 chip select input / output.                                                    |

|               |         |      |      |      | USART0 Asynchronous Receive.                                                          |

| US0_RX        | PE11    | PE6  | PC10 |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               |         | DET  | 5044 |      | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US0_TX        | PE10    | PE7  | PC11 |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US1_CLK       | PB7     | PD2  |      |      | USART1 clock input / output.                                                          |

| US1_CS        | PB8     | PD3  |      |      | USART1 chip select input / output.                                                    |

|               |         |      |      |      | USART1 Asynchronous Receive.                                                          |

| US1_RX        | PC1     | PD1  |      |      | USART1 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               | DOG     |      |      |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US1_TX        | PC0     | PD0  |      |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US2_CLK       | PC4     | PB5  |      |      | USART2 clock input / output.                                                          |

| US2_CS        | PC5     | PB6  |      |      | USART2 chip select input / output.                                                    |

|               |         |      |      |      | USART2 Asynchronous Receive.                                                          |

| US2_RX        | PC3     | PB4  |      |      | USART2 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               | DC2     |      |      |      | USART2 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US2_TX        | PC2 PB3 |      |      |      | USART2 Synchronous mode Master Output / Slave Input (MOSI).                           |

| Alternate     |      |      |     |      | LOCATION                                                                              |

|---------------|------|------|-----|------|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2   | 3    | Description                                                                           |

| PCNT1_S0IN    | PC4  | PB3  |     |      | Pulse Counter PCNT1 input number 0.                                                   |

| PCNT1_S1IN    | PC5  | PB4  |     |      | Pulse Counter PCNT1 input number 1.                                                   |

| PCNT2_S0IN    | PD0  | PE8  |     |      | Pulse Counter PCNT2 input number 0.                                                   |

| PCNT2_S1IN    | PD1  | PE9  |     |      | Pulse Counter PCNT2 input number 1.                                                   |

| TIM0_CC0      | PA0  | PA0  |     | PD1  | Timer 0 Capture Compare input / output channel 0.                                     |

| TIM0_CC1      | PA1  | PA1  |     | PD2  | Timer 0 Capture Compare input / output channel 1.                                     |

| TIM0_CC2      | PA2  | PA2  |     | PD3  | Timer 0 Capture Compare input / output channel 2.                                     |

| TIM0_CDTI0    | PA3  | PC13 | PF3 | PC13 | Timer 0 Complimentary Deat Time Insertion channel 0.                                  |

| TIM0_CDTI1    | PA4  | PC14 | PF4 | PC14 | Timer 0 Complimentary Deat Time Insertion channel 1.                                  |

| TIM0_CDTI2    | PA5  | PC15 | PF5 | PC15 | Timer 0 Complimentary Deat Time Insertion channel 2.                                  |

| TIM1_CC0      | PC13 | PE10 |     |      | Timer 1 Capture Compare input / output channel 0.                                     |

| TIM1_CC1      | PC14 | PE11 |     |      | Timer 1 Capture Compare input / output channel 1.                                     |

| TIM1_CC2      | PC15 | PE12 |     |      | Timer 1 Capture Compare input / output channel 2.                                     |

| TIM2_CC0      |      | PA12 |     |      | Timer 2 Capture Compare input / output channel 0.                                     |

| TIM2_CC1      |      | PA13 |     |      | Timer 2 Capture Compare input / output channel 1.                                     |

| TIM2_CC2      |      | PA14 |     |      | Timer 2 Capture Compare input / output channel 2.                                     |

| US0_CLK       | PE12 | PE5  |     |      | USART0 clock input / output.                                                          |

| US0_CS        | PE13 | PE4  |     |      | USART0 chip select input / output.                                                    |

|               |      |      |     |      | USART0 Asynchronous Receive.                                                          |

| US0_RX        | PE11 | PE6  |     |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                          |

| US0_TX        | PE10 | PE7  |     |      | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| 030_1X        | FEIU |      |     |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US1_CLK       | PB7  | PD2  |     |      | USART1 clock input / output.                                                          |

| US1_CS        | PB8  | PD3  |     |      | USART1 chip select input / output.                                                    |

|               |      |      |     |      | USART1 Asynchronous Receive.                                                          |

| US1_RX        |      | PD1  |     |      | USART1 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               |      | DDO  |     |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US1_TX        |      | PD0  |     |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US2_CLK       | PC4  | PB5  |     |      | USART2 clock input / output.                                                          |

| US2_CS        | PC5  | PB6  |     |      | USART2 chip select input / output.                                                    |

|               |      |      |     |      | USART2 Asynchronous Receive.                                                          |

| US2_RX        |      | PB4  |     |      | USART2 Synchronous mode Master Input / Slave Output (MI-SO).                          |

| Functionality0123DescriptionLCD_SEG9PE13LCD segment line 9. Segments 8, 9, 10 and 11 are<br>by SEGEN2.LCD segment line 10. Segments 8, 9, 10 and 11 are<br>led by SEGEN2.LCD_SEG10PE14LCD segment line 11. Segments 8, 9, 10 and 11 are<br>led by SEGEN2.LCD_SEG11PE15LCD segment line 11. Segments 8, 9, 10 and 11 are<br>led by SEGEN3.LCD_SEG13PA0LCD segment line 13. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG14PA1LCD segment line 14. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG15PA2LCD segment line 14. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG16PA3LCD segment line 16. Segments 12, 13, 14 and 15<br>trolled by SEGEN4.LCD_SEG17PA4LCD segment line 16. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG20PB3LCD segment line 18. Segments 16, 17, 18 and 19<br>trolled by SEGEN5.LCD_SEG21PB4LCD segment line 21. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6LCD segment line 21. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6LCD segment line 21. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LETIM0_0UT0PD6PB11PF0PC4Low Energy Timer LETIM0, output channel 0.LETIM0_OUT1PD7PF1PC5LCW Rerey Timer LETIM0, output Also used as receive in<br>duplex communication.LEU_RXPD5PB14PE14LEUART1 Receive input.LEU_RXPC7LEUART1 Transmit output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| LCD_SEG9PE13by SEGEN2.LCD_SEG10PE14Image: Constraint of the segment line 10. Segments 8, 9, 10 and 11 artified by SEGEN2.LCD_SEG11PE15Image: Constraint of the segment line 11. Segments 8, 9, 10 and 11 artified by SEGEN2.LCD_SEG13PA0Image: Constraint of the segment line 13. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG14PA1Image: Constraint of the segment line 14. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG15PA2Image: Constraint of the segment line 15. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG16PA3Image: Constraint of the segment line 16. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG16PA3Image: Constraint of the segment line 16. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG17PA4Image: Constraint of the segment line 17. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG20PB3Image: Constraint of the segment line 18. Segments 10, 17, 18 and 19<br>trolled by SEGEN5.LCD_SEG21PB4Image: Constraint of the segment line 20. Segment segment 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6Image: Constraint of the segment line 23. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6PB11PF0PC4Low Energy Timer LETIM0, output channel 0.LETIM0_OUT1PD7PF1PC5LCD_SEG24PB14Image: Constraint output. Also used as receive in<br>duplex communication.LEU_TXPD4PB13PE14LEUARTI Tranent output. Also used as receive in<br>duple                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| LCD_SEG10PE14Ied by SEGEN2.LCD_SEG11PE15LCD segment line 11. Segments 8, 9, 10 and 11 ar<br>led by SEGEN3.LCD_SEG13PA0LCD segment line 13. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG14PA1LCD segment line 14. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG15PA2LCD segment line 15. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG16PA3LCD segment line 16. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG17PA4LCD segment line 17. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG18PA5LCD segment line 18. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG20PB3LCD segment line 10. Segment 10 and 10 by SEGEN5.LCD_SEG21PB4LCD segment line 20. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG22PB5LCD segment line 23. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6LCD segment line 23. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LETIM0_OUT0PD6PB11PF1PC5Low Energy Timer LETIM0, output channel 0.LETIM0_OUT1PD7PF1PC5Low Energy Timer LETIM0, output channel 1.LEU0_TXPD4PB13PE14LEUARTO Receive input.LEUARTI Receive input.LEUARTI Receive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | controlled   |

| LCD_SEG11PE15Ied by SEGEN2.LCD_SEG13PA0Image: CD segment line 13. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG14PA1Image: CD segment line 14. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG15PA2Image: CD segment line 15. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG16PA3Image: CD segment line 16. Segments 12, 13, 14 and 15<br>trolled by SEGEN3.LCD_SEG16PA3Image: CD segment line 16. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG17PA4Image: CD segment line 18. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG18PA5Image: CD segment line 18. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG20PB3Image: CD segment line 20. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG21PB4Image: CD segment line 21. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6Image: CD segment line 23. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LETIM0_OUT0PD6PB11PF0PC4Low Energy Timer LETIM0, output channel 0.LETIM0_OUT1PD7PF1PC5Low Energy Timer LETIM0, output channel 1.LEU0_TXPD4PB13PE14LEUARTO Receive input.LEUARTI Receive input.Image: CD segment input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | econtrol-    |

| LCD_SEG13PA0trolled by<br>trolled by<br>SEGEN3.LCD_SEG14PA1LCDLCD segment line 14. Segments 12, 13, 14 and 15<br>trolled by<br>SEGEN3.LCD_SEG15PA2LCD segment line 16. Segments 12, 13, 14 and 15<br>trolled by<br>SEGEN3.LCD_SEG16PA3LCD segment line 16. Segments 16, 17, 18 and 19<br>trolled by<br>SEGEN4.LCD_SEG17PA4LCD segment line 17. Segments 16, 17, 18 and 19<br>trolled by<br>SEGEN4.LCD_SEG18PA5LCD segment line 18. Segments 16, 17, 18 and 19<br>trolled by<br>SEGEN4.LCD_SEG20PB3LCD segment line 20. Segments 20, 21, 22 and 23<br>trolled by<br>SEGEN5.LCD_SEG21PB4LCD segment line 21. Segments 20, 21, 22 and 23<br>trolled by<br>SEGEN5.LCD_SEG22PB5LCD segment line 22. Segments 20, 21, 22 and 23<br>trolled by<br>SEGEN5.LCD_SEG23PB6LCD segment line 23. Segments 20, 21, 22 and 23<br>trolled by<br>SEGEN5.LETIM0_OUT0PD6PB11PF0PC4Low Energy Timer LETIM0, output channel 0.LETIM0_OUT1PD7PF1PC5Lew Energy Timer LETIM0, output channel 1.LEU0_TXPD4PB13PE14LEUARTO Transmit output. Also used as receive in<br>utput.LEU1_RXPC7LEUART1 Receive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | econtrol-    |

| LCD_SEG14PA1Image of the second | are con-     |

| LCD_SEG15PA2Image: Constraint of the section of | are con-     |

| LCD_SEG16PA3rolled by SEGEN4.LCD_SEG17PA4LCD segment line 17. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG18PA5LCD segment line 18. Segments 16, 17, 18 and 19<br>trolled by SEGEN4.LCD_SEG20PB3LCD segment line 20. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG21PB4LCD segment line 21. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG22PB5LCD segment line 22. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LCD_SEG23PB6LCD segment line 23. Segments 20, 21, 22 and 23<br>trolled by SEGEN5.LETIM0_OUT0PD6PB11PF0PC4LETIM0_OUT1PD7PF1PC5Low Energy Timer LETIM0, output channel 0.LETIM0_OUT1PD7PF1PC5Low Energy Timer LETIM0, output channel 1.LEU0_TXPD4PB13PE14LEUART0 Receive input.LEU1_RXPC7LLEUART1 Receive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | are con-     |

| LCD_SEG17PA4Image: Section of the section of th | are con-     |

| LCD_SEG10PA3Image: Section of the section of th | are con-     |

| LCD_SEG20PB3Image: Second constraint of the second constraint  | are con-     |

| LCD_SEG21PB4Image: Section of the section of th | are con-     |

| LCD_SEG22PB5Image: Second Secon | are con-     |

| LCD_SEG23PB0Image: Section of the section of th | are con-     |

| LETIM0_OUT1   PD7   PF1   PC5   Low Energy Timer LETIM0, output channel 1.     LEU0_RX   PD5   PB14   PE15   LEUART0 Receive input.     LEU0_TX   PD4   PB13   PE14   LEUART0 Transmit output. Also used as receive in duplex communication.     LEU1_RX   PC7   LEUART1 Receive input.   LEUART1 Transmit output. Also used as receive in put.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | are con-     |

| LEU0_RX   PD5   PB14   PE15   LEUART0 Receive input.     LEU0_TX   PD4   PB13   PE14   LEUART0 Transmit output. Also used as receive in duplex communication.     LEU1_RX   PC7   LEUART1 Receive input.   LEUART1 Receive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |              |

| LEU0_TX   PD4   PB13   PE14   LEUART0 Transmit output. Also used as receive in duplex communication.     LEU1_RX   PC7   LEUART1 Receive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |              |

| LEU1_RX PC7 PE14 duplex communication.   LEU1_RX PC7 LEUART1 Receive input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | out in half  |

| L ELIADT1 Transmit output. Also used as reasive in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |              |

| LEU1_TX PC6 PA5 LEUART Transmit output. Also used as receive in duplex communication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | out in half  |

| LFXTAL_N PB8 Low Frequency Crystal (typically 32.768 kHz) negative so used as an optional external clock input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ive pin. Al- |

| LFXTAL_P PB7 Low Frequency Crystal (typically 32.768 kHz) posit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ve pin.      |

| PCNT0_S0IN PC13 Pulse Counter PCNT0 input number 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              |