Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 32MHz                                                                    |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 90                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16K × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                             |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 112-LFBGA                                                                |

| Supplier Device Package    | 112-BGA (10x10)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g290f64g-e-bga112 |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

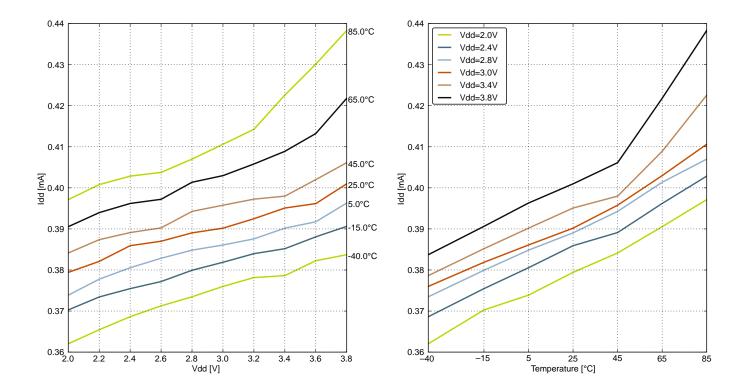

Figure 4.10. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 7 MHz

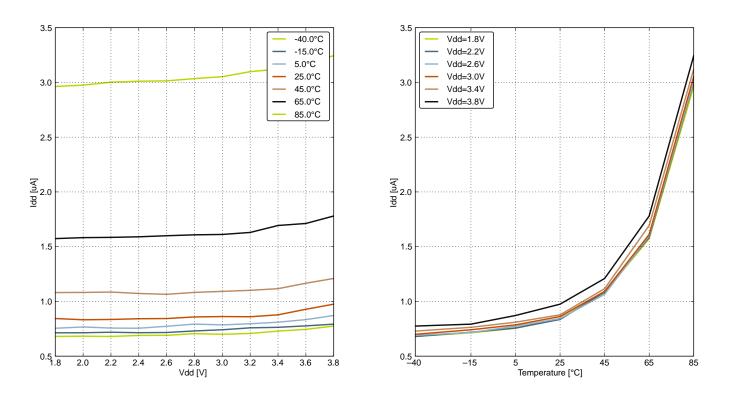

## 4.4.3 EM2 Current Consumption

Figure 4.11. EM2 Current Consumption, RTC prescaled to 1 kHz, 32.768 kHz LFRCO

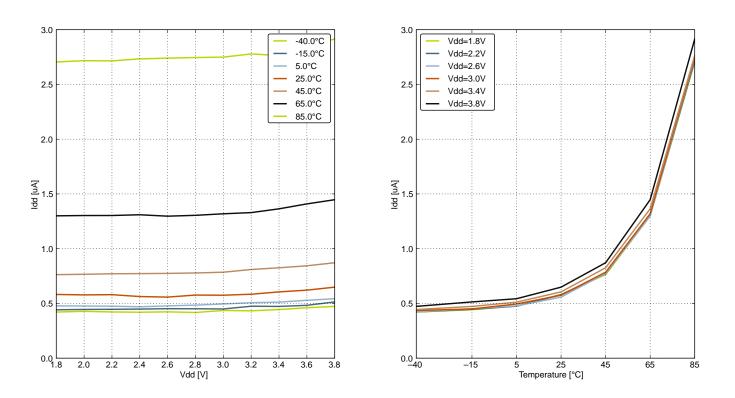

## 4.4.4 EM3 Current Consumption

Figure 4.12. EM3 Current Consumption

# Table 4.10. LFRCO

| Parameter                                                | Symbol              | Test Condition | Min   | Тур    | Max   | Unit |

|----------------------------------------------------------|---------------------|----------------|-------|--------|-------|------|

| Oscillation frequency, $V_{DD}$ = 3.0 V, $T_{AMB}$ =25°C | flfrco              |                | 31.29 | 32.768 | 34.24 | kHz  |

| Startup time not including soft-<br>ware calibration     | t <sub>LFRCO</sub>  |                | —     | 150    | —     | μs   |

| Current consumption                                      | I <sub>LFRCO</sub>  |                | _     | 190    | _     | nA   |

| Temperature coefficient                                  | TC <sub>LFRCO</sub> |                | —     | ±0.02  | —     | %/°C |

| Supply voltage coefficient                               | VC <sub>LFRCO</sub> |                | —     | ±15    | —     | %/V  |

| Frequency step for LSB change in TUNING value            | TUNESTEPLFRCO       |                | —     | 1.5    | —     | %    |

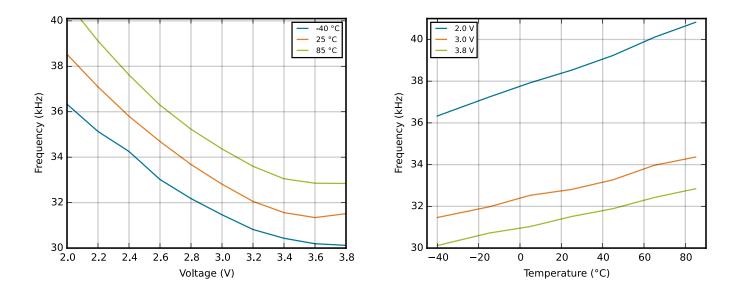

Figure 4.20. Calibrated LFRCO Frequency vs Temperature and Supply Voltage

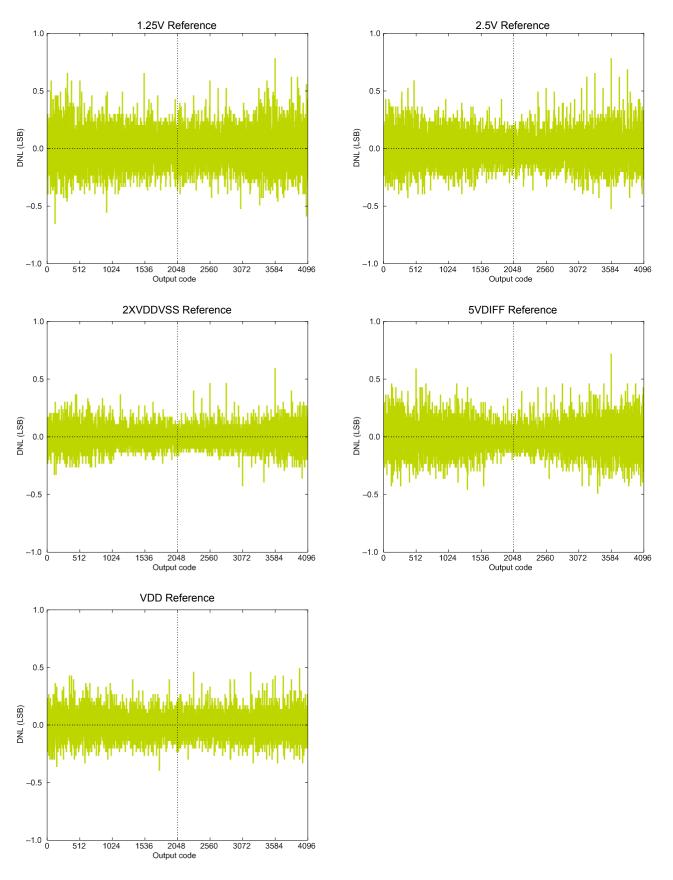

Figure 4.31. ADC Differential Linearity Error vs Code, VDD = 3V, Temp = 25°C

| Alternate     |      |      |     |      | LOCATION                                                                                                      |

|---------------|------|------|-----|------|---------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2   | 3    | Description                                                                                                   |

| LETIM0_OUT1   | PD7  |      | PF1 |      | Low Energy Timer LETIM0, output channel 1.                                                                    |

| LEU0_RX       | PD5  | PB14 |     |      | LEUART0 Receive input.                                                                                        |

| LEU0_TX       | PD4  | PB13 |     |      | LEUART0 Transmit output. Also used as receive input in half duplex communication.                             |

| LFXTAL_N      | PB8  |      |     |      | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional external clock input pin. |

| LFXTAL_P      | PB7  |      |     |      | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                    |

| PCNT0_S0IN    | PC13 |      | PC0 |      | Pulse Counter PCNT0 input number 0.                                                                           |

| PCNT0_S1IN    | PC14 |      | PC1 |      | Pulse Counter PCNT0 input number 1.                                                                           |

| TIM0_CC0      | PA0  | PA0  |     |      | Timer 0 Capture Compare input / output channel 0.                                                             |

| TIM0_CC1      | PA1  | PA1  |     |      | Timer 0 Capture Compare input / output channel 1.                                                             |

| TIM0_CC2      | PA2  | PA2  |     |      | Timer 0 Capture Compare input / output channel 2.                                                             |

| TIM0_CDTI0    |      | PC13 |     | PC13 | Timer 0 Complimentary Deat Time Insertion channel 0.                                                          |

| TIM0_CDTI1    |      | PC14 |     | PC14 | Timer 0 Complimentary Deat Time Insertion channel 1.                                                          |

| TIM0_CDTI2    |      | PC15 |     | PC15 | Timer 0 Complimentary Deat Time Insertion channel 2.                                                          |

| TIM1_CC0      | PC13 | PE10 |     |      | Timer 1 Capture Compare input / output channel 0.                                                             |

| TIM1_CC1      | PC14 | PE11 |     |      | Timer 1 Capture Compare input / output channel 1.                                                             |

| TIM1_CC2      | PC15 | PE12 |     |      | Timer 1 Capture Compare input / output channel 2.                                                             |

| US0_CLK       | PE12 |      |     |      | USART0 clock input / output.                                                                                  |

| US0_CS        | PE13 |      |     |      | USART0 chip select input / output.                                                                            |

|               |      |      |     |      | USART0 Asynchronous Receive.                                                                                  |

| US0_RX        | PE11 |      |     |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                                                  |

|               | 0540 |      |     |      | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication.                         |

| US0_TX        | PE10 |      |     |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                                                   |

| US1_CLK       | PB7  |      |     |      | USART1 clock input / output.                                                                                  |

| US1_CS        | PB8  |      |     |      | USART1 chip select input / output.                                                                            |

|               |      |      |     |      | USART1 Asynchronous Receive.                                                                                  |

| US1_RX        | PC1  |      |     |      | USART1 Synchronous mode Master Input / Slave Output (MI-SO).                                                  |

|               | DC0  |      |     |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication.                         |

| US1_TX        | PC0  |      |     |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                                                   |

# 5.1.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G200 and EFM32G210 is shown in the following table. Each GPIO port is organized as 16bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | _         | _         | _         | _         | _         | _         | _     | _     | _     | —     | _     | _     | _     | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | _         | PB11      | _         | _     | PB8   | PB7   | —     | _     | _     | _     | _     | _     | _     |

| Port C | PC15      | PC14      | PC13      | _         | —         | _         | —     | —     | —     | —     | —     | —     |       | _     | PC1   | PC0   |

| Port D | _         | _         | _         | _         | _         | _         | _     | _     | PD7   | PD6   | PD5   | PD4   |       | _     | —     | _     |

| Port E | _         | _         | PE13      | PE12      | PE11      | PE10      | _     | _     |       | _     | _     |       | _     | _     |       | _     |

| Port F | _         | _         |           |           | _         |           | _     | _     | _     | —     | —     | _     |       | PF2   | PF1   | PF0   |

# Table 5.3. GPIO Pinout

## 5.2 EFM32G222 (TQFP48)

## 5.2.1 Pinout

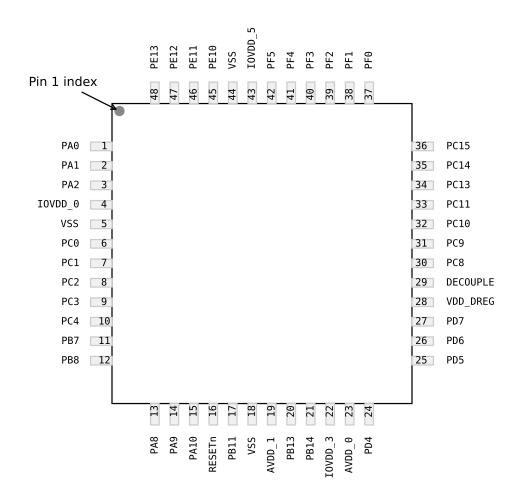

The EFM32G222 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.2. EFM32G222 Pinout (top view, not to scale)

#### Table 5.4. Device Pinout

|       | 48 Pin# and<br>Name |                 | Pin Alternate Functionality / Description |             |             |  |  |  |  |  |  |

|-------|---------------------|-----------------|-------------------------------------------|-------------|-------------|--|--|--|--|--|--|

| Pin # | Pin Name            | Analog          | Timers                                    | Other       |             |  |  |  |  |  |  |

| 1     | PA0                 |                 | TIM0_CC0 #0/1                             | I2C0_SDA #0 |             |  |  |  |  |  |  |

| 2     | PA1                 |                 | TIM0_CC1 #0/1                             | CMU_CLK1 #0 |             |  |  |  |  |  |  |

| 3     | PA2                 |                 | TIM0_CC2 #0/1                             |             | CMU_CLK0 #0 |  |  |  |  |  |  |

| 4     | IOVDD_0             | Digital IO powe | Digital IO power supply 0.                |             |             |  |  |  |  |  |  |

| 5     | VSS                 | Ground.         | Ground.                                   |             |             |  |  |  |  |  |  |

# 5.5.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G280 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | PA15      | PA14      | PA13      | PA12      | PA11      | PA10      | PA9   | PA8   | PA7   | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | PB12      | PB11      | PB10      | PB9   | PB8   | PB7   | PB6   | PB5   | PB4   | PB3   | PB2   | PB1   | PB0   |

| Port C | PC15      | PC14      | PC13      | PC12      | PC11      | PC10      | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | _         | _         | _         | PD12      | PD11      | PD10      | PD9   | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | PE7   | PE6   | PE5   | PE4   | PE3   | PE2   | PE1   | PE0   |

| Port F | _         |           |           |           |           |           | PF9   | PF8   | PF7   | PF6   | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

## Table 5.15. GPIO Pinout

|       | l2 Pin# and<br>Name |               | Ρ             | in Alternate Functionalit       | y / Description           |             |

|-------|---------------------|---------------|---------------|---------------------------------|---------------------------|-------------|

| Pin # | Pin Name            | Analog        | EBI           | Timers                          | Communication             | Other       |

| G10   | PC6                 | ACMP0_C<br>H6 |               |                                 | LEU1_TX #0<br>I2C0_SDA #2 |             |

| G11   | PC7                 | ACMP0_C<br>H7 |               |                                 | LEU1_RX #0<br>I2C0_SCL #2 |             |

| H1    | PC0                 | ACMP0_C<br>H0 |               | PCNT0_S0IN #2                   | US1_TX #0                 |             |

| H2    | PC2                 | ACMP0_C<br>H2 |               |                                 | US2_TX #0                 |             |

| H3    | PD14                |               |               |                                 | I2C0_SDA #3               |             |

| H4    | PA7                 |               |               |                                 |                           |             |

| H5    | PA8                 |               |               | TIM2_CC0 #0                     |                           |             |

| H6    | VSS                 | Ground.       |               |                                 |                           |             |

| H7    | IOVDD_3             | Digital IO po | wer supply 3. |                                 |                           |             |

| H8    | PD8                 |               |               |                                 |                           | CMU_CLK1 #1 |

| H9    | PD5                 | ADC0_CH<br>5  |               |                                 | LEU0_RX #0                |             |

| H10   | PD6                 | ADC0_CH<br>6  |               | LETIM0_OUT0 #0                  | I2C0_SDA #1               |             |

| H11   | PD7                 | ADC0_CH<br>7  |               | LETIM0_OUT1 #0                  | I2C0_SCL #1               |             |

| J1    | PC1                 | ACMP0_C<br>H1 |               | PCNT0_S1IN #2                   | US1_RX #0                 |             |

| J2    | PC3                 | ACMP0_C<br>H3 |               |                                 | US2_RX #0                 |             |

| J3    | PD15                |               |               |                                 | I2C0_SCL #3               |             |

| J4    | PA12                |               |               | TIM2_CC0 #1                     |                           |             |

| J5    | PA9                 |               |               | TIM2_CC1 #0                     |                           |             |

| J6    | PA10                |               |               | TIM2_CC2 #0                     |                           |             |

| J7    | PB9                 |               |               |                                 |                           |             |

| J8    | PB10                |               |               |                                 |                           |             |

| J9    | PD2                 | ADC0_CH<br>2  |               | TIM0_CC1 #3                     | US1_CLK #1                |             |

| J10   | PD3                 | ADC0_CH<br>3  |               | TIM0_CC2 #3                     | US1_CS #1                 |             |

| J11   | PD4                 | ADC0_CH<br>4  |               |                                 | LEU0_TX #0                |             |

| K1    | PB7                 | LFXTAL_P      |               |                                 | US1_CLK #0                |             |

| К2    | PC4                 | ACMP0_C<br>H4 |               | LETIM0_OUT0 #3<br>PCNT1_S0IN #0 | US2_CLK #0                |             |

| K3    | PA13                |               |               | TIM2_CC1 #1                     |                           |             |

| K4    | VSS                 | Ground.       |               |                                 |                           |             |

| Alternate     |      |      |     |      | LOCATION                                                                              |

|---------------|------|------|-----|------|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2   | 3    | Description                                                                           |

| PCNT1_S0IN    | PC4  | PB3  |     |      | Pulse Counter PCNT1 input number 0.                                                   |

| PCNT1_S1IN    | PC5  | PB4  |     |      | Pulse Counter PCNT1 input number 1.                                                   |

| PCNT2_S0IN    | PD0  | PE8  |     |      | Pulse Counter PCNT2 input number 0.                                                   |

| PCNT2_S1IN    | PD1  | PE9  |     |      | Pulse Counter PCNT2 input number 1.                                                   |

| TIM0_CC0      | PA0  | PA0  |     | PD1  | Timer 0 Capture Compare input / output channel 0.                                     |

| TIM0_CC1      | PA1  | PA1  |     | PD2  | Timer 0 Capture Compare input / output channel 1.                                     |

| TIM0_CC2      | PA2  | PA2  |     | PD3  | Timer 0 Capture Compare input / output channel 2.                                     |

| TIM0_CDTI0    | PA3  | PC13 | PF3 | PC13 | Timer 0 Complimentary Deat Time Insertion channel 0.                                  |

| TIM0_CDTI1    | PA4  | PC14 | PF4 | PC14 | Timer 0 Complimentary Deat Time Insertion channel 1.                                  |

| TIM0_CDTI2    | PA5  | PC15 | PF5 | PC15 | Timer 0 Complimentary Deat Time Insertion channel 2.                                  |

| TIM1_CC0      | PC13 | PE10 |     |      | Timer 1 Capture Compare input / output channel 0.                                     |

| TIM1_CC1      | PC14 | PE11 |     |      | Timer 1 Capture Compare input / output channel 1.                                     |

| TIM1_CC2      | PC15 | PE12 |     |      | Timer 1 Capture Compare input / output channel 2.                                     |

| TIM2_CC0      |      | PA12 |     |      | Timer 2 Capture Compare input / output channel 0.                                     |

| TIM2_CC1      |      | PA13 |     |      | Timer 2 Capture Compare input / output channel 1.                                     |

| TIM2_CC2      |      | PA14 |     |      | Timer 2 Capture Compare input / output channel 2.                                     |

| US0_CLK       | PE12 | PE5  |     |      | USART0 clock input / output.                                                          |

| US0_CS        | PE13 | PE4  |     |      | USART0 chip select input / output.                                                    |

|               |      |      |     |      | USART0 Asynchronous Receive.                                                          |

| US0_RX        | PE11 | PE6  |     |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                          |

| US0_TX        | PE10 | PE7  |     |      | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| 030_1X        | FEIU |      |     |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US1_CLK       | PB7  | PD2  |     |      | USART1 clock input / output.                                                          |

| US1_CS        | PB8  | PD3  |     |      | USART1 chip select input / output.                                                    |

|               |      |      |     |      | USART1 Asynchronous Receive.                                                          |

| US1_RX        |      | PD1  |     |      | USART1 Synchronous mode Master Input / Slave Output (MI-SO).                          |

|               |      | DDO  |     |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication. |

| US1_TX        |      | PD0  |     |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                           |

| US2_CLK       | PC4  | PB5  |     |      | USART2 clock input / output.                                                          |

| US2_CS        | PC5  | PB6  |     |      | USART2 chip select input / output.                                                    |

|               |      |      |     |      | USART2 Asynchronous Receive.                                                          |

| US2_RX        |      | PB4  |     |      | USART2 Synchronous mode Master Input / Slave Output (MI-SO).                          |

| Alternate     | ternate LOCATION |     |   |   |                                                                                                                                                            |  |  |  |  |  |

|---------------|------------------|-----|---|---|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Functionality | 0                | 1   | 2 | 3 | Description                                                                                                                                                |  |  |  |  |  |

| US2_TX        |                  | PB3 |   |   | USART2 Asynchronous Transmit.Also used as receive input<br>in half duplex communication.<br>USART2 Synchronous mode Master Output / Slave Input<br>(MOSI). |  |  |  |  |  |

# 5.7.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G840 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

| Table 5.21. | GPIO Pinout |  |

|-------------|-------------|--|

|             |             |  |

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | PA15      | PA14      | PA13      | PA12      | _         | _         | —     | _     | —     | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | PB12      | PB11      | —         |       | PB8   | PB7   | PB6   | PB5   | PB4   | PB3   | _     | _     | _     |

| Port C | PC15      | PC14      | PC13      | PC12      | _         | —         | _     | _     | PC7   | PC6   | PC5   | PC4   | _     | _     | _     | _     |

| Port D | _         |           | _         | _         | _         | _         |       | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | PE7   | PE6   | PE5   | PE4   |       | _     | _     | _     |

| Port F |           | _         | _         | _         | _         | _         | _     | _     | _     | _     | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

## 5.8 EFM32G842 (TQFP64)

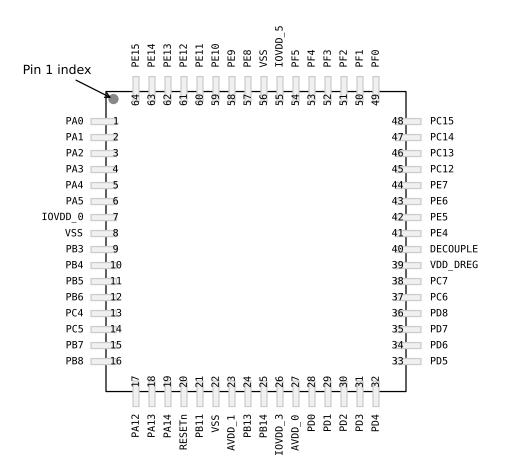

#### 5.8.1 Pinout

The EFM32G842 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.8. EFM32G842 Pinout (top view, not to scale)

#### Table 5.22. Device Pinout

|       | 64 Pin# and<br>Name |           | Pin Alternate Functionality / Description |               |             |  |  |  |  |  |

|-------|---------------------|-----------|-------------------------------------------|---------------|-------------|--|--|--|--|--|

| Pin # | Pin Name            | Analog    | Timers                                    | Communication | Other       |  |  |  |  |  |

| 1     | PA0                 | LCD_SEG13 | TIM0_CC0 #0/1                             | I2C0_SDA #0   |             |  |  |  |  |  |

| 2     | PA1                 | LCD_SEG14 | TIM0_CC1 #0/1                             | I2C0_SCL #0   | CMU_CLK1 #0 |  |  |  |  |  |

| 3     | PA2                 | LCD_SEG15 | TIM0_CC2 #0/1                             |               | CMU_CLK0 #0 |  |  |  |  |  |

| 4     | PA3                 | LCD_SEG16 | TIM0_CDTI0 #0                             |               |             |  |  |  |  |  |

| 5     | PA4                 | LCD_SEG17 | TIM0_CDTI1 #0                             |               |             |  |  |  |  |  |

| TQFP64 Pin# and<br>Name |          | Pin Alternate Functionality / Description   |                                                                                                                               |                        |                       |  |  |  |  |  |

|-------------------------|----------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|--|--|--|--|--|

| Pin #                   | Pin Name | Analog                                      | Timers                                                                                                                        | Communication          | Other                 |  |  |  |  |  |

| 38                      | PC7      | ACMP0_CH7                                   |                                                                                                                               | LEU1_RX #0 I2C0_SCL #2 |                       |  |  |  |  |  |

| 39                      | VDD_DREG | Power supply for on-chip voltage regulator. |                                                                                                                               |                        |                       |  |  |  |  |  |

| 40                      | DECOUPLE | Decouple outp pin.                          | Decouple output for on-chip voltage regulator. An external capacitance of size C <sub>DECOUPLE</sub> is required at this pin. |                        |                       |  |  |  |  |  |

| 41                      | PE4      | LCD_COM0                                    |                                                                                                                               | US0_CS #1              |                       |  |  |  |  |  |

| 42                      | PE5      | LCD_COM1                                    |                                                                                                                               | US0_CLK #1             |                       |  |  |  |  |  |

| 43                      | PE6      | LCD_COM2                                    |                                                                                                                               | US0_RX #1              |                       |  |  |  |  |  |

| 44                      | PE7      | LCD_COM3                                    |                                                                                                                               | US0_TX #1              |                       |  |  |  |  |  |

| 45                      | PC12     | ACMP1_CH4                                   |                                                                                                                               |                        | CMU_CLK0 #1           |  |  |  |  |  |

| 46                      | PC13     | ACMP1_CH5                                   | TIM0_CDTI0 #1/3 TIM1_CC0<br>#0 PCNT0_S0IN #0                                                                                  |                        |                       |  |  |  |  |  |

| 47                      | PC14     | ACMP1_CH6                                   | TIM0_CDTI1 #1/3 TIM1_CC1<br>#0 PCNT0_S1IN #0                                                                                  |                        |                       |  |  |  |  |  |

| 48                      | PC15     | ACMP1_CH7                                   | TIM0_CDTI2 #1/3 TIM1_CC2<br>#0                                                                                                |                        | DBG_SWO #1            |  |  |  |  |  |

| 49                      | PF0      |                                             | LETIM0_OUT0 #2                                                                                                                |                        | DBG_SWCLK #0/1        |  |  |  |  |  |

| 50                      | PF1      |                                             | LETIM0_OUT1 #2                                                                                                                |                        | DBG_SWDIO #0/1        |  |  |  |  |  |

| 51                      | PF2      | LCD_SEG0                                    |                                                                                                                               |                        | ACMP1_O #0 DBG_SWO #0 |  |  |  |  |  |

| 52                      | PF3      | LCD_SEG1                                    | TIM0_CDTI0 #2                                                                                                                 |                        |                       |  |  |  |  |  |

| 53                      | PF4      | LCD_SEG2                                    | TIM0_CDTI1 #2                                                                                                                 |                        |                       |  |  |  |  |  |

| 54                      | PF5      | LCD_SEG3                                    | TIM0_CDTI2 #2                                                                                                                 |                        |                       |  |  |  |  |  |

| 55                      | IOVDD_5  | Digital IO power supply 5.                  |                                                                                                                               |                        |                       |  |  |  |  |  |

| 56                      | VSS      | Ground.                                     |                                                                                                                               |                        |                       |  |  |  |  |  |

| 57                      | PE8      | LCD_SEG4                                    | PCNT2_S0IN #1                                                                                                                 |                        |                       |  |  |  |  |  |

| 58                      | PE9      | LCD_SEG5                                    | PCNT2_S1IN #1                                                                                                                 |                        |                       |  |  |  |  |  |

| 59                      | PE10     | LCD_SEG6                                    | TIM1_CC0 #1                                                                                                                   | US0_TX #0              | BOOT_TX               |  |  |  |  |  |

| 60                      | PE11     | LCD_SEG7                                    | TIM1_CC1 #1                                                                                                                   | US0_RX #0              | BOOT_RX               |  |  |  |  |  |

| 61                      | PE12     | LCD_SEG8                                    | TIM1_CC2 #1                                                                                                                   | US0_CLK #0             |                       |  |  |  |  |  |

| 62                      | PE13     | LCD_SEG9                                    |                                                                                                                               | US0_CS #0              | ACMP0_O #0            |  |  |  |  |  |

| 63                      | PE14     | LCD_SEG10                                   |                                                                                                                               | LEU0_TX #2             |                       |  |  |  |  |  |

| 64                      | PE15     | LCD_SEG11                                   |                                                                                                                               | LEU0_RX #2             |                       |  |  |  |  |  |

## 5.8.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G842 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | _         | PA14      | PA13      | PA12      | _         | _         | _     | _     | _     | _     | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | _         | PB11      | _         | _     | PB8   | PB7   | PB6   | PB5   | PB4   | PB3   | _     | _     | _     |

| Port C | PC15      | PC14      | PC13      | PC12      | —         | _         | —     | —     | PC7   | PC6   | PC5   | PC4   |       | _     | _     | _     |

| Port D | _         | _         |           |           | _         |           | _     | PD8   | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8   | PE7   | PE6   | PE5   | PE4   | _     | _     | _     | _     |

| Port F | _         |           |           |           |           |           |       |       |       |       | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

## Table 5.24. GPIO Pinout

| LQFP100 Pin#<br>and Name |               |               | Pi                          | n Alternate Functionalit                        | y / Description                      |                             |

|--------------------------|---------------|---------------|-----------------------------|-------------------------------------------------|--------------------------------------|-----------------------------|

| Pin #                    | Pin Name      | Analog        | EBI                         | Timers                                          | Communication                        | Other                       |

| 53                       | PD7           | ADC0_CH<br>7  |                             | LETIM0_OUT1 #0                                  | I2C0_SCL #1                          |                             |

| 54                       | PD8           |               |                             |                                                 |                                      | CMU_CLK1 #1                 |

| 55                       | PC6           | ACMP0_C<br>H6 |                             |                                                 | LEU1_TX #0<br>I2C0_SDA #2            |                             |

| 56                       | PC7           | ACMP0_C<br>H7 |                             |                                                 | LEU1_RX #0<br>I2C0_SCL #2            |                             |

| 57                       | VDD_DRE<br>G  | Power supp    | ly for on-chip voltage reg  | ulator.                                         |                                      |                             |

| 58                       | VSS           | Ground.       |                             |                                                 |                                      |                             |

| 59                       | DECOU-<br>PLE | Decouple or   | utput for on-chip voltage r | egulator. An external capa                      | acitance of size C <sub>DECOUP</sub> | LE is required at this pin. |

| 60                       | PE0           |               |                             | PCNT0_S0IN #1                                   | U0_TX #1                             |                             |

| 61                       | PE1           |               |                             | PCNT0_S1IN #1                                   | U0_RX #1                             |                             |

| 62                       | PE2           |               |                             |                                                 |                                      | ACMP0_O #1                  |

| 63                       | PE3           |               |                             |                                                 |                                      | ACMP1_O #1                  |

| 64                       | PE4           | LCD_COM<br>0  |                             |                                                 | US0_CS #1                            |                             |

| 65                       | PE5           | LCD_COM<br>1  |                             |                                                 | US0_CLK #1                           |                             |

| 66                       | PE6           | LCD_COM<br>2  |                             |                                                 | US0_RX #1                            |                             |

| 67                       | PE7           | LCD_COM<br>3  |                             |                                                 | US0_TX #1                            |                             |

| 68                       | PC8           | ACMP1_C<br>H0 |                             | TIM2_CC0 #2                                     | US0_CS #2                            |                             |

| 69                       | PC9           | ACMP1_C<br>H1 |                             | TIM2_CC1 #2                                     | US0_CLK #2                           |                             |

| 70                       | PC10          | ACMP1_C<br>H2 |                             | TIM2_CC2 #2                                     | US0_RX #2                            |                             |

| 71                       | PC11          | ACMP1_C<br>H3 |                             |                                                 | US0_TX #2                            |                             |

| 72                       | PC12          | ACMP1_C<br>H4 |                             |                                                 |                                      | CMU_CLK0 #1                 |

| 73                       | PC13          | ACMP1_C<br>H5 |                             | TIM0_CDTI0 #1/3<br>TIM1_CC0 #0<br>PCNT0_S0IN #0 |                                      |                             |

| 74                       | PC14          | ACMP1_C<br>H6 |                             | TIM0_CDTI1 #1/3<br>TIM1_CC1 #0<br>PCNT0_S1IN #0 | U0_TX #3                             |                             |

| 75                       | PC15          | ACMP1_C<br>H7 |                             | TIM0_CDTI2 #1/3<br>TIM1_CC2 #0                  | U0_RX #3                             | DBG_SWO #1                  |

| 76                       | PF0           |               |                             | LETIM0_OUT0 #2                                  |                                      | DBG_SWCLK #0/1              |

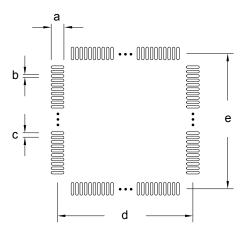

Figure 8.4. TQFP64 PCB Stencil Design

# Table 8.4. TQFP64 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.50      |

| b      | 0.20      |

| с      | 0.50      |

| d      | 11.50     |

| e      | 11.50     |

## Note:

- 1. The drawings are not to scale.

- 2. All dimensions are in millimeters.

- 3. All drawings are subject to change without notice.

- 4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

- 5. Stencil thickness 0.125 mm.

- 6. For detailed pin-positioning, see Pin Definitions.

| Symbol | Dim. (mm) |

|--------|-----------|

| d      | 6.00      |

| e      | 6.00      |

| f      | 4.52      |

| g      | 4.52      |

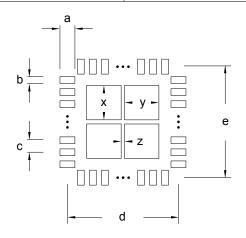

Figure 11.4. QFN32 PCB Stencil Design

# Table 11.4. QFN32 PCB Stencil Design Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 0.70      |

| b      | 0.25      |

| с      | 0.65      |

| d      | 6.00      |

| e      | 6.00      |

| x      | 1.30      |

| у      | 1.30      |

| Z      | 0.50      |

#### Note:

- 1. The drawings are not to scale.

- 2. All dimensions are in millimeters.

- 3. All drawings are subject to change without notice.

- 4. The PCB Land Pattern drawing is in compliance with IPC-7351B.

- 5. Stencil thickness 0.125 mm.

- 6. For detailed pin-positioning, see 5. Pin Definitions.

## 13.2 Revision 2.00

May 10th, 2017

Consolidated all EFM32G data sheets:

- EFM32G200

- EFM32G210

- EFM32G222

- EFM32G230

- EFM32G232

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G842

- EFM32G880

- EFM32G890

New formatting throughout.

Added 1. Feature List.

Updated ordering codes in 2. Ordering Information for Revision E and tape and reel.

Added Figure 2.1 Ordering Code Decoder on page 5.

Separated Memory Map figure into Figure 3.2 System Address Space with Core and Code Space Listing on page 27 and Figure 3.3 System Address Space with Peripheral Listing on page 28 for readability.

Removed footnote for storage temperature range in 4.2 Absolute Maximum Ratings.

#### In 4.6 Power Management:

- Updated EM0 condition for V<sub>BODextthr-</sub> specification.

- Added V<sub>BODextthr-</sub> in EM1 and EM2 specifications.

- Updated EM0 condition for V<sub>BODextthr+</sub> specification.

Updated Flash page erase time and device erase time in 4.7 Flash and added footnotes.

Updated figures in 4.9.3 LFRCO.

Updated figures and HFRCO current consumption typical values in 4.9.4 HFRCO.

## In 4.10 Analog Digital Converter (ADC):

- · Updated test conditions, updated specifications, and added footnote for average active current.

- Added input bias current.

- · Added input offset current.

- · Updated ADC clock frequency.

- Updated SNR, SINAD and SFDR.

- Updated offset voltage.

- Updated missing codes.

- · Added gain error drift and offset error drift.

- Added VREF output voltage, VREF voltage drift, VREF temperature drift, VREF current consumption, and ADC and DAC VREF matching.

## In 4.11 Digital Analog Converter (DAC):

- Updated I<sub>DAC</sub> parameter, test conditions, and footnote.

- Added DAC load current specification to 4.11 Digital Analog Converter (DAC).

- Added VREF output voltage, VREF voltage drift, VREF temperature drift, VREF current consumption, and ADC and DAC VREF matching.

Updated ACMP active current (BIASPROG=0b1111, FULLBIAS=1 and HALFBIAS=0 in ACMPn\_CTRL register) typical value in 4.12 Analog Comparator (ACMP).

Updated VCMP hysteresis typical value in 4.13 Voltage Comparator (VCMP).

## 13.19 Revision 0.82

December 9th, 2009

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

For LQFP100 devices, incorrect pin 0 removed from pinout table.

Updated contact information.

ADC current consumption numbers updated in ADC Electrical Characteristics.

For devices with LCD, updated LCD supply voltage range in LCD Electrical Characteristics.

#### 13.20 Revision 0.81

November 20th, 2009

This revision applies the following devices:

- EFM32G200

- EFM32G210

- EFM32G230

- EFM32G280

- EFM32G290

- EFM32G840

- EFM32G880

- EFM32G890

For devices without a differential DAC, System Summary updated.

Electrical Characteristics updated.

Storage temperature in Electrical Characteristics updated.

Temperature coefficient of band-gap reference in Electrical Characteristics added.

Erase times in Flash Electrical Characteristics updated.

Definitions of DNL and INL added in ADC section.

For devices with and LCD, LCD Electrical Characteristics added.

Current consumption of digital peripherals added in Electrical Characteristics.

For LQFP100 devices, package information in Pinout and Package corrected.

For BGA112 devices, pinout information in Pinout table corrected.

Updated errata section.