Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M3                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 32MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART                      |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                         |

| Number of I/O              | 56                                                                      |

| Program Memory Size        | 32KB (32K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 8K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                            |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                    |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 64-QFN (9x9)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g840f32g-e-qfn64 |

- Supply Voltage Comparator

- · Ultra efficient Power-on Reset and Brown-Out Detector

- · 2-pin Serial Wire Debug Interface

- 1-pin Serial Wire Viewer

- Pre-Programmed USB/UART Bootloader

- Temperature range -40 to 85 °C

- Single power supply 1.98 to 3.8 V

- Packages

- BGA112

- LQFP100

- TQFP64

- TQFP48

- QFN64

- QFN32

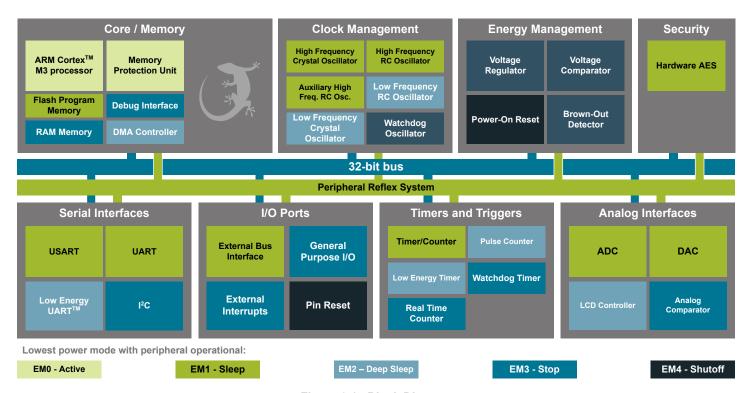

# 3. System Overview

### 3.1 System Introduction

The EFM32 MCUs are the world's most energy friendly microcontrollers. With a unique combination of the powerful 32-bit ARM Cortex-M3, innovative low energy techniques, short wake-up time from energy saving modes, and a wide selection of peripherals, the EFM32G microcontroller is well suited for any battery operated application as well as other systems requiring high performance and low-energy consumption. This section gives a short introduction to each of the modules in general terms and also shows a summary of the configuration for the EFM32G devices. For a complete feature set and in-depth information on the modules, the reader is referred to the EFM32G Reference Manual.

The diagram shows a superset of features available on the family, which vary by OPN. For more information about specific device features, consult Ordering Information.

Figure 3.1. Block Diagram

# 3.1.1 ARM Cortex-M3 Core

The ARM Cortex-M3 includes a 32-bit RISC processor which can achieve as much as 1.25 Dhrystone MIPS/MHz. A Memory Protection Unit with support for up to 8 memory segments is included, as well as a Wake-up Interrupt Controller handling interrupts triggered while the CPU is asleep. The EFM32 implementation of the Cortex-M3 is described in detail in EFM32G Reference Manual.

### 3.1.2 Debug Interface (DBG)

This device includes hardware debug support through a 2-pin serial-wire debug interface. In addition there is also a 1-wire Serial Wire Viewer pin which can be used to output profiling information, data trace and software-generated messages.

### 3.1.3 Memory System Controller (MSC)

The Memory System Controller (MSC) is the program memory unit of the EFM32G microcontroller. The flash memory is readable and writable from both the Cortex-M3 and DMA. The flash memory is divided into two blocks; the main block and the information block. Program code is normally written to the main block. Additionally, the information block is available for special user data and flash lock bits. There is also a read-only page in the information block containing system and device calibration data. Read and write operations are supported in the energy modes EM0 and EM1.

#### 3.1.14 Universal Asynchronous Receiver/Transmitter (UART)

The Universal Asynchronous serial Receiver and Transmitter (UART) is a very flexible serial I/O module. It supports full- and half-duplex asynchronous UART communication.

### 3.1.15 Low Energy Universal Asynchronous Receiver/Transmitter (LEUART)

The unique LEUART<sup>TM</sup>, the Low Energy UART, is a UART that allows two-way UART communication on a strict power budget. Only a 32.768 kHz clock is needed to allow UART communication up to 9600 baud/ s. The LEUART includes all necessary hardware support to make asynchronous serial communication possible with minimum of software intervention and energy consumption.

#### 3.1.16 Timer/Counter (TIMER)

The 16-bit general purpose Timer has 3 compare/capture channels for input capture and compare/Pulse-Width Modulation (PWM) output. TIMER0 also includes a Dead-Time Insertion module suitable for motor control applications.

#### 3.1.17 Real Time Counter (RTC)

The Real Time Counter (RTC) contains a 24-bit counter and is clocked either by a 32.768 kHz crystal oscillator, or a 32.768 kHz RC oscillator. In addition to energy modes EM0 and EM1, the RTC is also available in EM2. This makes it ideal for keeping track of time since the RTC is enabled in EM2 where most of the device is powered down.

### 3.1.18 Low Energy Timer (LETIMER)

The unique LETIMER<sup>TM</sup>, the Low Energy Timer, is a 16-bit timer that is available in energy mode EM2 in addition to EM1 and EM0. Because of this, it can be used for timing and output generation when most of the device is powered down, allowing simple tasks to be performed while the power consumption of the system is kept at an absolute minimum. The LETIMER can be used to output a variety of waveforms with minimal software intervention. It is also connected to the Real Time Counter (RTC), and can be configured to start counting on compare matches from the RTC.

### 3.1.19 Pulse Counter (PCNT)

The Pulse Counter (PCNT) can be used for counting pulses on a single input or to decode quadrature encoded inputs. It runs off either the internal LFACLK or the PCNTn S0IN pin as external clock source. The module may operate in energy mode EM0 - EM3.

#### 3.1.20 Analog Comparator (ACMP)

The Analog Comparator is used to compare the voltage of two analog inputs, with a digital output indicating which input voltage is higher. Inputs can either be one of the selectable internal references or from external pins. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

### 3.1.21 Voltage Comparator (VCMP)

The Voltage Supply Comparator is used to monitor the supply voltage from software. An interrupt can be generated when the supply falls below or rises above a programmable threshold. Response time and thereby also the current consumption can be configured by altering the current supply to the comparator.

### 3.1.22 Analog to Digital Converter (ADC)

The ADC is a Successive Approximation Register (SAR) architecture, with a resolution of up to 12 bits at up to one million samples per second. The integrated input mux can select inputs from 8 external pins and 6 internal signals.

### 3.1.23 Digital to Analog Converter (DAC)

The Digital to Analog Converter (DAC) can convert a digital value to an analog output voltage. The DAC is fully differential rail-to-rail, with 12-bit resolution. It has two single-ended output buffers which can be combined into one differential output. The DAC may be used for a number of different applications such as sensor interfaces or sound output.

#### 3.1.24 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

#### 3.1.25 General Purpose Input/Output (GPIO)

General Purpose Input/Output (GPIO) pins are organized into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

### 3.1.26 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 4x40 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

# 3.2.10 EFM32G880

The features of the EFM32G880 is a subset of the feature set described in the EFM32G Reference Manual. The following table describes device specific implementation of the features.

Table 3.10. EFM32G880 Configuration Summary

| Module    | Module                                   | Module                                                         |

|-----------|------------------------------------------|----------------------------------------------------------------|

| Cortex-M3 | Full configuration                       | NA                                                             |

| DBG       | Full configuration                       | DBG_SWCLK, DBG_SWDIO, DBG_SWO                                  |

| MSC       | Full configuration                       | NA                                                             |

| DMA       | Full configuration                       | NA                                                             |

| RMU       | Full configuration                       | NA                                                             |

| EMU       | Full configuration                       | NA                                                             |

| СМИ       | Full configuration                       | CMU_OUT0, CMU_OUT1                                             |

| WDOG      | Full configuration                       | NA                                                             |

| PRS       | Full configuration                       | NA                                                             |

| ЕВІ       | Full configuration                       | EBI_ARDY, EBI_ALE, EBI_WEn, EBI_REn, EBI_CS[3:0], EBI_AD[15:0] |

| I2C0      | Full configuration                       | I2C0_SDA, I2C0_SCL                                             |

| USART0    | Full configuration with IrDA             | US0_TX, US0_RX. US0_CLK, US0_CS                                |

| USART1    | Full configuration                       | US1_TX, US1_RX, US1_CLK, US1_CS                                |

| USART2    | Full configuration                       | US2_TX, US2_RX, US2_CLK, US2_CS                                |

| UART0     | Full configuration                       | U0_TX, U0_RX                                                   |

| LEUART0   | Full configuration                       | LEU0_TX, LEU0_RX                                               |

| LEUART1   | Full configuration                       | LEU1_TX, LEU1_RX                                               |

| TIMER0    | Full configuration with DTI              | TIM0_CC[2:0], TIM0_CDTI[2:0]                                   |

| TIMER1    | Full configuration                       | TIM1_CC[2:0]                                                   |

| TIMER2    | Full configuration                       | TIM2_CC[2:0]                                                   |

| RTC       | Full configuration                       | NA                                                             |

| LETIMER0  | Full configuration                       | LET0_O[1:0]                                                    |

| PCNT0     | Full configuration, 8-bit count register | PCNT0_S[1:0]                                                   |

| PCNT1     | Full configuration, 8-bit count register | PCNT1_S[1:0]                                                   |

| PCNT2     | Full configuration, 8-bit count register | PCNT2_S[1:0]                                                   |

| ACMP0     | Full configuration                       | ACMP0_CH[7:0], ACMP0_O                                         |

| ACMP1     | Full configuration                       | ACMP1_CH[7:0], ACMP1_O                                         |

| VCMP      | Full configuration                       | NA                                                             |

| ADC0      | Full configuration                       | ADC0_CH[7:0]                                                   |

| DAC0      | Full configuration                       | DAC0_OUT[1:0]                                                  |

| AES       | Full configuration                       | NA                                                             |

| GPIO      | 86 pins                                  | Available pins are shown in Table 4.3 (p. 57)                  |

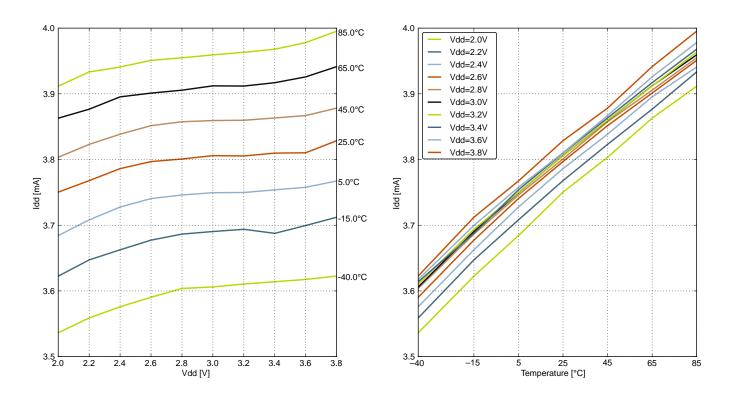

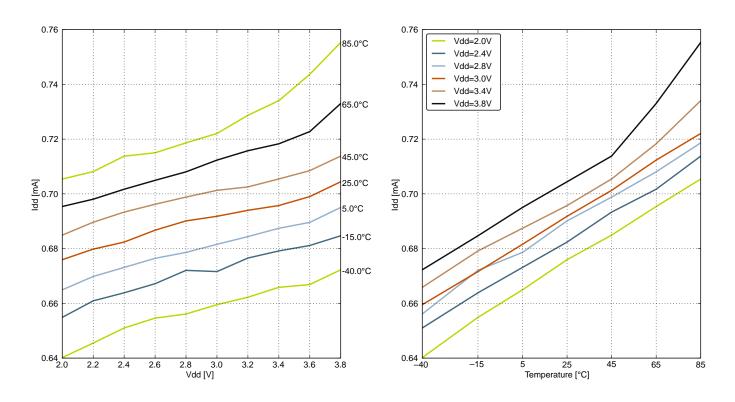

Figure 4.2. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 21 MHz

Figure 4.3. EM0 Current consumption while executing prime number calculation code from flash with HFRCO running at 14 MHz

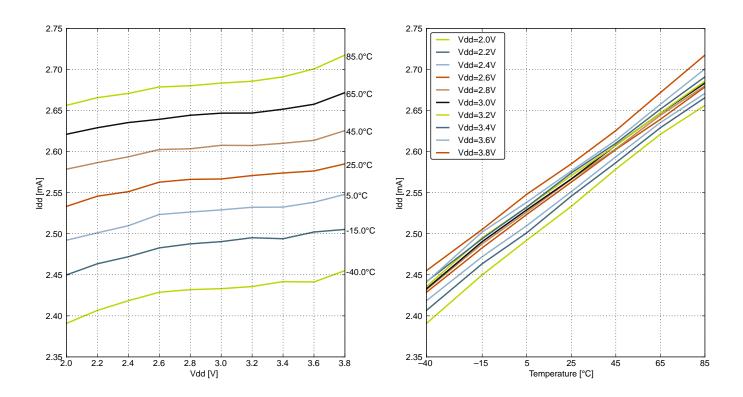

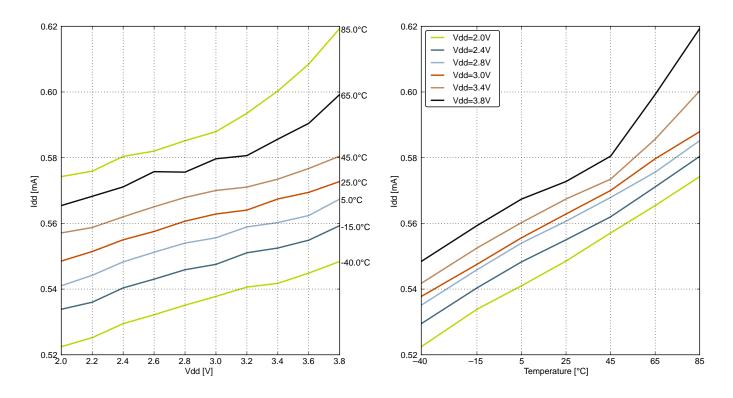

Figure 4.8. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 14 MHz

Figure 4.9. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 11 MHz

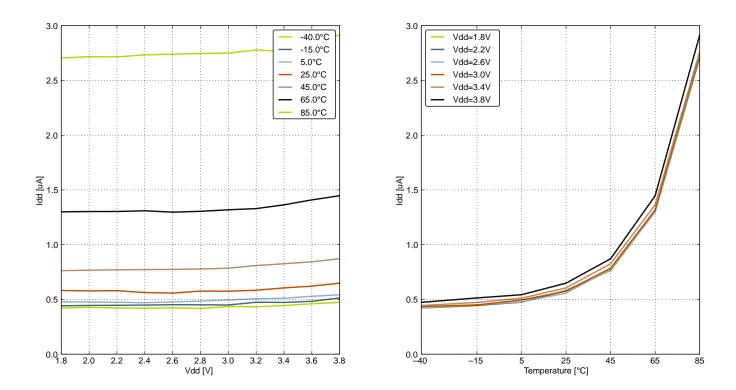

# 4.4.4 EM3 Current Consumption

Figure 4.12. EM3 Current Consumption

### 4.9 Oscillators

#### 4.9.1 LFXO

Table 4.8. LFXO

| Parameter                                             | Symbol              | Test Condition                                                                                               | Min            | Тур    | Max | Unit |

|-------------------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|----------------|--------|-----|------|

| Supported nominal crystal frequency                   | f <sub>LFXO</sub>   |                                                                                                              | _              | 32.768 | _   | kHz  |

| Supported crystal equivalent series resistance (ESR)  | ESR <sub>LFXO</sub> |                                                                                                              | _              | 30     | 120 | kOhm |

| Supported crystal external load range                 | C <sub>LFXOL</sub>  |                                                                                                              | X <sup>1</sup> | _      | 25  | pF   |

| Current consumption for core and buffer after startup | I <sub>LFXO</sub>   | ESR=30 kΩ, C <sub>L</sub> =10 pF, LFXO-<br>BOOST in CMU_CTRL is 1                                            | _              | 190    | _   | nA   |

| Start-up time                                         | t <sub>LFXO</sub>   | ESR=30 kΩ, C <sub>L</sub> =10 pF, 40% -<br>60% duty cycle has been<br>reached, LFXOBOOST in<br>CMU_CTRL is 1 | _              | 400    | _   | ms   |

### Note:

For safe startup of a given crystal, the Configurator tool in Simplicity Studio contains a tool to help users configure both load capacitance and software settings for using the LFXO. For details regarding the crystal configuration, the reader is referred to application note "AN0016 EFM32 Oscillator Design Consideration".

$<sup>1.\,</sup>See\,\,Minimum\,\,Load\,\,Capacitance\,\,(C_{LFXOL})\,\,Requirement\,\,For\,\,Safe\,\,Crystal\,\,Startup\,\,in\,\,Configurator\,\,in\,\,Simplicity\,\,Studio.$

| Parameter                   | Symbol             | Test Condition                                                                                                   | Min | Тур | Max | Unit |

|-----------------------------|--------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Signal-to-Noise Ratio (SNR) | SNR <sub>ADC</sub> | 1 MSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 13 MHz,<br>BIASPROG = 0xF4B    | _   | 59  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B     | _   | 63  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _   | 67  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, differential, internal 1.25 V reference, ADC_CLK = 13 MHz, BIA-SPROG = 0xF4B               | _   | 63  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, differential, internal 2.5 V reference, ADC_CLK = 13 MHz, BIA-SPROG = 0xF4B                | _   | 66  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, differential, 5 V reference, ADC_CLK =13 MHz, BIASPROG = 0xF4B                             | _   | 66  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, differential, V <sub>DD</sub> reference, ADC_CLK= 13 MHz, BIASPROG =0xF4B                  | 63  | 69  | _   | dB   |

|                             |                    | 1 MSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B      | _   | 70  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747 | _   | 62  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747    | _   | 63  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747   | _   | 67  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, differential, internal 1.25 V reference, ADC_CLK = 7 MHz, BIA-SPROG = 0x747              | _   | 63  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, differential, internal 2.5 V reference, ADC_CLK = 7 MHz, BIA-SPROG = 0x747               | _   | 66  | _   | dB   |

|                             |                    | 200 kSamples/s, 12 bit, differential, 5 V reference, ADC_CLK = 7 MHz, BIASPROG = 0x747                           | _   | 66  | _   | dB   |

| Parameter                                    | Symbol               | Test Condition                                                                                                   | Min | Тур | Max | Unit |

|----------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Signal-to-Noise And Distortion Ratio (SINAD) | SINAD <sub>ADC</sub> | 1 MSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 13 MHz,<br>BIASPROG = 0xF4B    | _   | 58  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B     | _   | 62  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _   | 66  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, differential, internal 1.25 V reference, ADC_CLK = 13 MHz, BIA-SPROG = 0xF4B               | _   | 63  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, differential, internal 2.5 V reference, ADC_CLK = 13 MHz, BIA-SPROG = 0xF4B                | _   | 66  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, differential, 5 V reference, ADC_CLK = 13 MHz, BIASPROG = 0xF4B                            | _   | 66  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, differential, V <sub>DD</sub> reference, ADC_CLK = 13 MHz, BIASPROG = 0xF4B                | 62  | 68  | _   | dB   |

|                                              |                      | 1 MSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B      | _   | 68  | _   | dB   |

|                                              |                      | 200 kSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747 | _   | 61  | _   | dB   |

|                                              |                      | 200 kSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747    | _   | 62  | _   | dB   |

|                                              |                      | 200 kSamples/s, 12 bit, single-<br>ended, VDD reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747               | _   | 66  | _   | dB   |

|                                              |                      | 200 kSamples/s, 12 bit, differential, internal 1.25 V reference, ADC_CLK = 7 MHz, BIA-SPROG = 0x747              | _   | 63  | _   | dB   |

|                                              |                      | 200 kSamples/s, 12 bit, differential, internal 2.5 V reference, ADC_CLK = 7 MHz, BIA-SPROG = 0x747               | _   | 66  | _   | dB   |

|                                              |                      | 200 kSamples/s, 12 bit, differential, 5V reference, ADC_CLK= 7 MHz, BIASPROG = 0x747                             | _   | 66  | _   | dB   |

| Parameter                          | Symbol              | Test Condition                                                                                                   | Min | Тур | Max | Unit |

|------------------------------------|---------------------|------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Spurious-Free Dynamic Range (SFDR) | SFDR <sub>ADC</sub> | 1 MSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 13 MHz,<br>BIASPROG = 0xF4B    | _   | 75  | _   | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B     | _   | 76  | _   | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _   | 76  | _   | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, differential, internal 1.25 V reference, ADC_CLK = 13 MHz, BIA-SPROG = 0xF4B               | _   | 78  | _   | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, differential, internal 2.5 V reference, ADC_CLK = 13 MHz, BIA-SPROG = 0xF4B                | _   | 77  |     | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, differential, V <sub>DD</sub> reference, ADC_CLK= 13 MHz, BIASPROG = 0xF4B                 | _   | 76  | _   | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, differential, 2xV <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B      | 68  | 79  | _   | dBc  |

|                                    |                     | 1 MSamples/s, 12 bit, differential, 5 V reference, ADC_CLK =13 MHz, BIASPROG = 0xF4B                             | _   | 79  | _   | dBc  |

|                                    |                     | 200 kSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747 | _   | 75  | _   | dBc  |

|                                    |                     | 200 kSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747    | _   | 75  | _   | dBc  |

|                                    |                     | 200 kSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747   | _   | 76  | _   | dBc  |

|                                    |                     | 200 kSamples/s, 12 bit, differential, internal 1.25 V reference, ADC_CLK = 7 MHz, BIA-SPROG = 0x747              | _   | 79  | _   | dBc  |

|                                    |                     | 200 kSamples/s, 12 bit, differential, internal 2.5 V reference, ADC_CLK = 7 MHz, BIA-SPROG = 0x747               | _   | 79  | _   | dBc  |

|                                    |                     | 200 kSamples/s, 12 bit, differential, 5 V reference, ADC_CLK = 7 MHz, BIASPROG = 0x747                           | _   | 78  | _   | dBc  |

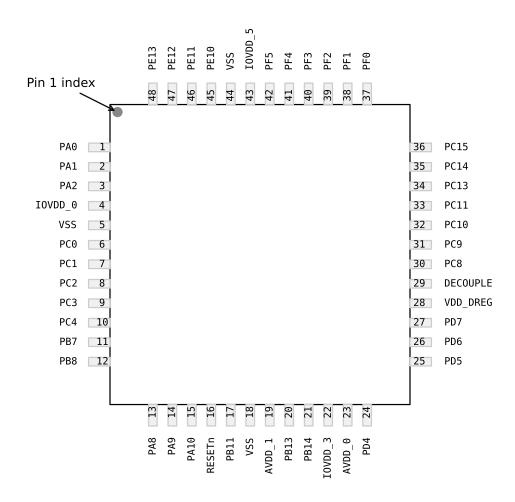

### 5.2 EFM32G222 (TQFP48)

#### 5.2.1 Pinout

The EFM32G222 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

Figure 5.2. EFM32G222 Pinout (top view, not to scale)

Table 5.4. Device Pinout

|      | 48 Pin# and<br>Name |                  | Pin Alternate Functionality / Description |               |             |  |  |  |  |  |  |

|------|---------------------|------------------|-------------------------------------------|---------------|-------------|--|--|--|--|--|--|

| Pin# | Pin Name            | Analog           | Timers                                    | Communication | Other       |  |  |  |  |  |  |

| 1    | PA0                 |                  | TIM0_CC0 #0/1                             | I2C0_SDA #0   |             |  |  |  |  |  |  |

| 2    | PA1                 |                  | TIM0_CC1 #0/1                             | I2C0_SCL #0   | CMU_CLK1 #0 |  |  |  |  |  |  |

| 3    | PA2                 |                  | TIM0_CC2 #0/1                             |               | CMU_CLK0 #0 |  |  |  |  |  |  |

| 4    | IOVDD_0             | Digital IO power | Digital IO power supply 0.                |               |             |  |  |  |  |  |  |

| 5    | VSS                 | Ground.          | Ground.                                   |               |             |  |  |  |  |  |  |

| Alternate     | LOCATION |   |      |   | LOCATION                                                                                                                                           |

|---------------|----------|---|------|---|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0        | 1 | 2    | 3 | Description                                                                                                                                        |

| US0_TX        | PE10     |   | PC11 |   | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication.  USART0 Synchronous mode Master Output / Slave Input (MOSI). |

| US1_CLK       | PB7      |   |      |   | USART1 clock input / output.                                                                                                                       |

| US1_CS        | PB8      |   |      |   | USART1 chip select input / output.                                                                                                                 |

| US1_RX        | PC1      |   |      |   | USART1 Asynchronous Receive.  USART1 Synchronous mode Master Input / Slave Output (MI-SO).                                                         |

| US1_TX        | PC0      |   |      |   | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication.  USART1 Synchronous mode Master Output / Slave Input (MOSI). |

### 5.2.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G222 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

Table 5.6. GPIO Pinout

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8 | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | _         | _         | _         | _         | _         | PA10      | PA9   | PA8   | _     | _     | _     | _     | _     | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | _         | PB11      | _         | _     | PB8   | PB7   | _     | _     | _     | _     | _     | _     | _     |

| Port C | PC15      | PC14      | PC13      | _         | PC11      | PC10      | PC9   | PC8   | _     | _     | _     | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | _         | _         | _         | _         | _         | _         | _     | _     | PD7   | PD6   | PD5   | PD4   | _     | _     | _     | _     |

| Port E | _         | _         | PE13      | PE12      | PE11      | PE10      | _     | _     | _     | _     | _     | _     | _     | _     | _     |       |

| Port F | _         | _         | _         | _         | _         | _         | _     | _     | _     | _     | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

| Alternate     |      |       |      |      | LOCATION                                                                              |                                                                                       |

|---------------|------|-------|------|------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Functionality | 0    | 1     | 2    | 3    | Description                                                                           |                                                                                       |

| TIM2_CC0      | PA8  | PA12  | PC8  |      | Timer 2 Capture Compare input / output channel 0.                                     |                                                                                       |

| TIM2_CC1      | PA9  | PA13  | PC9  |      | Timer 2 Capture Compare input / output channel 1.                                     |                                                                                       |

| TIM2_CC2      | PA10 | PA14  | PC10 |      | Timer 2 Capture Compare input / output channel 2.                                     |                                                                                       |

| U0_RX         | PF7  | PE1   | PA4  | PC15 | UART0 Receive input.                                                                  |                                                                                       |

| U0_TX         | PF6  | PE0   | PA3  | PC14 | UART0 Transmit output. Also used as receive input in half duplex communication.       |                                                                                       |

| US0_CLK       | PE12 | PE5   | PC9  |      | USART0 clock input / output.                                                          |                                                                                       |

| US0_CS        | PE13 | PE4   | PC8  |      | USART0 chip select input / output.                                                    |                                                                                       |

|               |      |       |      |      | USART0 Asynchronous Receive.                                                          |                                                                                       |

| US0_RX        | PE11 | PE6   | PC10 |      | USART0 Synchronous mode Master Input / Slave Output (MISO).                           |                                                                                       |

| US0_TX        | 5-10 | DE 10 | DEZ  | D044 |                                                                                       | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication. |

|               | PE10 | PE7   | PC11 |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                           |                                                                                       |

| US1_CLK       | PB7  | PD2   |      |      | USART1 clock input / output.                                                          |                                                                                       |

| US1_CS        | PB8  | PD3   |      |      | USART1 chip select input / output.                                                    |                                                                                       |

|               |      |       |      |      | USART1 Asynchronous Receive.                                                          |                                                                                       |

| US1_RX        | PC1  | PD1   |      |      | USART1 Synchronous mode Master Input / Slave Output (MISO).                           |                                                                                       |

| LIGA TV       | DOG  | DDG   |      |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication. |                                                                                       |

| US1_TX        | PC0  | PD0   |      |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                           |                                                                                       |

| US2_CLK       | PC4  | PB5   |      |      | USART2 clock input / output.                                                          |                                                                                       |

| US2_CS        | PC5  | PB6   |      |      | USART2 chip select input / output.                                                    |                                                                                       |

|               |      |       |      |      | USART2 Asynchronous Receive.                                                          |                                                                                       |

| US2_RX        | PC3  | PB4   |      |      | USART2 Synchronous mode Master Input / Slave Output (MISO).                           |                                                                                       |

| US2_TX        | DC2  |       |      |      | USART2 Asynchronous Transmit.Also used as receive input in half duplex communication. |                                                                                       |

|               | PC2  | PB3   |      |      | USART2 Synchronous mode Master Output / Slave Input (MOSI).                           |                                                                                       |

| Alternate     |      |     |     |   | LOCATION                                                                                                                                                                                                                                                                                                                            |

|---------------|------|-----|-----|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1   | 2   | 3 | Description                                                                                                                                                                                                                                                                                                                         |

| EBI_ARDY      | PF2  |     |     |   | External Bus Interface (EBI) Hardware Ready Control input.                                                                                                                                                                                                                                                                          |

| EBI_CS0       | PD9  |     |     |   | External Bus Interface (EBI) Chip Select output 0.                                                                                                                                                                                                                                                                                  |

| EBI_CS1       | PD10 |     |     |   | External Bus Interface (EBI) Chip Select output 1.                                                                                                                                                                                                                                                                                  |

| EBI_CS2       | PD11 |     |     |   | External Bus Interface (EBI) Chip Select output 2.                                                                                                                                                                                                                                                                                  |

| EBI_CS3       | PD12 |     |     |   | External Bus Interface (EBI) Chip Select output 3.                                                                                                                                                                                                                                                                                  |

| EBI_REn       | PF5  |     |     |   | External Bus Interface (EBI) Read Enable output.                                                                                                                                                                                                                                                                                    |

| EBI_WEn       | PF4  |     |     |   | External Bus Interface (EBI) Write Enable output.                                                                                                                                                                                                                                                                                   |

| HFXTAL_N      | PB14 |     |     |   | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                                                                                                                                |

| HFXTAL_P      | PB13 |     |     |   | High Frequency Crystal positive pin.                                                                                                                                                                                                                                                                                                |

| I2C0_SCL      | PA1  | PD7 | PC7 |   | I2C0 Serial Clock Line input / output.                                                                                                                                                                                                                                                                                              |

| I2C0_SDA      | PA0  | PD6 | PC6 |   | I2C0 Serial Data input / output.                                                                                                                                                                                                                                                                                                    |

| LCD_BCAP_N    | PA13 |     |     |   | LCD voltage booster (optional), boost capacitor, negative pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                       |

| LCD_BCAP_P    | PA12 |     |     |   | LCD voltage booster (optional), boost capacitor, positive pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                       |

| LCD_BEXT      | PA14 |     |     |   | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.  An external LCD voltage may also be applied to this pin if the booster is not enabled.  If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO. |

| LCD_COM0      | PE4  |     |     |   | LCD driver common line number 0.                                                                                                                                                                                                                                                                                                    |

| LCD_COM1      | PE5  |     |     |   | LCD driver common line number 1.                                                                                                                                                                                                                                                                                                    |

| LCD_COM2      | PE6  |     |     |   | LCD driver common line number 2.                                                                                                                                                                                                                                                                                                    |

| LCD_COM3      | PE7  |     |     |   | LCD driver common line number 3.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG0      | PF2  |     |     |   | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG1      | PF3  |     |     |   | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG2      | PF4  |     |     |   | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG3      | PF5  |     |     |   | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG4      | PE8  |     |     |   | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                |

| LCD_SEG5      | PE9  |     |     |   | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                |

| LCD_SEG6      | PE10 |     |     |   | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                |

| Alternate     |      |      |      |      | LOCATION                                                                                                      |

|---------------|------|------|------|------|---------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2    | 3    | Description                                                                                                   |

| LCD_SEG30     | PD11 |      |      |      | LCD segment line 30. Segments 28, 29, 30 and 31 are controlled by SEGEN7.                                     |

| LCD_SEG31     | PD12 |      |      |      | LCD segment line 31. Segments 28, 29, 30 and 31 are controlled by SEGEN7.                                     |

| LCD_SEG32     | РВ0  |      |      |      | LCD segment line 32. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG33     | PB1  |      |      |      | LCD segment line 33. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG34     | PB2  |      |      |      | LCD segment line 34. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG35     | PA7  |      |      |      | LCD segment line 35. Segments 32, 33, 34 and 35 are controlled by SEGEN8.                                     |

| LCD_SEG36     | PA8  |      |      |      | LCD segment line 36. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                     |

| LCD_SEG37     | PA9  |      |      |      | LCD segment line 37. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                     |

| LCD_SEG38     | PA10 |      |      |      | LCD segment line 38. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                     |

| LCD_SEG39     | PA11 |      |      |      | LCD segment line 39. Segments 36, 37, 38 and 39 are controlled by SEGEN9.                                     |

| LETIMO_OUT0   | PD6  | PB11 | PF0  | PC4  | Low Energy Timer LETIM0, output channel 0.                                                                    |

| LETIM0_OUT1   | PD7  | PB12 | PF1  | PC5  | Low Energy Timer LETIM0, output channel 1.                                                                    |

| LEU0_RX       | PD5  | PB14 | PE15 |      | LEUART0 Receive input.                                                                                        |

| LEU0_TX       | PD4  | PB13 | PE14 |      | LEUART0 Transmit output. Also used as receive input in half duplex communication.                             |

| LEU1_RX       | PC7  | PA6  |      |      | LEUART1 Receive input.                                                                                        |

| LEU1_TX       | PC6  | PA5  |      |      | LEUART1 Transmit output. Also used as receive input in half duplex communication.                             |

| LFXTAL_N      | PB8  |      |      |      | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional external clock input pin. |

| LFXTAL_P      | PB7  |      |      |      | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                    |

| PCNT0_S0IN    | PC13 | PE0  | PC0  |      | Pulse Counter PCNT0 input number 0.                                                                           |

| PCNT0_S1IN    | PC14 | PE1  | PC1  |      | Pulse Counter PCNT0 input number 1.                                                                           |

| PCNT1_S0IN    | PC4  | PB3  |      |      | Pulse Counter PCNT1 input number 0.                                                                           |

| PCNT1_S1IN    | PC5  | PB4  |      |      | Pulse Counter PCNT1 input number 1.                                                                           |

| PCNT2_S0IN    | PD0  | PE8  |      |      | Pulse Counter PCNT2 input number 0.                                                                           |

| PCNT2_S1IN    | PD1  | PE9  |      |      | Pulse Counter PCNT2 input number 1.                                                                           |

| TIM0_CC0      | PA0  | PA0  | PF6  | PD1  | Timer 0 Capture Compare input / output channel 0.                                                             |

| TIM0_CC1      | PA1  | PA1  | PF7  | PD2  | Timer 0 Capture Compare input / output channel 1.                                                             |

| TIM0_CC2      | PA2  | PA2  | PF8  | PD3  | Timer 0 Capture Compare input / output channel 2.                                                             |

| TIM0_CDTI0    | PA3  | PC13 | PF3  | PC13 | Timer 0 Complimentary Deat Time Insertion channel 0.                                                          |

| Alternate     |      |     |     |      | LOCATION                                                                                                                                                                                                                                                                                                                            |

|---------------|------|-----|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1   | 2   | 3    | Description                                                                                                                                                                                                                                                                                                                         |

| EBI_ARDY      | PF2  |     |     |      | External Bus Interface (EBI) Hardware Ready Control input.                                                                                                                                                                                                                                                                          |

| EBI_CS0       | PD9  |     |     |      | External Bus Interface (EBI) Chip Select output 0.                                                                                                                                                                                                                                                                                  |

| EBI_CS1       | PD10 |     |     |      | External Bus Interface (EBI) Chip Select output 1.                                                                                                                                                                                                                                                                                  |

| EBI_CS2       | PD11 |     |     |      | External Bus Interface (EBI) Chip Select output 2.                                                                                                                                                                                                                                                                                  |

| EBI_CS3       | PD12 |     |     |      | External Bus Interface (EBI) Chip Select output 3.                                                                                                                                                                                                                                                                                  |

| EBI_REn       | PF5  |     |     |      | External Bus Interface (EBI) Read Enable output.                                                                                                                                                                                                                                                                                    |

| EBI_WEn       | PF4  |     |     |      | External Bus Interface (EBI) Write Enable output.                                                                                                                                                                                                                                                                                   |

| HFXTAL_N      | PB14 |     |     |      | High Frequency Crystal negative pin. Also used as external optional clock input pin.                                                                                                                                                                                                                                                |

| HFXTAL_P      | PB13 |     |     |      | High Frequency Crystal positive pin.                                                                                                                                                                                                                                                                                                |

| I2C0_SCL      | PA1  | PD7 | PC7 | PD15 | I2C0 Serial Clock Line input / output.                                                                                                                                                                                                                                                                                              |

| I2C0_SDA      | PA0  | PD6 | PC6 | PD14 | I2C0 Serial Data input / output.                                                                                                                                                                                                                                                                                                    |

| LCD_BCAP_N    | PA13 |     |     |      | LCD voltage booster (optional), boost capacitor, negative pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                       |

| LCD_BCAP_P    | PA12 |     |     |      | LCD voltage booster (optional), boost capacitor, positive pin. If using the LCD voltage booster, connect a 22 nF capacitor between LCD_BCAP_N and LCD_BCAP_P.                                                                                                                                                                       |

| LCD_BEXT      | PA14 |     |     |      | LCD voltage booster (optional), boost output. If using the LCD voltage booster, connect a 1 uF capacitor between this pin and VSS.  An external LCD voltage may also be applied to this pin if the booster is not enabled.  If AVDD is used directly as the LCD supply voltage, this pin may be left unconnected or used as a GPIO. |

| LCD_COM0      | PE4  |     |     |      | LCD driver common line number 0.                                                                                                                                                                                                                                                                                                    |

| LCD_COM1      | PE5  |     |     |      | LCD driver common line number 1.                                                                                                                                                                                                                                                                                                    |

| LCD_COM2      | PE6  |     |     |      | LCD driver common line number 2.                                                                                                                                                                                                                                                                                                    |

| LCD_COM3      | PE7  |     |     |      | LCD driver common line number 3.                                                                                                                                                                                                                                                                                                    |

| LCD_SEG0      | PF2  |     |     |      | LCD segment line 0. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG1      | PF3  |     |     |      | LCD segment line 1. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG2      | PF4  |     |     |      | LCD segment line 2. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG3      | PF5  |     |     |      | LCD segment line 3. Segments 0, 1, 2 and 3 are controlled by SEGEN0.                                                                                                                                                                                                                                                                |

| LCD_SEG4      | PE8  |     |     |      | LCD segment line 4. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                |

| LCD_SEG5      | PE9  |     |     |      | LCD segment line 5. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                |

| LCD_SEG6      | PE10 |     |     |      | LCD segment line 6. Segments 4, 5, 6 and 7 are controlled by SEGEN1.                                                                                                                                                                                                                                                                |

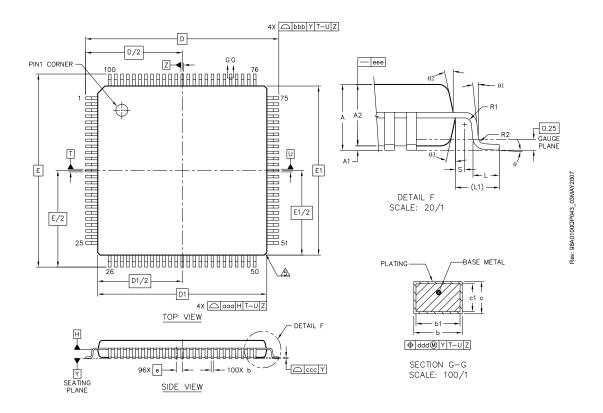

# 7. LQFP100 Package Specifications

### 7.1 LQFP100 Package Dimensions

Figure 7.1. LQFP100

#### Note:

- 1. Datum 'T', 'U' and 'Z' to be determined at datum plane 'H'

- 2. Datum 'D' and 'E' to be determined at seating plane datum 'Y'.

- 3. Dimension 'D1' and 'E1' do not include mold protrusions. Allowable protrusion is 0.25 per side. Dimensions 'D1' and 'E1' do include mold mismatch and are determined at datum plane datum 'H'.

- 4. Dimension 'b' does not include dambar protrusion. Allowable dambar protrusion shall not cause thelead width to exceed the maximum 'b' dimension by more than 0.08 mm. Dambar can not be located on the lower radius or the foot. Minimum space between protrusion and an adjacent lead is 0.07 mm.

- 5. Exact shape of each corner is optional.

Table 7.1. LQFP100 (Dimensions in mm)

|                         | SYMBOL | MIN  | NOM | MAX  |

|-------------------------|--------|------|-----|------|

| total thickness         | A      | _    | _   | 1.6  |

| stand off               | A1     | 0.05 | _   | 0.15 |

| mold thickness          | A2     | 1.35 | 1.4 | 1.45 |

| lead width (plating)    | b      | 0.17 | 0.2 | 0.27 |

| lead width              | b1     | 0.17 | _   | 0.23 |

| L/F thickness (plating) | С      | 0.09 | _   | 0.2  |

| lead thickness          | c1     | 0.09 | _   | 0.16 |

| DIM | MIN       | NOM     | MAX      | DIM | MIN  | NOM  | MAX |

|-----|-----------|---------|----------|-----|------|------|-----|

| b   | 0.17      | 0.22    | 0.27     | S   | 0.20 | _    | _   |

| b1  | 0.17      | 0.20    | 0.23     | θ   | 0°   | 3.5° | 7°  |

| С   | 0.09      | _       | 0.20     | θ1  | 0°   | _    | _   |

| C1  | 0.09      | _       | 0.16     | θ2  | 11°  | 12°  | 13° |

| D   |           | 12.0 BS | C        | θ3  | 11°  | 12°  | 13° |

| D1  |           | 10.0 BS | <b>C</b> |     |      |      |     |

| е   |           | 0.50 BS | <u> </u> |     |      |      |     |

| Е   |           | 12.0 BS | <b>C</b> |     |      |      |     |

| E1  | 10.0 BSC  |         |          |     |      |      |     |

| L   | 0.45 0.60 |         | 0.75     |     |      |      |     |

The TQFP64 Package is 10 by 10 mm in size and has a 0.5 mm pin pitch.

The TQFP64 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx.