Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

# Details

| Product Status             | Discontinued at Digi-Key                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 32MHz                                                                  |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SmartCard, SPI, UART/USART            |

| Peripherals                | Brown-out Detect/Reset, DMA, LCD, POR, PWM, WDT                        |

| Number of I/O              | 90                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 16K × 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.98V ~ 3.8V                                                           |

| Data Converters            | A/D 8x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 112-LFBGA                                                              |

| Supplier Device Package    | 112-BGA (10x10)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/efm32g890f64-bga112t |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.1.24 Advanced Encryption Standard Accelerator (AES)

The AES accelerator performs AES encryption and decryption with 128-bit or 256-bit keys. Encrypting or decrypting one 128-bit data block takes 52 HFCORECLK cycles with 128-bit keys and 75 HFCORECLK cycles with 256-bit keys. The AES module is an AHB slave which enables efficient access to the data and key registers. All write accesses to the AES module must be 32-bit operations, i.e. 8- or 16-bit operations are not supported.

#### 3.1.25 General Purpose Input/Output (GPIO)

General Purpose Input/Output (GPIO) pins are organized into ports with up to 16 pins each. These pins can individually be configured as either an output or input. More advanced configurations like open-drain, filtering and drive strength can also be configured individually for the pins. The GPIO pins can also be overridden by peripheral pin connections, like Timer PWM outputs or USART communication, which can be routed to several locations on the device. The GPIO supports up to 16 asynchronous external pin interrupts, which enables interrupts from any pin on the device. Also, the input value of a pin can be routed through the Peripheral Reflex System to other peripherals.

#### 3.1.26 Liquid Crystal Display Driver (LCD)

The LCD driver is capable of driving a segmented LCD display with up to 4x40 segments. A voltage boost function enables it to provide the LCD display with higher voltage than the supply voltage for the device. In addition, an animation feature can run custom animations on the LCD display without any CPU intervention. The LCD driver can also remain active even in Energy Mode 2 and provides a Frame Counter interrupt that can wake-up the device on a regular basis for updating data.

# EFM32G Data Sheet System Overview

| _                        |                |                            |

|--------------------------|----------------|----------------------------|

| 0x400e0400               | AES            | 0xffffffe                  |

| 0x400e0000               | AES            | 0xe0100000                 |

| 0x400cc400               | PRS            | 0xe00ffff                  |

| 0x400cc000               | FRS            | CM3 Peripherals            |

| 0x400ca400               | RMU            | 0xe0000000                 |

| 0x400ca000               | NH0            | 0xdfffffff                 |

| 0x400c8400               | СМИ            | 0.Aditititi                |

| 0x400c8000               | 6110           | 0×90000000                 |

| 0x400c6400               | EMU            | 0x8fffffff                 |

| 0x400c6000               |                | EBI Region 3               |

| 0x400c4000<br>0x400c2000 | DMA            | 0×8c000000                 |

| 0x400c2000               |                | 0x8bfffff                  |

| 0x400c0400               | MSC            | EBI Region 2               |

| 0x4008a400               |                | 0×88000000                 |

| 0x4008a000               | LCD            | 0x87fffff                  |

| 0x40088400               |                | EBI Region 1               |

| 0x40088000               | WDOG           | 0×84000000                 |

| 0x40086c00               | DONTO          | 0x83ffffff                 |

| 0x40086800               | PCNT2          | EBI Region 0<br>0x80000000 |

| 0x40086400               | PCNT1<br>PCNT0 |                            |

| 0x40086000               | PCNTU          | 0x7fffffff                 |

| 0x40084800               | LEUART1        | 0×44000000                 |

| 0x40084400               | LEUARTO        | 0x43ffffff                 |

| 0x40084000               | LEGATIO        | Peripherals (bit-band)     |

| 0x40082400               | LETIMERO       | 0×42000000                 |

| 0×40082000               |                | 0x41ffffff                 |

| 0x40080400               | RTC            |                            |

| 0×40080000               |                | 0×41000000                 |

| 0x40010c00               | TIMER2         | 0x40ffffff                 |

| 0×40010800<br>0×40010400 | TIMER1         | Peripherals                |

| 0x40010400               | TIMERO         | 0×40000000                 |

| 0x4000e400               |                | 0x3ffffff                  |

| 0x4000e000               | UART0          |                            |

| 0x4000cc00               |                | 0×22200000                 |

| 0x4000c800               | USART2         | 0x221fffff                 |

| 0x4000c400               | USART1         | SRAM (bit-band)            |

| 0x4000c000               | USART0         | 0×22000000                 |

| 0x4000a400               | 2C0            | / 0x21ffffff               |

| 0x4000a000               | 1200           | 0×20004000                 |

| 0x40008400               | EBI            | CDAM (1C Hp) 0x20003fff    |

| 0x40008000               | LDI            | SRAM (16 KB)               |

| 0x40007000               | GPIO           | (data space) 0x20000000    |

| 0x40006000               | GHO            | 0x1fffffff                 |

| 0x40004400               | DACO           |                            |

| 0x40004000               |                |                            |

| 0x40002400               | ADC0           |                            |

| 0x40002000               |                | / Code                     |

| 0×40001800<br>0×40001400 | ACMP1          |                            |

| 0x40001400               | ACMP0          |                            |

| 0x40001000               |                |                            |

| 0x40000400               | VCMP           | / 0×0000000                |

|                          |                |                            |

Figure 3.3. System Address Space with Peripheral Listing

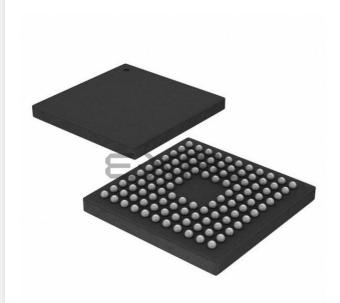

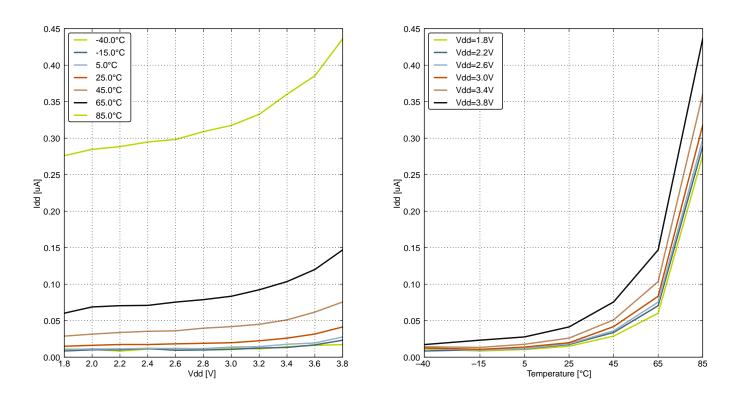

Figure 4.10. EM1 Current consumption with all peripheral clocks disabled and HFRCO running at 7 MHz

# 4.4.5 EM4 Current Consumption

Figure 4.13. EM4 Current Consumption

# 4.5 Transition between Energy Modes

The transition times are measured from the trigger to the first clock edge in the CPU.

# Table 4.4. Energy Modes Transitions

| Parameter                       | Symbol            | Min | Тур | Max | Unit                |

|---------------------------------|-------------------|-----|-----|-----|---------------------|

| Transition time from EM1 to EM0 | t <sub>EM10</sub> | _   | 0   | —   | HFCORECLK<br>cycles |

| Transition time from EM2 to EM0 | t <sub>EM20</sub> | _   | 2   | —   | μs                  |

| Transition time from EM3 to EM0 | t <sub>EM30</sub> | _   | 2   | _   | μs                  |

| Transition time from EM4 to EM0 | t <sub>EM40</sub> | _   | 163 | _   | μs                  |

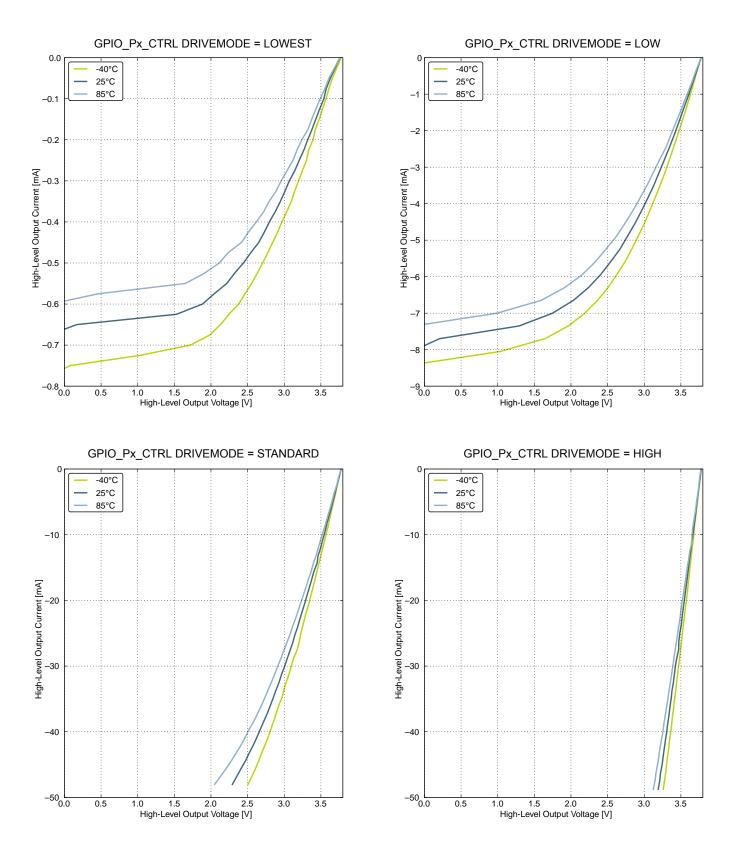

Figure 4.19. Typical High-Level Output Current, 3.8V Supply Voltage

| Parameter                                       | Symbol               | Test Condition                                                                                                   | Min | Тур                                                                                                           | Max | Unit |   |    |

|-------------------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------|-----|------|---|----|

| Signal-to-Noise And Distortion<br>Ratio (SINAD) | SINAD <sub>ADC</sub> | 1 MSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 13 MHz,<br>BIASPROG = 0xF4B    |     | 58                                                                                                            |     | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B     |     | 62                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, single-<br>ended, V <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _   | 66                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, internal 1.25 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B   | _   | 63                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, internal 2.5 V reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B    | _   | 66                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, 5 V reference, ADC_CLK =<br>13 MHz, BIASPROG = 0xF4B                    | —   | 66                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, V <sub>DD</sub> reference, ADC_CLK =<br>13 MHz, BIASPROG = 0xF4B        | 62  | 68                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 1 MSamples/s, 12 bit, differen-<br>tial, 2xV <sub>DD</sub> reference,<br>ADC_CLK = 13 MHz, BIA-<br>SPROG = 0xF4B |     | 68                                                                                                            |     | dB   |   |    |

|                                                 |                      | 200 kSamples/s, 12 bit, single-<br>ended, internal 1.25 V refer-<br>ence, ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747 | _   | 61                                                                                                            | _   | dB   |   |    |

|                                                 |                      |                                                                                                                  |     | 200 kSamples/s, 12 bit, single-<br>ended, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747 |     | 62   | _ | dB |

|                                                 |                      | 200 kSamples/s, 12 bit, single-<br>ended, VDD reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747               | _   | 66                                                                                                            |     | dB   |   |    |

|                                                 |                      | 200 kSamples/s, 12 bit, differen-<br>tial, internal 1.25 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747  | _   | 63                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 200 kSamples/s, 12 bit, differen-<br>tial, internal 2.5 V reference,<br>ADC_CLK = 7 MHz, BIA-<br>SPROG = 0x747   |     | 66                                                                                                            | _   | dB   |   |    |

|                                                 |                      | 200 kSamples/s, 12 bit, differen-<br>tial, 5V reference, ADC_CLK= 7<br>MHz, BIASPROG = 0x747                     | —   | 66                                                                                                            | —   | dB   |   |    |

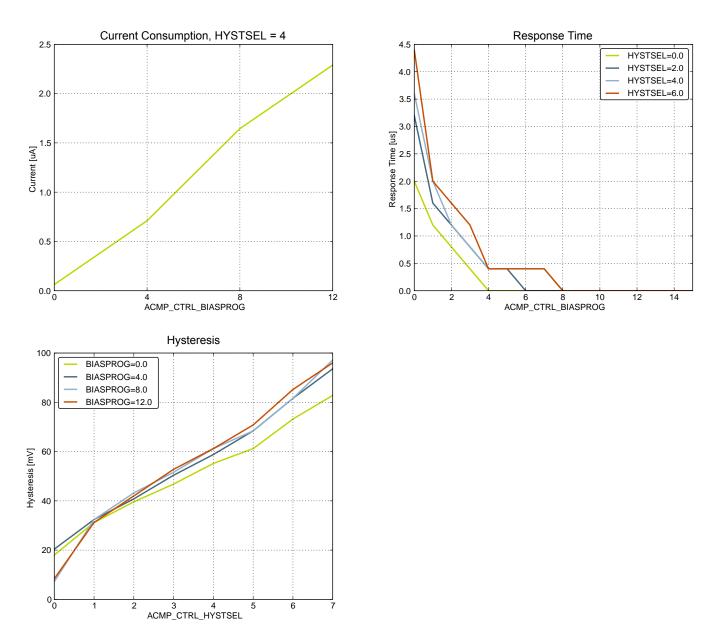

Figure 4.34. ACMP Characteristics, VDD = 3V, Temp = 25°C, FULLBIAS = 0, HALFBIAS = 1

# Table 5.1. Device Pinout

| QFN32 P | in# and Name |                        | Pin Alternate                                                          | Functionality / Description    |                                      |

|---------|--------------|------------------------|------------------------------------------------------------------------|--------------------------------|--------------------------------------|

| Pin #   | Pin Name     | Analog                 | Timers                                                                 | Communication                  | Other                                |

| 0       | VSS          | Ground.                |                                                                        |                                |                                      |

| 1       | PA0          |                        | TIM0_CC0 #0/1                                                          | I2C0_SDA #0                    |                                      |

| 2       | PA1          |                        | TIM0_CC1 #0/1                                                          | I2C0_SCL #0                    | CMU_CLK1 #0                          |

| 3       | PA2          |                        | TIM0_CC2 #0/1                                                          |                                | CMU_CLK0 #0                          |

| 4       | IOVDD_1      | Digital IO powe        | er supply 1.                                                           |                                |                                      |

| 5       | PC0          | ACMP0_CH0              | PCNT0_S0IN #2                                                          | US1_TX #0                      |                                      |

| 6       | PC1          | ACMP0_CH1              | PCNT0_S1IN #2                                                          | US1_RX #0                      |                                      |

| 7       | PB7          | LFXTAL_P               |                                                                        | US1_CLK #0                     |                                      |

| 8       | PB8          | LFXTAL_N               |                                                                        | US1_CS #0                      |                                      |

| 9       | RESETn       |                        | tive low.To apply an external re<br>nd let the internal pull-up ensure |                                | uired to only drive this pin low     |

| 10      | PB11         | DAC0_OUT0              | LETIM0_OUT0 #1                                                         |                                |                                      |

| 11      | AVDD_2       | Analog power           | supply 2.                                                              |                                |                                      |

| 12      | PB13         | HFXTAL_P               |                                                                        | LEU0_TX #1                     |                                      |

| 13      | PB14         | HFXTAL_N               |                                                                        | LEU0_RX #1                     |                                      |

| 14      | IOVDD_3      | Digital IO powe        | er supply 3.                                                           |                                |                                      |

| 15      | AVDD_0       | Analog power           | supply 0.                                                              |                                |                                      |

| 16      | PD4          | ADC0_CH4               |                                                                        | LEU0_TX #0                     |                                      |

| 17      | PD5          | ADC0_CH5               |                                                                        | LEU0_RX #0                     |                                      |

| 18      | PD6          | ADC0_CH6               | LETIM0_OUT0 #0                                                         | I2C0_SDA #1                    |                                      |

| 19      | PD7          | ADC0_CH7               | LETIM0_OUT1 #0                                                         | I2C0_SCL #1                    |                                      |

| 20      | VDD_DREG     | Power supply f         | or on-chip voltage regulator.                                          |                                |                                      |

| 21      | DECOUPLE     | Decouple outpo<br>pin. | ut for on-chip voltage regulator.                                      | An external capacitance of siz | $e C_{DECOUPLE}$ is required at this |

| 22      | PC13         | ACMP1_CH5              | TIM0_CDTI0 #1/3 TIM1_CC0<br>#0 PCNT0_S0IN #0                           |                                |                                      |

| 23      | PC14         | ACMP1_CH6              | TIM0_CDTI1 #1/3 TIM1_CC1<br>#0 PCNT0_S1IN #0                           |                                |                                      |

| 24      | PC15         | ACMP1_CH7              | TIM0_CDTI2 #1/3 TIM1_CC2<br>#0                                         |                                | DBG_SWO #1                           |

| 25      | PF0          |                        | LETIM0_OUT0 #2                                                         |                                | DBG_SWCLK #0/1                       |

| 26      | PF1          |                        | LETIM0_OUT1 #2                                                         |                                | DBG_SWDIO #0/1                       |

| 27      | PF2          |                        |                                                                        |                                | ACMP1_O #0 DBG_SWO #0                |

| 28      | IOVDD_5      | Digital IO powe        | er supply 5.                                                           |                                |                                      |

| 29      | PE10         |                        | TIM1_CC0 #1                                                            | US0_TX #0                      | BOOT_TX                              |

| 30      | PE11         |                        | TIM1_CC1 #1                                                            | US0_RX #0                      | BOOT_RX                              |

| Alternate     |      |      |     |      | LOCATION                                                                                                      |

|---------------|------|------|-----|------|---------------------------------------------------------------------------------------------------------------|

| Functionality | 0    | 1    | 2   | 3    | Description                                                                                                   |

| LETIM0_OUT1   | PD7  |      | PF1 |      | Low Energy Timer LETIM0, output channel 1.                                                                    |

| LEU0_RX       | PD5  | PB14 |     |      | LEUART0 Receive input.                                                                                        |

| LEU0_TX       | PD4  | PB13 |     |      | LEUART0 Transmit output. Also used as receive input in half duplex communication.                             |

| LFXTAL_N      | PB8  |      |     |      | Low Frequency Crystal (typically 32.768 kHz) negative pin. Also used as an optional external clock input pin. |

| LFXTAL_P      | PB7  |      |     |      | Low Frequency Crystal (typically 32.768 kHz) positive pin.                                                    |

| PCNT0_S0IN    | PC13 |      | PC0 |      | Pulse Counter PCNT0 input number 0.                                                                           |

| PCNT0_S1IN    | PC14 |      | PC1 |      | Pulse Counter PCNT0 input number 1.                                                                           |

| TIM0_CC0      | PA0  | PA0  |     |      | Timer 0 Capture Compare input / output channel 0.                                                             |

| TIM0_CC1      | PA1  | PA1  |     |      | Timer 0 Capture Compare input / output channel 1.                                                             |

| TIM0_CC2      | PA2  | PA2  |     |      | Timer 0 Capture Compare input / output channel 2.                                                             |

| TIM0_CDTI0    |      | PC13 |     | PC13 | Timer 0 Complimentary Deat Time Insertion channel 0.                                                          |

| TIM0_CDTI1    |      | PC14 |     | PC14 | Timer 0 Complimentary Deat Time Insertion channel 1.                                                          |

| TIM0_CDTI2    |      | PC15 |     | PC15 | Timer 0 Complimentary Deat Time Insertion channel 2.                                                          |

| TIM1_CC0      | PC13 | PE10 |     |      | Timer 1 Capture Compare input / output channel 0.                                                             |

| TIM1_CC1      | PC14 | PE11 |     |      | Timer 1 Capture Compare input / output channel 1.                                                             |

| TIM1_CC2      | PC15 | PE12 |     |      | Timer 1 Capture Compare input / output channel 2.                                                             |

| US0_CLK       | PE12 |      |     |      | USART0 clock input / output.                                                                                  |

| US0_CS        | PE13 |      |     |      | USART0 chip select input / output.                                                                            |

|               |      |      |     |      | USART0 Asynchronous Receive.                                                                                  |

| US0_RX        | PE11 |      |     |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                                                  |

|               | 0540 |      |     |      | USART0 Asynchronous Transmit.Also used as receive input in half duplex communication.                         |

| US0_TX        | PE10 |      |     |      | USART0 Synchronous mode Master Output / Slave Input (MOSI).                                                   |

| US1_CLK       | PB7  |      |     |      | USART1 clock input / output.                                                                                  |

| US1_CS        | PB8  |      |     |      | USART1 chip select input / output.                                                                            |

|               |      |      |     |      | USART1 Asynchronous Receive.                                                                                  |

| US1_RX        | PC1  |      |     |      | USART1 Synchronous mode Master Input / Slave Output (MI-SO).                                                  |

|               | DC0  |      |     |      | USART1 Asynchronous Transmit.Also used as receive input in half duplex communication.                         |

| US1_TX        | PC0  |      |     |      | USART1 Synchronous mode Master Output / Slave Input (MOSI).                                                   |

# 5.3.3 GPIO Pinout Overview

The specific GPIO pins available in EFM32G230 is shown in the following table. Each GPIO port is organized as 16-bit ports indicated by letters A through F, and the individual pin on this port is indicated by a number from 15 down to 0.

| Port   | Pin<br>15 | Pin<br>14 | Pin<br>13 | Pin<br>12 | Pin<br>11 | Pin<br>10 | Pin 9 | Pin 8    | Pin 7 | Pin 6 | Pin 5 | Pin 4 | Pin 3 | Pin 2 | Pin 1 | Pin 0 |

|--------|-----------|-----------|-----------|-----------|-----------|-----------|-------|----------|-------|-------|-------|-------|-------|-------|-------|-------|

| Port A | PA15      |           | _         |           | _         | PA10      | PA8   | PA8<br>— | _     | PA6   | PA5   | PA4   | PA3   | PA2   | PA1   | PA0   |

| Port B | _         | PB14      | PB13      | PB12      | PB11      | _         | _     | PB8      | PB7   | _     | _     | _     | _     | _     | _     | —     |

| Port C | PC15      | PC14      | PC13      | PC12      | PC11      | PC10      | PC9   | PC8      | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| Port D | _         | _         | _         | _         | _         | _         | _     | PD8      | PD7   | PD6   | PD5   | PD4   | PD3   | PD2   | PD1   | PD0   |

| Port E | PE15      | PE14      | PE13      | PE12      | PE11      | PE10      | PE9   | PE8      | —     | _     | —     | —     | _     | _     | —     | —     |

| Port F | _         |           | _         | _         | _         | _         | _     | _        | _     | _     | PF5   | PF4   | PF3   | PF2   | PF1   | PF0   |

# Table 5.9. GPIO Pinout

|       | 64 Pin# and<br>Name |                 | Pin Alternate                                | Functionality / Description     |                                             |  |  |  |  |  |

|-------|---------------------|-----------------|----------------------------------------------|---------------------------------|---------------------------------------------|--|--|--|--|--|

| Pin # | Pin Name            | Analog          | Timers                                       | Communication                   | Other                                       |  |  |  |  |  |

| 39    | VDD_DREG            | Power supply f  | bly for on-chip voltage regulator.           |                                 |                                             |  |  |  |  |  |

| 40    | DECOUPLE            | Decouple outpup | ut for on-chip voltage regulator.            | An external capacitance of size | e C <sub>DECOUPLE</sub> is required at this |  |  |  |  |  |

| 41    | PC8                 | ACMP1_CH0       | TIM2_CC0 #2                                  | US0_CS #2                       |                                             |  |  |  |  |  |

| 42    | PC9                 | ACMP1_CH1       | TIM2_CC1 #2                                  | US0_CLK #2                      |                                             |  |  |  |  |  |

| 43    | PC10                | ACMP1_CH2       | TIM2_CC2 #2                                  | US0_RX #2                       |                                             |  |  |  |  |  |

| 44    | PC11                | ACMP1_CH3       |                                              | US0_TX #2                       |                                             |  |  |  |  |  |

| 45    | PC12                | ACMP1_CH4       |                                              |                                 | CMU_CLK0 #1                                 |  |  |  |  |  |

| 46    | PC13                | ACMP1_CH5       | TIM0_CDTI0 #1/3 TIM1_CC0<br>#0 PCNT0_S0IN #0 |                                 |                                             |  |  |  |  |  |

| 47    | PC14                | ACMP1_CH6       | TIM0_CDTI1 #1/3 TIM1_CC1<br>#0 PCNT0_S1IN #0 |                                 |                                             |  |  |  |  |  |

| 48    | PC15                | ACMP1_CH7       | TIM0_CDTI2 #1/3 TIM1_CC2<br>#0               |                                 | DBG_SWO #1                                  |  |  |  |  |  |

| 49    | PF0                 |                 | LETIM0_OUT0 #2                               |                                 | DBG_SWCLK #0/1                              |  |  |  |  |  |

| 50    | PF1                 |                 | LETIM0_OUT1 #2                               |                                 | DBG_SWDIO #0/1                              |  |  |  |  |  |

| 51    | PF2                 |                 |                                              |                                 | ACMP1_O #0 DBG_SWO #0                       |  |  |  |  |  |

| 52    | PF3                 |                 | TIM0_CDTI0 #2                                |                                 |                                             |  |  |  |  |  |

| 53    | PF4                 |                 | TIM0_CDTI1 #2                                |                                 |                                             |  |  |  |  |  |

| 54    | PF5                 |                 | TIM0_CDTI2 #2                                |                                 |                                             |  |  |  |  |  |

| 55    | IOVDD_5             | Digital IO powe | er supply 5.                                 |                                 |                                             |  |  |  |  |  |

| 56    | VSS                 | Ground.         |                                              |                                 |                                             |  |  |  |  |  |

| 57    | PE8                 |                 | PCNT2_S0IN #1                                |                                 |                                             |  |  |  |  |  |

| 58    | PE9                 |                 | PCNT2_S1IN #1                                |                                 |                                             |  |  |  |  |  |

| 59    | PE10                |                 | TIM1_CC0 #1                                  | US0_TX #0                       | BOOT_TX                                     |  |  |  |  |  |

| 60    | PE11                |                 | TIM1_CC1 #1                                  | US0_RX #0                       | BOOT_RX                                     |  |  |  |  |  |

| 61    | PE12                |                 | TIM1_CC2 #1                                  | US0_CLK #0                      |                                             |  |  |  |  |  |

| 62    | PE13                |                 |                                              | US0_CS #0                       | ACMP0_O #0                                  |  |  |  |  |  |

| 63    | PE14                |                 |                                              | LEU0_TX #2                      |                                             |  |  |  |  |  |

| 64    | PE15                |                 |                                              | LEU0_RX #2                      |                                             |  |  |  |  |  |

#### 5.5 EFM32G280 (LQFP100)

#### 5.5.1 Pinout

The EFM32G280 pinout is shown in the following figure and table. Alternate locations are denoted by "#" followed by the location number (Multiple locations on the same pin are split with "/"). Alternate locations can be configured in the LOCATION bitfield in the \*\_ROUTE register in the module in question.

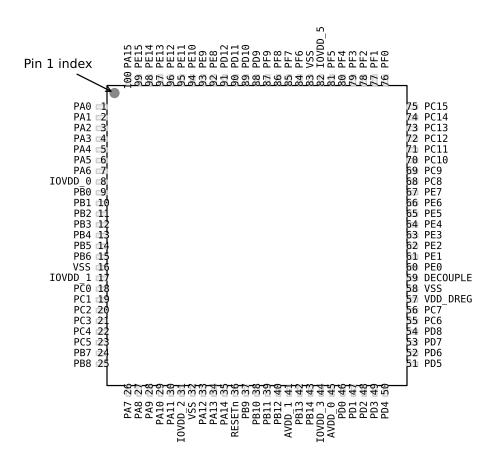

Figure 5.5. EFM32G280 Pinout (top view, not to scale)

#### Table 5.13. Device Pinout

|       | P100 Pin#<br>d Name | Pin Alternate Functionality / Description |             |                               |               |             |  |  |  |

|-------|---------------------|-------------------------------------------|-------------|-------------------------------|---------------|-------------|--|--|--|

| Pin # | Pin Name            | Analog                                    | EBI         | Timers                        | Communication | Other       |  |  |  |

| 1     | PA0                 |                                           | EBI_AD09 #0 | TIM0_CC0 #0/1                 | I2C0_SDA #0   |             |  |  |  |

| 2     | PA1                 |                                           | EBI_AD10 #0 | AD10 #0 TIM0_CC1 #0/1 I2C0_S0 |               | CMU_CLK1 #0 |  |  |  |

| 3     | PA2                 |                                           | EBI_AD11 #0 | TIM0_CC2 #0/1                 |               | CMU_CLK0 #0 |  |  |  |

| 4     | PA3                 |                                           | EBI_AD12 #0 | TIM0_CDTI0 #0                 | U0_TX #2      |             |  |  |  |

| 5     | PA4                 |                                           | EBI_AD13 #0 | TIM0_CDTI1 #0                 | U0_RX #2      |             |  |  |  |

|       | P100 Pin#<br>d Name |                | Ρ             | in Alternate Functionality                                   | / / Description               |                           |

|-------|---------------------|----------------|---------------|--------------------------------------------------------------|-------------------------------|---------------------------|

| Pin # | Pin Name            | Analog         | EBI           | Timers                                                       | Communication                 | Other                     |

| 6     | PA5                 |                | EBI_AD14 #0   | TIM0_CDTI2 #0                                                | LEU1_TX #1                    |                           |

| 7     | PA6                 |                | EBI_AD15 #0   |                                                              | LEU1_RX #1                    |                           |

| 8     | IOVDD_0             | Digital IO pov | wer supply 0. |                                                              |                               |                           |

| 9     | PB0                 |                |               | TIM1_CC0 #2                                                  |                               |                           |

| 10    | PB1                 |                |               | TIM1_CC1 #2                                                  |                               |                           |

| 11    | PB2                 |                |               | TIM1_CC2 #2                                                  |                               |                           |

| 12    | PB3                 |                |               | PCNT1_S0IN #1                                                | US2_TX #1                     |                           |

| 13    | PB4                 |                |               | PCNT1_S1IN #1                                                | US2_RX #1                     |                           |

| 14    | PB5                 |                |               |                                                              | US2_CLK #1                    |                           |

| 15    | PB6                 |                |               |                                                              | US2_CS #1                     |                           |

| 16    | VSS                 | Ground.        |               | 1                                                            | 1                             |                           |

| 17    | IOVDD_1             | Digital IO pov | wer supply 1. |                                                              |                               |                           |

| 18    | PC0                 | ACMP0_C<br>H0  |               | PCNT0_S0IN #2                                                | US1_TX #0                     |                           |

| 19    | PC1                 | ACMP0_C<br>H1  |               | PCNT0_S1IN #2                                                | US1_RX #0                     |                           |

| 20    | PC2                 | ACMP0_C<br>H2  |               |                                                              | US2_TX #0                     |                           |

| 21    | PC3                 | ACMP0_C<br>H3  |               |                                                              | US2_RX #0                     |                           |

| 22    | PC4                 | ACMP0_C<br>H4  |               | LETIM0_OUT0 #3<br>PCNT1_S0IN #0                              | US2_CLK #0                    |                           |

| 23    | PC5                 | ACMP0_C<br>H5  |               | LETIM0_OUT1 #3<br>PCNT1_S1IN #0                              | US2_CS #0                     |                           |

| 24    | PB7                 | LFXTAL_P       |               |                                                              | US1_CLK #0                    |                           |

| 25    | PB8                 | LFXTAL_N       |               |                                                              | US1_CS #0                     |                           |

| 26    | PA7                 |                |               |                                                              |                               |                           |

| 27    | PA8                 |                |               | TIM2_CC0 #0                                                  |                               |                           |

| 28    | PA9                 |                |               | TIM2_CC1 #0                                                  |                               |                           |

| 29    | PA10                |                |               | TIM2_CC2 #0                                                  |                               |                           |

| 30    | PA11                |                |               |                                                              |                               |                           |

| 31    | IOVDD_2             | Digital IO pov | wer supply 2. |                                                              |                               |                           |

| 32    | VSS                 | Ground.        |               |                                                              |                               |                           |

| 33    | PA12                |                |               | TIM2_CC0 #1                                                  |                               |                           |

| 34    | PA13                |                |               | TIM2_CC1 #1                                                  |                               |                           |

| 35    | PA14                |                |               | TIM2_CC2 #1                                                  |                               |                           |

| 36    | RESETn              |                |               | external reset source to this<br>ure that reset is released. | pin, it is required to only c | Irive this pin low during |

#### 5.5.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      |   |   | LOCATION                                                  |

|---------------|------|------|---|---|-----------------------------------------------------------|

| Functionality | 0    | 1    | 2 | 3 | Description                                               |

| ACMP0_CH0     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                       |

| ACMP0_CH1     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                       |

| ACMP0_CH2     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                       |

| ACMP0_CH3     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                       |

| ACMP0_CH4     | PC4  |      |   |   | Analog comparator ACMP0, channel 4.                       |

| ACMP0_CH5     | PC5  |      |   |   | Analog comparator ACMP0, channel 5.                       |

| ACMP0_CH6     | PC6  |      |   |   | Analog comparator ACMP0, channel 6.                       |

| ACMP0_CH7     | PC7  |      |   |   | Analog comparator ACMP0, channel 7.                       |

| ACMP0_O       | PE13 | PE2  |   |   | Analog comparator ACMP0, digital output.                  |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                       |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP1, channel 1.                       |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP1, channel 2.                       |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP1, channel 3.                       |

| ACMP1_CH4     | PC12 |      |   |   | Analog comparator ACMP1, channel 4.                       |

| ACMP1_CH5     | PC13 |      |   |   | Analog comparator ACMP1, channel 5.                       |

| ACMP1_CH6     | PC14 |      |   |   | Analog comparator ACMP1, channel 6.                       |

| ACMP1_CH7     | PC15 |      |   |   | Analog comparator ACMP1, channel 7.                       |

| ACMP1_O       | PF2  | PE3  |   |   | Analog comparator ACMP1, digital output.                  |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0. |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1. |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2. |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3. |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4. |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5. |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6. |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7. |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                            |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                            |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.             |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.             |

|               |      |      |   |   |                                                           |

#### Table 5.14. Alternate functionality overview

|       | P100 Pin#<br>d Name |               | Pi             | n Alternate Functionalit        | y / Description |       |

|-------|---------------------|---------------|----------------|---------------------------------|-----------------|-------|

| Pin # | Pin Name            | Analog        | EBI            | Timers                          | Communication   | Other |

| 4     | PA3                 | LCD_SEG<br>16 | EBI_AD12 #0    | TIM0_CDTI0 #0                   | U0_TX #2        |       |

| 5     | PA4                 | LCD_SEG<br>17 | EBI_AD13 #0    | TIM0_CDTI1 #0                   | U0_RX #2        |       |

| 6     | PA5                 | LCD_SEG<br>18 | EBI_AD14 #0    | TIM0_CDTI2 #0                   | LEU1_TX #1      |       |

| 7     | PA6                 | LCD_SEG<br>19 | EBI_AD15 #0    |                                 | LEU1_RX #1      |       |

| 8     | IOVDD_0             | Digital IO po | ower supply 0. |                                 | 1               |       |

| 9     | PB0                 | LCD_SEG<br>32 |                | TIM1_CC0 #2                     |                 |       |

| 10    | PB1                 | LCD_SEG<br>33 |                | TIM1_CC1 #2                     |                 |       |

| 11    | PB2                 | LCD_SEG<br>34 |                | TIM1_CC2 #2                     |                 |       |

| 12    | PB3                 | LCD_SEG<br>20 |                | PCNT1_S0IN #1                   | US2_TX #1       |       |

| 13    | PB4                 | LCD_SEG<br>21 |                | PCNT1_S1IN #1                   | US2_RX #1       |       |

| 14    | PB5                 | LCD_SEG<br>22 |                |                                 | US2_CLK #1      |       |

| 15    | PB6                 | LCD_SEG<br>23 |                |                                 | US2_CS #1       |       |

| 16    | VSS                 | Ground.       |                |                                 |                 |       |

| 17    | IOVDD_1             | Digital IO po | ower supply 1. |                                 |                 |       |

| 18    | PC0                 | ACMP0_C<br>H0 |                | PCNT0_S0IN #2                   | US1_TX #0       |       |

| 19    | PC1                 | ACMP0_C<br>H1 |                | PCNT0_S1IN #2                   | US1_RX #0       |       |

| 20    | PC2                 | ACMP0_C<br>H2 |                |                                 | US2_TX #0       |       |

| 21    | PC3                 | ACMP0_C<br>H3 |                |                                 | US2_RX #0       |       |

| 22    | PC4                 | ACMP0_C<br>H4 |                | LETIM0_OUT0 #3<br>PCNT1_S0IN #0 | US2_CLK #0      |       |

| 23    | PC5                 | ACMP0_C<br>H5 |                | LETIM0_OUT1 #3<br>PCNT1_S1IN #0 | US2_CS #0       |       |

| 24    | PB7                 | LFXTAL_P      |                |                                 | US1_CLK #0      |       |

| 25    | PB8                 | LFXTAL_N      |                |                                 | US1_CS #0       |       |

| 26    | PA7                 | LCD_SEG<br>35 |                |                                 |                 |       |

| 27    | PA8                 | LCD_SEG<br>36 |                | TIM2_CC0 #0                     |                 |       |

#### 5.9.2 Alternate Functionality Pinout

A wide selection of alternate functionality is available for multiplexing to various pins. This is shown in the following table. The table shows the name of the alternate functionality in the first column, followed by columns showing the possible LOCATION bitfield settings.

**Note:** Some functionality, such as analog interfaces, do not have alternate settings or a LOCATION bitfield. In these cases, the pinout is shown in the column corresponding to LOCATION 0.

| Alternate     |      |      |   |   | LOCATION                                                  |  |  |

|---------------|------|------|---|---|-----------------------------------------------------------|--|--|

| Functionality | 0    | 1    | 2 | 3 | Description                                               |  |  |

| ACMP0_CH0     | PC0  |      |   |   | Analog comparator ACMP0, channel 0.                       |  |  |

| ACMP0_CH1     | PC1  |      |   |   | Analog comparator ACMP0, channel 1.                       |  |  |

| ACMP0_CH2     | PC2  |      |   |   | Analog comparator ACMP0, channel 2.                       |  |  |

| ACMP0_CH3     | PC3  |      |   |   | Analog comparator ACMP0, channel 3.                       |  |  |

| ACMP0_CH4     | PC4  |      |   |   | Analog comparator ACMP0, channel 4.                       |  |  |

| ACMP0_CH5     | PC5  |      |   |   | Analog comparator ACMP0, channel 5.                       |  |  |

| ACMP0_CH6     | PC6  |      |   |   | Analog comparator ACMP0, channel 6.                       |  |  |

| ACMP0_CH7     | PC7  |      |   |   | Analog comparator ACMP0, channel 7.                       |  |  |

| ACMP0_O       | PE13 | PE2  |   |   | Analog comparator ACMP0, digital output.                  |  |  |

| ACMP1_CH0     | PC8  |      |   |   | Analog comparator ACMP1, channel 0.                       |  |  |

| ACMP1_CH1     | PC9  |      |   |   | Analog comparator ACMP1, channel 1.                       |  |  |

| ACMP1_CH2     | PC10 |      |   |   | Analog comparator ACMP1, channel 2.                       |  |  |

| ACMP1_CH3     | PC11 |      |   |   | Analog comparator ACMP1, channel 3.                       |  |  |

| ACMP1_CH4     | PC12 |      |   |   | Analog comparator ACMP1, channel 4.                       |  |  |

| ACMP1_CH5     | PC13 |      |   |   | Analog comparator ACMP1, channel 5.                       |  |  |

| ACMP1_CH6     | PC14 |      |   |   | Analog comparator ACMP1, channel 6.                       |  |  |

| ACMP1_CH7     | PC15 |      |   |   | Analog comparator ACMP1, channel 7.                       |  |  |

| ACMP1_O       | PF2  | PE3  |   |   | Analog comparator ACMP1, digital output.                  |  |  |

| ADC0_CH0      | PD0  |      |   |   | Analog to digital converter ADC0, input channel number 0. |  |  |

| ADC0_CH1      | PD1  |      |   |   | Analog to digital converter ADC0, input channel number 1. |  |  |

| ADC0_CH2      | PD2  |      |   |   | Analog to digital converter ADC0, input channel number 2. |  |  |

| ADC0_CH3      | PD3  |      |   |   | Analog to digital converter ADC0, input channel number 3. |  |  |

| ADC0_CH4      | PD4  |      |   |   | Analog to digital converter ADC0, input channel number 4. |  |  |

| ADC0_CH5      | PD5  |      |   |   | Analog to digital converter ADC0, input channel number 5. |  |  |

| ADC0_CH6      | PD6  |      |   |   | Analog to digital converter ADC0, input channel number 6. |  |  |

| ADC0_CH7      | PD7  |      |   |   | Analog to digital converter ADC0, input channel number 7. |  |  |

| BOOT_RX       | PE11 |      |   |   | Bootloader RX.                                            |  |  |

| BOOT_TX       | PE10 |      |   |   | Bootloader TX.                                            |  |  |

| CMU_CLK0      | PA2  | PC12 |   |   | Clock Management Unit, clock output number 0.             |  |  |

| CMU_CLK1      | PA1  | PD8  |   |   | Clock Management Unit, clock output number 1.             |  |  |

#### Table 5.26. Alternate functionality overview

| Alternate     |      |      |      |      | LOCATION                                                                                                                                                   |  |

|---------------|------|------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Functionality | 0    | 1    | 2    | 3    | Description                                                                                                                                                |  |

| TIM0_CDTI1    | PA4  | PC14 | PF4  | PC14 | Timer 0 Complimentary Deat Time Insertion channel 1.                                                                                                       |  |

| TIM0_CDTI2    | PA5  | PC15 | PF5  | PC15 | Timer 0 Complimentary Deat Time Insertion channel 2.                                                                                                       |  |

| TIM1_CC0      | PC13 | PE10 | PB0  |      | Timer 1 Capture Compare input / output channel 0.                                                                                                          |  |

| TIM1_CC1      | PC14 | PE11 | PB1  |      | Timer 1 Capture Compare input / output channel 1.                                                                                                          |  |

| TIM1_CC2      | PC15 | PE12 | PB2  |      | Timer 1 Capture Compare input / output channel 2.                                                                                                          |  |

| TIM2_CC0      | PA8  | PA12 | PC8  |      | Timer 2 Capture Compare input / output channel 0.                                                                                                          |  |

| TIM2_CC1      | PA9  | PA13 | PC9  |      | Timer 2 Capture Compare input / output channel 1.                                                                                                          |  |

| TIM2_CC2      | PA10 | PA14 | PC10 |      | Timer 2 Capture Compare input / output channel 2.                                                                                                          |  |

| U0_RX         | PF7  | PE1  | PA4  | PC15 | UART0 Receive input.                                                                                                                                       |  |

| U0_TX         | PF6  | PE0  | PA3  | PC14 | UART0 Transmit output. Also used as receive input in half duplex communication.                                                                            |  |

| US0_CLK       | PE12 | PE5  | PC9  |      | USART0 clock input / output.                                                                                                                               |  |

| US0_CS        | PE13 | PE4  | PC8  |      | USART0 chip select input / output.                                                                                                                         |  |

|               |      | PE6  | PC10 |      | USART0 Asynchronous Receive.                                                                                                                               |  |

| US0_RX        | PE11 |      |      |      | USART0 Synchronous mode Master Input / Slave Output (MI-SO).                                                                                               |  |

| US0_TX        | PE10 | PE7  | PC11 |      | USART0 Asynchronous Transmit.Also used as receive input<br>in half duplex communication.<br>USART0 Synchronous mode Master Output / Slave Input<br>(MOSI). |  |

| US1_CLK       | PB7  | PD2  |      |      | USART1 clock input / output.                                                                                                                               |  |

| US1_CS        | PB8  | PD3  |      |      | USART1 chip select input / output.                                                                                                                         |  |

| US1_RX        | PC1  | PD1  |      |      | USART1 Asynchronous Receive.<br>USART1 Synchronous mode Master Input / Slave Output (MI-<br>SO).                                                           |  |

| US1_TX        | PC0  | PD0  |      |      | USART1 Asynchronous Transmit.Also used as receive input<br>in half duplex communication.<br>USART1 Synchronous mode Master Output / Slave Input<br>(MOSI). |  |

| US2_CLK       | PC4  | PB5  |      |      | USART2 clock input / output.                                                                                                                               |  |

| US2_CS        | PC5  | PB6  |      |      | USART2 chip select input / output.                                                                                                                         |  |

| US2_RX        | PC3  | PB4  |      |      | USART2 Asynchronous Receive.<br>USART2 Synchronous mode Master Input / Slave Output (MI-<br>SO).                                                           |  |

| US2_TX        | PC2  | PB3  |      |      | USART2 Asynchronous Transmit.Also used as receive input<br>in half duplex communication.<br>USART2 Synchronous mode Master Output / Slave Input<br>(MOSI). |  |

# 8.2 TQFP64 PCB Layout

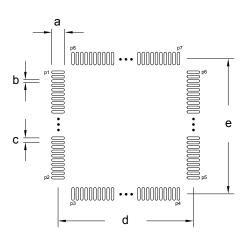

Figure 8.2. TQFP64 PCB Land Pattern

| Symbol | Dim. (mm) | Symbol | Pin Number | Symbol | Pin Number |

|--------|-----------|--------|------------|--------|------------|

| а      | 1.60      | P1     | 1          | P6     | 48         |

| b      | 0.30      | P2     | 16         | P7     | 49         |

| С      | 0.50      | P3     | 17         | P8     | 64         |

| d      | 11.50     | P4     | 32         |        |            |

| е      | 11.50     | P5     | 33         |        |            |

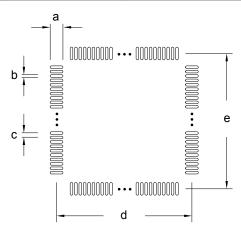

Figure 8.3. TQFP64 PCB Solder Mask

# Table 8.3. TQFP64 PCB Solder Mask Dimensions (Dimensions in mm)

| Symbol | Dim. (mm) |

|--------|-----------|

| а      | 1.72      |

| b      | 0.42      |

| с      | 0.50      |

| d      | 11.50     |

| e      | 11.50     |

| DIM | MIN      | NOM       | MAX   | DIM | MIN | NOM        | MAX |

|-----|----------|-----------|-------|-----|-----|------------|-----|

| D   | 0.170    | —         | 0.270 | S1  | _   | 4.500 BSC  | —   |

| E   | 0.950    | —         | 1.050 | V   |     | 9.000 BSC  | —   |

| F   | 0.170    | —         | 0.230 | V1  | _   | 4.5000 BSC | —   |

| G   | —        | 0.500 BSC |       | W   | _   | 0.200 BSC  | —   |

| Н   | 0.050    | _         | 0.150 | AA  | _   | 1.000BSC   | —   |

| J   | 0.090    | —         | 0.200 |     |     |            |     |

| К   | 0.500    | _         | 0.700 |     |     |            |     |

| L   | 0DE<br>G | _         | 7DEG  |     |     |            |     |

The TQFP48 Package is 7 by 7 mm in size and has a 0.5 mm pin pitch.

The TQFP48 Package uses Nickel-Palladium-Gold preplated leadframe.

All EFM32 packages are RoHS compliant and free of Bromine (Br) and Antimony (Sb).

For additional Quality and Environmental information, please see: http://www.silabs.com/support/quality/pages/default.aspx

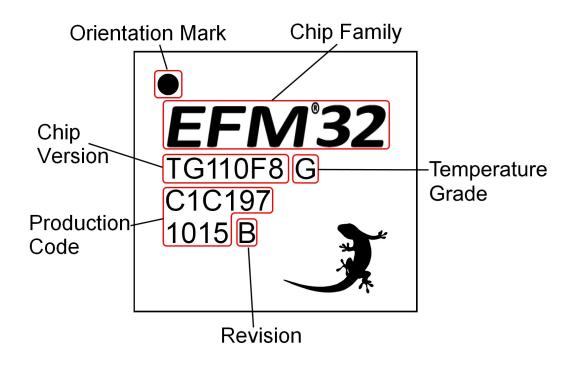

# 11.3 QFN32 Package Marking

In the illustration below package fields and position are shown.