Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                       |

| Core Size                  | 32-Bit Single-Core                                                    |

| Speed                      | 48MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                       |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 38                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 4K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                          |

| Data Converters            | A/D 10x12b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 48-LQFP                                                               |

| Supplier Device Package    | 48-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f038c6t7 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **3.8** Direct memory access controller (DMA)

The 5-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14) and ADC.

### 3.9 Interrupts and events

### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex<sup>®</sup>-M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

### 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 24 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 38 GPIOs can be connected to the 16 external interrupt lines.

## 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 10 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

| Aspect                              | Analog filter                                         | Digital filter                                                                                           |  |  |  |

|-------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Pulse width of<br>suppressed spikes | ≥ 50 ns                                               | Programmable length from 1 to 15<br>I2Cx peripheral clocks                                               |  |  |  |

| Benefits                            | Available in Stop mode                                | <ul> <li>Extra filtering capability vs.</li> <li>standard requirements</li> <li>Stable length</li> </ul> |  |  |  |

| Drawbacks                           | Variations depending on temperature, voltage, process | Wakeup from Stop on address<br>match is not available when digital<br>filter is enabled.                 |  |  |  |

### Table 6. Comparison of I<sup>2</sup>C analog and digital filters

In addition, I2C1 provides hardware support for SMBUS 2.0 and PMBUS 1.1: ARP capability, Host notify protocol, hardware CRC (PEC) generation/verification, timeouts verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripheral can be served by the DMA controller.

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 |

|--------------------------------------------------------------|------|

| 7-bit addressing mode                                        | Х    |

| 10-bit addressing mode                                       | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    |

| Fast Mode Plus with extra output drive I/Os (up to 1 Mbit/s) | х    |

| Independent clock                                            | Х    |

| SMBus                                                        | Х    |

| Wakeup from STOP                                             | Х    |

### Table 7. STM32F038x6 I<sup>2</sup>C implementation

1. X = supported.

# 3.14 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds one universal synchronous/asynchronous receiver/transmitter (USART1) which communicates at speeds of up to 6 Mbit/s.

It provides hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 supports also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and has a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interface can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>         | USART1 |

|---------------------------------------------|--------|

| Hardware flow control for modem             | Х      |

| Continuous communication using DMA          | Х      |

| Multiprocessor communication                | Х      |

| Synchronous mode                            | Х      |

| Smartcard mode                              | Х      |

| Single-wire half-duplex communication       | Х      |

| IrDA SIR ENDEC block                        | Х      |

| LIN mode                                    | Х      |

| Dual clock domain and wakeup from Stop mode | Х      |

| Receiver timeout interrupt                  | Х      |

| Modbus communication                        | Х      |

| Auto baud rate detection                    | Х      |

| Driver Enable                               | Х      |

|                                             | •      |

Table 8. STM32F038x6 USART implementation

1. X = supported.

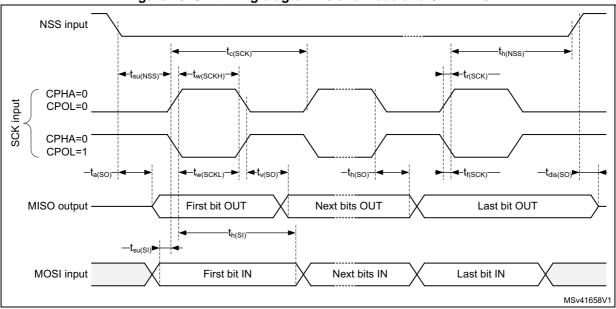

# 3.15 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

The SPI is able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

One standard I<sup>2</sup>S interface (multiplexed with SPI1) supporting four different audio standards can operate as master or slave at half-duplex communication mode. It can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, it can output a clock for an external audio component at 256 times the sampling frequency.

| Т | Table 9. STM32F038x6 SPI/I <sup>2</sup> S implementation | n |

|---|----------------------------------------------------------|---|

|   |                                                          |   |

| SPI features <sup>(1)</sup> | SPI |

|-----------------------------|-----|

| Hardware CRC calculation    | Х   |

| Rx/Tx FIFO                  | Х   |

| NSS pulse mode              | Х   |

| I <sup>2</sup> S mode       | Х   |

| TI mode                     | Х   |

1. X = supported.

# 3.16 Serial wire debug port (SW-DP)

An ARM SW-DP interface is provided to allow a serial wire debugging tool to be connected to the MCU.

| Na               | me                      | Abbreviation                                                                                                                         | Definition                                                  |  |  |  |  |  |  |

|------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| Pin r            | ame                     | Unless otherwise specified in brackets below the pin name, the pin fund<br>during and after reset is the same as the actual pin name |                                                             |  |  |  |  |  |  |

|                  |                         | S                                                                                                                                    | Supply pin                                                  |  |  |  |  |  |  |

| Pin              | type                    | I                                                                                                                                    | Input-only pin                                              |  |  |  |  |  |  |

|                  |                         | I/O                                                                                                                                  | Input / output pin                                          |  |  |  |  |  |  |

|                  |                         | FT                                                                                                                                   | 5 V-tolerant I/O                                            |  |  |  |  |  |  |

|                  |                         | FTf                                                                                                                                  | 5 V-tolerant I/O, FM+ capable                               |  |  |  |  |  |  |

|                  |                         | TTa 3.3 V-tolerant I/O directly connected to ADC                                                                                     |                                                             |  |  |  |  |  |  |

| I/O str          | ucture                  | POR External power on reset pin with embedded weak pul resistor, powered from V <sub>DDA</sub>                                       |                                                             |  |  |  |  |  |  |

|                  |                         | TC Standard 3.3V I/O                                                                                                                 |                                                             |  |  |  |  |  |  |

|                  |                         | В                                                                                                                                    | Dedicated BOOT0 pin                                         |  |  |  |  |  |  |

|                  |                         | RST                                                                                                                                  | Bidirectional reset pin with embedded weak pull-up resistor |  |  |  |  |  |  |

| No               | tes                     | Unless otherwise specified by a note, all I/Os are set as floating inputs durin and after reset                                      |                                                             |  |  |  |  |  |  |

| Die              | Alternate functions     | Functions select                                                                                                                     | ted through GPIOx_AFR registers                             |  |  |  |  |  |  |

| Pin<br>functions | Additional<br>functions | Functions directly selected/enabled through peripheral registers                                                                     |                                                             |  |  |  |  |  |  |

| Table 10. Legend/abbreviations | used in the | pinout table |

|--------------------------------|-------------|--------------|

| Pin number |          |          | ber     |         |                                   |          | _      |        | Pin functions       |                                            |  |  |

|------------|----------|----------|---------|---------|-----------------------------------|----------|--------|--------|---------------------|--------------------------------------------|--|--|

| LQFP48     | UFQFPN32 | NFQFPN28 | WLCSP25 | TSSOP20 | Pin name<br>(function upon reset) | Pin type | )<br>N |        | Alternate functions | Additional<br>functions                    |  |  |

| 1          | -        | -        | -       | -       | VBAT                              | S        | -      | -      | Backup power supply |                                            |  |  |

| 2          | -        | -        | -       | -       | PC13                              | I/O      | тс     | (1)(2) | -                   | RTC_TAMP1,<br>RTC_TS,<br>RTC_OUT,<br>WKUP2 |  |  |

| 3          | -        | -        | -       | -       | PC14-OSC32_IN<br>(PC14)           | I/O      | тс     | (1)(2) | -                   | OSC32_IN                                   |  |  |

| 4          | -        | -        | -       | -       | PC15-OSC32_OUT<br>(PC15)          | I/O      | тс     | (1)(2) | -                   | OSC32_OUT                                  |  |  |

### Table 11. Pin definitions

| Pin name | AF0                 | AF1      | AF2        | AF3       |

|----------|---------------------|----------|------------|-----------|

| PB0      | EVENTOUT            | TIM3_CH3 | TIM1_CH2N  | -         |

| PB1      | TIM14_CH1           | TIM3_CH4 | TIM1_CH3N  | -         |

| PB2      | -                   | -        | -          | -         |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT | TIM2_CH2   | -         |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1 | EVENTOUT   | -         |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2 | TIM16_BKIN | I2C1_SMBA |

| PB6      | USART1_TX           | I2C1_SCL | TIM16_CH1N | -         |

| PB7      | USART1_RX           | I2C1_SDA | TIM17_CH1N | -         |

| PB8      | -                   | I2C1_SCL | TIM16_CH1  | -         |

| PB9      | IR_OUT              | I2C1_SDA | TIM17_CH1  | EVENTOUT  |

| PB10     | -                   | I2C1_SCL | TIM2_CH3   | -         |

| PB11     | EVENTOUT            | I2C1_SDA | TIM2_CH4   | -         |

| PB12     | SPI1_NSS            | EVENTOUT | TIM1_BKIN  | -         |

| PB13     | SPI1_SCK            | -        | TIM1_CH1N  | -         |

| PB14     | SPI1_MISO           | -        | TIM1_CH2N  | -         |

| PB15     | SPI1_MOSI           | -        | TIM1_CH3N  | -         |

# 6 Electrical characteristics

## 6.1 Parameter conditions

Unless otherwise specified, all voltages are referenced to V<sub>SS</sub>.

### 6.1.1 Minimum and maximum values

Unless otherwise specified, the minimum and maximum values are guaranteed in the worst conditions of ambient temperature, supply voltage and frequencies by tests in production on 100% of the devices with an ambient temperature at  $T_A = 25$  °C and  $T_A = T_A max$  (given by the selected temperature range).

Data based on characterization results, design simulation and/or technology characteristics are indicated in the table footnotes and are not tested in production. Based on characterization, the minimum and maximum values refer to sample tests and represent the mean value plus or minus three times the standard deviation (mean  $\pm 3\sigma$ ).

### 6.1.2 Typical values

Unless otherwise specified, typical data are based on  $T_A = 25$  °C,  $V_{DD} = 1.8$  V and  $V_{DDA} = 3.3$  V. They are given only as design guidelines and are not tested.

Typical ADC accuracy values are determined by characterization of a batch of samples from a standard diffusion lot over the full temperature range, where 95% of the devices have an error less than or equal to the value indicated (mean  $\pm 2\sigma$ ).

### 6.1.3 Typical curves

Unless otherwise specified, all typical curves are given only as design guidelines and are not tested.

### 6.1.4 Loading capacitor

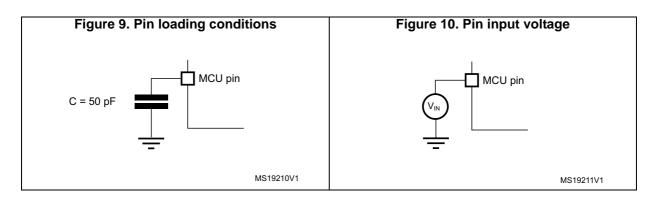

The loading conditions used for pin parameter measurement are shown in *Figure 9*.

### 6.1.5 Pin input voltage

The input voltage measurement on a pin of the device is described in Figure 10.

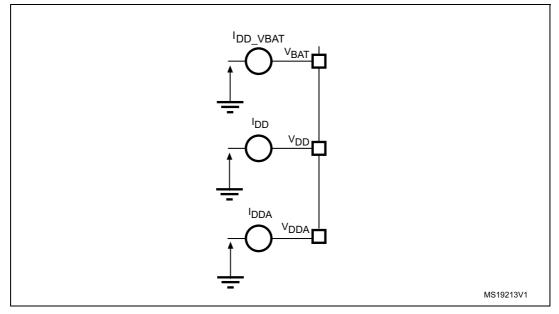

# 6.1.7 Current consumption measurement

### Figure 12. Current consumption measurement scheme

| Symbol           |                         |                       |                   |     | V <sub>DDA</sub>                    | = 2.4 V |        | V <sub>DDA</sub> = 3.6 V |       |       |        |    |

|------------------|-------------------------|-----------------------|-------------------|-----|-------------------------------------|---------|--------|--------------------------|-------|-------|--------|----|

|                  | Parameter               | Conditions            | f <sub>HCLK</sub> | Tum | Max @ T <sub>A</sub> <sup>(2)</sup> |         |        | Turn                     | М     | (2)   | Unit   |    |

|                  |                         |                       |                   | Тур | 25 °C                               | 85 °C   | 105 °C | Тур                      | 25 °C | 85 °C | 105 °C |    |

|                  |                         | HSE                   | 48 MHz            | 147 | 170                                 | 180     | 184    | 160                      | 183   | 195   | 199    |    |

|                  | Cupply                  | bypass,<br>PLL on     | 32 MHz            | 101 | 121                                 | 127     | 129    | 109                      | 129   | 137   | 140    |    |

|                  | Supply<br>current in    |                       | 24 MHz            | 79  | 97                                  | 101     | 103    | 86                       | 104   | 110   | 112    |    |

|                  | Run or<br>Sleep         | HSE                   | 8 MHz             | 1   | 3                                   | 3       | 3      | 2                        | 3     | 3     | 4      |    |

| I <sub>DDA</sub> | mode,                   | bypass,<br>PLL off    | 1 MHz             | 1   | 2                                   | 2       | 2      | 2                        | 2     | 3     | 3      | μA |

|                  | code<br>executing       |                       | 48 MHz            | 219 | 243                                 | 256     | 260    | 240                      | 267   | 279   | 284    |    |

|                  | from Flash<br>memory or | HSI clock,<br>PLL on  | 32 MHz            | 172 | 195                                 | 203     | 206    | 190                      | 210   | 222   | 226    |    |

|                  | RAM                     |                       | 24 MHz            | 150 | 170                                 | 177     | 180    | 165                      | 186   | 193   | 196    |    |

|                  |                         | HSI clock,<br>PLL off | 8 MHz             | 71  | 83                                  | 87      | 88     | 81                       | 95    | 97    | 98     |    |

Table 22. Typical and maximum current consumption from the  $V_{\text{DDA}}$  supply

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

| Symbol P         | Parameter               | Conditions          | Typ. @ V <sub>DD</sub> = 1.8 V |                          |                          |                          |                          |                          |                          | Мах                    |                        |                         |      |

|------------------|-------------------------|---------------------|--------------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|--------------------------|------------------------|------------------------|-------------------------|------|

|                  |                         |                     | V <sub>DDA</sub> = 1.8 V       | V <sub>DDA</sub> = 2.0 V | V <sub>DDA</sub> = 2.4 V | V <sub>DDA</sub> = 2.7 V | V <sub>DDA</sub> = 3.0 V | V <sub>DDA</sub> = 3.3 V | V <sub>DDA</sub> = 3.6 V | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

| I <sub>DD</sub>  | Supply                  |                     |                                |                          |                          |                          |                          | 2.3                      | 14.9                     | 35.6                   |                        |                         |      |

| I <sub>DDA</sub> | current in<br>Stop mode | All oscillators OFF | 0.8                            | 0.8                      | 0.8                      | 0.9                      | 0.9                      | 1.0                      | 1.1                      | 1.5                    | 2.6                    | 3.4                     | μA   |

### Table 23. Typical and maximum consumption in Stop mode

| Symbol           | Symbol Parameter                |                   |                        | sumption in<br>mode     |                        | sumption in mode        | Unit |

|------------------|---------------------------------|-------------------|------------------------|-------------------------|------------------------|-------------------------|------|

| Symbol           | Falainetei                      | f <sub>HCLK</sub> | Peripherals<br>enabled | Peripherals<br>disabled | Peripherals<br>enabled | Peripherals<br>disabled | Unit |

|                  |                                 | 48 MHz            | 18.5                   | 11.6                    | 10.8                   | 2.6                     |      |

|                  |                                 | 36 MHz            | 14.1                   | 8.9                     | 8.2                    | 2.0                     |      |

|                  |                                 | 32 MHz            | 12.7                   | 8.1                     | 7.3                    | 1.8                     |      |

|                  | Current                         | 24 MHz            | 9.7                    | 6.2                     | 5.6                    | 1.4                     |      |

|                  | consumption                     | 16 MHz            | 6.7                    | 4.3                     | 3.9                    | 1.1                     | m۸   |

| I <sub>DD</sub>  | from V <sub>DD</sub><br>supply  | 8 MHz             | 3.4                    | 2.3                     | 1.9                    | 0.6                     | - mA |

|                  | Supply                          | 4 MHz             | 2.1                    | 1.4                     | 1.3                    | 0.5                     |      |

|                  |                                 | 2 MHz             | 1.3                    | 0.9                     | 0.9                    | 0.5                     |      |

|                  |                                 | 1 MHz             | 0.9                    | 0.7                     | 0.7                    | 0.4                     |      |

|                  |                                 | 500 kHz           | 0.7                    | 0.6                     | 0.6                    | 0.4                     |      |

|                  |                                 | 48 MHz            |                        | 1:                      | 36                     |                         |      |

|                  |                                 | 36 MHz            |                        | 1(                      | 05                     |                         |      |

|                  |                                 | 32 MHz            |                        | 9                       | 6                      |                         |      |

|                  | Current                         | 24 MHz            |                        | 7                       | 6                      |                         |      |

| I <sub>DDA</sub> | consumption                     | 16 MHz            |                        | 5                       | 6                      |                         | μA   |

| 'DDA             | from V <sub>DDA</sub><br>supply | 8 MHz             |                        |                         | 1                      |                         | μΛ   |

|                  | Supply                          | 4 MHz             |                        |                         | 1                      |                         |      |

|                  |                                 | 2 MHz             |                        |                         | 1                      |                         | 1    |

|                  |                                 | 1 MHz             |                        |                         | 1                      |                         |      |

|                  |                                 | 500 kHz           |                        |                         | 1                      |                         |      |

# Table 25. Typical current consumption, code executing from Flash memory,running from HSE 8 MHz crystal

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 44: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt

### 6.3.5 Wakeup time from low-power mode

The wakeup times given in *Table 28* are the latency between the event and the execution of the first user instruction. The device goes in low-power mode after the WFE (Wait For Event) instruction, in the case of a WFI (Wait For Interruption) instruction, 16 CPU cycles must be added to the following timings due to the interrupt latency in the Cortex M0 architecture.

The SYSCLK clock source setting is kept unchanged after wakeup from Sleep mode. During wakeup from Stop mode, SYSCLK takes the default setting: HSI 8 MHz.

The wakeup source from Sleep and Stop mode is an EXTI line configured in event mode.

All timings are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*..

| Symbol               | Parameter              |         | V <sub>DDA</sub> | Мах   | Unit |

|----------------------|------------------------|---------|------------------|-------|------|

| Symbol               | Falameter              | = 1.8 V | = 3.3 V          | IVIAX | Unit |

| t <sub>WUSTOP</sub>  | Wakeup from Stop mode  |         | 2.8              | 5.3   | μs   |

| t <sub>WUSLEEP</sub> | Wakeup from Sleep mode | 4 SYSCL | K cycles         | -     | μs   |

### Table 28. Low-power mode wakeup timings

### 6.3.6 External clock source characteristics

### High-speed external user clock generated from an external source

In bypass mode the HSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in Section 6.3.13. However, the recommended clock input waveform is shown in *Figure 13: High-speed external clock source AC timing diagram*.

| Symbol                                       | Parameter <sup>(1)</sup>             | Min                    | Тур | Max                    | Unit |

|----------------------------------------------|--------------------------------------|------------------------|-----|------------------------|------|

| f <sub>HSE_ext</sub>                         | User external clock source frequency | -                      | 8   | 32                     | MHz  |

| V <sub>HSEH</sub>                            | OSC_IN input pin high level voltage  | 0.7 V <sub>DDIOx</sub> | -   | V <sub>DDIOx</sub>     | V    |

| V <sub>HSEL</sub>                            | OSC_IN input pin low level voltage   | V <sub>SS</sub>        | -   | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(HSEH)</sub><br>t <sub>w(HSEL)</sub> | OSC_IN high or low time              | 15                     | -   | -                      | ns   |

| t <sub>r(HSE)</sub><br>t <sub>f(HSE)</sub>   | OSC_IN rise or fall time             | -                      | -   | 20                     | 115  |

### Table 29. High-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

### High-speed external clock generated from a crystal/ceramic resonator

The high-speed external (HSE) clock can be supplied with a 4 to 32 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 31*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter                   | Conditions <sup>(1)</sup>                                   | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-----------------------------|-------------------------------------------------------------|--------------------|-----|--------------------|------|

| f <sub>OSC_IN</sub>                 | Oscillator frequency        | -                                                           | 4                  | 8   | 32                 | MHz  |

| R <sub>F</sub>                      | Feedback resistor           | -                                                           | -                  | 200 | -                  | kΩ   |

|                                     |                             | During startup <sup>(3)</sup>                               | -                  | -   | 8.5                |      |

| I <sub>DD</sub>                     |                             | V <sub>DD</sub> = 1.8 V,<br>Rm = 30 Ω,<br>CL = 10 pF@8 MHz  | -                  | 0.4 | -                  |      |

|                                     |                             | V <sub>DD</sub> = 1.8 V,<br>Rm = 45 Ω,<br>CL = 10 pF@8 MHz  | -                  | 0.5 | _                  |      |

|                                     | HSE current consumption     | V <sub>DD</sub> = 1.8 V,<br>Rm = 30 Ω,<br>CL = 5 pF@32 MHz  | -                  | 0.8 | -                  | mA   |

|                                     |                             | V <sub>DD</sub> = 1.8 V,<br>Rm = 30 Ω,<br>CL = 10 pF@32 MHz | -                  | 1   | -                  |      |

|                                     |                             | V <sub>DD</sub> = 1.8 V,<br>Rm = 30 Ω,<br>CL = 20 pF@32 MHz | -                  | 1.5 | -                  |      |

| 9 <sub>m</sub>                      | Oscillator transconductance | Startup                                                     | 10                 | -   | -                  | mA/V |

| t <sub>SU(HSE)</sub> <sup>(4)</sup> | Startup time                | V <sub>DD</sub> is stabilized                               | -                  | 2   | -                  | ms   |

| Table 31. | HSE | oscillator | characteristics |

|-----------|-----|------------|-----------------|

|           |     |            |                 |

1. Resonator characteristics given by the crystal/ceramic resonator manufacturer.

2. Guaranteed by design, not tested in production.

3. This consumption level occurs during the first 2/3 of the  $t_{\mbox{SU(HSE)}}$  startup time

4. t<sub>SU(HSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer

For  $C_{L1}$  and  $C_{L2}$ , it is recommended to use high-quality external ceramic capacitors in the 5 pF to 20 pF range (Typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see *Figure 15*).  $C_{L1}$  and  $C_{L2}$  are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of  $C_{L1}$  and  $C_{L2}$ . PCB and MCU pin capacitance must be included (10 pF can be used as a rough estimate of the combined pin and board capacitance) when sizing  $C_{L1}$  and  $C_{L2}$ .

Note: For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website www.st.com.

| Symbol           | Description                                    | Func<br>suscer | Unit               |      |

|------------------|------------------------------------------------|----------------|--------------------|------|

|                  | Description                                    |                | Positive injection | Unit |

|                  | Injected current on BOOT0                      | -0             | NA                 |      |

| I <sub>INJ</sub> | Injected current on all FT, FTf and POR pins   | -5             | NA                 | mA   |

|                  | Injected current on all TTa, TC and RESET pins | -5             | +5                 |      |

### Table 43. I/O current injection susceptibility

### 6.3.13 I/O port characteristics

### General input/output characteristics

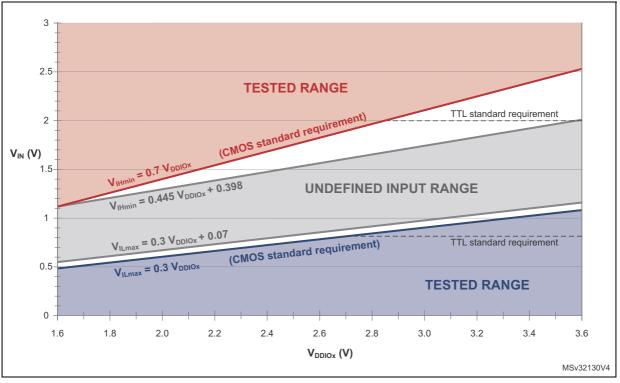

Unless otherwise specified, the parameters given in *Table 44* are derived from tests performed under the conditions summarized in *Table 18: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                                | Conditions                                                                     | Min                                            | Тур                | Max                                          | Unit |

|------------------|------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------|--------------------|----------------------------------------------|------|

|                  |                                          | TC and TTa I/O                                                                 | -                                              | -                  | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  |      |

|                  | Low level input                          | FT and FTf I/O                                                                 | -                                              | -                  | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |

| V <sub>IL</sub>  | voltage                                  | BOOT0                                                                          | -                                              | -                  | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V    |

|                  |                                          | All I/Os except<br>BOOT0 pin                                                   | -                                              | -                  | 0.3 V <sub>DDIOx</sub>                       |      |

|                  |                                          | TC and TTa I/O                                                                 | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                  | -                                            |      |

|                  | High lovel input                         | FT and FTf I/O                                                                 | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                  | -                                            |      |

| V <sub>IH</sub>  | High level input<br><sup>H</sup> voltage | BOOT0                                                                          | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                  | -                                            | V    |

|                  | All I/Os except<br>BOOT0 pin             | 0.7 V <sub>DDIOx</sub>                                                         | -                                              | -                  |                                              |      |

|                  |                                          | TC and TTa I/O                                                                 | -                                              | 200 <sup>(1)</sup> | -                                            |      |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis            | FT and FTf I/O                                                                 | -                                              | 100 <sup>(1)</sup> | -                                            | mV   |

|                  |                                          | BOOT0                                                                          | -                                              | 300 <sup>(1)</sup> | -                                            |      |

|                  |                                          | TC, FT and FTf I/O<br>TTa in digital mode<br>$V_{SS} \le V_{IN} \le V_{DDIOX}$ | -                                              | -                  | ± 0.1                                        |      |

| I <sub>lkg</sub> | Input leakage<br>current <sup>(2)</sup>  | TTa in digital mode<br>V <sub>DDIOx</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDA</sub> | -                                              | -                  | 1                                            | μA   |

|                  |                                          | TTa in analog mode<br>V <sub>SS</sub> ≤ V <sub>IN</sub> ≤ V <sub>DDA</sub>     | -                                              | -                  | ± 0.2                                        |      |

|                  |                                          | FT and FTf I/O<br>$V_{DDIOx} \le V_{IN} \le 5 V$                               | -                                              | -                  | 10                                           |      |

### Table 44. I/O static characteristics

Figure 19. TC and TTa I/O input characteristics

Figure 20. Five volt tolerant (FT and FTf) I/O input characteristics

### **Output driving current**

The GPIOs (general purpose input/outputs) can sink or source up to +/-8 mA, and sink or source up to +/- 20 mA (with a relaxed  $V_{OL}/V_{OH}$ ).

In the user application, the number of I/O pins which can drive current must be limited to respect the absolute maximum rating specified in Section 6.2:

- The sum of the currents sourced by all the I/Os on V<sub>DDIOx</sub>, plus the maximum consumption of the MCU sourced on V<sub>DD</sub>, cannot exceed the absolute maximum rating ΣI<sub>VDD</sub> (see *Table 15: Voltage characteristics*).

- The sum of the currents sunk by all the I/Os on V<sub>SS</sub>, plus the maximum consumption of the MCU sunk on V<sub>SS</sub>, cannot exceed the absolute maximum rating ΣI<sub>VSS</sub> (see *Table 15: Voltage characteristics*).

### **Output voltage levels**

Unless otherwise specified, the parameters given in the table below are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 18: General operating conditions*. All I/Os are CMOS- and TTL-compliant (FT, TTa or TC unless otherwise specified).

| Symbol                            | Parameter                                                  | Conditions                | Min                     | Max | Unit |

|-----------------------------------|------------------------------------------------------------|---------------------------|-------------------------|-----|------|

| V <sub>OL</sub> <sup>(2)</sup>    | Output low level voltage for an I/O pin                    | I <sub>IO</sub>   = 4 mA  | -                       | 0.4 | V    |

| V <sub>OH</sub> <sup>(2)</sup>    | Output high level voltage for an I/O pin                   | 1101 - 4 MA               | V <sub>DDIOx</sub> -0.4 | -   | V    |

| V <sub>OLFm+</sub> <sup>(3)</sup> | Output low level voltage for an FTf I/O pin in<br>Fm+ mode | I <sub>IO</sub>   = 10 mA | -                       | 0.4 | V    |

### Table 45. Output voltage characteristics<sup>(1)</sup>

1. The I<sub>IO</sub> current sourced or sunk by the device must always respect the absolute maximum rating specified in *Table 15: Voltage characteristics*, and the sum of the currents sourced or sunk by all the I/Os (I/O ports and control pins) must always respect the absolute maximum ratings  $\Sigma I_{IO}$ .

2. Data based on characterization results. Not tested in production.

3. Data based on design simulation only. Not tested in production.

| Symbol                                 | Parameter                        | Conditions                                      | Min                                                                        | Тур   | Мах                                               | Unit                       |

|----------------------------------------|----------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|-------|---------------------------------------------------|----------------------------|

|                                        |                                  | ADC clock = HSI14                               | 1.5 ADC<br>cycles + 2<br>f <sub>PCLK</sub> cycles                          | -     | 1.5 ADC<br>cycles + 3<br>f <sub>PCLK</sub> cycles | -                          |

| W <sub>LATENCY</sub> <sup>(2)(4)</sup> | ADC_DR register ready<br>latency | ADC clock = PCLK/2                              | -                                                                          | 4.5   | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                  | ADC clock = PCLK/4                              | -                                                                          | 8.5   | -                                                 | f <sub>PCLK</sub><br>cycle |

|                                        |                                  | $f_{ADC} = f_{PCLK}/2 = 14 \text{ MHz}$         |                                                                            | 0.196 | •                                                 | μs                         |

|                                        | Trigger conversion latency       | f <sub>ADC</sub> = f <sub>PCLK</sub> /2         | 5.5                                                                        |       | 1/f <sub>PCLK</sub>                               |                            |

| t <sub>latr</sub> (2)                  |                                  | $f_{ADC} = f_{PCLK}/4 = 12 \text{ MHz}$         | 0.219                                                                      |       |                                                   | μs                         |

|                                        |                                  | $f_{ADC} = f_{PCLK}/4$                          | 10.5                                                                       |       | 1/f <sub>PCLK</sub>                               |                            |

|                                        |                                  | f <sub>ADC</sub> = f <sub>HSI14</sub> = 14 MHz  | 0.179                                                                      | -     | 0.250                                             | μs                         |

| Jitter <sub>ADC</sub>                  | ADC jitter on trigger conversion | f <sub>ADC</sub> = f <sub>HSI14</sub>           | -                                                                          | 1     | -                                                 | 1/f <sub>HSI14</sub>       |

| ts <sup>(2)</sup>                      | Sampling time                    | f <sub>ADC</sub> = 14 MHz                       | 0.107                                                                      | -     | 17.1                                              | μs                         |

| lS'-'                                  | Sampling time                    | -                                               | 1.5                                                                        | -     | 239.5                                             | 1/f <sub>ADC</sub>         |

| t <sub>STAB</sub> <sup>(2)</sup>       | Stabilization time               | -                                               |                                                                            | 14    |                                                   | 1/f <sub>ADC</sub>         |

| t <sub>CONV</sub> <sup>(2)</sup>       | Total conversion time            | f <sub>ADC</sub> = 14 MHz,<br>12-bit resolution | 1                                                                          | -     | 18                                                | μs                         |

|                                        | (including sampling time)        | 12-bit resolution                               | 14 to 252 (t <sub>S</sub> for sampling +12.5 for successive approximation) |       |                                                   | 1/f <sub>ADC</sub>         |

Table 49. ADC characteristics (continued)

1. During conversion of the sampled value (12.5 x ADC clock period), an additional consumption of 100  $\mu$ A on I<sub>DDA</sub> and 60  $\mu$ A on I<sub>DD</sub> should be taken into account.

2. Guaranteed by design, not tested in production.

3. Specified value includes only ADC timing. It does not include the latency of the register access.

4. This parameter specify latency for transfer of the conversion result to the ADC\_DR register. EOC flag is set at this time.

### Equation 1: R<sub>AIN</sub> max formula

$$R_{AIN} < \frac{T_{S}}{f_{ADC} \times C_{ADC} \times \ln(2^{N+2})} - R_{ADC}$$

The formula above (*Equation 1*) is used to determine the maximum external impedance allowed for an error below 1/4 of LSB. Here N = 12 (from 12-bit resolution).

| T <sub>s</sub> (cycles) | t <sub>S</sub> (µs) | R <sub>AIN</sub> max (kΩ) <sup>(1)</sup> |

|-------------------------|---------------------|------------------------------------------|

| 1.5                     | 0.11                | 0.4                                      |

| 7.5                     | 0.54                | 5.9                                      |

| 13.5                    | 0.96                | 11.4                                     |

### Table 50. $R_{AIN}$ max for $f_{ADC} = 14$ MHz

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |  |  |  |  |

|-------------------|--------------|--------------------------------|--------------------------------|------|--|--|--|--|

| /4                | 0            | 0.1                            | 409.6                          |      |  |  |  |  |

| /8                | 1            | 0.2                            | 819.2                          |      |  |  |  |  |

| /16               | 2            | 0.4                            | 1638.4                         |      |  |  |  |  |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |  |  |  |  |

| /64               | 4            | 1.6                            | 6553.6                         |      |  |  |  |  |

| /128              | 5            | 3.2                            | 13107.2                        |      |  |  |  |  |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |  |  |  |  |

Table 55. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |

|-----------|-------|-------------------|-------------------|------|

| 1         | 0     | 0.0853            | 5.4613            |      |

| 2         | 1     | 0.1706            | 10.9226           | ms   |

| 4         | 2     | 0.3413            | 21.8453           | ms   |

| 8         | 3     | 0.6826            | 43.6906           |      |

Table 56. WWDG min/max timeout value at 48 MHz (PCLK)

### 6.3.19 Communication interfaces

### I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.13: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

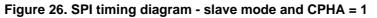

Figure 25. SPI timing diagram - slave mode and CPHA = 0

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}$

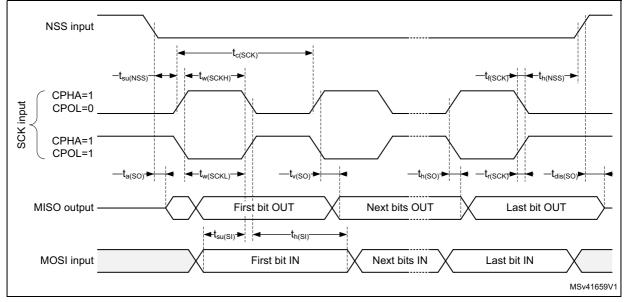

Figure 27. SPI timing diagram - master mode

1. Measurement points are done at CMOS levels: 0.3  $V_{\text{DD}}$  and 0.7  $V_{\text{DD}}.$

| Table | 59. | l <sup>2</sup> S | characteristics <sup>(1)</sup> |

|-------|-----|------------------|--------------------------------|

|-------|-----|------------------|--------------------------------|

| Symbol                                  | Parameter                                                               | Conditions                                               | Min   | Мах   | Unit |

|-----------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------|-------|-------|------|

| f <sub>CK</sub><br>1/t <sub>c(CK)</sub> | I <sup>2</sup> S clock frequency                                        | Master mode (data: 16 bits, Audio<br>frequency = 48 kHz) | 1.597 | 1.601 | MHz  |

|                                         |                                                                         | Slave mode                                               | 0     | 6.5   |      |

| t <sub>r(CK)</sub>                      | I <sup>2</sup> S clock rise time                                        | Consolitive load C = 15 pE                               | -     | 10    |      |

| t <sub>f(CK)</sub>                      | I <sup>2</sup> S clock fall time                                        | Capacitive load C <sub>L</sub> = 15 pF                   | -     | 12    |      |

| t <sub>w(CKH)</sub>                     | <sup>2</sup> S clock high time Master f <sub>PCLK</sub> = 16 MHz, audio |                                                          | 306   | -     | ns   |

| t <sub>w(CKL)</sub>                     | I <sup>2</sup> S clock low time                                         | clock low time frequency = 48 kHz                        |       | -     |      |

| t <sub>v(WS)</sub>                      | WS valid time                                                           | Master mode                                              | 2     | -     | 115  |

| t <sub>h(WS)</sub>                      | WS hold time                                                            | Master mode                                              | 2     | -     |      |

| t <sub>su(WS)</sub>                     | WS setup time                                                           | Slave mode                                               | 7     | -     |      |

| t <sub>h(WS)</sub>                      | WS hold time                                                            | Slave mode                                               | 0     | -     |      |

| DuCy(SCK)                               | I <sup>2</sup> S slave input clock duty cycle                           | Slave mode                                               | 25    | 75    | %    |

### IMPORTANT NOTICE - PLEASE READ CAREFULLY

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics – All rights reserved