Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM7®                                                                      |

| Core Size                  | 16/32-Bit                                                                  |

| Speed                      | 55MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, SPI, SSC, UART/USART, USB                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 32                                                                         |

| Program Memory Size        | 128KB (128K x 8)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 32K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                              |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-LQFP                                                                    |

| Supplier Device Package    | 64-LQFP (10x10)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7s128d-au |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 13.3 Functional Description

## 13.3.1 Reset Controller Overview

The Reset Controller is made up of an NRST Manager, a Brownout Manager, a Startup Counter and a Reset State Manager. It runs at Slow Clock and generates the following reset signals:

- proc\_nreset: Processor reset line. It also resets the Watchdog Timer.

- periph\_nreset: Affects the whole set of embedded peripherals.

- nrst\_out: Drives the NRST pin.

These reset signals are asserted by the Reset Controller, either on external events or on software action. The Reset State Manager controls the generation of reset signals and provides a signal to the NRST Manager when an assertion of the NRST pin is required.

The NRST Manager shapes the NRST assertion during a programmable time, thus controlling external device resets.

The startup counter waits for the complete crystal oscillator startup. The wait delay is given by the crystal oscillator startup time maximum value that can be found in the section Crystal Oscillator Characteristics in the Electrical Characteristics section of the product documentation.

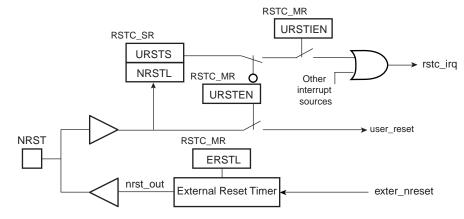

## 13.3.2 NRST Manager

The NRST Manager samples the NRST input pin and drives this pin low when required by the Reset State Manager. Figure 13-2 shows the block diagram of the NRST Manager.

## Figure 13-2. NRST Manager

#### 13.3.2.1 NRST Signal or Interrupt

The NRST Manager samples the NRST pin at Slow Clock speed. When the line is detected low, a User Reset is reported to the Reset State Manager.

However, the NRST Manager can be programmed to not trigger a reset when an assertion of NRST occurs. Writing the bit URSTEN at 0 in RSTC\_MR disables the User Reset trigger.

The level of the pin NRST can be read at any time in the bit NRSTL (NRST level) in RSTC\_SR. As soon as the pin NRST is asserted, the bit URSTS in RSTC\_SR is set. This bit clears only when RSTC\_SR is read.

The Reset Controller can also be programmed to generate an interrupt instead of generating a reset. To do so, the bit URSTIEN in RSTC\_MR must be written at 1.

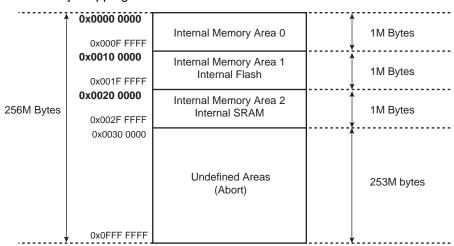

If an access is done in the address area 0x0030 000 to 0x003F FFFF, no abort is generated.

Figure 18-3. Internal Memory Mapping

## 18.3.2.2 Internal Memory Area 0

The first 32 bytes of Internal Memory Area 0 contain the ARM processor exception vectors, in particular, the Reset Vector at address 0x0.

Before execution of the remap command, the on-chip Flash is mapped into Internal Memory Area 0, so that the ARM7TDMI reaches an executable instruction contained in Flash. After the remap command, the internal SRAM at address 0x0020 0000 is mapped into Internal Memory Area 0. The memory mapped into Internal Memory Area 0 is accessible in both its original location and at address 0x0.

#### 18.3.3 Remap Command

After execution, the Remap Command causes the Internal SRAM to be accessed through the Internal Memory Area 0.

As the ARM vectors (Reset, Abort, Data Abort, Prefetch Abort, Undefined Instruction, Interrupt, and Fast Interrupt) are mapped from address 0x0 to address 0x20, the Remap Command allows the user to redefine dynamically these vectors under software control.

The Remap Command is accessible through the Memory Controller User Interface by writing the MC\_RCR (Remap Control Register) RCB field to one.

The Remap Command can be cancelled by writing the MC\_RCR RCB field to one, which acts as a toggling command. This allows easy debug of the user-defined boot sequence by offering a simple way to put the chip in the same configuration as after a reset.

## 18.3.4 Abort Status

There are three reasons for an abort to occur:

- access to an undefined address

- an access to a misaligned address.

When an abort occurs, a signal is sent back to all the masters, regardless of which one has generated the access. However, only the ARM7TDMI can take an abort signal into account, and only under the condition that it was generating an access. The Peripheral DMA Controller does not handle the abort input signal. Note that the connection is not represented in Figure 18-1.

## 20.2.2 Signal Names

Depending on the MODE settings, DATA is latched in different internal registers.

| MODE[3:0] | Symbol | Data                  |  |  |  |

|-----------|--------|-----------------------|--|--|--|

| 0000      | CMDE   | Command Register      |  |  |  |

| 0001      | ADDR0  | Address Register LSBs |  |  |  |

| 0010      | ADDR1  |                       |  |  |  |

| 0011      | ADDR2  |                       |  |  |  |

| 0100      | ADDR3  | Address Register MSBs |  |  |  |

| 0101      | DATA   | Data Register         |  |  |  |

| Default   | IDLE   | No register           |  |  |  |

Table 20-2. Mode Coding

When MODE is equal to CMDE, then a new command (strobed on DATA[15:0] or DATA[7:0] signals) is stored in the command register.

Note: DATA[7:0] pertains to the SAM7S32/16.

| DATA[15:0]<br>DATA[7:0] <sup>(1)</sup> | Symbol | Command Executed                     |

|----------------------------------------|--------|--------------------------------------|

|                                        |        |                                      |

| 0x0011                                 | READ   | Read Flash                           |

| 0x0012                                 | WP     | Write Page Flash                     |

| 0x0022                                 | WPL    | Write Page and Lock Flash            |

| 0x0032                                 | EWP    | Erase Page and Write Page            |

| 0x0042                                 | EWPL   | Erase Page and Write Page then Lock  |

| 0x0013                                 | EA     | Erase All                            |

| 0x0014                                 | SLB    | Set Lock Bit                         |

| 0x0024                                 | CLB    | Clear Lock Bit                       |

| 0x0015                                 | GLB    | Get Lock Bit                         |

| 0x0034                                 | SGPB   | Set General Purpose NVM bit          |

| 0x0044                                 | CGPB   | Clear General Purpose NVM bit        |

| 0x0025                                 | GGPB   | Get General Purpose NVM bit          |

| 0x0054                                 | SSE    | Set Security Bit                     |

| 0x0035                                 | GSE    | Get Security Bit                     |

| 0x001F                                 | WRAM   | Write Memory                         |

| 0x0016                                 | SEFC   | Select EFC Controller <sup>(2)</sup> |

| 0x001E                                 | GVE    | Get Version                          |

| Table 20-3. | Command Bit Coding |

|-------------|--------------------|

|-------------|--------------------|

Notes: 1. DATA[7:0] pertains to the SAM7S32/16.

2. Applies to SAM7S512.

## 20.2.5 Device Operations

Several commands on the Flash memory are available. These commands are summarized in Table 20-3 on page 126. Each command is driven by the programmer through the parallel interface running several read/write hand-shaking sequences.

When a new command is executed, the previous one is automatically achieved. Thus, chaining a read command after a write automatically flushes the load buffer in the Flash.

In the following tables, 21-6 through 21-18

## • DATA[15:0] pertains to SAM7S512/256/128/64/321/161

## • DATA[7:0] pertains to SAM7S32/16

## 20.2.5.1 Flash Read Command

This command is used to read the contents of the Flash memory. The read command can start at any valid address in the memory plane and is optimized for consecutive reads. Read handshaking can be chained; an internal address buffer is automatically increased.

| Step | Handshake Sequence | MODE[3:0] | DATA[15:0]         |

|------|--------------------|-----------|--------------------|

| 1    | Write handshaking  | CMDE      | READ               |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB |

| 3    | Write handshaking  | ADDR1     | Memory Address     |

| 4    | Read handshaking   | DATA      | *Memory Address++  |

| 5    | Read handshaking   | DATA      | *Memory Address++  |

|      |                    |           |                    |

| n    | Write handshaking  | ADDR0     | Memory Address LSB |

| n+1  | Write handshaking  | ADDR1     | Memory Address     |

| n+2  | Read handshaking   | DATA      | *Memory Address++  |

| n+3  | Read handshaking   | DATA      | *Memory Address++  |

|      |                    |           |                    |

Table 20-6. Read Command

Table 20-7. Read Command

| Step | Handshake Sequence | MODE[3:0] | DATA[7:0]          |

|------|--------------------|-----------|--------------------|

| 1    | Write handshaking  | CMDE      | READ               |

| 2    | Write handshaking  | ADDR0     | Memory Address LSB |

| 3    | Write handshaking  | ADDR1     | Memory Address     |

| 4    | Write handshaking  | ADDR2     | Memory Address     |

| 5    | Write handshaking  | ADDR3     | Memory Address     |

| 6    | Read handshaking   | DATA      | *Memory Address++  |

| 7    | Read handshaking   | DATA      | *Memory Address++  |

|      |                    |           |                    |

| n    | Write handshaking  | ADDR0     | Memory Address LSB |

| n+1  | Write handshaking  | ADDR1     | Memory Address     |

# 23.8.7 AIC Interrupt Pending Register

| Register Name: | AIC_IPR | ξ     |       |       |       |       |       |

|----------------|---------|-------|-------|-------|-------|-------|-------|

| Access Type:   | Read-on | lly   |       |       |       |       |       |

| Reset Value:   | 0x0     |       |       |       |       |       |       |

| 31             | 30      | 29    | 28    | 27    | 26    | 25    | 24    |

| PID31          | PID30   | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23             | 22      | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23          | PID22   | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15             | 14      | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15          | PID14   | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7              | 6       | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7           | PID6    | PID5  | PID4  | PID3  | PID2  | SYS   | FIQ   |

## • FIQ, SYS, PID2-PID31: Interrupt Pending

0 = Corresponding interrupt is not pending.

1 = Corresponding interrupt is pending.

## 23.8.8 AIC Interrupt Mask Register

| Register Name: | AIC_IMR   | 0     |       |       |       |       |       |

|----------------|-----------|-------|-------|-------|-------|-------|-------|

| Access Type:   | Read-only | y     |       |       |       |       |       |

| Reset Value:   | 0x0       |       |       |       |       |       |       |

| 31             | 30        | 29    | 28    | 27    | 26    | 25    | 24    |

| PID31          | PID30     | PID29 | PID28 | PID27 | PID26 | PID25 | PID24 |

| 23             | 22        | 21    | 20    | 19    | 18    | 17    | 16    |

| PID23          | PID22     | PID21 | PID20 | PID19 | PID18 | PID17 | PID16 |

| 15             | 14        | 13    | 12    | 11    | 10    | 9     | 8     |

| PID15          | PID14     | PID13 | PID12 | PID11 | PID10 | PID9  | PID8  |

| 7              | 6         | 5     | 4     | 3     | 2     | 1     | 0     |

| PID7           | PID6      | PID5  | PID4  | PID3  | PID2  | SYS   | FIQ   |

## • FIQ, SYS, PID2-PID31: Interrupt Mask

0 = Corresponding interrupt is disabled.

1 = Corresponding interrupt is enabled.

## 25. Power Management Controller (PMC)

## 25.1 Description

The Power Management Controller (PMC) optimizes power consumption by controlling all system and user peripheral clocks. The PMC enables/disables the clock inputs to many of the peripherals and the ARM Processor.

The Power Management Controller provides the following clocks:

- MCK, the Master Clock, programmable from a few hundred Hz to the maximum operating frequency of the device. It is available to the modules running permanently, such as the AIC and the Memory Controller.

- Processor Clock (PCK), switched off when entering processor in idle mode.

- Peripheral Clocks, typically MCK, provided to the embedded peripherals (USART, SSC, SPI, TWI, TC, MCI, etc.) and independently controllable. In order to reduce the number of clock names in a product, the Peripheral Clocks are named MCK in the product datasheet.

- UDP Clock (UDPCK), required by USB Device Port operations. (Does not pertain to SAM7S32/16.)

- Programmable Clock Outputs can be selected from the clocks provided by the clock generator and driven on the PCKx pins.

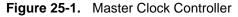

## 25.2 Master Clock Controller

The Master Clock Controller provides selection and division of the Master Clock (MCK). MCK is the clock provided to all the peripherals and the memory controller.

The Master Clock is selected from one of the clocks provided by the Clock Generator. Selecting the Slow Clock provides a Slow Clock signal to the whole device. Selecting the Main Clock saves power consumption of the PLL.

The Master Clock Controller is made up of a clock selector and a prescaler.

The Master Clock selection is made by writing the CSS field (Clock Source Selection) in PMC\_MCKR (Master Clock Register). The prescaler supports the division by a power of 2 of the selected clock between 1 and 64. The PRES field in PMC\_MCKR programs the prescaler.

Each time PMC\_MCKR is written to define a new Master Clock, the MCKRDY bit is cleared in PMC\_SR. It reads 0 until the Master Clock is established. Then, the MCKRDY bit is set and can trigger an interrupt to the processor. This feature is useful when switching from a high-speed clock to a lower one to inform the software when the change is actually done.

## 25.3 Processor Clock Controller

The PMC features a Processor Clock Controller (PCK) that implements the Processor Idle Mode. The Processor Clock can be disabled by writing the System Clock Disable Register (PMC\_SCDR). The status of this clock (at least for debug purpose) can be read in the System Clock Status Register (PMC\_SCSR).

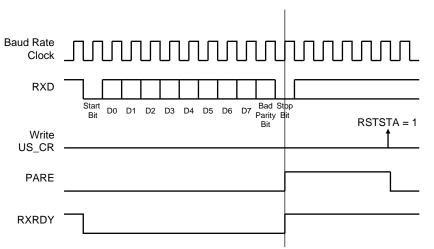

## 25.8 Clock Switching Details

## 25.8.1 Master Clock Switching Timings

Table 25-1 gives the worst case timings required for the Master Clock to switch from one selected clock to another one. This is in the event that the prescaler is de-activated. When the prescaler is activated, an additional time of 64 clock cycles of the new selected clock has to be added.

| From       | Main Clock                                                                | SLCK                                               | PLL Clock                                          |

|------------|---------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|

| То         |                                                                           |                                                    |                                                    |

| Main Clock | _                                                                         | 4 x SLCK +<br>2.5 x Main Clock                     | 3 x PLL Clock +<br>4 x SLCK +<br>1 x Main Clock    |

| SLCK       | 0.5 x Main Clock +<br>4.5 x SLCK                                          | _                                                  | 3 x PLL Clock +<br>5 x SLCK                        |

| PLL Clock  | 0.5 x Main Clock +<br>4 x SLCK +<br>PLLCOUNT x SLCK +<br>2.5 x PLLx Clock | 2.5 x PLL Clock +<br>5 x SLCK +<br>PLLCOUNT x SLCK | 2.5 x PLL Clock +<br>4 x SLCK +<br>PLLCOUNT x SLCK |

Table 25-1. Clock Switching Timings (Worst Case)

## 25.8.2 Clock Switching Waveforms

#

| LOCK           |  |

|----------------|--|

| MCKRDY         |  |

| Master Clock   |  |

| Write PMC_MCKR |  |

0 = The buffer empty signal from the transmitter PDC channel is inactive.

1 = The buffer empty signal from the transmitter PDC channel is active.

## • RXBUFF: Receive Buffer Full

0 = The buffer full signal from the receiver PDC channel is inactive.

1 = The buffer full signal from the receiver PDC channel is active.

## • COMMTX: Debug Communication Channel Write Status

0 = COMMTX from the ARM processor is inactive.

1 = COMMTX from the ARM processor is active.

## • COMMRX: Debug Communication Channel Read Status

0 = COMMRX from the ARM processor is inactive.

1 = COMMRX from the ARM processor is active.

## 27.6.21 PIO Pull Up Disable Register

Name:

```

PIO_PUDR

```

| Access Type: | Write-on | ly  |     |     |     |     |     |

|--------------|----------|-----|-----|-----|-----|-----|-----|

| 31           | 30       | 29  | 28  | 27  | 26  | 25  | 24  |

| P31          | P30      | P29 | P28 | P27 | P26 | P25 | P24 |

| 23           | 22       | 21  | 20  | 19  | 18  | 17  | 16  |

| P23          | P22      | P21 | P20 | P19 | P18 | P17 | P16 |

| 15           | 14       | 13  | 12  | 11  | 10  | 9   | 8   |

| P15          | P14      | P13 | P12 | P11 | P10 | P9  | P8  |

| 7            | 6        | 5   | 4   | 3   | 2   | 1   | 0   |

| P7           | P6       | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Pull Up Disable.

0 = No effect.

1 = Disables the pull up resistor on the I/O line.

## 27.6.22 PIO Pull Up Enable Register

Name: PIO\_PUER

| Access Type: | Write-only |

|--------------|------------|

|--------------|------------|

| 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  |

|-----|-----|-----|-----|-----|-----|-----|-----|

| P31 | P30 | P29 | P28 | P27 | P26 | P25 | P24 |

| 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  |

| P23 | P22 | P21 | P20 | P19 | P18 | P17 | P16 |

| 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

| P15 | P14 | P13 | P12 | P11 | P10 | P9  | P8  |

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0  |

## • P0-P31: Pull Up Enable.

0 = No effect.

1 = Enables the pull up resistor on the I/O line.

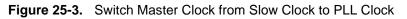

Figure 29-9. Master Read with Multiple Data Bytes

## 31.5 Product Dependencies

## 31.5.1 I/O Lines

The pins used for interfacing the USART may be multiplexed with the PIO lines. The programmer must first program the PIO controller to assign the desired USART pins to their peripheral function. If I/O lines of the USART are not used by the application, they can be used for other purposes by the PIO Controller.

To prevent the TXD line from falling when the USART is disabled, the use of an internal pull up is mandatory. If the hardware handshaking feature or Modem mode is used, the internal pull up on TXD must also be enabled.

All the pins of the modems may or may not be implemented on the USART. Only USART1 is fully equipped with all the modem signals. On USARTs not equipped with the corresponding pin, the associated control bits and statuses have no effect on the behavior of the USART.

## 31.5.2 Power Management

The USART is not continuously clocked. The programmer must first enable the USART Clock in the Power Management Controller (PMC) before using the USART. However, if the application does not require USART operations, the USART clock can be stopped when not needed and be restarted later. In this case, the USART will resume its operations where it left off.

Configuring the USART does not require the USART clock to be enabled.

## 31.5.3 Interrupt

The USART interrupt line is connected on one of the internal sources of the Advanced Interrupt Controller. Using the USART interrupt requires the AIC to be programmed first. Note that it is not recommended to use the USART interrupt line in edge sensitive mode.

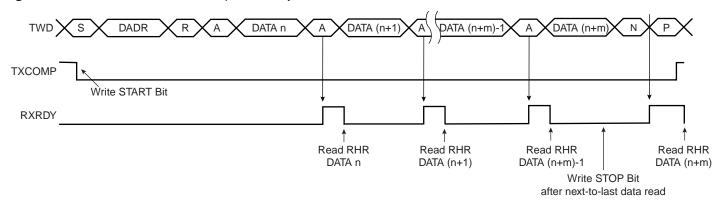

## 31.6.3.5 Parity

The USART supports five parity modes selected by programming the PAR field in the Mode Register (US\_MR). The PAR field also enables the Multidrop mode, see "Multidrop Mode" on page 374. Even and odd parity bit generation and error detection are supported.

If even parity is selected, the parity generator of the transmitter drives the parity bit at 0 if a number of 1s in the character data bit is even, and at 1 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If odd parity is selected, the parity generator of the transmitter drives the parity bit at 1 if a number of 1s in the character data bit is even, and at 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit at 1 if a number of 1s in the character data bit is even, and at 0 if the number of 1s is odd. Accordingly, the receiver parity checker counts the number of received 1s and reports a parity error if the sampled parity bit does not correspond. If the mark parity is used, the parity generator of the transmitter drives the parity bit at 1 for all characters. The receiver parity checker reports an error if the parity bit is sampled at 0. If the space parity is used, the parity generator of the transmitter drives the parity bit at 0 for all characters. The receiver parity checker reports an error if the parity bit is sampled at 1. If parity is disabled, the transmitter does not generate any parity bit and the receiver does not report any parity error.

Table 31-6 shows an example of the parity bit for the character 0x41 (character ASCII "A") depending on the configuration of the USART. Because there are two bits at 1, 1 bit is added when a parity is odd, or 0 is added when a parity is even.

| Character | Hexa | Binary    | Parity Bit | Parity Mode |

|-----------|------|-----------|------------|-------------|

| A         | 0x41 | 0100 0001 | 1          | Odd         |

| A         | 0x41 | 0100 0001 | 0          | Even        |

| А         | 0x41 | 0100 0001 | 1          | Mark        |

| А         | 0x41 | 0100 0001 | 0          | Space       |

| A         | 0x41 | 0100 0001 | None       | None        |

**Table 31-6.**Parity Bit Examples

When the receiver detects a parity error, it sets the PARE (Parity Error) bit in the Channel Status Register (US\_CSR). The PARE bit can be cleared by writing the Control Register (US\_CR) with the RSTSTA bit at 1. Figure 31-14 illustrates the parity bit status setting and clearing.

## Figure 31-14. Parity Error

## 31.7.4 USART Interrupt Disable Register

| Name:        | US_IDR   |      |        |        |                      |                      |                     |

|--------------|----------|------|--------|--------|----------------------|----------------------|---------------------|

| Access Type: | Write-or | nly  |        |        |                      |                      |                     |

| 31           | 30       | 29   | 28     | 27     | 26                   | 25                   | 24                  |

| -            | -        | —    | -      | —      | -                    | -                    | -                   |

| 23           | 22       | 21   | 20     | 19     | 18                   | 17                   | 16                  |

| —            | —        | —    | -      | CTSIC  | DCDIC <sup>(1)</sup> | DSRIC <sup>(1)</sup> | RIIC <sup>(1)</sup> |

| 15           | 14       | 13   | 12     | 11     | 10                   | 9                    | 8                   |

| -            | -        | NACK | RXBUFF | TXBUFE | ITERATION            | TXEMPTY              | TIMEOUT             |

| 7            | 6        | 5    | 4      | 3      | 2                    | 1                    | 0                   |

| PARE         | FRAME    | OVRE | ENDTX  | ENDRX  | RXBRK                | TXRDY                | RXRDY               |

Note: 1. DCDIC, DSRIC and RIIC do not pertain to the SAM7S32/16.

- RXRDY: RXRDY Interrupt Disable

- TXRDY: TXRDY Interrupt Disable

- RXBRK: Receiver Break Interrupt Disable

- ENDRX: End of Receive Transfer Interrupt Disable

- ENDTX: End of Transmit Interrupt Disable

- OVRE: Overrun Error Interrupt Disable

- FRAME: Framing Error Interrupt Disable

- PARE: Parity Error Interrupt Disable

- TIMEOUT: Time-out Interrupt Disable

- TXEMPTY: TXEMPTY Interrupt Disable

- ITERATION: Iteration Interrupt Disable

- TXBUFE: Buffer Empty Interrupt Disable

- RXBUFF: Buffer Full Interrupt Disable

- NACK: Non Acknowledge Interrupt Disable

- RIIC: Ring Indicator Input Change Disable

- DSRIC: Data Set Ready Input Change Disable

- DCDIC: Data Carrier Detect Input Change Interrupt Disable

- CTSIC: Clear to Send Input Change Interrupt Disable

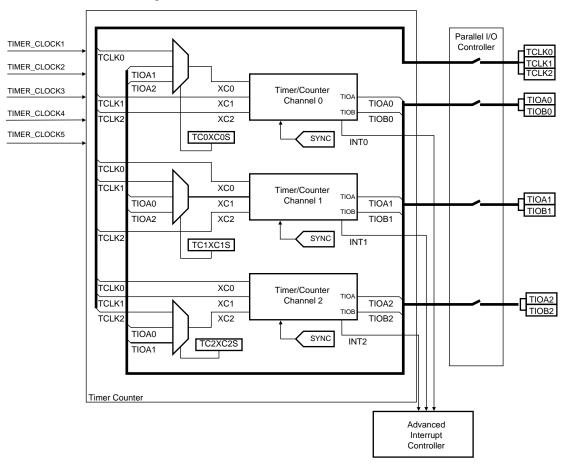

## 33.2 Block Diagram

Figure 33-1. Timer Counter Block Diagram

Table 33-2.

Signal Name Description

| Block/Channel  | Signal Name   | Description                                                                    |

|----------------|---------------|--------------------------------------------------------------------------------|

|                | XC0, XC1, XC2 | External Clock Inputs                                                          |

|                | ΤΙΟΑ          | Capture Mode: Timer Counter Input<br>Waveform Mode: Timer Counter Output       |

| Channel Signal | TIOB          | Capture Mode: Timer Counter Input<br>Waveform Mode: Timer Counter Input/Output |

|                | INT           | Interrupt Signal Output                                                        |

|                | SYNC          | Synchronization Input Signal                                                   |

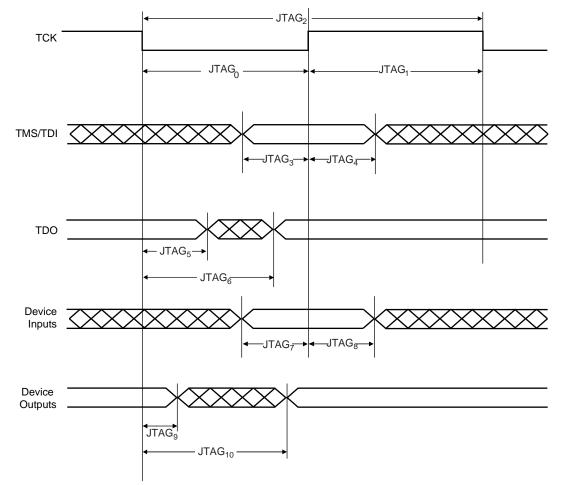

## 37.10.4.2 JTAG Interface Signals

| Symbol             | Parameter                      | Conditions | Min | Max | Units |

|--------------------|--------------------------------|------------|-----|-----|-------|

| JTAG <sub>0</sub>  | TCK Low Half-period            | (1)        | 6.5 |     | ns    |

| JTAG <sub>1</sub>  | TCK High Half-period           | (1)        | 5.5 |     | ns    |

| JTAG <sub>2</sub>  | TCK Period                     | (1)        | 12  |     | ns    |

| JTAG <sub>3</sub>  | TDI, TMS Setup before TCK High | (1)        | 2   |     | ns    |

| JTAG <sub>4</sub>  | TDI, TMS Hold after TCK High   | (1)        | 3   |     | ns    |

| JTAG <sub>5</sub>  | TDO Hold Time                  | (1)        | 4   |     | ns    |

| JTAG <sub>6</sub>  | TCK Low to TDO Valid           | (1)        |     | 16  | ns    |

| JTAG <sub>7</sub>  | Device Inputs Setup Time       | (1)        | 0   |     | ns    |

| JTAG <sub>8</sub>  | Device Inputs Hold Time        | (1)        | 3   |     | ns    |

| JTAG <sub>9</sub>  | Device Outputs Hold Time       | (1)        | 6   |     | ns    |

| JTAG <sub>10</sub> | TCK to Device Outputs Valid    | (1)        |     | 18  | ns    |

## Table 37-27. JTAG Interface Timing Specification

Note: 1. V<sub>VDDIO</sub> from 3.0V to 3.6V, maximum external capacitor = 40pF

## Figure 37-18. JTAG Interface Signals

## 40.18.6.3 SPI: Bad tx\_ready behavior when CSAAT=1 and SCBR = 1

If the SPI is programmed with CSAAT = 1, SCBR(baudrate) = 1 and two transfers are performed consecutively on the same slave with an IDLE state between them, the tx\_ready signal does not rise after the second data has been transferred in the shifter. This can imply for example, that the second data is sent twice.

## **Problem Fix/Workaround**

Do not use the combination CSAAT=1 and SCBR =1.

## 40.18.6.4 SPI: LASTXFER (Last Transfer) behavior

In FIXED Mode, with CSAAT bit set, and in "PDC mode" the Chip Select can rise depending on the data written in the SPI\_TDR when the TX\_EMPTY flag is set. If for example, the PDC writes a "1" in the bit 24 (LASTXFER bit) of the SPI\_TDR, the chip select will rise as soon as the TXEMPTY flag is set.

## **Problem Fix/Workaround**

Use the CS in PIO mode when PDC mode is required and CS has to be maintained between transfers.

## 40.18.6.5 SPI: SPCK Behavior in Master Mode

SPCK pin can toggle out before the first transfer in Master Mode.

## **Problem Fix/Workaround**

In Master Mode, MSTR bit must be set (in SPI\_MR register) before configuring SPI\_CSRx registers.

## 40.18.6.6 SPI: Chip Select and Fixed Mode

In fixed Mode, if a transfer is performed through a PDC on a Chip select different from the Chip select 0, the output spi\_size sampled by the PDC will depend on the field, BITS (Bits per Transfer) of SPI\_CSR0 register, whatever the selected Chip select is. For example, if SPI\_CSR0 is configured for a 10-bit transfer whereas SPI\_CSR1 is configured for an 8-bit transfer, when a transfer is performed in Fixed mode through the PDC, on Chip select 1, the transfer will be considered as a HalfWord transfer.

#### Problem Fix/Workaround

If a PDC transfer has to be performed in 8 bits, on a Chip select y (y as different from 0), the BITS field of the SPI\_CSR0 must be configured in 8 bits, in the same way as the BITS field of the CSRy Register.

#### 40.18.6.7 SPI: Baudrate Set to 1

When Baudrate is set at 1 (i.e. when serial clock frequency equals the system clock frequency) and when the BITS field of the SPI\_CSR register (number of bits to be transmitted) equals an ODD value (in this case 9,11,13 or 15), an additional pulse will be generated on output SPCK.

Everything is OK if the BITS field equals 8,10,12,14 or 16 and Baudrate = 1.

## **Problem Fix/Workaround**

None.

40.18.6.8 SPI: Disable In Slave Mode

The SPI disable is not possible in slave mode.

#### **Problem Fix/Workaround**

Read first the received data, then perform the software reset.

## 40.18.6.9 SPI: Disable Issue

The SPI Command "SPI Disable" is not possible during a transfer, it must be performed only after TX\_EMPTY rising else there is everlasting dummy transfers occur.

## Problem Fix/Workaround

- GOVRE inactive,

- previous data stored in LCDR being neither data from channel "y", nor data from channel "x".

GOVRE should be set but is not.

## **Problem Fix/Workaround**

None

## 40.20.1.7 ADC: GOVRE Bit is not Set when Disabling a Channel

When disabling channel "y" at the same instant as an end of conversion on channel "x", EOC[x] and DRDY being already active, GOVRE does not rise.

Note: OVRE[x] rises as expected.

## Problem Fix/Workaround

None

## 40.20.1.8 ADC: OVRE Flag Behavior

When the OVRE flag (on channel i) has been set but the related EOC status (of channel i) has been cleared (by a read of CDRi or LCDR), reading the Status register at the same instant as an end of conversion (causing the set of EOC status on channel i), does not lead to a reset of the OVRE flag (on channel i) as expected.

Problem Fix/Workaround:

None

## 40.20.1.9 ADC: EOC Set although Channel Disabled

If a channel is disabled while a conversion is running and if a read of CDR is performed at the same time as an end of conversion of any channel occurs, the EOC of the channel with the conversion running may rise (whereas it has been disabled).

## **Problem Fix/Workaround**

Do not take into account the EOC of a disabled channel

## 40.20.1.10 ADC: Spurious Clear of EOC Flag

If "x" and "y" are two successively converted channels and "z" is yet another enabled channel ("z" being neither "x" nor "y"), reading CDR on channel "z" at the same instant as an end of conversion on channel "y" automatically clears EOC[x] instead of EOC[z].

#### **Problem Fix/Workaround**

None.

## 40.20.1.11 ADC: Sleep Mode

If Sleep mode is activated while there is no activity (no conversion is being performed), it will take effect only after a conversion occurs.

## Problem Fix/Workaround

To activate sleep mode as soon as possible, it is recommended to write successively, ADC Mode Register (SLEEP) then ADC Control Register (START bit field); to start an analog-to-digital conversion, in order put ADC into sleep mode at the end of this conversion.

## 40.22.4 Pulse Width Modulation Controller (PWM)

## 40.22.4.1 PWM: Update when PWM\_CCNTx = 0 or 1

If the Channel Counter Register value is 0 or 1, the Channel Period Register or Channel Duty Cycle Register is directly modified when writing the Channel Update Register.

## Problem Fix/Workaround

Check the Channel Counter Register before writing the update register.

40.22.4.2 PWM: Update when PWM\_CPRDx = 0

When Channel Period Register equals 0, the period update is not operational.

## **Problem Fix/Workaround**

Do not write 0 in the period register.

## 40.22.4.3 PWM: Counter Start Value

In left aligned mode, the first start value of the counter is 0. For the other periods, the counter starts at 1.

## Problem Fix/Workaround

None.

## 40.22.4.4 PWM: Constraints on Duty Cycle Value

Setting Channel Duty Cycle Register (PWM\_CDTYx) at 0 in center aligned mode or at 0 or 1 in left aligned mode may change the polarity of the signal.

## **Problem Fix/Workaround**

Do not set PWM\_CDTYx at 0 in center aligned mode.

Do not set PWM\_CDTYx at 0 or 1 in left aligned mode.

## 40.22.4.5 PWM: Behavior of CHIDx Status Bits in the PWM\_SR Register

Erratic behavior of the CHIDx status bit in the PWM\_SR Register. When a channel is disabled by writing in the PWM\_DIS Register just after enabling it (before completion of a Clock Period of the clock selected for the channel), the PWM line is internally disabled but the CHIDx status bit in the PWM\_SR stays at 1.

## **Problem Fix/Workaround**

Do not disable a channel before completion of one period of the selected clock.

## 40.22.5 Real Time Timer (RTT)

#### 40.22.5.1 RTT: Possible Event Loss when Reading RTT\_SR

If an event (RTTINC or ALMS) occurs within the same slow clock cycle during which the RTT\_SR is read, the corresponding bit might be cleared. This can lead to the loss of this event.

#### **Problem Fix/Workaround:**

The software must handle the RTT event as an interrupt and should not poll RTT\_SR.

## 40.22.6 Serial Peripheral Interface (SPI)

#### 40.22.6.1 20. SPI: Pulse Generation on SPCK

In Master Mode, there is an additional pulse generated on SPCK when the SPI is configured as follows:

- The Baudrate is odd and different from 1

- The Polarity is set to 1

- The Phase is set to 0

| Version<br>6175H | Comments (Continued)                                                                              | Change<br>Request<br>Ref. |

|------------------|---------------------------------------------------------------------------------------------------|---------------------------|

|                  | All AT91SAM7S:                                                                                    |                           |

|                  | "Analog-to-Digital Converter (ADC)", errata applies to all AT91SAM7S products.                    | 4752                      |

|                  | "USART: DCD is active High instead of Low", errata applies to all AT91SAM7S products.             |                           |

|                  | "SPI: Bad Serial Clock Generation on 2nd Chip Select", errata applies to all AT91SAM7S products.  |                           |

|                  | "SPI: Bad Behavior when CSAAT = 1 and SCBR = 1", errata applies to all AT91SAM7S products.        | rfo                       |

|                  | AT91SAM7S256 Mfg # 58818C, AT91SAM7S256 Parts.A, AT91SAM7S128 Mfg # 58818C, AT91SAM7S128 Parts A, |                           |

|                  | added the following:                                                                              |                           |

|                  | Section 40.6.14.2 "WDT: The Watchdog Timer Status Register and Interrupt"                         | 3811                      |

|                  | Section 40.7.13.2 "WDT: The Watchdog Timer Status Register and Interrupt"                         |                           |

|                  | Section 40.11.14.2 "WDT: The Watchdog Timer Status Register and Interrupt"                        |                           |

|                  | Section 40.12.13.2 "WDT: The Watchdog Timer Status Register and Interrupt"                        |                           |

|                  | AT91SAM7S512 Section 40.4.9.1 "USART: CTS in Hardware Handshaking" updated                        | 3954                      |

|                  | AT91SAM7S512/256/128, added the following: (and in newly added "B Parts")                         |                           |

|                  | Section 40.4.9.4 "USART: RXBRK Flag Error in Asynchronous Mode"                                   |                           |

|                  | Section 40.6.12.4 "USART: RXBRK Flag Error in Asynchronous Mode"                                  | 4646                      |

|                  | Section 40.11.12.4 "USART: RXBRK Flag Error in Asynchronous Mode"                                 |                           |

|                  | Section 40.12.11.4 "USART: RXBRK Flag Error in Asynchronous Mode"                                 |                           |

| Version<br>6175G | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Change<br>Request<br>Ref. |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|                  | Added note to "Description" on page 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3442                      |

|                  | TC: added Figure 32-2 "Clock Chaining Selection" page 393                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3342                      |

|                  | SAM-BA Boot: Section 21.5.3 "USB Device Port" reference to INF example and lit°6123 removed. (Doc no longer available on web.)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 3647                      |

|                  | UDP: Table 35-2, "USB Communication Flow", Isochronous supported endpoint size is 64.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3475                      |

|                  | Errata: items added to the Errata Sections listed below.<br>Section 40.6 "SAM7S256 Errata - Manufacturing Number 58818C"<br>Section 40.7 "SAM7S256 Errata - Revision A Parts"<br>Section 40.11 "SAM7S128 Errata - Manufacturing Number 58818C"<br>Section 40.12 "SAM7S128 Errata - Revision A Parts"<br>Watchdog Timer: "The Watchdog Timer May Lock the Device in a Reset State"<br>Real-time Timer: "RTT_VR May be Corrupted"<br>Power Management Controller: "Slow Clock Selected in PMC and a Transition Occurs on PA1" and<br>"Programming CSS in PMC_MCKR Register" | 3652                      |