Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | ARM7®                                                                          |

| Core Size                  | 16/32-Bit                                                                      |

| Speed                      | 55MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, SSC, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                                  |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-LQFP                                                                        |

| Supplier Device Package    | 64-LQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7s256d-au-999 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 64-lead LQFP and 64-pad QFN Pinout 4.2

|       |                                                                   |  |    |               | - |    |             | - |  |

|-------|-------------------------------------------------------------------|--|----|---------------|---|----|-------------|---|--|

| 1     | ADVREF                                                            |  | 17 | GND           |   | 33 | TDI         |   |  |

| 2     | GND                                                               |  | 18 | VDDIO         |   | 34 | PA6/PGMNOE  |   |  |

| 3     | AD4                                                               |  | 19 | PA16/PGMD4    |   | 35 | PA5/PGMRDY  |   |  |

| 4     | AD5                                                               |  | 20 | PA15/PGMD3    |   | 36 | PA4/PGMNCMD |   |  |

| 5     | AD6                                                               |  | 21 | PA14/PGMD2    |   | 37 | PA27/PGMD15 |   |  |

| 6     | AD7                                                               |  | 22 | PA13/PGMD1    |   | 38 | PA28        |   |  |

| 7     | VDDIN                                                             |  | 23 | PA24/PGMD12   |   | 39 | NRST        |   |  |

| 8     | VDDOUT                                                            |  | 24 | VDDCORE       |   | 40 | TST         |   |  |

| 9     | PA17/PGMD5/AD0                                                    |  | 25 | PA25/PGMD13   |   | 41 | PA29        |   |  |

| 10    | PA18/PGMD6/AD1                                                    |  | 26 | PA26/PGMD14   |   | 42 | PA30        |   |  |

| 11    | PA21/PGMD9                                                        |  | 27 | PA12/PGMD0    |   | 43 | PA3         |   |  |

| 12    | VDDCORE                                                           |  | 28 | PA11/PGMM3    |   | 44 | PA2/PGMEN2  |   |  |

| 13    | PA19/PGMD7/AD2                                                    |  | 29 | PA10/PGMM2    |   | 45 | VDDIO       |   |  |

| 14    | PA22/PGMD10                                                       |  | 30 | PA9/PGMM1     |   | 46 | GND         |   |  |

| 15    | PA23/PGMD11                                                       |  | 31 | PA8/PGMM0     |   | 47 | PA1/PGMEN1  |   |  |

| 16    | PA20/PGMD8/AD3                                                    |  | 32 | PA7/PGMNVALID |   | 48 | PA0/PGMEN0  |   |  |

| Note: | 1. The bottom pad of the QFN package must be connected to ground. |  |    |               |   |    |             |   |  |

#### Table 4-1. SAM7S512/256/128/64/321/161 Pinout<sup>(1)</sup>

Note: 1. The bottom pad of the QFN package must be connected to ground.

**Atmel**

49

50

51

52

53

54

55

56 57

58

59

60

61

62

63

64

TDO

JTAGSEL

TMS

PA31

тск

VDDCORE

ERASE DDM

DDP

VDDIO

VDDFLASH

GND

XOUT

XIN/PGMCK

PLLRC

VDDPLL

## 4.3 48-lead LQFP and 48-pad QFN Package Outlines

Figure 4-3 and Figure 4-4 show the orientation of the 48-lead LQFP and the 48-pad QFN package. A detailed mechanical description is given in the section Mechanical Characteristics of the full datasheet.

#### Figure 4-3. 48-lead LQFP Package (Top View)

Figure 4-4. 48-pad QFN Package (Top View)

## 4.4 48-lead LQFP and 48-pad QFN Pinout

| Table 4 | -2. SAWI7552/10 FI | iout |               |   |    |             |   |    |           |

|---------|--------------------|------|---------------|---|----|-------------|---|----|-----------|

| 1       | ADVREF             | 13   | VDDIO         |   | 25 | TDI         |   | 37 | TDO       |

| 2       | GND                | 14   | PA16/PGMD4    |   | 26 | PA6/PGMNOE  |   | 38 | JTAGSEL   |

| 3       | AD4                | 15   | PA15/PGMD3    | Ĩ | 27 | PA5/PGMRDY  |   | 39 | TMS       |

| 4       | AD5                | 16   | PA14/PGMD2    | 1 | 28 | PA4/PGMNCMD |   | 40 | TCK       |

| 5       | AD6                | 17   | PA13/PGMD1    | 1 | 29 | NRST        |   | 41 | VDDCORE   |

| 6       | AD7                | 18   | VDDCORE       | 1 | 30 | TST         |   | 42 | ERASE     |

| 7       | VDDIN              | 19   | PA12/PGMD0    | Ĩ | 31 | PA3         |   | 43 | VDDFLASH  |

| 8       | VDDOUT             | 20   | PA11/PGMM3    | Ĩ | 32 | PA2/PGMEN2  |   | 44 | GND       |

| 9       | PA17/PGMD5/AD0     | 21   | PA10/PGMM2    | 1 | 33 | VDDIO       |   | 45 | XOUT      |

| 10      | PA18/PGMD6/AD1     | 22   | PA9/PGMM1     | 1 | 34 | GND         |   | 46 | XIN/PGMCK |

| 11      | PA19/PGMD7/AD2     | 23   | PA8/PGMM0     | Ī | 35 | PA1/PGMEN1  | ] | 47 | PLLRC     |

| 12      | PA20/AD3           | 24   | PA7/PGMNVALID | Ī | 36 | PA0/PGMEN0  | ] | 48 | VDDPLL    |

Table 4-2.SAM7S32/16 Pinout<sup>(1)</sup>

Note: 1. The bottom pad of the QFN package must be connected to ground.

# Atmel

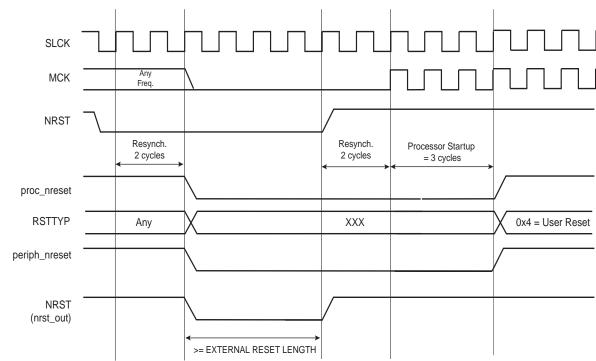

#### 13.3.4.2 User Reset

The User Reset is entered when a low level is detected on the NRST pin and the bit URSTEN in RSTC\_MR is at 1. The NRST input signal is resynchronized with SLCK to insure proper behavior of the system.

The User Reset is entered as soon as a low level is detected on NRST. The Processor Reset and the Peripheral Reset are asserted.

The User Reset is left when NRST rises, after a two-cycle resynchronization time and a three-cycle processor startup. The processor clock is re-enabled as soon as NRST is confirmed high.

When the processor reset signal is released, the RSTTYP field of the Status Register (RSTC\_SR) is loaded with the value 0x4, indicating a User Reset.

The NRST Manager guarantees that the NRST line is asserted for EXTERNAL\_RESET\_LENGTH Slow Clock cycles, as programmed in the field ERSTL. However, if NRST does not rise after EXTERNAL\_RESET\_LENGTH because it is driven low externally, the internal reset lines remain asserted until NRST actually rises.

Figure 13-5. User Reset State

• When the bit is set, the bit FRDY in the Flash Programming Status Register (MC\_FSR) rises. If an interrupt has been enabled by setting the bit FRDY in MC\_FMR, the interrupt line of the Memory Controller is activated.

Two errors can be detected in the MC\_FSR register after a programming sequence:

- Programming Error: A bad keyword and/or an invalid command have been written in the MC\_FCR register

- If the general-purpose bit number is greater than the total number of general-purpose bits, then the command has no effect.

It is possible to deactivate a general-purpose NVM bit set previously. The clear sequence is:

- Start the Clear General-purpose Bit command (CGPB) by writing the Flash Command Register with CGPB and the number of the general-purpose bit to be cleared in the PAGEN field.

- When the clear completes, the bit FRDY in the Flash Programming Status Register (MC\_FSR) rises. If an interrupt has been enabled by setting the bit FRDY in MC\_FMR, the interrupt line of the Memory Controller is activated.

Two errors can be detected in the MC\_FSR register after a programming sequence:

- Programming Error: a bad keyword and/or an invalid command have been written in the MC\_FCR register

- If the number of the general-purpose bit set in the PAGEN field is greater than the total number of generalpurpose bits, then the command has no effect.

The Clear General-purpose Bit command programs the general-purpose NVM bit to 0; the corresponding bit GPNVM0 to GPNVMx in MC\_FSR reads 0. The Set General-purpose Bit command programs the general-purpose NVM bit to 1; the corresponding bit GPNVMx in MC\_FSR reads 1.

Note: Access to the Flash in read mode is permitted when a Set, Clear or Get General-purpose NVM Bit command is performed.

#### 19.2.4.5 Security Bit

The goal of the security bit is to prevent external access to the internal bus system. (Does not apply to EFC1 on theSAM7S512.) JTAG, Fast Flash Programming and Flash Serial Test Interface features are disabled. Once set, this bit can be reset only by an external hardware ERASE request to the chip. Refer to the product definition section for the pin name that controls the ERASE. In this case, the full memory plane is erased and all lock and general-purpose NVM bits are cleared. The security bit in the MC\_FSR is cleared only after these operations. The activation sequence is:

- Start the Set Security Bit command (SSB) by writing the Flash Command Register.

- When the locking completes, the bit FRDY in the Flash Programming Status Register (MC\_FSR) rises. If an interrupt has been enabled by setting the bit FRDY in MC\_FMR, the interrupt line of the Memory Controller is activated.

When the security bit is active, the SECURITY bit in the MC\_FSR is set.

#### 20.2.2 Signal Names

Depending on the MODE settings, DATA is latched in different internal registers.

| MODE[3:0] | Symbol | Data                  |  |  |  |

|-----------|--------|-----------------------|--|--|--|

| 0000      | CMDE   | Command Register      |  |  |  |

| 0001      | ADDR0  | Address Register LSBs |  |  |  |

| 0010      | ADDR1  |                       |  |  |  |

| 0011      | ADDR2  |                       |  |  |  |

| 0100      | ADDR3  | Address Register MSBs |  |  |  |

| 0101      | DATA   | Data Register         |  |  |  |

| Default   | IDLE   | No register           |  |  |  |

Table 20-2. Mode Coding

When MODE is equal to CMDE, then a new command (strobed on DATA[15:0] or DATA[7:0] signals) is stored in the command register.

Note: DATA[7:0] pertains to the SAM7S32/16.

| DATA[15:0]<br>DATA[7:0] <sup>(1)</sup> | Symbol | Command Executed                     |

|----------------------------------------|--------|--------------------------------------|

|                                        |        |                                      |

| 0x0011                                 | READ   | Read Flash                           |

| 0x0012                                 | WP     | Write Page Flash                     |

| 0x0022                                 | WPL    | Write Page and Lock Flash            |

| 0x0032                                 | EWP    | Erase Page and Write Page            |

| 0x0042                                 | EWPL   | Erase Page and Write Page then Lock  |

| 0x0013                                 | EA     | Erase All                            |

| 0x0014                                 | SLB    | Set Lock Bit                         |

| 0x0024                                 | CLB    | Clear Lock Bit                       |

| 0x0015                                 | GLB    | Get Lock Bit                         |

| 0x0034                                 | SGPB   | Set General Purpose NVM bit          |

| 0x0044                                 | CGPB   | Clear General Purpose NVM bit        |

| 0x0025                                 | GGPB   | Get General Purpose NVM bit          |

| 0x0054                                 | SSE    | Set Security Bit                     |

| 0x0035                                 | GSE    | Get Security Bit                     |

| 0x001F                                 | WRAM   | Write Memory                         |

| 0x0016                                 | SEFC   | Select EFC Controller <sup>(2)</sup> |

| 0x001E                                 | GVE    | Get Version                          |

| Table 20-3. | Command Bit Coding |

|-------------|--------------------|

|-------------|--------------------|

Notes: 1. DATA[7:0] pertains to the SAM7S32/16.

2. Applies to SAM7S512.

#### 22.4.7 PDC Transmit Next Pointer Register

| Register Name: | PERIPH_TNPR |    |        |    |    |    |    |

|----------------|-------------|----|--------|----|----|----|----|

| Access Type:   | Read-write  |    |        |    |    |    |    |

| 31             | 30          | 29 | 28     | 27 | 26 | 25 | 24 |

|                | TXNPTR      |    |        |    |    |    |    |

| 23             | 22          | 21 | 20     | 19 | 18 | 17 | 16 |

|                |             |    | TXNPTR |    |    |    |    |

| 15             | 14          | 13 | 12     | 11 | 10 | 9  | 8  |

|                | TXNPTR      |    |        |    |    |    |    |

| 7              | 6           | 5  | 4      | 3  | 2  | 1  | 0  |

|                | TXNPTR      |    |        |    |    |    |    |

#### • TXNPTR: Transmit Next Pointer Address

TXNPTR is the address of the next buffer to transmit when the current buffer is empty.

#### 22.4.8 PDC Transmit Next Counter Register

| Register Name: | PERIPH_TNCR |      |    |    |    |    |    |

|----------------|-------------|------|----|----|----|----|----|

| Access Type:   | Read-w      | rite |    |    |    |    |    |

| 31             | 30          | 29   | 28 | 27 | 26 | 25 | 24 |

|                |             |      |    |    |    |    |    |

| 23             | 22          | 21   | 20 | 19 | 18 | 17 | 16 |

|                |             |      |    | -  |    |    |    |

| 15             | 14          | 13   | 12 | 11 | 10 | 9  | 8  |

| TXNCR          |             |      |    |    |    |    |    |

| 7              | 6           | 5    | 4  | 3  | 2  | 1  | 0  |

|                | TXNCR       |      |    |    |    |    |    |

#### • TXNCR: Transmit Next Counter Value

TXNCR is the size of the next buffer to transmit.

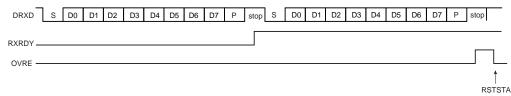

#### 26.4.2.4 Receiver Overrun

If DBGU\_RHR has not been read by the software (or the Peripheral Data Controller) since the last transfer, the RXRDY bit is still set and a new character is received, the OVRE status bit in DBGU\_SR is set. OVRE is cleared when the software writes the control register DBGU\_CR with the bit RSTSTA (Reset Status) at 1.

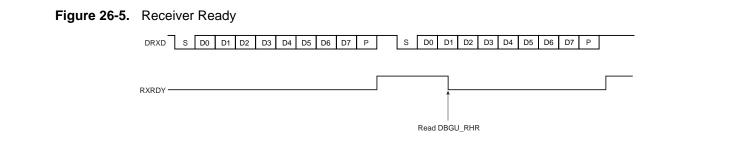

#### Figure 26-6. Receiver Overrun

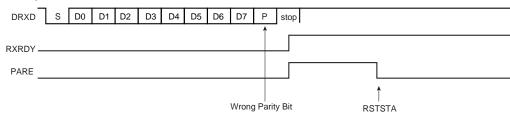

#### 26.4.2.5 Parity Error

Each time a character is received, the receiver calculates the parity of the received data bits, in accordance with the field PAR in DBGU\_MR. It then compares the result with the received parity bit. If different, the parity error bit PARE in DBGU\_SR is set at the same time the RXRDY is set. The parity bit is cleared when the control register DBGU\_CR is written with the bit RSTSTA (Reset Status) at 1. If a new character is received before the reset status command is written, the PARE bit remains at 1.

#### Figure 26-7. Parity Error

#### 26.4.2.6 Receiver Framing Error

When a start bit is detected, it generates a character reception when all the data bits have been sampled. The stop bit is also sampled and when it is detected at 0, the FRAME (Framing Error) bit in DBGU\_SR is set at the same time the RXRDY bit is set. The bit FRAME remains high until the control register DBGU\_CR is written with the bit RSTSTA at 1.

- EXT shows the use of the extension identifier register

- NVPTYP and NVPSIZ identifies the type of embedded non-volatile memory and its size

- ARCH identifies the set of embedded peripheral

- SRAMSIZ indicates the size of the embedded SRAM

- EPROC indicates the embedded ARM processor

- VERSION gives the revision of the silicon

The second register is device-dependent and reads 0 if the bit EXT is 0.

#### 26.4.8 ICE Access Prevention

The Debug Unit allows blockage of access to the system through the ARM processor's ICE interface. This feature is implemented via the register Force NTRST (DBGU\_FNR), that allows assertion of the NTRST signal of the ICE Interface. Writing the bit FNTRST (Force NTRST) to 1 in this register prevents any activity on the TAP controller.

On standard devices, the FNTRST bit resets to 0 and thus does not prevent ICE access.

This feature is especially useful on custom ROM devices for customers who do not want their on-chip code to be visible.

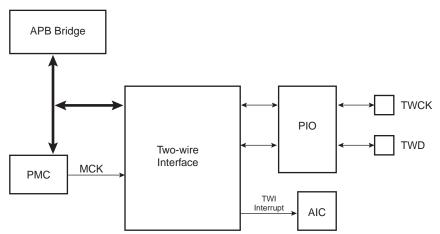

### 30.3 Block Diagram

Figure 30-1. Block Diagram

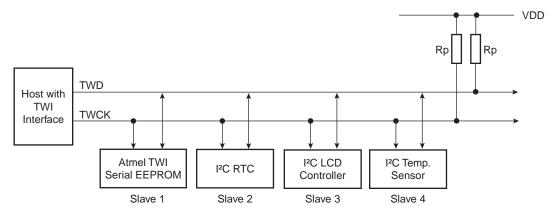

#### 30.4 Application Block Diagram

Rp: Pull up value as given by the I<sup>2</sup>C Standard

#### 30.4.1 I/O Lines Description

#### Table 30-3. I/O Lines Description

| Pin Name | Pin Description       | Туре         |

|----------|-----------------------|--------------|

| TWD      | Two-wire Serial Data  | Input/Output |

| ТѠСК     | Two-wire Serial Clock | Input/Output |

#### 30.5 Product Dependencies

#### 30.5.1 I/O Lines

Both TWD and TWCK are bidirectional lines, connected to a positive supply voltage via a current source or pull-up resistor (see Figure 30-2 on page 320). When the bus is free, both lines are high. The output stages of devices connected to the bus must have an open-drain or open-collector to perform the wired-AND function.

#### 33.5.11.4 WAVSEL = 11

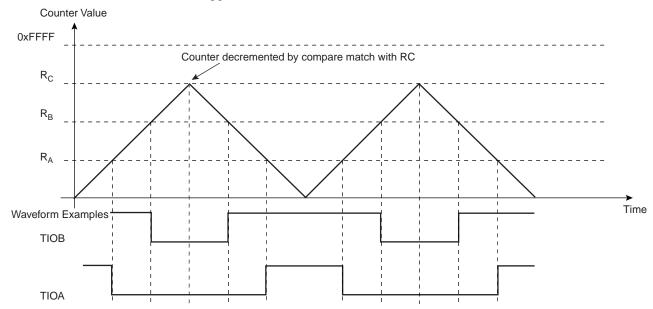

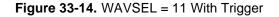

When WAVSEL = 11, the value of TC\_CV is incremented from 0 to RC. Once RC is reached, the value of TC\_CV is decremented to 0, then re-incremented to RC and so on. See Figure 33-13.

A trigger such as an external event or a software trigger can modify TC\_CV at any time. If a trigger occurs while TC\_CV is incrementing, TC\_CV then decrements. If a trigger is received while TC\_CV is decrementing, TC\_CV then increments. See Figure 33-14.

RC Compare can stop the counter clock (CPCSTOP = 1) and/or disable the counter clock (CPCDIS = 1).

Figure 33-13. WAVSEL = 11 Without Trigger

#### 34.6.8 PWM Interrupt Status Register

| Register Name | : PWM_I | -   |    |       |       |       |       |

|---------------|---------|-----|----|-------|-------|-------|-------|

| Access Type:  | Read-o  | nly |    |       |       |       |       |

| 31            | 30      | 29  | 28 | 27    | 26    | 25    | 24    |

| -             | _       | _   | -  | -     | -     | -     | -     |

| 23            | 22      | 21  | 20 | 19    | 18    | 17    | 16    |

| -             | _       | _   | -  | -     | -     | -     | _     |

| 15            | 14      | 13  | 12 | 11    | 10    | 9     | 8     |

| -             | -       | —   | -  | -     | -     | -     | -     |

| 7             | 6       | 5   | 4  | 3     | 2     | 1     | 0     |

| _             | _       | _   | -  | CHID3 | CHID2 | CHID1 | CHID0 |

#### • CHIDx: Channel ID

0 = No new channel period has been achieved since the last read of the PWM\_ISR register.

1 = At least one new channel period has been achieved since the last read of the PWM\_ISR register.

Note: Reading PWM\_ISR automatically clears CHIDx flags.

## Atmel

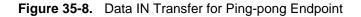

- 3. The microcontroller notifies the USB peripheral it has finished writing in Bank 0 of the FIFO by setting the TXPKTRDY in the endpoint's UDP\_ CSRx register.

- 4. Without waiting for TXPKTRDY to be cleared, the microcontroller writes the second data payload to be sent in the FIFO (Bank 1), writing zero or more byte values in the endpoint's UDP\_ FDRx register.

- 5. The microcontroller is notified that the first Bank has been released by the USB device when TXCOMP in the endpoint's UDP\_ CSRx register is set. An interrupt is pending while TXCOMP is being set.

- 6. Once the microcontroller has received TXCOMP for the first Bank, it notifies the USB device that it has prepared the second Bank to be sent, raising TXPKTRDY in the endpoint's UDP\_ CSRx register.

- 7. At this step, Bank 0 is available and the microcontroller can prepare a third data payload to be sent.

**Warning:** There is software critical path due to the fact that once the second bank is filled, the driver has to wait for TX\_COMP to set TX\_PKTRDY. If the delay between receiving TX\_COMP is set and TX\_PKTRDY is set too long, some Data IN packets may be NACKed, reducing the bandwidth.

**Warning:** TX\_COMP must be cleared after TX\_PKTRDY has been set.

#### 35.5.2.5 Data OUT Transaction

Data OUT transactions are used in control, isochronous, bulk and interrupt transfers and conduct the transfer of data from the host to the device. Data OUT transactions in isochronous transfers must be done using endpoints with ping-pong attributes.

#### 35.5.2.6 Data OUT Transaction Without Ping-pong Attributes

To perform a Data OUT transaction, using a non ping-pong endpoint:

- 1. The host generates a Data OUT packet.

- This packet is received by the USB device endpoint. While the FIFO associated to this endpoint is being used by the microcontroller, a NAK PID is returned to the host. Once the FIFO is available, data are written to the FIFO by the USB device and an ACK is automatically carried out to the host.

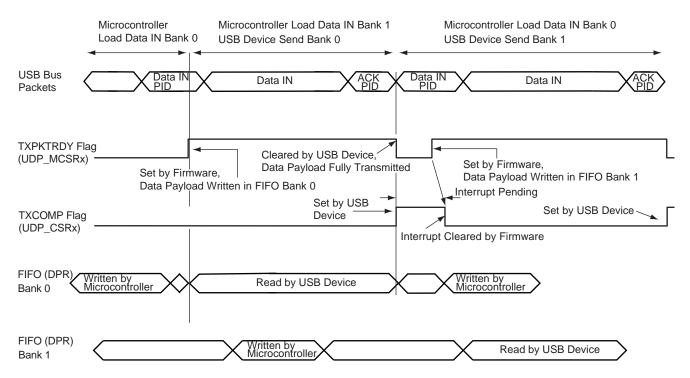

| Symbol                                         | Parameter                                   | Conditions  | Min                                           | Мах                                             | Units |

|------------------------------------------------|---------------------------------------------|-------------|-----------------------------------------------|-------------------------------------------------|-------|

| SSC <sub>7</sub> <sup>(1)</sup>                | TK addre to TF/TD (TK input TF input)       | 3.3V domain | 6 (+3*t <sub>СРМСК</sub> ) <sup>(1)(2)</sup>  | 29.5 (+3*t <sub>CPMCK</sub> ) <sup>(1)(2)</sup> | ns    |

| 55C7 <sup>(1)</sup>                            | TK edge to TF/TD (TK input, TF input)       | 1.8V domain | 10 (+3*t <sub>CPMCK</sub> ) <sup>(1)(2)</sup> | 56 (+3*t <sub>CPMCK</sub> ) <sup>(1)(2)</sup>   | ns    |

|                                                | •                                           | Receiver    |                                               | •                                               |       |

| 000                                            | DE/DD actum time before DK adre (DK input)  | 3.3V domain | 0                                             |                                                 | ns    |

| SSC <sub>8</sub> RF/RD setup time before RK ec | RF/RD setup time before RK edge (RK input)  | 1.8V domain | 0                                             |                                                 | ns    |

| 000                                            | DE/DD hold time ofter DK odro (DK innut)    | 3.3V domain | t <sub>CPMCK</sub>                            |                                                 | ns    |

| SSC <sub>9</sub> RF/RD hold time after F       | RF/RD hold time after RK edge (RK input)    | 1.8V domain | t <sub>CPMCK</sub>                            |                                                 | ns    |

|                                                |                                             | 3.3V domain | 6 <sup>(2)</sup>                              | 27 <sup>(2)</sup>                               | ns    |

| SSC <sub>10</sub>                              | RK edge to RF (RK input)                    | 1.8V domain | 10.5 <sup>(2)</sup>                           | 58 <sup>(2)</sup>                               | ns    |

| 000                                            |                                             | 3.3V domain | 26 - t <sub>СРМСК</sub>                       |                                                 | ns    |

| SSC <sub>11</sub>                              | RF/RD setup time before RK edge (RK output) | 1.8V domain | 56.5 - t <sub>СРМСК</sub>                     |                                                 | ns    |

| 000                                            |                                             | 3.3V domain | t <sub>CPMCK</sub> - 10                       |                                                 | ns    |

| SSC <sub>12</sub> F                            | RF/RD hold time after RK edge (RK output)   | 1.8V domain | t <sub>CPMCK</sub> - 5.5                      |                                                 | ns    |

| 000                                            |                                             | 3.3V domain | 0 <sup>(2)</sup>                              | 4 <sup>(2)</sup>                                | ns    |

| SSC <sub>13</sub>                              | RK edge to RF (RK output)                   | 1.8V domain | 0 <sup>(2)</sup>                              | 12 <sup>(2)</sup>                               | ns    |

Table 37-23. SSC Timings (Continued)

- Notes: 1. Timings SSC4 and SSC7 depend on the start condition. When STTDLY = 0 (Receive start delay) and START = 4, or 5 or 7 (Receive Start Selection), two Periods of the MCK must be added to timings.

- For output signals (TF, TD, RF), Min and Max access times are defined. The Min access time is the time between the TK (or RK) edge and the signal change. The Max access timing is the time between the TK edge and the signal stabilization. Figure 37-16 illustrates Min and Max accesses for SSC0. The same applies for SSC1, SSC4, and SSC7, SSC10 and SSC13.

- 3. 3.3V domain: V<sub>VDDIO</sub> from 3.0V to 3.6V, maximum external capacitor = 40 pF.

- 4. 1.8V domain: V<sub>VDDIO</sub> from 1.65V to 1.95V, maximum external capacitor = 20 pF.

- 5. t<sub>CPMCK</sub>: Master Clock period in ns

Figure 37-16. Min and Max access time of output signals

"SAM7S256 Errata - Revision B Parts" on page 634 "SAM7S256 Errata - Revision C Parts" on page 642 "SAM7S256 Errata - Revision D Parts" on page 644 "SAM7S128 Errata - Manufacturing Number 58818C" on page 646 "SAM7S128 Errata - Revision A Parts" on page 656 "SAM7S128 Errata - Revision B Parts" on page 666 "SAM7S128 Errata - Revision C Parts" on page 674 "SAM7S128 Errata - Revision D Parts" on page 676 "SAM7S64 Errata - Manufacturing Number 58814G" on page 678 "SAM7S64 Errata - Revision A Parts" on page 688 "SAM7S64 Errata - Revision B Parts" on page 697 "SAM7S64 Errata - Revision C Parts" on page 706 "SAM7S321 Errata - Revision A Parts" on page 708 "SAM7S32 Errata - Manufacturing Number 58814G" on page 716 "SAM7S32 Errata - Revision A Parts" on page 725 "SAM7S32 Errata - Revision B Parts" on page 734 "SAM7S161 Errata - Revision A Parts" on page 742 "SAM7S16 Errata - Revision A Parts" on page 747

This maximum number of write/erase cycles is not applicable to 256 KB Flash memory, it remains at 10K for the Flash memory.

Problem Fix/Workaround

None.

#### 40.8.3 Parallel Input/Output Controller (PIO)

40.8.3.1 PIO: Electrical Characteristics on NRST and PA0-PA16 and PA21-31

When NRST or PA0-PA16 or PA21-PA31 are set as digital inputs with pull-up enabled, the voltage of the I/O stabilizes at VPull-up.

Vpull-up

| VPull-up Min   | VPull-up Max   |

|----------------|----------------|

| VDDIO - 0.65 V | VDDIO - 0.45 V |

This condition causes a leakage through VDDIO. This leakage is 45  $\mu$ A per pad in worst case at 3.3 V and 25  $\mu$ A at 1.8V.

I Leakage

| Parameter         | Тур    | Max   |

|-------------------|--------|-------|

| I Leakage at 3,3V | 2.5 µA | 45 µA |

| I Leakage at 1.8V | 1 µA   | 25 µA |

#### **Problem Fix/Workaround**

It is recommended to use an external pull-up if needed.

#### 40.8.3.2 PIO: Drive Low NRST, PA0-PA16 and PA21-PA31

When NRST or PA0-PA16 and or PA21-PA31 are set as digital inputs with pull-up enabled, driving the I/O with an output impedance higher than 500 ohms may not drive the I/O to a logical zero.

#### Problem Fix/Workaround

Output impedance must be lower than 500 ohms.

#### 40.8.4 Pulse Width Modulation Controller (PWM)

#### 40.8.4.1 PWM: Update when PWM\_CCNTx = 0 or 1

If the Channel Counter Register value is 0 or 1, the Channel Period Register or Channel Duty Cycle Register is directly modified when writing the Channel Update Register.

#### Problem Fix/Workaround

Check the Channel Counter Register before writing the update register.

#### 40.8.4.2 PWM: Update when PWM\_CPRDx = 0

When Channel Period Register equals 0, the period update is not operational.

#### Problem Fix/Workaround

Do not write 0 in the period register.

#### 40.8.4.3 PWM: Counter Start Value

In left aligned mode, the first start value of the counter is 0. For the other periods, the counter starts at 1.

#### 40.11.11 Two-wire Interface (TWI)

#### 40.11.11.1 TWI: Clock Divider

The value of CLDIV x  $2^{CKDIV}$  must be less than or equal to 8191, the value of CHDIV x  $2^{CKDIV}$  must be less than or equal to 8191.

#### Problem Fix/Workaround

None.

#### 40.11.11.2 TWI: Software Reset

When a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

#### **Problem Fix/Workaround**

None.

#### 40.11.11.3 TWI: Disabling Does not Operate Correctly

Any transfer in progress is immediately frozen if the Control Register (TWI\_CR) is written with the bit MSDIS at 1. Furthermore, the status bits TXCOMP and TXRDY in the Status Register (TWI\_SR) are not reset.

#### **Problem Fix/Workaround**

The user must wait for the end of transfer before disabling the TWI. In addition, the interrupts must be disabled before disabling the TWI.

#### 40.11.11.4 TWI: NACK Status Bit Lost

During a master frame, if TWI\_SR is read between the Non Acknowledge condition detection and the TXCOMP bit rising in the TWI\_SR, the NACK bit is not set.

#### **Problem Fix/Workaround**

The user must wait for the TXCOMP status bit by interrupt and must not read the TWI\_SR as long as transmission is not completed.

TXCOMP and NACK fields are set simultaneously and the NACK field is reset after the read of the TWI\_SR.

None.

#### 40.13.9.4 USART: RXBRK Flag Error in Asynchronous Mode

In receiver mode, when there are two consecutive characters (without timeguard in between), RXBRK is not taken into account. As a result, the RXBRK flag is not enabled correctly and the frame error flag is set.

#### Problem Fix/Workaround

Constraints on the transmitter device connected to the SAM7S USART receiver side:

The transmitter may use the timeguard feature or send two STOP conditions. Only one STOP condition is taken into account by the receiver state machine. After this STOP condition, as there is no valid data, the receiver state machine will go in idle mode and enable the RXBRK flag.

#### 40.13.9.5 USART: DCD is active High instead of Low

The DCD signal is active at High level in the USART Modem Mode.

DCD should be active at Low level.

#### Problem Fix/Workaround

Add an inverter.

#### 40.13.10 Voltage Regulator

40.13.10.1 Voltage Regulator: Current Consumption in Deep Mode

Current consumption in Deep Mode is maximum 60  $\mu$ A instead of 25  $\mu$ A.

Due to current rejection from VDDIN to VDDCORE, the current consumption in Deep Mode cannot be guaranteed. Instead,  $60 \ \mu A$  is guaranteed whatever the condition.

#### Problem Fix/Workaround

None.

40.13.10.2 Voltage Regulator: Load Versus Temperature Maximum load is 50 mA at 85 °C (instead of 100 mA).

Maximum load is 100 mA at 70°C.

Problem Fix/Workaround

None.

selected Chip select is. For example, if SPI\_CSR0 is configured for a 10-bit transfer whereas SPI\_CSR1 is configured for an 8-bit transfer, when a transfer is performed in Fixed mode through the PDC, on Chip select 1, the transfer will be considered as a HalfWord transfer.

#### **Problem Fix/Workaround**

If a PDC transfer has to be performed in 8 bits, on a Chip select y (y as different from 0), the BITS field of the SPI\_CSR0 must be configured in 8 bits, in the same way as the BITS field of the CSRy Register.

#### 40.21.7.6 SPI: Baudrate Set to 1

When Baudrate is set at 1 (i.e. when serial clock frequency equals the system clock frequency) and when the BITS field of the SPI\_CSR register (number of bits to be transmitted) equals an ODD value (in this case 9,11,13 or 15), an additional pulse will be generated on output SPCK.

Everything is OK if the BITS field equals 8,10,12,14 or 16 and Baudrate = 1.

#### Problem Fix/Workaround

None.

#### 40.21.7.7 SPI: Disable In Slave Mode

The SPI disable is not possible in slave mode.

#### Problem Fix/Workaround

Read first the received data, then perform the software reset.

#### 40.21.7.8 SPI: Disable Issue

The SPI Command "SPI Disable" is not possible during a transfer, it must be performed only after TX\_EMPTY rising else there is everlasting dummy transfers occur.

#### Problem Fix/Workaround

None.

#### 40.21.7.9 SPI: Software Reset and SPIEN Bit

The SPI Command "software reset" does not reset the SPIEN config bit. Therefore rewriting an SPI enable command does not set TX\_READY, TX\_EMPTY flags.

#### Problem Fix/Workaround

Send SPI disable command after a software reset.

#### 40.21.7.10 SPI: CSAAT = 1 and Delay

If CSAAT = 1 for current access and there is no more TX request for a time greater than DLYBCT + DLYBCS, then if an access is requested on another slave, the NPCS bus switches from one CS to the one requested without DLYBCS. External Slaves may reach a contention on SPI\_MISO line for a short period.

#### **Problem Fix/Workaround**

Assert the Last Transfer Command (NPCS de-activation) for the last character of each slave.

#### 40.21.7.11 SPI: Bad Serial Clock Generation on 2nd Chip Select

Bad Serial clock generation on the 2nd chip select when SCBR = 1, CPOL = 1 and NCPHA = 0.

This occurs using SPI with the following conditions:

- Master Mode

- CPOL = 1 and NCPHA = 0

- Multiple chip selects are used with one transfer with Baud rate (SCBR) equal to 1 (i.e., when serial clock frequency equals the system clock frequency) and the other transfers set with SCBR are not equal to 1

### 40.22 SAM7S32 Errata - Revision A Parts

Refer to Section 40.1 "Marking" on page 595.

Note: AT91SAM7S32 Revision A chip ID is 0x2708 0340.

#### 40.22.1 Analog-to-Digital Converter (ADC)

#### 40.22.1.1 ADC: DRDY Bit Cleared

The DRDY Flag should be clear only after a read of ADC\_LCDR (Last Converted Data Register). A read of any ADC\_CDRx register (Channel Data Register) automatically clears the DRDY flag.

#### Problem Fix/Workaround:

None

#### 40.22.1.2 ADC: DRDY not Cleared on Disable

When reading LCDR at the same instant as an end of conversion, with DRDY already active, DRDY is kept active regardless of the enable status of the current channel. This sets DRDY, whereas new data is not stored.

#### **Problem Fix/Workaround**

None

#### 40.22.1.3 ADC: DRDY Possibly Skipped due to CDR Read

Reading CDR for channel "y" at the same instant as an end of conversion on channel "x" with EOC[x] already active, leads to skipping to set the DRDY flag if channel "x" is enabled.

#### **Problem Fix/Workaround**

Use of DRDY functionality with access to CDR registers should be avoided.

#### 40.22.1.4 ADC: Possible Skip on DRDY when Disabling a Channel

DRDY does not rise when disabling channel "y" at the same time as an end of "x" channel conversion, although data is stored into CDRx and LCDR.

#### Problem Fix/Workaround

None.

#### 40.22.1.5 ADC: GOVRE Bit is not Updated

Read of the Status Register at the same instant as an end of conversion leads to skipping the update of the GOVRE (general overrun) flag. GOVRE is neither reset nor set.

For example, if reading the status while an end of conversion is occurring and:

- 1. GOVRE is active but DRDY is inactive, does not correspond to a new general overrun condition but the GOVRE flag is not reset.

- 2. GOVRE is inactive but DRDY is active, does correspond to a new general overrun condition but the GOVRE flag is not set.

#### **Problem Fix/Workaround**

None

#### 40.22.1.6 ADC: GOVRE Bit is not Set when Reading CDR

When reading CDRy (Channel Data Register y) at the same instant as an end of conversion on channel "x" with the following conditions:

- EOC[x] already active,

- DRDY already active,

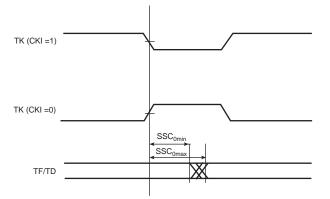

#### 40.24.6 Universal Synchronous Asynchronous Receiver Transmitter (USART)

#### 40.24.6.1 USART: DCD is active High instead of Low

The DCD signal is active at High level in the USART Modem Mode.

DCD should be active at Low level.

#### Problem Fix/Workaround

Add an inverter.