Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | ARM7®                                                                          |

| Core Size                  | 16/32-Bit                                                                      |

| Speed                      | 55MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, SPI, SSC, UART/USART, USB                                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 32                                                                             |

| Program Memory Size        | 256КВ (256К х 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 1.95V                                                                  |

| Data Converters            | A/D 8x10b                                                                      |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/at91sam7s256d-mu-999 |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• Programmable center or left aligned output waveform

# 10.11 USB Device Port (Does not pertain to SAM7S32/16)

- USB V2.0 full-speed compliant, 12 Mbits per second.

- Embedded USB V2.0 full-speed transceiver

- Embedded 328-byte dual-port RAM for endpoints

- Four endpoints

- Endpoint 0: 8 bytes

- Endpoint 1 and 2: 64 bytes ping-pong

- Endpoint 3: 64 bytes

- Ping-pong Mode (two memory banks) for isochronous and bulk endpoints

- Suspend/resume logic

## 10.12 Analog-to-digital Converter

- 8-channel ADC

- 10-bit 384 Ksamples/sec. or 8-bit 583 Ksamples/sec. Successive Approximation Register ADC

- ±2 LSB Integral Non Linearity, ±1 LSB Differential Non Linearity

- Integrated 8-to-1 multiplexer, offering eight independent 3.3V analog inputs

- External voltage reference for better accuracy on low voltage inputs

- Individual enable and disable of each channel

- Multiple trigger source

- Hardware or software trigger

- External trigger pin

- Timer Counter 0 to 2 outputs TIOA0 to TIOA2 trigger

- Sleep Mode and conversion sequencer

- Automatic wakeup on trigger and back to sleep mode after conversions of all enabled channels

- Four of eight analog inputs shared with digital signals

| (Continued) |

|-------------|

| 0x270A0741  |

| 0x270A0742  |

| 0x270A0743  |

| 0x270D0940  |

| 0x270B0941  |

| 0x270B0942  |

| 0x270B0943  |

| 0x270B0A40  |

| 0x270B0A4F  |

|             |

Table 12-2.

SAM7S Series Debug Unit Chip ID (Continued)

For further details on the Debug Unit, see the Debug Unit section.

#### 12.5.4 IEEE 1149.1 JTAG Boundary Scan

IEEE 1149.1 JTAG Boundary Scan allows pin-level access independent of the device packaging technology.

IEEE 1149.1 JTAG Boundary Scan is enabled when JTAGSEL is high. The SAMPLE, EXTEST and BYPASS functions are implemented. In ICE debug mode, the ARM processor responds with a non-JTAG chip ID that identifies the processor to the ICE system. This is not IEEE 1149.1 JTAG-compliant.

It is not possible to switch directly between JTAG and ICE operations. A chip reset must be performed after JTAG-SEL is changed.

A Boundary-scan Descriptor Language (BSDL) file is provided to set up testing.

#### 12.5.4.1 JTAG Boundary-scan Register

The Boundary-scan Register (BSR) contains 96 bits that correspond to active pins and associated control signals.

Each SAM7Sxx input/output pin corresponds to a 3-bit register in the BSR. The OUTPUT bit contains data that can be forced on the pad. The INPUT bit facilitates the observability of data applied to the pad. The CONTROL bit selects the direction of the pad.

| Bit Number | Pin Name       | Pin Type | Associated BSR<br>Cells |

|------------|----------------|----------|-------------------------|

| 96         |                |          | INPUT                   |

| 95         | PA17/PGMD5/AD0 | IN/OUT   | OUTPUT                  |

| 94         |                |          | CONTROL                 |

| 93         |                |          | INPUT                   |

| 92         | PA18/PGMD6/AD1 | IN/OUT   | OUTPUT                  |

| 91         |                |          | CONTROL                 |

| 90         |                |          | INPUT <sup>(1)</sup>    |

| 89         | PA21/PGMD9*    | IN/OUT*  | OUTPUT <sup>(1)</sup>   |

| 88         |                |          | CONTROL <sup>(1)</sup>  |

Table 12-3.

SAM7Sxx JTAG Boundary Scan Register

#### 13.3.5 Reset State Priorities

The Reset State Manager manages the following priorities between the different reset sources, given in descending order:

- Power-up Reset

- Brownout Reset

- Watchdog Reset

- Software Reset

- User Reset

Particular cases are listed below:

- When in User Reset:

- A watchdog event is impossible because the Watchdog Timer is being reset by the proc\_nreset signal.

- A software reset is impossible, since the processor reset is being activated.

- When in Software Reset:

- A watchdog event has priority over the current state.

- The NRST has no effect.

- When in Watchdog Reset:

- The processor reset is active and so a Software Reset cannot be programmed.

- A User Reset cannot be entered.

#### 13.3.6 Reset Controller Status Register

The Reset Controller status register (RSTC\_SR) provides several status fields:

- RSTTYP field: This field gives the type of the last reset, as explained in previous sections.

- SRCMP bit: This field indicates that a Software Reset Command is in progress and that no further software reset should be performed until the end of the current one. This bit is automatically cleared at the end of the current software reset.

- NRSTL bit: The NRSTL bit of the Status Register gives the level of the NRST pin sampled on each MCK rising edge.

- URSTS bit: A high-to-low transition of the NRST pin sets the URSTS bit of the RSTC\_SR register. This

transition is also detected on the Master Clock (MCK) rising edge (see Figure 13-9). If the User Reset is

disabled (URSTEN = 0) and if the interruption is enabled by the URSTIEN bit in the RSTC\_MR register, the

URSTS bit triggers an interrupt. Reading the RSTC\_SR status register resets the URSTS bit and clears the

interrupt.

- BODSTS bit: This bit indicates a brownout detection when the brownout reset is disabled (bod\_rst\_en = 0). It triggers an interrupt if the bit BODIEN in the RSTC\_MR register enables the interrupt. Reading the RSTC\_SR register resets the BODSTS bit and clears the interrupt.

#### 16.4.2 Watchdog Timer Mode Register

WDT MR

Register Name

| Register Marine |         | IN              |          |    |    |    |    |  |

|-----------------|---------|-----------------|----------|----|----|----|----|--|

| Access Type:    | Read-v  | Read-write Once |          |    |    |    |    |  |

| 31              | 30      | 29              | 28       | 27 | 26 | 25 | 24 |  |

| -               | —       | WDIDLEHLT       | WDDBGHLT |    | WE | DD |    |  |

| 23              | 22      | 21              | 20       | 19 | 18 | 17 | 16 |  |

|                 |         |                 | W        | DD |    |    |    |  |

| 15              | 14      | 13              | 12       | 11 | 10 | 9  | 8  |  |

| WDDIS           | WDRPROC | WDRSTEN         | WDFIEN   |    | W  | V  |    |  |

| 7               | 6       | 5               | 4        | 3  | 2  | 1  | 0  |  |

|                 | WDV     |                 |          |    |    |    |    |  |

|                 |         |                 |          |    |    |    |    |  |

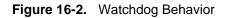

#### • WDV: Watchdog Counter Value

Defines the value loaded in the 12-bit Watchdog Counter.

#### • WDFIEN: Watchdog Fault Interrupt Enable

- 0: A Watchdog fault (underflow or error) has no effect on interrupt.

- 1: A Watchdog fault (underflow or error) asserts interrupt.

#### • WDRSTEN: Watchdog Reset Enable

- 0: A Watchdog fault (underflow or error) has no effect on the resets.

- 1: A Watchdog fault (underflow or error) triggers a Watchdog reset.

#### WDRPROC: Watchdog Reset Processor

- 0: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates all resets.

- 1: If WDRSTEN is 1, a Watchdog fault (underflow or error) activates the processor reset.

#### • WDD: Watchdog Delta Value

Defines the permitted range for reloading the Watchdog Timer.

If the Watchdog Timer value is less than or equal to WDD, writing WDT\_CR with WDRSTT = 1 restarts the timer.

If the Watchdog Timer value is greater than WDD, writing WDT\_CR with WDRSTT = 1 causes a Watchdog error.

#### WDDBGHLT: Watchdog Debug Halt

0: The Watchdog runs when the processor is in debug state.

1: The Watchdog stops when the processor is in debug state.

#### • WDIDLEHLT: Watchdog Idle Halt

0: The Watchdog runs when the system is in idle mode.

1: The Watchdog stops when the system is in idle state.

#### • WDDIS: Watchdog Disable

- 0: Enables the Watchdog Timer.

- 1: Disables the Watchdog Timer.

## 17.2 Voltage Regulator Power Controller (VREG) User Interface

# Offset Register Name Access 0x60 Voltage Regulator Mode Register VREG\_MR Read-write

### Table 17-1.Register Mapping

#### 17.2.1 Voltage Regulator Mode Register

| Register Name | e: VREG_ | MR   |    |    |    |    |        |

|---------------|----------|------|----|----|----|----|--------|

| Access Type:  | Read-w   | rite |    |    |    |    |        |

| 31            | 30       | 29   | 28 | 27 | 26 | 25 | 24     |

| -             | -        | —    | -  | -  | -  | -  | -      |

| 23            | 22       | 21   | 20 | 19 | 18 | 17 | 16     |

| _             | -        | -    | -  | -  | -  | -  | -      |

| 15            | 14       | 13   | 12 | 11 | 10 | 9  | 8      |

| -             | -        | -    | -  | -  | -  | —  | -      |

| 7             | 6        | 5    | 4  | 3  | 2  | 1  | 0      |

| _             | _        | -    | _  | -  | —  | _  | PSTDBY |

#### • PSTDBY: Periodic Interval Value

0 = Voltage regulator in normal mode.

1 = Voltage regulator in standby mode (low-power mode).

Reset

0x0

#### Table 20-20. Signal Description List (Continued)

| Signal Name | Function              | Туре   | Active<br>Level | Comments                    |

|-------------|-----------------------|--------|-----------------|-----------------------------|

|             | Tes                   | t      |                 |                             |

| TST         | Test Mode Select      | Input  | High            | Must be connected to VDDIO. |

| PGMEN0      | Test Mode Select      | Input  | High            | Must be connected to VDDIO  |

| PGMEN1      | Test Mode Select      | Input  | High            | Must be connected to VDDIO  |

| PGMEN2      | Test Mode Select      | Input  | Low             | Must be connected to GND    |

|             | JTA                   | G      |                 |                             |

| тск         | JTAG TCK              | Input  | -               | Pulled-up input at reset    |

| TDI         | JTAG Test Data In     | Input  | -               | Pulled-up input at reset    |

| TDO         | JTAG Test Data Out    | Output | -               |                             |

| TMS         | JTAG Test Mode Select | Input  | -               | Pulled-up input at reset    |

#### 20.3.2 Entering Serial Programming Mode

The following algorithm puts the device in Serial Programming Mode:

- Apply GND, VDDIO, VDDCORE, VDDFLASH and VDDPLL.

- Apply XIN clock within T<sub>POR RESET</sub> + 32(T<sub>SCLK</sub>) if an external clock is available.

- Wait for T<sub>POR\_RESET</sub>.

- Reset the TAP controller clocking 5 TCK pulses with TMS set.

- Shift 0x2 into the IR register (IR is 4 bits long, LSB first) without going through the Run-Test-Idle state.

- Shift 0x2 into the DR register (DR is 4 bits long, LSB first) without going through the Run-Test-Idle state.

- Shift 0xC into the IR register (IR is 4 bits long, LSB first) without going through the Run-Test-Idle state.

- Note: After reset, the device is clocked by the internal RC oscillator. Before clearing RDY signal, if an external clock (> 32 kHz) is connected to XIN, then the device will switch on the external clock. Else, XIN input is not considered. An higher frequency on XIN speeds up the programmer handshake.

| TDI | TMS | TAP Controller State |

|-----|-----|----------------------|

| Х   | 1   |                      |

| Х   | 1   |                      |

| Х   | 1   |                      |

| Х   | 1   |                      |

| Х   | 1   | Test-Logic Reset     |

| Х   | 0   | Run-Test/Idle        |

| Xt  | 1   | Select-DR-Scan       |

Table 20-21. Reset TAP Controller and Go to Select-DR-Scan

#### 20.3.3 Read/Write Handshake

The read/write handshake is done by carrying out read/write operations on two registers of the device that are accessible through the JTAG:

- Debug Comms Control Register: DCCR

- Debug Comms Data Register: DCDR

## 23.7 Functional Description

#### 23.7.1 Interrupt Source Control

#### 23.7.1.1 Interrupt Source Mode

The Advanced Interrupt Controller independently programs each interrupt source. The SRCTYPE field of the corresponding AIC\_SMR (Source Mode Register) selects the interrupt condition of each source.

The internal interrupt sources wired on the interrupt outputs of the embedded peripherals can be programmed either in level-sensitive mode or in edge-triggered mode. The active level of the internal interrupts is not important for the user.

The external interrupt sources can be programmed either in high level-sensitive or low level-sensitive modes, or in positive edge-triggered or negative edge-triggered modes.

#### 23.7.1.2 Interrupt Source Enabling

Each interrupt source, including the FIQ in source 0, can be enabled or disabled by using the command registers; AIC\_IECR (Interrupt Enable Command Register) and AIC\_IDCR (Interrupt Disable Command Register). This set of registers conducts enabling or disabling in one instruction. The interrupt mask can be read in the AIC\_IMR register. A disabled interrupt does not affect servicing of other interrupts.

#### 23.7.1.3 Interrupt Clearing and Setting

All interrupt sources programmed to be edge-triggered (including the FIQ in source 0) can be individually set or cleared by writing respectively the AIC\_ISCR and AIC\_ICCR registers. Clearing or setting interrupt sources programmed in level-sensitive mode has no effect.

The clear operation is perfunctory, as the software must perform an action to reinitialize the "memorization" circuitry activated when the source is programmed in edge-triggered mode. However, the set operation is available for auto-test or software debug purposes. It can also be used to execute an AIC-implementation of a software interrupt.

The AIC features an automatic clear of the current interrupt when the AIC\_IVR (Interrupt Vector Register) is read. Only the interrupt source being detected by the AIC as the current interrupt is affected by this operation. (See "Priority Controller" on page 167.) The automatic clear reduces the operations required by the interrupt service routine entry code to reading the AIC\_IVR. Note that the automatic interrupt clear is disabled if the interrupt source has the Fast Forcing feature enabled as it is considered uniquely as a FIQ source. (For further details, See "Fast Forcing" on page 171.)

The automatic clear of the interrupt source 0 is performed when AIC\_FVR is read.

#### 23.7.1.4 Interrupt Status

Atmel

For each interrupt, the AIC operation originates in AIC\_IPR (Interrupt Pending Register) and its mask in AIC\_IMR (Interrupt Mask Register). AIC\_IPR enables the actual activity of the sources, whether masked or not.

The AIC\_ISR register reads the number of the current interrupt (see "Priority Controller" on page 167) and the register AIC\_CISR gives an image of the signals nIRQ and nFIQ driven on the processor.

Each status referred to above can be used to optimize the interrupt handling of the systems.

#### 23.7.4 Fast Interrupt

#### 23.7.4.1 Fast Interrupt Source

The interrupt source 0 is the only source which can raise a fast interrupt request to the processor except if fast forcing is used. The interrupt source 0 is generally connected to a FIQ pin of the product, either directly or through a PIO Controller.

#### 23.7.4.2 Fast Interrupt Control

The fast interrupt logic of the AIC has no priority controller. The mode of interrupt source 0 is programmed with the AIC\_SMR0 and the field PRIOR of this register is not used even if it reads what has been written. The field SRC-TYPE of AIC\_SMR0 enables programming the fast interrupt source to be positive-edge triggered or negative-edge triggered or high-level sensitive or low-level sensitive

Writing 0x1 in the AIC\_IECR (Interrupt Enable Command Register) and AIC\_IDCR (Interrupt Disable Command Register) respectively enables and disables the fast interrupt. The bit 0 of AIC\_IMR (Interrupt Mask Register) indicates whether the fast interrupt is enabled or disabled.

#### 23.7.4.3 Fast Interrupt Vectoring

The fast interrupt handler address can be stored in AIC\_SVR0 (Source Vector Register 0). The value written into this register is returned when the processor reads AIC\_FVR (Fast Vector Register). This offers a way to branch in one single instruction to the interrupt handler, as AIC\_FVR is mapped at the absolute address 0xFFFF F104 and thus accessible from the ARM fast interrupt vector at address 0x0000 001C through the following instruction:

#### LDR PC,[PC,# -&F20]

When the processor executes this instruction it loads the value read in AIC\_FVR in its program counter, thus branching the execution on the fast interrupt handler. It also automatically performs the clear of the fast interrupt source if it is programmed in edge-triggered mode.

#### 23.7.4.4 Fast Interrupt Handlers

This section gives an overview of the fast interrupt handling sequence when using the AIC. It is assumed that the programmer understands the architecture of the ARM processor, and especially the processor interrupt modes and associated status bits.

#### Assuming that:

- 1. The Advanced Interrupt Controller has been programmed, AIC\_SVR0 is loaded with the fast interrupt service routine address, and the interrupt source 0 is enabled.

- 2. The Instruction at address 0x1C (FIQ exception vector address) is required to vector the fast interrupt:

- LDR PC, [PC, # -&F20]

3. The user does not need nested fast interrupts.

When nFIQ is asserted, if the bit "F" of CPSR is 0, the sequence is:

- 1. The CPSR is stored in SPSR\_fiq, the current value of the program counter is loaded in the FIQ link register (R14\_FIQ) and the program counter (R15) is loaded with 0x1C. In the following cycle, during fetch at address 0x20, the ARM core adjusts R14\_fiq, decrementing it by four.

- 2. The ARM core enters FIQ mode.

- 3. When the instruction loaded at address 0x1C is executed, the program counter is loaded with the value read in AIC\_FVR. Reading the AIC\_FVR has effect of automatically clearing the fast interrupt, if it has been programmed to be edge triggered. In this case only, it de-asserts the nFIQ line on the processor.

- 4. The previous step enables branching to the corresponding interrupt service routine. It is not necessary to save the link register R14\_fiq and SPSR\_fiq if nested fast interrupts are not needed.

- 5. The Interrupt Handler can then proceed as required. It is not necessary to save registers R8 to R13 because FIQ mode has its own dedicated registers and the user R8 to R13 are banked. The other regis-

#### Access Type: Read/Write

| Reset | Value: | 0x0 |

|-------|--------|-----|

|       |        |     |

| 31 | 30  | 29   | 28 | 27 | 26 | 25    | 24 |

|----|-----|------|----|----|----|-------|----|

| -  | -   | -    | -  | -  | -  | -     | -  |

| 23 | 22  | 21   | 20 | 19 | 18 | 17    | 16 |

| -  | -   | -    | -  | -  | -  | -     | -  |

| 15 | 14  | 13   | 12 | 11 | 10 | 9     | 8  |

| -  | -   | -    | -  | -  | -  | -     | -  |

| 7  | 6   | 5    | 4  | 3  | 2  | 1     | 0  |

| _  | SRC | ГҮРЕ | -  | _  |    | PRIOR |    |

#### • PRIOR: Priority Level

Programs the priority level for all sources except FIQ source (source 0).

The priority level can be between 0 (lowest) and 7 (highest).

The priority level is not used for the FIQ in the related SMR register AIC\_SMRx.

#### • SRCTYPE: Interrupt Source Type

The active level or edge is not programmable for the internal interrupt sources.

| SRCTYPE |                                            | Internal Interrupt Sources                                        | External Interrupt Sources |  |

|---------|--------------------------------------------|-------------------------------------------------------------------|----------------------------|--|

| 0       | 0 High level Sensitive Low level Sensitive |                                                                   | Low level Sensitive        |  |

| 0       | 1                                          | Positive edge triggered         Negative edge triggered           |                            |  |

| 1       | 0                                          | High level Sensitive                                              | High level Sensitive       |  |

| 1       | 1                                          | 1         Positive edge triggered         Positive edge triggered |                            |  |

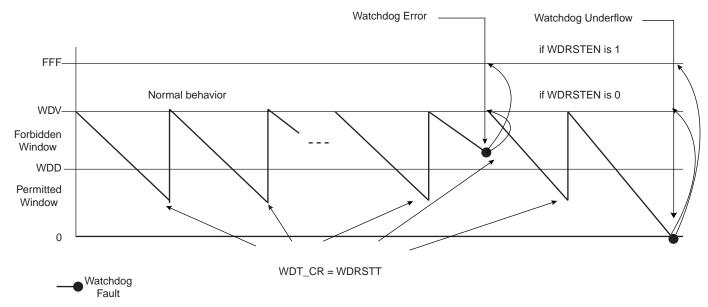

Figure 31-16. Receiver Time-out Block Diagram

Table 31-8 gives the maximum time-out period for some standard baud rates.

Table 31-8.Maximum Time-out Period

| Baud Rate | Bit Time | Time-out |

|-----------|----------|----------|

| bit/sec   | μs       | ms       |

| 600       | 1 667    | 109 225  |

| 1 200     | 833      | 54 613   |

| 2 400     | 417      | 27 306   |

| 4 800     | 208      | 13 653   |

| 9 600     | 104      | 6 827    |

| 14400     | 69       | 4 551    |

| 19200     | 52       | 3 413    |

| 28800     | 35       | 2 276    |

| 33400     | 30       | 1 962    |

| 56000     | 18       | 1 170    |

| 57600     | 17       | 1 138    |

| 200000    | 5        | 328      |

#### 31.6.3.9 Framing Error

The receiver is capable of detecting framing errors. A framing error happens when the stop bit of a received character is detected at level 0. This can occur if the receiver and the transmitter are fully desynchronized.

A framing error is reported on the FRAME bit of the Channel Status Register (US\_CSR). The FRAME bit is asserted in the middle of the stop bit as soon as the framing error is detected. It is cleared by writing the Control Register (US\_CR) with the RSTSTA bit at 1.

#### 33.6.12 TC Interrupt Disable Register

| Register Name: | TC_IDR   | TC_IDRx [x=02] |      |      |      |       |       |  |  |

|----------------|----------|----------------|------|------|------|-------|-------|--|--|

| Access Type:   | Write-or | nly            |      |      |      |       |       |  |  |

| 31             | 30       | 29             | 28   | 27   | 26   | 25    | 24    |  |  |

| -              | -        | _              | -    | _    | _    | _     | _     |  |  |

| 23             | 22       | 21             | 20   | 19   | 18   | 17    | 16    |  |  |

| -              | -        | -              | -    | -    | -    | -     | -     |  |  |

| 15             | 14       | 13             | 12   | 11   | 10   | 9     | 8     |  |  |

| -              | -        | -              | -    | -    | -    | -     | -     |  |  |

| 7              | 6        | 5              | 4    | 3    | 2    | 1     | 0     |  |  |

| ETRGS          | LDRBS    | LDRAS          | CPCS | CPBS | CPAS | LOVRS | COVFS |  |  |

|                |          | •              | •    | •    | •    | •     | •     |  |  |

#### • COVFS: Counter Overflow

0 = No effect.

1 = Disables the Counter Overflow Interrupt.

#### • LOVRS: Load Overrun

0 = No effect.

1 = Disables the Load Overrun Interrupt (if WAVE = 0).

#### • CPAS: RA Compare

0 = No effect.

1 = Disables the RA Compare Interrupt (if WAVE = 1).

#### CPBS: RB Compare

0 = No effect.

1 = Disables the RB Compare Interrupt (if WAVE = 1).

#### CPCS: RC Compare

0 = No effect.

1 = Disables the RC Compare Interrupt.

#### • LDRAS: RA Loading

0 = No effect.

1 = Disables the RA Load Interrupt (if WAVE = 0).

#### • LDRBS: RB Loading

0 = No effect.

1 = Disables the RB Load Interrupt (if WAVE = 0).

#### • ETRGS: External Trigger

0 = No effect.

1 = Disables the External Trigger Interrupt.

#### 35.6.10 UDP Endpoint Control and Status Register

0 1/1

- · · ·

| Register Name | e: UDP_C        | $UDP\_CSRx [x = 0Y]$ |          |                       |         |                 |        |  |

|---------------|-----------------|----------------------|----------|-----------------------|---------|-----------------|--------|--|

| Access Type:  | Read-w          | Read-write           |          |                       |         |                 |        |  |

| 31            | 30              | 29                   | 28       | 27                    | 26      | 25              | 24     |  |

| -             | -               | -                    | -        | -                     |         | RXBYTECNT       |        |  |

| 23            | 22              | 21                   | 20       | 19                    | 18      | 17              | 16     |  |

| RXBYTECNT     |                 |                      |          |                       |         |                 |        |  |

| 15            | 14              | 13                   | 12       | 11                    | 10      | 9               | 8      |  |

| EPEDS         | -               | -                    | —        | DTGLE                 | EPTYPE  |                 |        |  |

| 7             | 6               | 5                    | 4        | 3                     | 2       | 1               | 0      |  |

| DIR           | RX_DATA_<br>BK1 | FORCE<br>STALL       | TXPKTRDY | STALLSENT<br>ISOERROR | RXSETUP | RX_DATA_<br>BK0 | TXCOMP |  |

| 7             | RX_DATA_        | FORCE                |          | 3<br>STALLSENT        | _       | 1<br>RX_DATA_   | -      |  |

WARNING: Due to synchronization between MCK and UDPCK, the software application must wait for the end of the write operation before executing another write by polling the bits which must be set/cleared.

//! Clear flags of UDP UDP\_CSR register and waits for synchronization #define Udp\_ep\_clr\_flag(pInterface, endpoint, flags) { \ pInterface->UDP\_CSR[endpoint] &= ~(flags); \ while ( (pInterface->UDP\_CSR[endpoint] & (flags)) == (flags) ); \ } //! Set flags of UDP UDP\_CSR register and waits for synchronization #define Udp\_ep\_set\_flag(pInterface, endpoint, flags) { \ pInterface->UDP\_CSR[endpoint] |= (flags); \ while ( (pInterface->UDP\_CSR[endpoint] & (flags)) != (flags) ); \ } Note: In a preemptive environment, set or clear the flag and wait for a time of 1 UDPCK clock cycle and 1peripheral clock cycle. How-

ever, RX\_DATA\_BLK0, TXPKTRDY, RX\_DATA\_BK1 require wait times of 3 UDPCK clock cycles and 3 peripheral clock cycles before accessing DPR.

#### TXCOMP: Generates an IN Packet with Data Previously Written in the DPR

This flag generates an interrupt while it is set to one.

Write (Cleared by the firmware):

0 =Clear the flag, clear the interrupt.

```

1 = No effect.

```

Read (Set by the USB peripheral):

0 = Data IN transaction has not been acknowledged by the Host.

1 = Data IN transaction is achieved, acknowledged by the Host.

After having issued a Data IN transaction setting TXPKTRDY, the device firmware waits for TXCOMP to be sure that the host has acknowledged the transaction.

#### RX\_DATA\_BK0: Receive Data Bank 0

#### 36.6.10 ADC Interrupt Mask Register

| Register Name | ADC_IN  | IR    |       |        |       |       |       |

|---------------|---------|-------|-------|--------|-------|-------|-------|

| Access Type:  | Read-or | nly   |       |        |       |       |       |

| 31            | 30      | 29    | 28    | 27     | 26    | 25    | 24    |

| -             | —       | -     | -     | -      | -     | —     | -     |

| 23            | 22      | 21    | 20    | 19     | 18    | 17    | 16    |

| _             | _       | _     | -     | RXBUFF | ENDRX | GOVRE | DRDY  |

| 15            | 14      | 13    | 12    | 11     | 10    | 9     | 8     |

| OVRE7         | OVRE6   | OVRE5 | OVRE4 | OVRE3  | OVRE2 | OVRE1 | OVRE0 |

| 7             | 6       | 5     | 4     | 3      | 2     | 1     | 0     |

| EOC7          | EOC6    | EOC5  | EOC4  | EOC3   | EOC2  | EOC1  | EOC0  |

- EOCx: End of Conversion Interrupt Mask x

- OVREx: Overrun Error Interrupt Mask x

- DRDY: Data Ready Interrupt Mask

- GOVRE: General Overrun Error Interrupt Mask

- ENDRX: End of Receive Buffer Interrupt Mask

- RXBUFF: Receive Buffer Full Interrupt Mask

- 0 = The corresponding interrupt is disabled.

- 1 = The corresponding interrupt is enabled.

Do not use a multiple Chip Select configuration where at least one SCRx register is configured with SCBR = 1 and the others differ from 1 if NCPHA = 0 and CPOL = 1.

If all chip selects are configured with Baudrate = 1, the issue does not appear.

#### 40.4.7 Synchronous Serial Controller (SSC)

40.4.7.1 SSC: Periodic Transmission Limitations in Master Mode

If the Least Significant Bit is sent first (MSBF = 0), the first TAG during the frame synchro is not sent.

#### Problem Fix/Workaround

None.

#### 40.4.7.2 SSC: Transmitter Limitations in Slave Mode

If TK is programmed as output and TF is programmed as input, it is impossible to emit data when the start of edge (rising or falling) of synchro has a Start Delay equal to zero.

#### **Problem Fix/Workaround**

None.

#### 40.4.7.3 SSC: Transmitter Limitations in Slave Mode

If TK is programmed as an input and TF is programmed as an output and requested to be set to low/high during data emission, the Frame Synchro signal is generated one bit clock period after the data start and one data bit is lost. This problem does not exist when generating a periodic synchro.

#### **Problem Fix/Workaround**

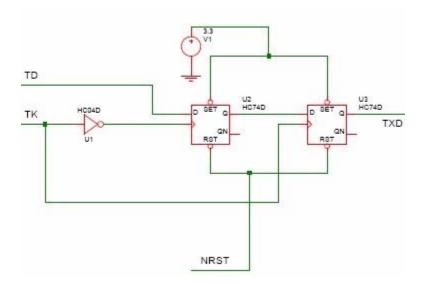

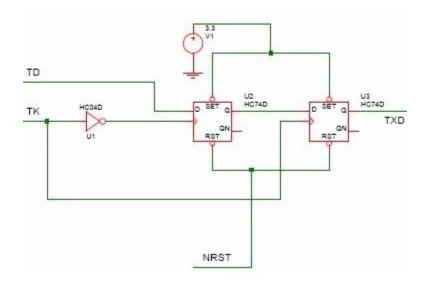

The data need to be delayed for one bit clock period with an external assembly. In the following schematic, TD, TK and NRST are SAM7S signals, TXD is the delayed data to connect to the device.

#### 40.4.8 Two-wire Interface (TWI)

#### 40.4.8.1 TWI: Clock Divider

The value of CLDIV x  $2^{CKDIV}$  must be less than or equal to 8191, the value of CHDIV x  $2^{CKDIV}$  must be less than or equal to 8191.

#### **Problem Fix/Workaround**

#### 40.5.7.2 SSC: Transmitter Limitations in Slave Mode

If TK is programmed as output and TF is programmed as input, it is impossible to emit data when the start of edge (rising or falling) of synchro has a Start Delay equal to zero.

#### **Problem Fix/Workaround**

None.

#### 40.5.7.3 SSC: Transmitter Limitations in Slave Mode

If TK is programmed as an input and TF is programmed as an output and requested to be set to low/high during data emission, the Frame Synchro signal is generated one bit clock period after the data start and one data bit is lost. This problem does not exist when generating a periodic synchro.

#### **Problem Fix/Workaround**

The data need to be delayed for one bit clock period with an external assembly. In the following schematic, TD, TK and NRST are SAM7S signals, TXD is the delayed data to connect to the device.

#### 40.5.8 Two-wire Interface (TWI)

#### 40.5.8.1 TWI: Clock Divider

The value of CLDIV x  $2^{CKDIV}$  must be less than or equal to 8191, the value of CHDIV x  $2^{CKDIV}$  must be less than or equal to 8191.

#### **Problem Fix/Workaround**

None.

40.5.8.2 TWI: Software Reset

when a software reset is performed during a frame and when TWCK is low, it is impossible to initiate a new transfer in READ or WRITE mode.

#### **Problem Fix/Workaround**

None.

## 40.5.8.3 TWI: Disabling Does not Operate Correctly

Any transfer in progress is immediately frozen if the Control Register (TWI\_CR) is written with the bit MSDIS at 1. Furthermore, the status bits TXCOMP and TXRDY in the Status Register (TWI\_SR) are not reset.

#### 40.6.5 Parallel Input/Output Controller (PIO)

#### 40.6.5.1 PIO: Leakage on PA17 - PA20

When PA17, PA18, PA19 or PA20 (the I/O lines multiplexed with the analog inputs) are set as digital inputs with pull-up disabled, the leakage can be 9  $\mu$ A in worst case and 90 nA in typical case per I/O when the I/O is set externally at low level.

#### **Problem Fix/Workaround**

Set the I/O to VDDIO by internal or external pull-up.

#### 40.6.5.2 PIO: Electrical Characteristics on NRST and PA0-PA16 and PA21-31

When NRST or PA0-PA16 or PA21-PA31 are set as digital inputs with pull-up enabled, the voltage of the I/O stabilizes at VPull-up.

#### Vpull-up

| VPull-up Min   | VPull-up Max   |  |  |

|----------------|----------------|--|--|

| VDDIO - 0.65 V | VDDIO - 0.45 V |  |  |

This condition causes a leakage through VDDIO. This leakage is 45  $\mu$ A per pad in worst case at 3.3 V and 25  $\mu$ A at 1.8V.

#### I Leakage

| Parameter         | Тур    | Max   |

|-------------------|--------|-------|

| I Leakage at 3,3V | 2.5 µA | 45 µA |

| I Leakage at 1.8V | 1 µA   | 25 µA |

#### **Problem Fix/Workaround**

It is recommended to use an external pull-up if needed.

#### 40.6.5.3 PIO: Drive Low NRST, PA0-PA16 and PA21-PA31

When NRST or PA0-PA16 and or PA21-PA31 are set as digital inputs with pull-up enabled, driving the I/O with an output impedance higher than 500 ohms may not drive the I/O to a logical zero.

#### **Problem Fix/Workaround**

Output impedance must be lower than 500 ohms.

#### 40.6.6 Power Management Controller (PMC)

#### 40.6.6.1 PMC: Slow Clock Selected in PMC and a Transition Occurs on PA1

Under certain rare circumstances, when CSS = 00 in PMC\_MCKR, and PA1 is set as an input and a transition occurs on PA1, device malfunction might occur.

#### **Problem Fix/Workaround**

Do not transition PA1 as an input when CSS = 00 in PMC\_MCKR.

#### 40.6.6.2 PMC: Programming CSS in PMC\_MCKR Register

Under certain rare circumstances, reprogramming the CSS value in the PMC\_MCKR register (i.e switching the main clock source) might generate malfunction of the device if the following two actions occur simultaneously.

- 1. Switching from:

- PLL Clock to Slow Clock or

#### 40.22.8.4 TWI: NACK Status Bit Lost

During a master frame, if TWI\_SR is read between the Non Acknowledge condition detection and the TXCOMP bit rising in the TWI\_SR, the NACK bit is not set.

#### **Problem Fix/Workaround**

The user must wait for the TXCOMP status bit by interrupt and must not read the TWI\_SR as long as transmission is not completed.

TXCOMP and NACK fields are set simultaneously and the NACK field is reset after the read of the TWI\_SR.

#### 40.22.8.5 TWI: Possible Receive Holding Register Corruption

When loading the TWI\_RHR, the transfer direction is ignored. The last data byte received in the TWI\_RHR is corrupted at the end of the first subsequent transmit data byte. Neither RXRDY nor OVERRUN status bits are set if this occurs.

#### **Problem Fix/Workaround**

The user must be sure that received data is read before transmitting any new data.

#### 40.22.9 Universal Synchronous Asynchronous Receiver Transmitter (USART)

#### 40.22.9.1 USART: Hardware Handshake

The Hardware Handshake does not work at speeds higher than 750 kbauds.

#### Problem Fix/Workaround

None.

#### 40.22.9.2 USART: CTS in Hardware Handshaking

When Hardware Handshaking is used and if CTS goes low near the end of the starting bit, a character can be lost.

#### **Problem Fix/Workaround**

CTS must not go low during a time slot occurring between 2 Master Clock periods before the starting bit and 16 Master Clock periods after the rising edge of the starting bit.

#### 40.22.9.3 USART: Hardware Handshaking – Two Characters Sent

If CTS switches from 0 to 1 during the TX of a character and if the holding register (US\_THR) is not empty, the content of US\_THR will also be transmitted.

#### **Problem Fix/Workaround**

Don't use the PDC in transmit mode and do not fill US\_THR before TXEMPTY is set at 1.

#### 40.22.9.4 USART: XOFF Character Bad Behavior

The XOFF character is sent only when the receive buffer is detected full. While the XOFF is being sent, the remote transmitter is still transmitting. As only one Holding register is available in the receiver, characters will be lost in reception. This makes the software handshaking functionality ineffective.

**Problem Fix/Workaround**

None.

40.22.9.5 USART: DCD is active High instead of Low

The DCD signal is active at High level in the USART Modem Mode.

DCD should be active at Low level.

#### Problem Fix/Workaround

Add an inverter.

#### **Problem Fix/Workaround**

Check the Channel Counter Register before writing the update register.

#### 40.24.2.2 PWM: Update when PWM\_CPRDx = 0

When Channel Period Register equals 0, the period update is not operational.

#### Problem Fix/Workaround

Do not write 0 in the period register.

#### 40.24.2.3 PWM: Counter Start Value

In left aligned mode, the first start value of the counter is 0. For the other periods, the counter starts at 1.

#### Problem Fix/Workaround

None.

#### 40.24.2.4 PWM: Constraints on Duty Cycle Value

Setting Channel Duty Cycle Register (PWM\_CDTYx) at 0 in center aligned mode or at 0 or 1 in left aligned mode may change the polarity of the signal.

#### Problem Fix/Workaround

Do not set PWM\_CDTYx at 0 in center aligned mode.

Do not set PWM\_CDTYx at 0 or 1 in left aligned mode.

#### 40.24.2.5 PWM: Behavior of CHIDx Status Bits in the PWM\_SR Register

Erratic behavior of the CHIDx status bit in the PWM\_SR Register. When a channel is disabled by writing in the PWM\_DIS Register just after enabling it (before completion of a Clock Period of the clock selected for the channel), the PWM line is internally disabled but the CHIDx status bit in the PWM\_SR stays at 1.

#### **Problem Fix/Workaround**

Do not disable a channel before completion of one period of the selected clock.

#### 40.24.3 Real Time Timer (RTT)

#### 40.24.3.1 RTT: Possible Event Loss when Reading RTT\_SR

If an event (RTTINC or ALMS) occurs within the same slow clock cycle during which the RTT\_SR is read, the corresponding bit might be cleared. This can lead to the loss of this event.

#### Problem Fix/Workaround:

The software must handle the RTT event as an interrupt and should not poll RTT\_SR.

#### 40.24.4 Serial Peripheral Interface (SPI)

40.24.4.1 SPI: Bad Serial Clock Generation on 2nd Chip Select

Bad Serial clock generation on the 2nd chip select when SCBR = 1, CPOL = 1 and NCPHA = 0.

This occurs using SPI with the following conditions:

- Master Mode

- CPOL = 1 and NCPHA = 0

- Multiple chip selects are used with one transfer with Baud rate (SCBR) equal to 1 (i.e., when serial clock frequency equals the system clock frequency) and the other transfers set with SCBR are not equal to 1

- Transmitting with the slowest chip select and then with the fastest one, then an additional pulse is generated on output SPCK during the second transfer.