#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                     |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | H8/300H                                                                      |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 12MHz                                                                        |

| Connectivity               | SCI                                                                          |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 8KB (8K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | ·                                                                            |

| RAM Size                   | 1.5K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                    |

| Data Converters            | A/D 4x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -20°C ~ 75°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 32-LQFP                                                                      |

| Supplier Device Package    | 32-LQFP (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/df36902gfhv |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Notice

- All information included in this document is current as of the date this document is issued. Such information, however, is subject to change without any prior notice. Before purchasing or using any Renesas Electronics products listed herein, please confirm the latest product information with a Renesas Electronics sales office. Also, please pay regular and careful attention to additional and different information to be disclosed by Renesas Electronics such as that disclosed through our website.

- Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or others.

- 3. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part.

- 4. Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the use of these circuits, software, or information.

- 5. When exporting the products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations. You should not use Renesas Electronics products or the technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations.

- 6. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 7. Renesas Electronics products are classified according to the following three quality grades: "Standard", "High Quality", and "Specific". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below. You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for written consent of Renesas Electronics. Further, you may not use any Renesas Electronics product for any application for which it is not intended without the prior written consent of Renesas Electronics. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for an application categorized as "Specific" or for which the product is not intended where you have failed to obtain the prior written consent of Renesas Electronics product is "Standard" unless otherwise expressly specified in a Renesas Electronics atta abooks, etc.

- "Standard": Computers; office equipment; communications equipment; test and measurement equipment; audio and visual equipment; home electronic appliances; machine tools; personal electronic equipment; and industrial robots.

- "High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anticrime systems; safety equipment; and medical equipment not specifically designed for life support.

- "Specific": Aircraft; aerospace equipment; submersible repeaters; nuclear reactor control systems; medical equipment or systems for life support (e.g. artificial life support devices or systems), surgical implantations, or healthcare intervention (e.g. excision, etc.), and any other applications or purposes that pose a direct threat to human life.

- 8. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 9. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or system manufactured by you.

- 10. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU ROHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- 11. This document may not be reproduced or duplicated, in any form, in whole or in part, without prior written consent of Renesas Electronics.

- Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries.

- (Note 1) "Renesas Electronics" as used in this document means Renesas Electronics Corporation and also includes its majorityowned subsidiaries.

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

# Figures

| Section 1   | Overview                                                                 |    |

|-------------|--------------------------------------------------------------------------|----|

| Figure 1.1  | Internal Block Diagram of H8/36912 Group                                 | 3  |

| Figure 1.2  | Internal Block Diagram of H8/36902 Group                                 | 4  |

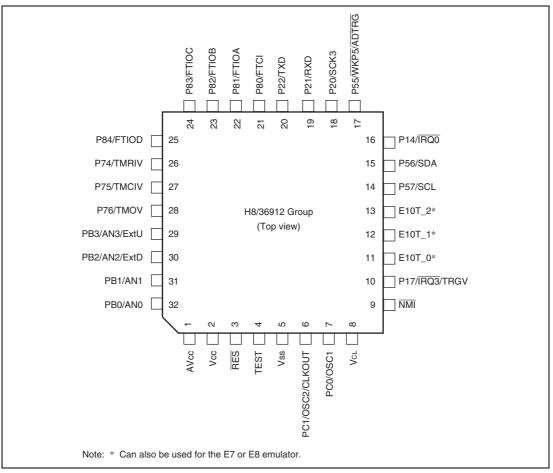

| Figure 1.3  | Pin Arrangement of H8/36912 Group (FP-32A)                               | 5  |

| Figure 1.4  | Pin Arrangement of H8/36902 Group (FP-32A)                               | 6  |

| Figure 1.5  | Pin Arrangement of H8/36912 Group (FP-32D, 32P4B)                        | 7  |

| Figure 1.6  | Pin Arrangement of H8/36902 Group (FP-32D, 32P4B)                        | 8  |

| Section 2   | СРИ                                                                      |    |

| Figure 2.1  | Memory Map (1)                                                           | 12 |

| Figure 2.1  | Memory Map (2)                                                           | 13 |

| Figure 2.2  | CPU Registers                                                            | 14 |

| Figure 2.3  | Usage of General Registers                                               | 15 |

| Figure 2.4  | Relationship between Stack Pointer and Stack Area                        | 16 |

| Figure 2.5  | General Register Data Formats (1)                                        |    |

| Figure 2.5  | General Register Data Formats (2)                                        | 19 |

| Figure 2.6  | Memory Data Formats                                                      | 20 |

| Figure 2.7  | Instruction Formats                                                      |    |

| Figure 2.8  | Branch Address Specification in Memory Indirect Mode                     | 35 |

| Figure 2.9  | On-Chip Memory Access Cycle                                              |    |

| Figure 2.10 | On-Chip Peripheral Module Access Cycle (3-State Access)                  |    |

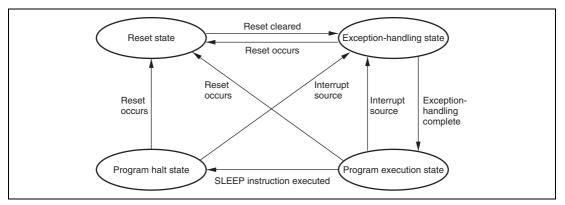

| Figure 2.11 | CPU Operation States                                                     |    |

| Figure 2.12 | 2 State Transitions                                                      | 40 |

| Figure 2.13 | B Example of Timer Configuration with Two Registers Allocated to Same    |    |

|             | Address                                                                  | 41 |

| Section 3   | Exception Handling                                                       |    |

| Figure 3.1  | Reset Sequence                                                           |    |

| Figure 3.2  | Stack Status after Exception Handling                                    |    |

| Figure 3.3  | Interrupt Sequence                                                       | 60 |

| Figure 3.4  | Port Mode Register Setting and Interrupt Request Flag Clearing Procedure | 61 |

| Section 4   | Address Break                                                            |    |

| Figure 4.1  | Block Diagram of Address Break                                           | 63 |

| -           | Address Break Interrupt Operation Example (1)                            |    |

| -           | Address Break Interrupt Operation Example (2)                            |    |

| Section 5   | Clock Pulse Generators                                                      |       |

|-------------|-----------------------------------------------------------------------------|-------|

| Figure 5.1  | Block Diagram of Clock Pulse Generators                                     | 69    |

| Figure 5.2  | State Transition of System Clock                                            | 75    |

| Figure 5.3  | Flowchart of Clock Switching On-chip Oscillator Clock to External Clock (1) | 76    |

| Figure 5.4  | Flowchart of Clock Switching External Clock to On-chip Oscillator Clock (2) | 77    |

| Figure 5.5  | Timing Chart of Switching On-chip Oscillator Clock to External Clock        | 78    |

| Figure 5.6  | Timing Chart to Switch External Clock to On-chip Oscillator Clock           | 79    |

| Figure 5.7  | Example of Trimming Flow for On-chip Oscillator Frequency                   | 80    |

| Figure 5.8  | Timing Chart of Trimming of On-chip Oscillator Frequency                    | 81    |

| Figure 5.9  | Example of Connection to Crystal Resonator                                  | 82    |

| Figure 5.10 | Equivalent Circuit of Crystal Resonator                                     | 82    |

| Figure 5.11 | Example of Connection to Ceramic Resonator                                  | 83    |

| Figure 5.12 | Example of External Clock Input                                             | 83    |

| Figure 5.13 | Example of Incorrect Board Design                                           | 84    |

| Section 6   | Power-Down Modes                                                            |       |

| Figure 6.1  | Mode Transition Diagram                                                     | 91    |

| Section 7   | ROM                                                                         |       |

| Figure 7.1  | Flash Memory Block Configuration                                            | 98    |

| Figure 7.2  | Programming/Erasing Flowchart Example in User Program Mode                  | . 106 |

| Figure 7.3  | Program/Program-Verify Flowchart                                            | . 108 |

| Figure 7.4  | Erase/Erase-Verify Flowchart                                                | .111  |

| Section 9   | I/O Ports                                                                   |       |

| Figure 9.1  | Port 1 Pin Configuration                                                    | .117  |

| Figure 9.2  | Port 2 Pin Configuration                                                    | . 121 |

| Figure 9.3  | Port 5 Pin Configuration                                                    | . 124 |

| Figure 9.4  | Port 7 Pin Configuration                                                    | . 128 |

| Figure 9.5  | Port 8 Pin Configuration                                                    | . 130 |

| Figure 9.6  | Port B Pin Configuration                                                    | .134  |

| Figure 9.7  | Port C Pin Configuration                                                    | . 136 |

| Section 10  | Timer B1                                                                    |       |

| Figure 10.1 | Block Diagram of Timer B1                                                   | . 139 |

| Section 11  | Timer V                                                                     |       |

| Figure 11.1 | Block Diagram of Timer V                                                    | . 146 |

| Figure 11.2 | Increment Timing with Internal Clock                                        | . 153 |

| Figure 11.3 | Increment Timing with External Clock                                        | . 153 |

| -           | OVF Set Timing                                                              |       |

| Figure 11.5 | CMFA and CMFB Set Timing                                                    | . 154 |

# 1.3 Pin Arrangement

Figure 1.3 Pin Arrangement of H8/36912 Group (FP-32A)

| Bit | Bit Name | Initial<br>Value | R/W | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|----------|------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | I        | 1                | R/W | Interrupt Mask Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |     | Masks interrupts other than NMI when set to 1. NMI is accepted regardless of the I bit setting. The I bit is set to 1 at the start of an exception-handling sequence.                                                                                                                                                                                                                                                                                                                                                     |

| 6   | UI       | Undefined        | R/W | User Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| _   |          |                  |     | Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5   | Н        | Undefined        | R/W | Half-Carry Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|     |          |                  |     | When the ADD.B, ADDX.B, SUB.B, SUBX.B, CMP.B, or<br>NEG.B instruction is executed, this flag is set to 1 if there<br>is a carry or borrow at bit 3, and cleared to 0 otherwise.<br>When the ADD.W, SUB.W, CMP.W, or NEG.W<br>instruction is executed, the H flag is set to 1 if there is a<br>carry or borrow at bit 11, and cleared to 0 otherwise.<br>When the ADD.L, SUB.L, CMP.L, or NEG.L instruction is<br>executed, the H flag is set to 1 if there is a carry or<br>borrow at bit 27, and cleared to 0 otherwise. |

| 4   | U        | Undefined        | R/W | User Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|     |          |                  |     | Can be written and read by software using the LDC, STC, ANDC, ORC, and XORC instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3   | Ν        | Undefined        | R/W | Negative Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |                  |     | Stores the value of the most significant bit of data as a sign bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2   | Z        | Undefined        | R/W | Zero Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |                  |     | Set to 1 to indicate zero data, and cleared to 0 to indicate non-zero data.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1   | V        | Undefined        | R/W | Overflow Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|     |          |                  |     | Set to 1 when an arithmetic overflow occurs, and cleared to 0 at other times.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0   | С        | Undefined        | R/W | Carry Flag                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |          |                  |     | Set to 1 when a carry occurs, and cleared to 0 otherwise.<br>Used by:                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | Add instructions, to indicate a carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|     |          |                  |     | Subtract instructions, to indicate a borrow                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     |          |                  |     | Shift and rotate instructions, to indicate a carry                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|     |          |                  |     | The carry flag is also used as a bit accumulator by bit manipulation instructions.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

### 2.3.2 Memory Data Formats

Figure 2.6 shows the data formats in memory. The H8/300H CPU can access word data and longword data in memory, however word or longword data must begin at an even address. If an attempt is made to access word or longword data at an odd address, an address error does not occur, however the least significant bit of the address is regarded as 0, so access begins the preceding address. This also applies to instruction fetches.

When ER7 (SP) is used as an address register to access the stack, the operand size should be word or longword.

| Data Type     | Address                      | Data Format     |

|---------------|------------------------------|-----------------|

|               | 7                            | 7 0             |

| 1-bit data    | Address L                    | 7 6 5 4 3 2 1 0 |

| Byte data     | Address L M                  | ISB             |

| Word data     | Address 2M M<br>Address 2M+1 | ISB LSB         |

| Longword data | Address 2N+1<br>Address 2N+2 | ISB             |

|               | Address 2N+3                 |                 |

Figure 2.6 Memory Data Formats

| Instruction | n Size*       | Function                                                                                                                                                                                                               |

|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRAPA       | —             | Starts trap-instruction exception handling.                                                                                                                                                                            |

| RTE         | _             | Returns from an exception-handling routine.                                                                                                                                                                            |

| SLEEP       | _             | Causes a transition to a power-down state.                                                                                                                                                                             |

| LDC         | B/W           | $(EAs) \rightarrow CCR$<br>Moves the source operand contents to the CCR. The CCR size is one<br>byte, but in transfer from memory, data is read by word access.                                                        |

| STC         | B/W           | $CCR \rightarrow (EAd), EXR \rightarrow (EAd)$<br>Transfers the CCR contents to a destination location. The condition code<br>register size is one byte, but in transfer to memory, data is written by<br>word access. |

| ANDC        | В             | $\label{eq:ccr} \begin{array}{l} CCR \land \#IMM \to CCR, \ EXR \land \#IMM \to EXR \\ Logically \ ANDs \ the \ CCR \ with \ immediate \ data. \end{array}$                                                            |

| ORC         | В             | CCR $\lor$ #IMM $\rightarrow$ CCR, EXR $\lor$ #IMM $\rightarrow$ EXR<br>Logically ORs the CCR with immediate data.                                                                                                     |

| XORC        | В             | CCR $\oplus$ #IMM $\rightarrow$ CCR, EXR $\oplus$ #IMM $\rightarrow$ EXR<br>Logically XORs the CCR with immediate data.                                                                                                |

| NOP         |               | $PC + 2 \rightarrow PC$<br>Only increments the program counter.                                                                                                                                                        |

| Note: *     | Refers to the | e operand size.                                                                                                                                                                                                        |

|             | B: Byte       |                                                                                                                                                                                                                        |

#### Table 2.8 System Control Instructions

W: Word

Figure 2.12 State Transitions

## 2.8 Usage Notes

#### 2.8.1 Notes on Data Access to Empty Areas

The address space of this LSI includes empty areas in addition to the ROM, RAM, and on-chip I/O registers areas available to the user. When data is transferred from CPU to empty areas, the transferred data will be lost. This action may also cause the CPU to malfunction. When data is transferred from an empty area to CPU, the contents of the data cannot be guaranteed.

#### 2.8.2 EEPMOV Instruction

EEPMOV is a block-transfer instruction and transfers the byte size of data indicated by R4L, which starts from the address indicated by R5, to the address indicated by R6. Set R4L and R6 so that the end address of the destination address (value of R6 + R4L) does not exceed H'FFFF (the value of R6 must not change from H'FFFF to H'0000 during execution).

#### 2.8.3 Bit Manipulation Instruction

The BSET, BCLR, BNOT, BST, and BIST instructions read data from the specified address in byte units, manipulate the data of the target bit, and write data to the same address again in byte units. Special care is required when using these instructions in cases where two registers are assigned to the same address or when a bit is directly manipulated for a port, because this may rewrite data of a bit other than the bit to be manipulated.

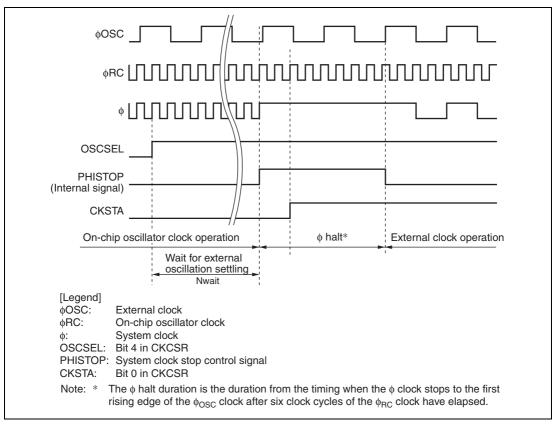

### 5.3.2 Clock Change Timing

The timing for changing clocks are shown in figures 5.5 and 5.6.

Figure 5.5 Timing Chart of Switching On-chip Oscillator Clock to External Clock

| Bit Name |      |      |                | Operating Frequency |       |       |       |         |       |

|----------|------|------|----------------|---------------------|-------|-------|-------|---------|-------|

| STS2     | STS1 | STS0 | Wait Time      | 10 MHz              | 8 MHz | 5 MHz | 4 MHz | 2.5 MHz | 2 MHz |

| 0        | 0    | 0    | 8,192 states   | 0.8                 | 1.0   | 1.6   | 2.0   | 3.3     | 4.1   |

| 0        | 0    | 1    | 16,384 states  | 1.6                 | 2.0   | 3.3   | 4.1   | 6.6     | 8.2   |

| 0        | 1    | 0    | 32,768 states  | 3.3                 | 4.1   | 6.6   | 8.2   | 13.1    | 16.4  |

| 0        | 1    | 1    | 65,536 states  | 6.6                 | 8.2   | 13.1  | 16.4  | 26.2    | 32.8  |

| 1        | 0    | 0    | 131,072 states | 13.1                | 16.4  | 26.2  | 32.8  | 52.4    | 65.5  |

| 1        | 0    | 1    | 1,024 states   | 0.10                | 0.13  | 0.21  | 0.26  | 0.42    | 0.51  |

| 1        | 1    | 0    | 128 states     | 0.01                | 0.02  | 0.03  | 0.03  | 0.05    | 0.06  |

| 1        | 1    | 1    | 16 states      | 0.00                | 0.00  | 0.00  | 0.00  | 0.00    | 0.01  |

#### Table 6.1 Operating Frequency and Wait Time

Notes: 1. Time unit is ms.

2. The on-chip oscillator clock counts the wait states, even when the external clock is used as system clock.

#### 11.3.4 Timer Control/Status Register V (TCSRV)

TCSRV indicates the status flag and controls outputs by using a compare match.

|          | Initial           |                                                                                                                                                                |                                                                                                                                                                                                                                         |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Name | Value             | R/W                                                                                                                                                            | Description                                                                                                                                                                                                                             |

| CMFB     | 0                 | R/W                                                                                                                                                            | Compare Match Flag B                                                                                                                                                                                                                    |

|          |                   |                                                                                                                                                                | [Setting condition]                                                                                                                                                                                                                     |

|          |                   |                                                                                                                                                                | When the TCNTV value matches the TCORB value                                                                                                                                                                                            |

|          |                   |                                                                                                                                                                | [Clearing condition]                                                                                                                                                                                                                    |

|          |                   |                                                                                                                                                                | • After reading CMFB = 1, cleared by writing 0 to CMFB                                                                                                                                                                                  |

| CMFA     | 0                 | R/W                                                                                                                                                            | Compare Match Flag A                                                                                                                                                                                                                    |

|          |                   |                                                                                                                                                                | [Setting condition]                                                                                                                                                                                                                     |

|          |                   |                                                                                                                                                                | When the TCNTV value matches the TCORA value                                                                                                                                                                                            |

|          |                   |                                                                                                                                                                | [Clearing condition]                                                                                                                                                                                                                    |

|          |                   |                                                                                                                                                                | • After reading CMFA = 1, cleared by writing 0 to CMFA                                                                                                                                                                                  |

| OVF      | 0                 | R/W                                                                                                                                                            | Timer Overflow Flag                                                                                                                                                                                                                     |

|          |                   |                                                                                                                                                                | [Setting condition]                                                                                                                                                                                                                     |

|          |                   |                                                                                                                                                                | When TCNTV overflows from H'FF to H'00                                                                                                                                                                                                  |

|          |                   |                                                                                                                                                                | [Clearing condition]                                                                                                                                                                                                                    |

|          |                   |                                                                                                                                                                | • After reading OVF = 1, cleared by writing 0 to OVF                                                                                                                                                                                    |

|          | 1                 |                                                                                                                                                                | Reserved                                                                                                                                                                                                                                |

|          |                   |                                                                                                                                                                | This bit is always read as 1.                                                                                                                                                                                                           |

| OS3      | 0                 | R/W                                                                                                                                                            | Output Select 3 and 2                                                                                                                                                                                                                   |

| OS2      | 0                 | R/W                                                                                                                                                            | These bits select an output method for the TMOV pin by the compare match of TCORB and TCNTV.                                                                                                                                            |

|          |                   |                                                                                                                                                                | 00: No change                                                                                                                                                                                                                           |

|          |                   |                                                                                                                                                                | 01: 0 output                                                                                                                                                                                                                            |

|          |                   |                                                                                                                                                                | 10: 1 output                                                                                                                                                                                                                            |

|          |                   |                                                                                                                                                                | 11: Output toggles                                                                                                                                                                                                                      |

|          | OVF<br>OVS<br>OS3 | Bit Name         Value           CMFB         0           CMFA         0           CMFA         0           OVF         0            1           OS3         0 | Bit Name         Value         R/W           CMFB         0         R/W           CMFA         0         R/W           CMFA         0         R/W           OVF         0         R/W            1            OS3         0         R/W |

# 11.6 Usage Notes

The following types of contention or operation can occur in timer V operation.

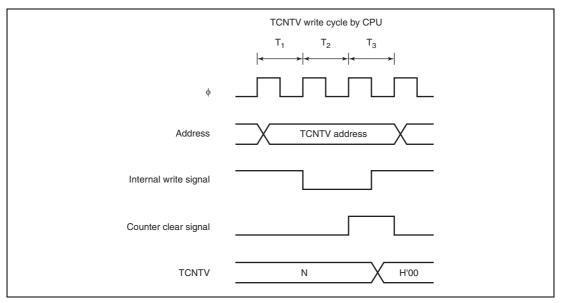

- 1. Writing to registers is performed in the T3 state of a TCNTV write cycle. If a TCNTV clear signal is generated in the T3 state of a TCNTV write cycle, as shown in figure 11.11, clearing takes precedence and the write to the counter is not carried out. If counting-up is generated in the T3 state of a TCNTV write cycle, writing takes precedence.

- 2. If a compare match is generated in the T3 state of a TCORA or TCORB write cycle, the write to TCORA or TCORB takes precedence and the compare match signal is inhibited. Figure 11.12 shows the timing.

- 3. If compare matches A and B occur simultaneously, any conflict between the output selections for compare match A and compare match B is resolved by the following priority: toggle output > output 1 > output 0.

- 4. Depending on the timing, TCNTV may be incremented by a switch between different internal clock sources. When TCNTV is internally clocked, an increment pulse is generated from the falling edge of an internal clock signal, that is divided system clock ( $\phi$ ). Therefore, as shown in figure 11.13 the switch is from a high clock signal to a low clock signal, the switchover is seen as a falling edge, causing TCNTV to increment. TCNTV can also be incremented by a switch between internal and external clocks.

Figure 11.11 Contention between TCNTV Write and Clear

RENESAS

# Section 12 Timer W

The timer W has a 16-bit timer having output compare and input capture functions. The timer W can count external events and output pulses with an arbitrary duty cycle by compare match between the timer counter and four general registers. Thus, it can be applied to various systems.

## 12.1 Features

- Selection of five counter clock sources: four internal clocks ( $\phi$ ,  $\phi/2$ ,  $\phi/4$ , and  $\phi/8$ ) and an external clock (external events can be counted)

- Capability to process up to four pulse outputs or four pulse inputs

- Four general registers:

- Independently assignable output compare or input capture functions

- Usable as two pairs of registers; one register of each pair operates as a buffer for the output compare or input capture register

- Four selectable operating modes:

- Waveform output by compare match

- Selections of 0 output, 1 output, or toggle output

- Input capture function

- Rising edge, falling edge, or both edges

- Counter clearing function

- Counters can be cleared by compare match

- PWM mode

- Up to three-phase PWM output can be provided with desired duty ratio.

- Any initial timer output value can be set

- Five interrupt sources

Four compare match/input capture interrupts and an overflow interrupt.

# **15.3** Register Descriptions

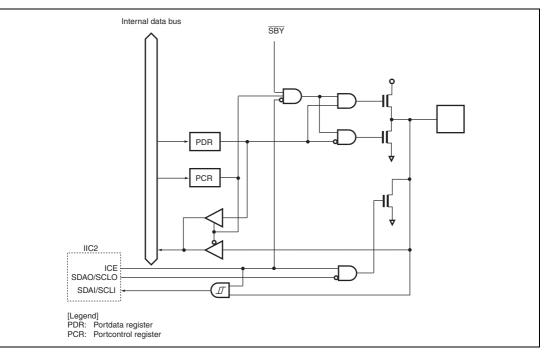

The I<sup>2</sup>C bus interface 2 has the following registers.

- I<sup>2</sup>C bus control register 1 (ICCR1)

- I<sup>2</sup>C bus control register 2 (ICCR2)

- I<sup>2</sup>C bus mode register (ICMR)

- I<sup>2</sup>C bus interrupt enable register (ICIER)

- I<sup>2</sup>C bus status register (ICSR)

- I<sup>2</sup>C bus slave address register (SAR)

- I<sup>2</sup>C bus transmit data register (ICDRT)

- I<sup>2</sup>C bus receive data register (ICDRR)

- I<sup>2</sup>C bus shift register (ICDRS)

### 15.3.1 I<sup>2</sup>C Bus Control Register 1 (ICCR1)

ICCR1 enables or disables the I<sup>2</sup>C bus interface 2, controls transmission or reception, and selects master or slave mode, transmission or reception, and transfer clock frequency in master mode.

| Bit | Bit Name | Initial Value | R/W | Description                                                                             |

|-----|----------|---------------|-----|-----------------------------------------------------------------------------------------|

| 7   | ICE      | 0             | R/W | I <sup>2</sup> C Bus Interface Enable                                                   |

|     |          |               |     | 0: This module is halted. (SCL and SDA pins are set to port function.)                  |

|     |          |               |     | 1: This bit is enabled for transfer operations. (SCL and SDA pins are bus drive state.) |

| 6   | RCVD     | 0             | R/W | Reception Disable                                                                       |

|     |          |               |     | This bit enables or disables the next operation when TRS is 0 and ICDRR is read.        |

|     |          |               |     | 0: Enables next reception                                                               |

|     |          |               |     | 1: Disables next reception                                                              |

|                            |                   |      | CKS = 0 |      |      | CKS = 1 |      |  |

|----------------------------|-------------------|------|---------|------|------|---------|------|--|

| Item                       | Symbol            | Min. | Тур.    | Max. | Min. | Тур.    | Max. |  |

| A/D conversion start delay | t <sub>D</sub>    | 6    | _       | 9    | 4    | _       | 5    |  |

| Input sampling time        | t <sub>spl</sub>  | _    | 31      | _    | _    | 15      | _    |  |

| A/D conversion time        | t <sub>conv</sub> | 131  |         | 134  | 69   |         | 70   |  |

#### Table 16.3 A/D Conversion Time (Single Mode)

Note: All values represent the number of states.

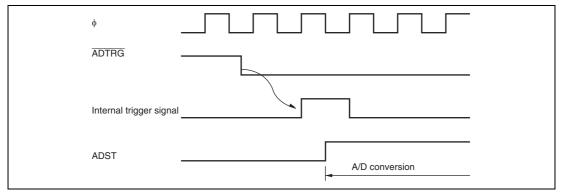

#### 16.4.4 External Trigger Input Timing

A/D conversion can also be started by an external trigger input. When the TRGE bit is set to 1 in ADCR, external trigger input is enabled at the  $\overline{\text{ADTRG}}$  pin. A falling edge at the  $\overline{\text{ADTRG}}$  input pin sets the ADST bit to 1 in ADCSR, starting A/D conversion. Other operations, in both single and scan modes, are the same as when the bit ADST has been set to 1 by software. Figure 16.3 shows the timing.

Figure 16.3 External Trigger Input Timing

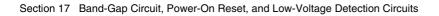

Figure 17.6 Operational Timing of LVDI Circuit (When Compared Voltage is Input through ExtU and ExtD Pins)

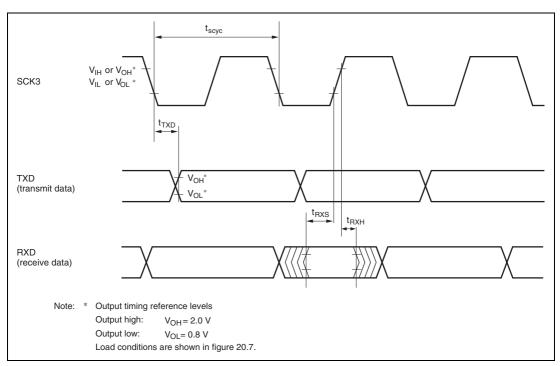

# 20.5 Output Load Condition

Figure 20.7 Output Load Circuit

RENESAS

## A.3 Number of Execution States

The status of execution for each instruction of the H8/300H CPU and the method of calculating the number of states required for instruction execution are shown below. Table A.4 shows the number of cycles of each type occurring in each instruction, such as instruction fetch and data read/write. Table A.3 shows the number of states required for each cycle. The total number of states required for execution of an instruction can be calculated by the following expression:

Execution states =  $I \times S_1 + J \times S_2 + K \times S_K + L \times S_L + M \times S_M + N \times S_N$

Examples: When instruction is fetched from on-chip ROM, and an on-chip RAM is accessed.

BSET #0, @FF00

From table A.4:  $I = L = 2, \quad J = K = M = N = 0$

From table A.3:  $S_1 = 2$ ,  $S_1 = 2$

Number of states required for execution =  $2 \times 2 + 2 \times 2 = 8$

When instruction is fetched from on-chip ROM, branch address is read from on-chip ROM, and on-chip RAM is used for stack area.

JSR @@ 30

From table A.4: I = 2, J = K = 1, L = M = N = 0

From table A.3:

$S_{_{\rm I}}=S_{_{\rm J}}=S_{_{\rm K}}=2$

Number of states required for execution =  $2 \times 2 + 1 \times 2 + 1 \times 2 = 8$

Figure B.6 (1) Port 5 Block Diagram (P57, P56) (for H8/36912 Group)

# Т

| Timer B1                    | 139   |

|-----------------------------|-------|

| Auto-reload timer operation | . 142 |

| Interval timer operation    | . 142 |

| Timer V                     | 145   |

| Timer W                     | 159   |

| Transfer Rate               | 244   |

# V

| Vector address |  |

|----------------|--|

|----------------|--|

# W

| Watchdog timer | 1 |

|----------------|---|

|----------------|---|