Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status                | Active                                                                                                                |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Core Processor                | ARM® Cortex®-M7                                                                                                       |

| Core Size                     | 32-Bit Single-Core                                                                                                    |

| Speed                         | 216MHz                                                                                                                |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                                     |

| Number of I/O                 | 132                                                                                                                   |

| Program Memory Size           | 2MB (2M x 8)                                                                                                          |

| Program Memory Type           | FLASH                                                                                                                 |

| EEPROM Size                   | -                                                                                                                     |

| RAM Size                      | 512K x 8                                                                                                              |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                                           |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                                 |

| Oscillator Type               | Internal                                                                                                              |

| Operating Temperature         | -40°C ~ 105°C (TA)                                                                                                    |

| Mounting Type                 | Surface Mount                                                                                                         |

| Package / Case                | 201-UFBGA                                                                                                             |

| Supplier Device Package       | 176+25UFBGA (10x10)                                                                                                   |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f777iik7                                                 |

|                               |                                                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# List of tables

| Table 1.  | Device summary                                                                                                     |     |

|-----------|--------------------------------------------------------------------------------------------------------------------|-----|

| Table 2.  | STM32F777xx, STM32F778Ax and STM32F779xx features and peripheral counts                                            | 16  |

| Table 3.  | Voltage regulator configuration mode versus device operating mode                                                  | 32  |

| Table 4.  | Regulator ON/OFF and internal reset ON/OFF availability.                                                           |     |

| Table 5.  | Voltage regulator modes in stop mode                                                                               |     |

| Table 6.  | Timer feature comparison.                                                                                          |     |

| Table 7.  | I2C implementation                                                                                                 |     |

| Table 8.  | USART implementation                                                                                               |     |

| Table 9.  | Legend/abbreviations used in the pinout table                                                                      |     |

| Table 10. | STM32F777xx, STM32F778Ax and STM32F779xx pin and                                                                   | -   |

|           | ball definitions                                                                                                   | 64  |

| Table 11. | FMC pin definition.                                                                                                |     |

| Table 12. | STM32F777xx, STM32F778Ax and STM32F779xx alternate                                                                 | 00  |

|           | function mapping                                                                                                   | 02  |

| Table 13. | STM32F777xx, STM32F778Ax and STM32F779xx register                                                                  | 52  |

| Table 15. | boundary addresses                                                                                                 | 07  |

| Table 14. | Voltage characteristics                                                                                            |     |

| Table 14. | Current characteristics                                                                                            |     |

|           | Thermal characteristics                                                                                            |     |

| Table 16. |                                                                                                                    |     |

| Table 17. | General operating conditions                                                                                       |     |

| Table 18. | Limitations depending on the operating power supply range                                                          |     |

| Table 19. | VCAP1/VCAP2 operating conditions                                                                                   |     |

| Table 20. | Operating conditions at power-up / power-down (regulator ON)                                                       |     |

| Table 21. | Operating conditions at power-up / power-down (regulator OFF)                                                      |     |

| Table 22. | Reset and power control block characteristics                                                                      |     |

| Table 23. | Over-drive switching characteristics                                                                               | 21  |

| Table 24. | Typical and maximum current consumption in Run mode, code with data processing running from ITCM RAM, regulator ON | ഹ   |

| Table 25  |                                                                                                                    | 22  |

| Table 25. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Single bank mode, ART ON except prefetch / L1-cache ON)                                 |     |

|           | or SRAM on AXI (L1-cache ON), regulator ON                                                                         | 23  |

| Table 26. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Dual bank mode, ART ON except prefetch / L1-cache ON),                                  | ~ . |

|           | regulator ON                                                                                                       | 24  |

| Table 27. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Single bank mode) or SRAM on AXI (L1-cache disabled),                                   |     |

|           | regulator ON                                                                                                       | 25  |

| Table 28. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Dual bank mode), regulator ON                                                           | 26  |

| Table 29. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Single bank mode) on ITCM interface (ART disabled),                                     |     |

|           | regulator ON                                                                                                       | 27  |

| Table 30. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Dual bank mode) on ITCM interface (ART disabled),                                       |     |

|           | regulator ON                                                                                                       | 28  |

| Table 31. | Typical and maximum current consumption in Run mode, code with data processing                                     |     |

|           | running from Flash memory (Single bank mode, ART ON except prefetch / L1-cache ON)                                 |     |

|           | or SRAM on AXI (L1-cache ON), regulator OFF                                                                        |     |

|           |                                                                                                                    |     |

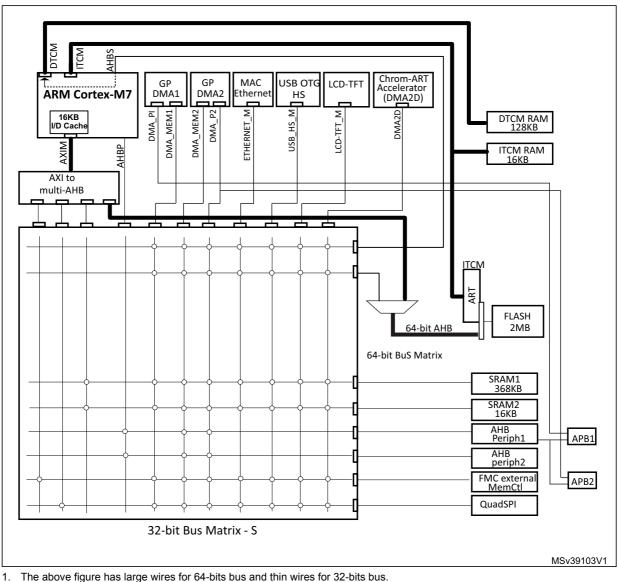

FMC, Quad-SPI, AHB and APB peripherals) and ensures a seamless and efficient operation even when several high-speed peripherals work simultaneously.

Figure 3. STM32F777xx, STM32F778Ax and STM32F779xx AXI-AHB bus matrix architecture<sup>(1)</sup>

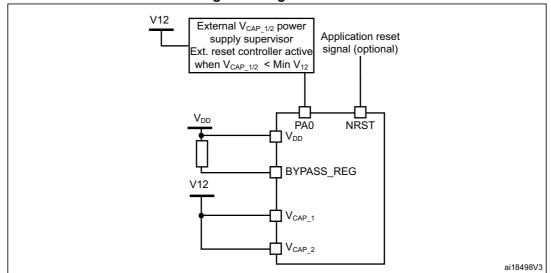

#### Figure 8. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is slower than the time for  $V_{DD}$  to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

- *Note:* The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

# 2.31 SD/SDIO/MMC card host interface (SDMMC)

SDMMC host interfaces are available, that support the MultiMediaCard System Specification Version 4.2 in three different databus modes: 1-bit (default), 4-bit and 8-bit.

The interface allows data transfer at up to 50 MHz, and is compliant with the SD Memory Card Specification Version 2.0.

The SDMMC Card Specification Version 2.0 is also supported with two different databus modes: 1-bit (default) and 4-bit.

The current version supports only one SD/SDMMC/MMC4.2 card at any one time and a stack of MMC4.1 or previous.

The SDMMC can be served by the DMA controller

# 2.32 Ethernet MAC interface with dedicated DMA and IEEE 1588 support

The devices provide an IEEE-802.3-2002-compliant media access controller (MAC) for ethernet LAN communications through an industry-standard medium-independent interface (MII) or a reduced medium-independent interface (RMII). The microcontroller requires an external physical interface device (PHY) to connect to the physical LAN bus (twisted-pair, fiber, etc.). The PHY is connected to the device MII port using 17 signals for MII or 9 signals for RMII, and can be clocked using the 25 MHz (MII) from the microcontroller.

The devices include the following features:

- Supports 10 and 100 Mbit/s rates

- Dedicated DMA controller allowing high-speed transfers between the dedicated SRAM and the descriptors

- Tagged MAC frame support (VLAN support)

- Half-duplex (CSMA/CD) and full-duplex operation

- MAC control sublayer (control frames) support

- 32-bit CRC generation and removal

- Several address filtering modes for physical and multicast address (multicast and group addresses)

- 32-bit status code for each transmitted or received frame

- Internal FIFOs to buffer transmit and receive frames. The transmit FIFO and the receive FIFO are both 2 Kbytes.

- Supports hardware PTP (precision time protocol) in accordance with IEEE 1588 2008 (PTP V2) with the time stamp comparator connected to the TIM2 input

- Triggers interrupt when system time becomes greater than target time

- Software configurable to OTG1.3 and OTG2.0 modes of operation

- USB 2.0 LPM (Link Power Management) support

- Battery Charging Specification Revision 1.2 support

- Internal FS OTG PHY support

- External HS or HS OTG operation supporting ULPI in SDR mode. The OTG PHY is connected to the microcontroller ULPI port through 12 signals. It can be clocked using the 60 MHz output.

- Internal USB DMA

- HNP/SNP/IP inside (no need for any external resistor)

- for OTG/Host modes, a power switch is needed in case bus-powered devices are connected

# 2.36 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The devices embed a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory overhead. It has a clock domain independent from the CPU clock, allowing the HDMI-CEC controller to wakeup the MCU from Stop mode on data reception.

# 2.37 Digital camera interface (DCMI)

The devices embed a camera interface that can connect with camera modules and CMOS sensors through an 8-bit to 14-bit parallel interface, to receive video data. The camera interface can sustain a data transfer rate up to 54 Mbytes/s in 8-bit mode at 54 MHz. It features:

- Programmable polarity for the input pixel clock and synchronization signals

- Parallel data communication can be 8-, 10-, 12- or 14-bit

- Supports 8-bit progressive video monochrome or raw bayer format, YCbCr 4:2:2 progressive video, RGB 565 progressive video or compressed data (like JPEG)

- Supports continuous mode or snapshot (a single frame) mode

- Capability to automatically crop the image

| Name                   | Abbreviation                                                     | Definition                                                                                         |  |  |  |  |

|------------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin name               |                                                                  | specified in brackets below the pin name, the pin function during and after as the actual pin name |  |  |  |  |

|                        | S                                                                | Supply pin                                                                                         |  |  |  |  |

| Pin type               | I                                                                | Input only pin                                                                                     |  |  |  |  |

|                        | I/O                                                              | Input / output pin                                                                                 |  |  |  |  |

|                        | FT                                                               | 5 V tolerant I/O                                                                                   |  |  |  |  |

| I/O structure          | ТТа                                                              | a 3.3 V tolerant I/O directly connected to ADC                                                     |  |  |  |  |

| NO Structure           | В                                                                | B Dedicated BOOT pin                                                                               |  |  |  |  |

|                        | RST                                                              | Bidirectional reset pin with weak pull-up resistor                                                 |  |  |  |  |

| Notes                  | Unless otherwise                                                 | specified by a note, all I/Os are set as floating inputs during and after reset                    |  |  |  |  |

| Alternate<br>functions | Functions selected                                               | d through GPIOx_AFR registers                                                                      |  |  |  |  |

| Additional functions   | Functions directly selected/enabled through peripheral registers |                                                                                                    |  |  |  |  |

## Table 9. Legend/abbreviations used in the pinout table

# Table 10. STM32F777xx, STM32F778Ax and STM32F779xx pin andball definitions

|         |         |          |         | Pin N   | umbe     | ər                      |         |                |          |                                |          |    |       |                                                                                               |                         |  |

|---------|---------|----------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|----|-------|-----------------------------------------------------------------------------------------------|-------------------------|--|

|         | s       | ТМ32     | 2F777   | 'xx     |          | -                       |         | F778/<br>F779: |          | reset                          |          |    |       |                                                                                               |                         |  |

| LQFP100 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type |    | Notes | Alternate functions                                                                           | Additional<br>functions |  |

| 1       | 1       | A2       | 1       | 1       | A3       | E10                     | 1       | 1              | A3       | PE2                            | I/O      | FT | -     | TRACECLK, SPI4_SCK,<br>SAI1_MCLK_A,<br>QUADSPI_BK1_IO2,<br>ETH_MII_TXD3,<br>FMC_A23, EVENTOUT | -                       |  |

| 2       | 2       | A1       | 2       | 2       | A2       | F10                     | 2       | 2              | A2       | PE3                            | I/O      | FT | -     | TRACED0, SAI1_SD_B,<br>FMC_A19, EVENTOUT                                                      | -                       |  |

#### Pinouts and pin description

- NC (not-connected) pins are not bonded. They must be configured by software to output push-pull and forced to 0 in the output data register to avoid an extra current consumption in low-power modes. list of pins: PI8, PI12, PI13, PI14, PF6, PF7, PF8, PF9, PC2, PC3, PC4, PC5, PI15, PJ0, PJ1, PJ2, PJ3, PJ4, PJ5, PH6, PH7, PJ12, PJ13, PJ14, PJ15, PG14, PK3, PK4, PK5, PK6 and PK7.

- PC13, PC14, PC15 and Pl8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and Pl8 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF. - These I/Os must not be used as a current source (e.g. to drive an LED).

- 3. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- 4. If the device is in regulator OFF/internal reset ON mode (BYPASS\_REG pin is set to VDD), then PA0 is used as an internal reset (active low).

- 5. Internally connected to VDD or VSS depending on part number.

# Table 26. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (Dual bank mode, ART ON except prefetch / L1-cache ON), regulator ON

| Symbol          | Deremeter              | Conditions                                   | £ (MILI-)  | Turn                    |     | Max <sup>(1)</sup>     |                        |                         |      |    |  |

|-----------------|------------------------|----------------------------------------------|------------|-------------------------|-----|------------------------|------------------------|-------------------------|------|----|--|

| Symbol          | Symbol Parameter       | Parameter                                    | Conditions | f <sub>HCLK</sub> (MHz) | Тур | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |    |  |

|                 |                        |                                              | 216        | 190                     | 219 | 255                    | -                      |                         |      |    |  |

|                 |                        |                                              | 200        | 177                     | 204 | 242                    | 268                    |                         |      |    |  |

|                 |                        |                                              | 180        | 157                     | 173 | 208                    | 228                    |                         |      |    |  |

|                 |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 168        | 139                     | 153 | 185                    | 204                    |                         |      |    |  |

|                 |                        |                                              |            | 144                     | 107 | 117                    | 144                    | 161                     |      |    |  |

|                 |                        |                                              |            |                         |     | 60                     | 48                     | 54                      | 81   | 98 |  |

|                 | Supply                 |                                              | 25         | 23                      | 28  | 54                     | 71                     | mA                      |      |    |  |

| I <sub>DD</sub> | current in<br>RUN mode |                                              | 216        | 92                      | 104 | 150                    | -                      |                         |      |    |  |

|                 |                        |                                              | 200        | 86                      | 97  | 143                    | 170                    |                         |      |    |  |

|                 |                        |                                              | 180        | 76                      | 85  | 119                    | 140                    |                         |      |    |  |

|                 |                        | All peripherals disabled <sup>(3)</sup>      | 168        | 67                      | 75  | 107                    | 126                    |                         |      |    |  |

|                 |                        |                                              | 144        | 52                      | 58  | 84                     | 101                    |                         |      |    |  |

|                 |                        |                                              | 60         | 23                      | 28  | 54                     | 71                     |                         |      |    |  |

|                 |                        |                                              | 25         | 11                      | 15  | 42                     | 59                     |                         |      |    |  |

1. Guaranteed by characterization results.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Symbol                                  | Parameter                                                | Conditions                                                             |                    | ,<br>Min     | Тур  | Мах          | Unit |

|-----------------------------------------|----------------------------------------------------------|------------------------------------------------------------------------|--------------------|--------------|------|--------------|------|

| Symbol                                  | Falameter                                                | Conditions                                                             |                    | IVIIII       | тур  | IVIAA        | Onit |

| t                                       | PLLSAI lock time                                         | VCO freq = 192 MHz                                                     | 2                  | 75           | -    | 200          | 116  |

| t <sub>LOCK</sub>                       |                                                          | VCO freq = 432 MHz                                                     | <u>.</u>           | 100          | -    | 300          | μs   |

|                                         |                                                          | Cycle to cycle at                                                      | RMS                | -            | 90   | -            |      |

|                                         |                                                          | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                           | peak<br>to<br>peak | -            | ±280 | -            | ps   |

| Jitter <sup>(3)</sup>                   | Master SAI clock jitter                                  | Average frequency o<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                  | -            | 90   | -            | ps   |

|                                         | FS clock jitter                                          | Cycle to cycle at 48 I<br>on 1000 samples                              | КНz                | -            | 400  | -            | ps   |

| I <sub>DD(PLLSAI)</sub> <sup>(4)</sup>  | PLLSAI power consumption on $V_{\text{DD}}$              | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.15<br>0.45 | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLLSAI)</sub> <sup>(4)</sup> | PLLSAI power consumption on $V_{\mbox{\scriptsize DDA}}$ | VCO freq = 192 MHz<br>VCO freq = 432 MHz                               |                    | 0.30<br>0.55 | -    | 0.40<br>0.85 | mA   |

Table 49. PLLISAI characteristics (continued)

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

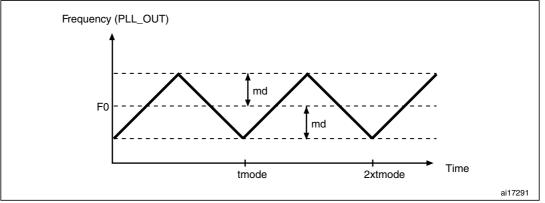

## 5.3.12 PLL spread spectrum clock generation (SSCG) characteristics

The spread spectrum clock generation (SSCG) feature allows to reduce electromagnetic interferences (see *Table 61: EMI characteristics*). It is available only on the main PLL.

| Symbol            | Parameter             | Min  | Тур | Max <sup>(1)</sup>  | Unit |  |  |  |

|-------------------|-----------------------|------|-----|---------------------|------|--|--|--|

| f <sub>Mod</sub>  | Modulation frequency  | -    | -   | 10                  | KHz  |  |  |  |

| md                | Peak modulation depth | 0.25 | -   | 2                   | %    |  |  |  |

| MODEPER * INCSTEP | -                     | -    | -   | 2 <sup>15</sup> – 1 | -    |  |  |  |

#### Table 50. SSCG parameters constraint

1. Guaranteed by design.

Equation 1

The frequency modulation period (MODEPER) is given by the equation below:

$MODEPER = round[f_{PLL \ IN}/(4 \times f_{Mod})]$

$f_{\mathsf{PLL\_IN}}$  and  $f_{\mathsf{Mod}}$  must be expressed in Hz. As an example:

DocID028294 Rev 4

If  $f_{PLL\_IN} = 1$  MHz, and  $f_{MOD} = 1$  kHz, the modulation depth (MODEPER) is given by equation 1:

MODEPER = round

$$[10^{6}/(4 \times 10^{3})] = 250$$

Equation 2

Equation 2 allows to calculate the increment step (INCSTEP):

INCSTEP = round[

$$((2^{15}-1) \times md \times PLLN)/(100 \times 5 \times MODEPER)$$

]

$f_{VCO OUT}$  must be expressed in MHz.

With a modulation depth (md) =  $\pm 2$  % (4 % peak to peak), and PLLN = 240 (in MHz):

INCSTEP = round[ $((2^{15}-1) \times 2 \times 240)/(100 \times 5 \times 250)$ ] = 126md(quantitazed)%

An amplitude quantization error may be generated because the linear modulation profile is obtained by taking the quantized values (rounded to the nearest integer) of MODPER and INCSTEP. As a result, the achieved modulation depth is quantized. The percentage quantized modulation depth is given by the following formula:

$$md_{quantized}$$

% = (MODEPER × INCSTEP × 100 × 5)/((2<sup>15</sup> - 1) × PLLN)

As a result:

$$md_{quantized}$$

% =  $(250 \times 126 \times 100 \times 5)/((2^{15} - 1) \times 240)$  = 2.002%(peak)

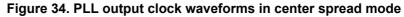

*Figure 34* and *Figure 35* show the main PLL output clock waveforms in center spread and down spread modes, where:

F0 is  $f_{PLL_OUT}$  nominal. T<sub>mode</sub> is the modulation period. md is the modulation depth.

- 1. Guaranteed by characterization results.

- 2. Cycling performed over the whole temperature range.

## 5.3.17 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 60*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> =<br>216 MHz, conforms to IEC 61000-<br>4-2 | 2B              |

| V <sub>FTB</sub>  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> =+25 °C, f <sub>HCLK</sub> =<br>168 MHz, conforms to IEC 61000-<br>4-2  | 5A              |

#### Table 60. EMS characteristics

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

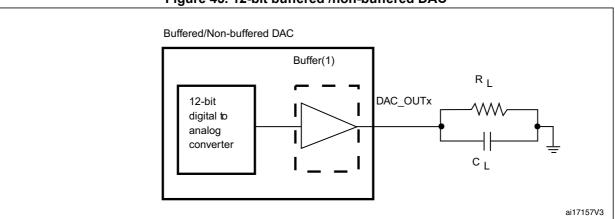

Figure 45. 12-bit buffered /non-buffered DAC

The DAC integrates an output buffer that can be used to reduce the output impedance and to drive external loads directly without the use of an external operational amplifier. The buffer can be bypassed by configuring the BOFFx bit in the DAC\_CR register.

### 5.3.29 Communications interfaces

## I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s.

- Fast-mode Plus (Fm+): with a bit rate up to 1Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2C peripheral is properly configured (refer to RM0410 reference manual) and when the I2CCLK frequency is greater than the minimum shown in the table below:

| Symbol    | Parameter           | Con            | dition                     | Min                       | Unit |  |

|-----------|---------------------|----------------|----------------------------|---------------------------|------|--|

|           |                     | Standard-mode  |                            | 2                         |      |  |

|           |                     | Fast-mode      | Analog filter ON<br>DNF=0  | 8                         |      |  |

| f(I2CCLK) | I2CCLK<br>frequency | i ast-mode     | Analog filter OFF<br>DNF=1 | 9                         | MHz  |  |

|           |                     |                | Fast-mode Plus             | Analog filter ON<br>DNF=0 | 16   |  |

|           |                     | rast-mode rius | Analog filter OFF<br>DNF=1 | 16                        |      |  |

Table 83. Minimum I2CCLK frequency in all I2C modes

The SDA and SCL I/O requirements are met with the following restrictions:

- The SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

- The 20mA output drive requirement in Fast-mode Plus is not supported. This limits the maximum load Cload supported in Fm+, which is given by these formulas:

Tr(SDA/SCL)=0.8473xRpxCload

$R_p(min)= (VDD-V_{OL}(max))/I_{OL}(max)$

Where Rp is the I2C lines pull-up. Refer to Section 5.3.20: I/O port characteristics for the I2C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to *Table 84* for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах               | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|-------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 70 <sup>(3)</sup> | ns   |

### Table 84. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered.

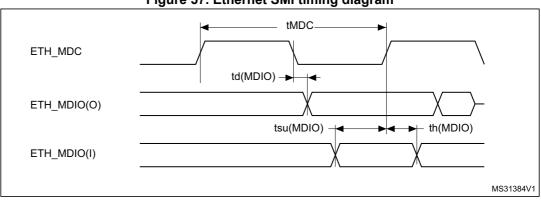

#### Figure 57. Ethernet SMI timing diagram

| Symbol                | Parameter                | Min                   | Тур                     | Мах                   | Unit |

|-----------------------|--------------------------|-----------------------|-------------------------|-----------------------|------|

| t <sub>MDC</sub>      | MDC cycle time(2.38 MHz) | 400                   | 400                     | 403                   |      |

| T <sub>d(MDIO)</sub>  | Write data valid time    | T <sub>HCLK</sub> + 1 | T <sub>HCLK</sub> + 1.5 | T <sub>HCLK</sub> + 3 | ns   |

| t <sub>su(MDIO)</sub> | Read data setup time     | 12.5                  | -                       | -                     | 115  |

| t <sub>h(MDIO)</sub>  | Read data hold time      | 0                     | -                       | -                     |      |

1. Guaranteed by characterization results.

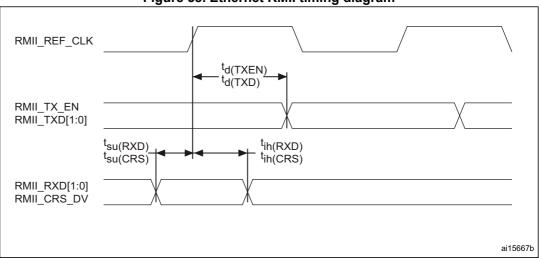

*Table 97* gives the list of Ethernet MAC signals for the RMII and *Figure 58* shows the corresponding timing diagram.

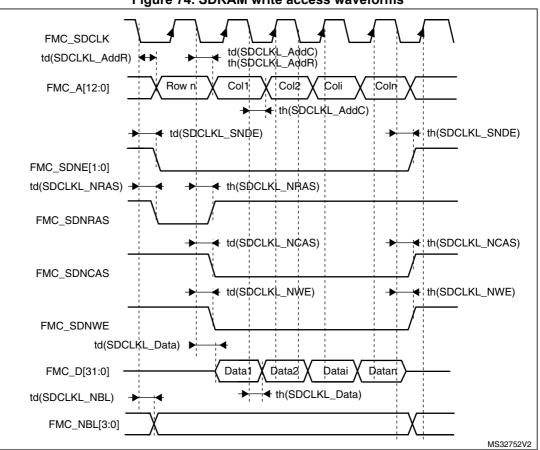

Figure 74. SDRAM write access waveforms

#### Table 116. SDRAM write timings<sup>(1)</sup>

| Symbol                        | Parameter              | Min                      | Мах                      | Unit |

|-------------------------------|------------------------|--------------------------|--------------------------|------|

| t <sub>w(SDCLK)</sub>         | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>d(SDCLKL _Data</sub> ) | Data output valid time | -                        | 3                        |      |

| t <sub>h(SDCLKL</sub> _Data)  | Data output hold time  | 0                        | -                        |      |

| t <sub>d(SDCLKL_Add)</sub>    | Address valid time     | -                        | 3.5                      |      |

| t <sub>d(SDCLKL_SDNWE)</sub>  | SDNWE valid time       | -                        | 1.5                      |      |

| t <sub>h(SDCLKL_SDNWE)</sub>  | SDNWE hold time        | 0.5                      | -                        | ns   |

| t <sub>d(SDCLKL_SDNE)</sub>   | Chip select valid time | -                        | 1.5                      | 113  |

| t <sub>h(SDCLKLSDNE)</sub>    | Chip select hold time  | 0.5                      | -                        |      |

| t <sub>d(SDCLKL_SDNRAS)</sub> | SDNRAS valid time      | -                        | 1                        |      |

| t <sub>h(SDCLKL_SDNRAS)</sub> | SDNRAS hold time       | 0.5                      | -                        |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS valid time      | -                        | 1                        |      |

| t <sub>d(SDCLKL_SDNCAS)</sub> | SDNCAS hold time       | 0.5                      | -                        |      |

1. Guaranteed by characterization results.

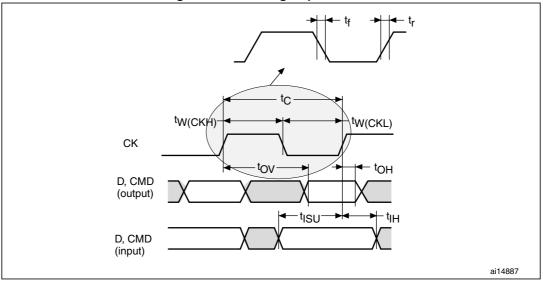

### 5.3.36 SD/SDIO MMC card host interface (SDMMC) characteristics

Unless otherwise specified, the parameters given in *Table 123* for the SDIO/MMC interface are derived from tests performed under the ambient temperature,  $f_{PCLK2}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 30 pF

- Measurement points are done at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.20: I/O port characteristics for more details on the input/output characteristics.

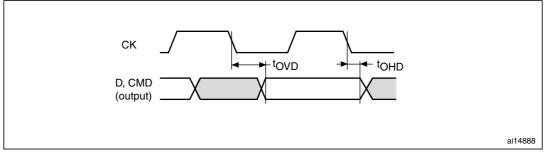

Figure 81. SDIO high-speed mode

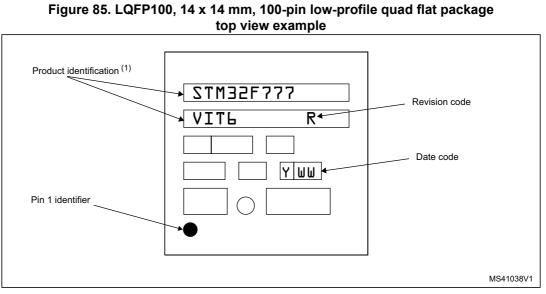

#### LQFP100 device making

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

228/255

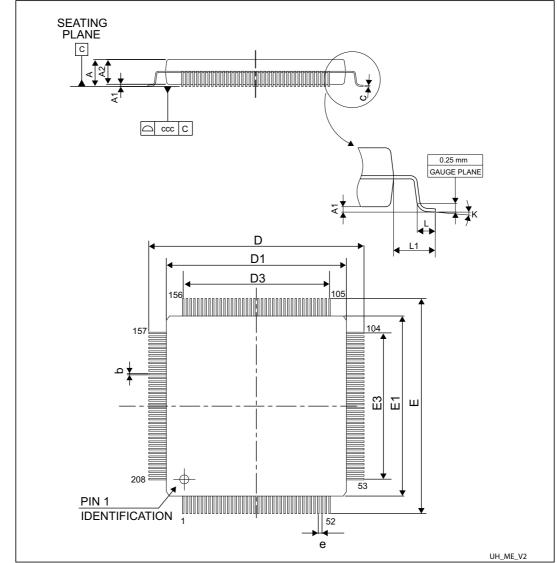

# 6.4 LQFP208 28 x 28 mm low-profile quad flat package information

Figure 92. LQFP208, 28 x 28 mm, 208-pin low-profile quad flat package outline

1. Drawing is not to scale.

# 6.5 WLCSP 180-bump, 5.5 x 6 mm, wafer level chip scale package information

e1 A1 BALL LOCATION // bbb Z D G -DETAIL A e2 F A1 ORIENTATION REFERENCE -▶lel A2 -A3 TOP VIEW BOTTOM VIEW SIDE VIEW BUMP 🛆 eee Z Ż Notes 1&2 øb(180x) Øccc@ZXY Øddd@Z SEATING PLANE DETAIL A ROTATED 90° A05G\_WLCSP180\_ME\_V1

Figure 95. WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

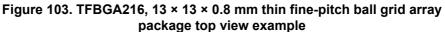

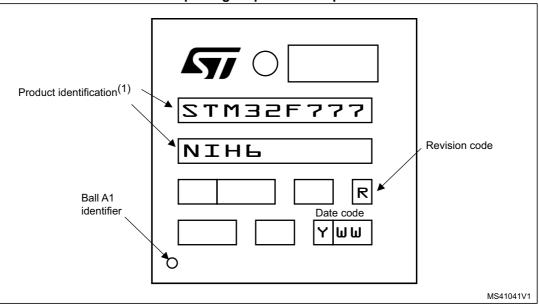

#### **TFBGA216 device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.