Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status                | Active                                                                                                   |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                        |

| Number of I/O                 | 159                                                                                                      |

| Program Memory Size           | 2MB (2M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | ·                                                                                                        |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 105°C (TA)                                                                                       |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 216-TFBGA                                                                                                |

| Supplier Device Package       | 216-TFBGA (13x13)                                                                                        |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f777nih7tr                                  |

|                               |                                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The supply voltage can drop to 1.7 V with the use of an external power supply supervisor (refer to *Section 2.18.2: Internal reset OFF*). A comprehensive set of power-saving mode allows the design of low-power applications.

The STM32F777xx, STM32F778Ax and STM32F779xx devices offer devices in 10 packages ranging from 100 pins to 216 pins. The set of included peripherals changes with the device chosen.

These features make the STM32F777xx, STM32F778Ax and STM32F779xx microcontrollers suitable for a wide range of applications:

- Motor drive and application control

- Medical equipment

- Industrial applications: PLC, inverters, circuit breakers

- Printers, and scanners

- Alarm systems, video intercom, and HVAC

- Home audio appliances

- Mobile applications, Internet of Things

- Wearable devices: smartwatches.

Figure 2 shows the general block diagram of the device family

### 2.10 LCD-TFT controller

The LCD-TFT display controller provides a 24-bit parallel digital RGB (Red, Green, Blue) and delivers all signals to interface directly to a broad range of LCD and TFT panels up to XGA (1024x768) resolution with the following features:

- 2 display layers with dedicated FIFO (64x32-bit)

- Color Look-Up table (CLUT) up to 256 colors (256x24-bit) per layer

- Up to 8 input color formats selectable per layer

- Flexible blending between two layers using alpha value (per pixel or constant)

- Flexible programmable parameters for each layer

- Color keying (transparency color)

- Up to 4 programmable interrupt events

## 2.11 Chrom-ART Accelerator<sup>™</sup> (DMA2D)

The Chrom-Art Accelerator <sup>™</sup> (DMA2D) is a graphic accelerator which offers advanced bit blitting, row data copy and pixel format conversion. It supports the following functions:

- Rectangle filling with a fixed color

- Rectangle copy

- Rectangle copy with pixel format conversion

- Rectangle composition with blending and pixel format conversion

Various image format codings are supported, from indirect 4bpp color mode up to 32bpp direct color. It embeds dedicated memory to store color lookup tables.

An interrupt can be generated when an operation is complete or at a programmed watermark.

All the operations are fully automatized and are running independently from the CPU or the DMAs.

### 2.12 Nested vectored interrupt controller (NVIC)

The devices embed a nested vectored interrupt controller able to manage 16 priority levels, and handle up to 110 maskable interrupt channels plus the 16 interrupt lines of the  $Cortex^{\ensuremath{\mathbb{R}}}$ -M7 with FPU core.

- Closely coupled NVIC gives low-latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Allows early processing of interrupts

- Processing of late arriving, higher-priority interrupts

- Support tail chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimum interrupt latency.

The RTC clock sources can be:

- A 32.768 kHz external crystal (LSE)

- An external resonator or oscillator(LSE)

- The internal low power RC oscillator (LSI, with typical frequency of 32 kHz)

- The high-speed external clock (HSE) divided by 32

The RTC is functional in  $V_{BAT}$  mode and in all low-power modes when it is clocked by the LSE. When clocked by the LSI, the RTC is not functional in  $V_{BAT}$  mode, but is functional in all low-power modes.

All RTC events (Alarm, WakeUp Timer, Timestamp or Tamper) can generate an interrupt and wakeup the device from the low-power modes.

#### 2.21 Low-power modes

The devices support three low-power modes to achieve the best compromise between low power consumption, short startup time and available wakeup sources:

#### Sleep mode

In Sleep mode, only the CPU is stopped. All peripherals continue to operate and can wake up the CPU when an interrupt/event occurs.

Stop mode

The Stop mode achieves the lowest power consumption while retaining the contents of SRAM and registers. All clocks in the 1.2 V domain are stopped, the PLL, the HSI RC and the HSE crystal oscillators are disabled.

The voltage regulator can be put either in main regulator mode (MR) or in low-power mode (LPR). Both modes can be configured as follows (see *Table 5: Voltage regulator modes in stop mode*):

- Normal mode (default mode when MR or LPR is enabled)

- Under-drive mode.

The device can be woken up from the Stop mode by any of the EXTI line (the EXTI line source can be one of the 16 external lines, the PVD output, the RTC alarm / wakeup / tamper / time stamp events, the USB OTG FS/HS wakeup or the Ethernet wakeup and LPTIM1 asynchronous interrupt).

| Voltage regulator<br>configuration | Main regulator (MR)    | Low-power regulator (LPR) |

|------------------------------------|------------------------|---------------------------|

| Normal mode                        | MR ON                  | LPR ON                    |

| Under-drive mode                   | MR in under-drive mode | LPR in under-drive mode   |

#### Table 5. Voltage regulator modes in stop mode

#### Standby mode

The Standby mode is used to achieve the lowest power consumption. The internal voltage regulator is switched off so that the entire 1.2 V domain is powered off. The PLL, the HSI RC and the HSE crystal oscillators are also switched off. After entering

#### Pinouts and pin description

|         |         |          | I       | Pin N   | umbe     | ər                      |               |         |          |                                |          |               |       |                                                                                                                                          |                         |

|---------|---------|----------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         | S       | TM32     | F777    | xx      |          |                         | FM32I<br>FM32 |         |          | reset                          |          |               |       |                                                                                                                                          |                         |

| LQFP100 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                      | Additional<br>functions |

| 81      | 114     | B12      | 142     | 164     | B12      | A4                      | 142           | 164     | B12      | PD0                            | I/O      | FT            | -     | DFSDM1_CKIN6,<br>DFSDM1_DATIN7,<br>UART4_RX, CAN1_RX,<br>FMC_D2, EVENTOUT                                                                | -                       |

| 82      | 115     | C12      | 143     | 165     | C12      | D5                      | 143           | 165     | C12      | PD1                            | I/O      | FT            | -     | DFSDM1_DATIN6,<br>DFSDM1_CKIN7,<br>UART4_TX, CAN1_TX,<br>FMC_D3, EVENTOUT                                                                |                         |

| 83      | 116     | D12      | 144     | 166     | D12      | D6                      | 144           | 166     | D12      | PD2                            | I/O      | FT            | -     | TRACED2, TIM3_ETR,<br>UART5_RX,<br>SDMMC1_CMD,<br>DCMI_D11, EVENTOUT                                                                     | -                       |

| 84      | 117     | D11      | 145     | 167     | C11      | В5                      | 145           | 167     | C11      | PD3                            | I/O      | FT            | -     | DFSDM1_CKOUT,<br>SPI2_SCK/I2S2_CK,<br>DFSDM1_DATIN0,<br>USART2_CTS, FMC_CLK,<br>DCMI_D5, LCD_G7,<br>EVENTOUT                             | -                       |

| 85      | 118     | D10      | 146     | 168     | D11      | A5                      | 146           | 168     | D11      | PD4                            | 1/0      | FT            | -     | DFSDM1_CKIN0,<br>USART2_RTS, FMC_NOE,<br>EVENTOUT                                                                                        | -                       |

| 86      | 119     | C11      | 147     | 169     | C10      | C5                      | 147           | 169     | C10      | PD5                            | I/O      | FT            | -     | USART2_TX, FMC_NWE,<br>EVENTOUT                                                                                                          | -                       |

| -       | 120     | D8       | 148     | 170     | F8       | B6                      | 148           | 170     | F8       | VSS                            | S        | -             | -     | -                                                                                                                                        | -                       |

| -       | 121     | C8       | 149     | 171     | E9       | A6                      | 149           | 171     | E9       | VDDSDM<br>MC                   | s        | -             | -     | -                                                                                                                                        | -                       |

| 87      | 122     | B11      | 150     | 172     | B11      | E6                      | 150           | 172     | B11      | PD6                            | I/O      | FT            | -     | DFSDM1_CKIN4,<br>SPI3_MOSI/I2S3_SD,<br>SAI1_SD_A, USART2_RX,<br>DFSDM1_DATIN1,<br>SDMMC2_CK,<br>FMC_NWAIT, DCMI_D10,<br>LCD_B2, EVENTOUT | -                       |

# Table 10. STM32F777xx, STM32F778Ax and STM32F779xx pin andball definitions (continued)

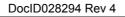

# 4 Memory mapping

The memory map is shown in *Figure 21*.

Figure 21. Memory map

| Bus  | Boundary address          | Peripheral         |

|------|---------------------------|--------------------|

|      | 0x4001 7C00 - 0x4001 FFFF | Reserved           |

|      | 0x4001 7800 - 0x4001 7BFF | MDIOS              |

|      | 0x4001 7400 - 0x4001 77FF | DFSDM1             |

|      | 0x4001 6C00 - 0x4001 73FF | DSI Host           |

|      | 0x4001 6800 - 0x4001 6BFF | LCD-TFT            |

|      | 0x4001 6000 - 0x4001 67FF | Reserved           |

|      | 0x4001 5C00 - 0x4001 5FFF | SAI2               |

|      | 0x4001 5800 - 0x4001 5BFF | SAI1               |

|      | 0x4001 5400 - 0x4001 57FF | SPI6               |

|      | 0x4001 5000 - 0x4001 53FF | SPI5               |

|      | 0x4001 4C00 - 0x4001 4FFF | Reserved           |

|      | 0x4001 4800 - 0x4001 4BFF | TIM11              |

|      | 0x4001 4400 - 0x4001 47FF | TIM10              |

|      | 0x4001 4000 - 0x4001 43FF | TIM9               |

| APB2 | 0x4001 3C00 - 0x4001 3FFF | EXTI               |

|      | 0x4001 3800 - 0x4001 3BFF | SYSCFG             |

|      | 0x4001 3400 - 0x4001 37FF | SPI4               |

|      | 0x4001 3000 - 0x4001 33FF | SPI1/I2S1          |

|      | 0x4001 2C00 - 0x4001 2FFF | SDMMC1             |

|      | 0x4001 2400 - 0x4001 2BFF | Reserved           |

|      | 0x4001 2000 - 0x4001 23FF | ADC1 - ADC2 - ADC3 |

|      | 0x4001 1C00 - 0x4001 1FFF | SDMMC2             |

|      | 0x4001 1800 - 0x4001 1BFF | Reserved           |

|      | 0x4001 1400 - 0x4001 17FF | USART6             |

|      | 0x4001 1000 - 0x4001 13FF | USART1             |

|      | 0x4001 0800 - 0x4001 0FFF | Reserved           |

|      | 0x4001 0400 - 0x4001 07FF | TIM8               |

|      | 0x4001 0000 - 0x4001 03FF | TIM1               |

# Table 13. STM32F777xx, STM32F778Ax and STM32F779xx register boundary addresses<sup>(1)</sup> (continued)

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> ...) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure good operation of the device. It is not recommended to remove filtering capacitors to reduce PCB size or cost. This might cause incorrect operation of the device.

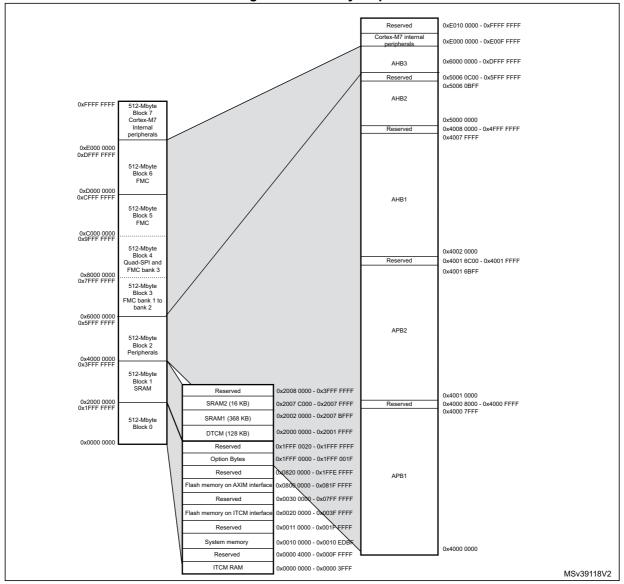

#### 5.1.7 Current consumption measurement

## 5.2 Absolute maximum ratings

Stresses above the absolute maximum ratings listed in *Table 14: Voltage characteristics*, *Table 15: Current characteristics*, and *Table 16: Thermal characteristics* may cause permanent damage to the device. These are stress ratings only and the functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. The device mission profile (application conditions) is compliant with JEDEC JESD47 Qualification Standard. Extended mission profiles are available on demand.

| Symbol                            | Ratings                                                                                                                                              | Min                                                      | Max                  | Unit |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------|------|

| V <sub>DD</sub> -V <sub>SS</sub>  | External main supply voltage (including $V_{DDA}$ , $V_{DD}$ , $V_{BAT}$ , $V_{DDUSB}$ , $V_{DDDSI}$ <sup>(1)</sup> and $V_{DDSDMMC}$ <sup>(2)</sup> | - 0.3                                                    | 4.0                  |      |

|                                   | Input voltage on FT pins <sup>(3)</sup>                                                                                                              | V <sub>SS</sub> – 0.3                                    | V <sub>DD</sub> +4.0 |      |

| V                                 | Input voltage on TTa pins                                                                                                                            | V <sub>SS</sub> - 0.3                                    | 4.0                  |      |

| V <sub>IN</sub>                   | Input voltage on any other pin                                                                                                                       | V <sub>SS</sub> - 0.3                                    | 4.0                  |      |

|                                   | Input voltage on BOOT pin                                                                                                                            | V <sub>SS</sub>                                          | 9.0                  |      |

| $ \Delta V_{DDx} $                | Variations between different $V_{DD}$ power pins                                                                                                     | -                                                        | 50                   | mV   |

| V <sub>SSX</sub> -V <sub>SS</sub> | Variations between all the different ground pins <sup>(4)</sup>                                                                                      | -                                                        | 50                   |      |

| V <sub>ESD(HBM)</sub>             | Electrostatic discharge voltage (human body model)                                                                                                   | see Sectio<br>Absolute n<br>ratings (ele<br>sensitivity) | naximum<br>ectrical  | -    |

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- When the regulator is ON, the voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 144 \text{ MHz}$

- Scale 2 for 144 MHz <  $f_{HCLK} \le$  168 MHz

- Scale 1 for 168 MHz <  $f_{HCLK} \le 216$  MHz. The over-drive is only ON at 216 MHz.

- When the regulator is OFF, the V12 is provided externally as described in *Table 17: General operating conditions*:

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- External clock frequency is 25 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The typical current consumption values are obtained for 1.7 V  $\leq V_{DD} \leq 3.6$  V voltage range and for T<sub>A</sub>= 25 °C unless otherwise specified.

- The maximum values are obtained for  $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$  voltage range and a maximum ambient temperature (T<sub>A</sub>) unless otherwise specified.

- For the voltage range  $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ , the maximum frequency is 180 MHz.

# Table 24. Typical and maximum current consumption in Run mode, code with data processing<br/>running from ITCM RAM, regulator ON

| Symbol          | Doromotor              | Conditions                                   | £ (MALI_)               | Turn |                        | Unit                   |                         |      |

|-----------------|------------------------|----------------------------------------------|-------------------------|------|------------------------|------------------------|-------------------------|------|

| I <sub>DD</sub> | Parameter              | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit |

|                 |                        |                                              | 216                     | 193  | 221 <sup>(4)</sup>     | 258 <sup>(4)</sup>     | -                       |      |

|                 |                        |                                              | 200                     | 179  | 207                    | 244                    | 279                     |      |

|                 |                        |                                              | 180                     | 159  | 176 <sup>(4)</sup>     | 210 <sup>(4)</sup>     | 238 <sup>(4)</sup>      |      |

|                 |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 142  | 156                    | 187                    | 211                     |      |

|                 | Supply                 |                                              | 144                     | 122  | 135                    | 167                    | 190                     |      |

|                 |                        |                                              | 60                      | 49   | 55                     | 81                     | 103                     | mA   |

|                 |                        |                                              | 25                      | 23   | 28                     | 28 54 76               | 76                      |      |

| DD              | current in<br>RUN mode |                                              | 216                     | 95   | 107 <sup>(4)</sup>     | 153 <sup>(4)</sup>     | -                       | ША   |

|                 |                        |                                              | 200                     | 88   | 100                    | 146                    | 180                     |      |

|                 |                        |                                              | 180                     | 78   | 88 <sup>(4)</sup>      | 122 <sup>(4)</sup>     | 147 <sup>(4)</sup>      |      |

|                 |                        | All peripherals disabled <sup>(3)</sup>      | 168                     | 70   | 78                     | 109                    | 133                     |      |

|                 |                        |                                              | 144                     | 60   | 68                     | 99                     | 123                     |      |

|                 |                        |                                              | 60                      | 24   | 29                     | 55                     | 76                      |      |

|                 |                        |                                              | 25                      | 12   | 16                     | 42                     | 63                      |      |

1. Guaranteed by characterization results, unless otherwise specified.

# Table 30. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (Dual bank mode) on ITCM interface (ART disabled), regulator ON

| Cumhal          | Demonster         | Conditions                                   | £ (MIL-)                | True |           | Max <sup>(1)</sup> |           | Unit |

|-----------------|-------------------|----------------------------------------------|-------------------------|------|-----------|--------------------|-----------|------|

| Symbol          | Parameter         | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | TA= 25 °C | TA=85 °C           | TA=105 °C | Unit |

|                 |                   |                                              | 216                     | 191  | 218       | 255                | -         |      |

|                 |                   |                                              | 200                     | 178  | 195       | 241                | 269       |      |

|                 |                   |                                              | 180                     | 164  | 179       | 214                | 236       |      |

|                 |                   | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 147  | 160       | 192                | 212       |      |

|                 |                   |                                              | 144                     | 121  | 130       | 157                | 175       |      |

|                 |                   |                                              | 60                      | 60   | 66        | 93                 | 111       | mA   |

|                 | Supply current in |                                              | 25                      | 28   | 33        | 59                 | 77        |      |

| I <sub>DD</sub> | RUN mode          |                                              | 216                     | 93   | 104       | 150                | -         |      |

|                 |                   |                                              | 200                     | 87   | 97        | 144                | 171       |      |

|                 |                   |                                              | 180                     | 83   | 92        | 126                | 148       |      |

|                 |                   | All peripherals disabled <sup>(3)</sup>      | 168                     | 75   | 82        | 114                | 134       |      |

|                 |                   |                                              | 144                     | 65   | 71        | 97                 | 115       |      |

|                 |                   |                                              | 60                      | 35   | 40        | 66                 | 84        |      |

|                 |                   |                                              | 25                      | 16   | 20        | 47                 | 64        |      |

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

- 1. Guaranteed by characterization results.

- 2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

- 3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Cumhal          | Deremeter                | Conditions             | £ (MIL-)                | Turn   |                        | Max <sup>(1)</sup>     |                         | Unit |

|-----------------|--------------------------|------------------------|-------------------------|--------|------------------------|------------------------|-------------------------|------|

| Symbol          | Parameter                | Conditions             | f <sub>HCLK</sub> (MHz) | :) Typ | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C |      |

|                 |                          |                        | 216                     | 128    | 144 <sup>(3)</sup>     | 190 <sup>(3)</sup>     | -                       |      |

|                 |                          |                        | 200                     | 119    | 134                    | 180                    | 214                     |      |

|                 |                          | All                    | 180                     | 105    | 118 <sup>(3)</sup>     | 153 <sup>(3)</sup>     | 178 <sup>(3)</sup>      |      |

|                 |                          | peripherals            | 168                     | 93     | 105                    | 136                    | 156                     |      |

|                 |                          | enabled <sup>(2)</sup> | 144                     | 72     | 80                     | 107                    | 124                     |      |

|                 |                          |                        | 60                      | 33     | 39                     | 65                     | 82                      |      |

|                 | Supply                   |                        | 25                      | 17     | 21                     | 47                     | 65                      | mA   |

| I <sub>DD</sub> | current in<br>Sleep mode |                        | 216                     | 18     | 25 <sup>(3)</sup>      | 71 <sup>(3)</sup>      | -                       |      |

|                 |                          |                        | 200                     | 17     | 24                     | 70                     | 112                     |      |

|                 |                          | All                    | 180                     | 14     | 20 <sup>(3)</sup>      | 54 <sup>(3)</sup>      | 75 <sup>(3)</sup>       |      |

|                 |                          | peripherals            | 168                     | 13     | 18                     | 49                     | 69                      |      |

|                 |                          | disabled               | 144                     | 10     | 14                     | 40                     | 58                      |      |

|                 |                          |                        | 60                      | 6      | 10                     | 36                     | 53                      |      |

|                 |                          |                        | 25                      | 4      | 8                      | 34                     | 51                      |      |

Table 33. Typical and maximum current consumption in Sleep mode, regulator ON

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. Guaranteed by test in production.

|                                                                                |                                                    | 39. Peripheral   | I <sub>DD</sub> (Typ) <sup>(1)</sup> |                  |             |

|--------------------------------------------------------------------------------|----------------------------------------------------|------------------|--------------------------------------|------------------|-------------|

|                                                                                | Peripheral                                         | Scale 1          | Scale 2                              | Scale 3          | Unit        |

|                                                                                | GPIOA                                              | 2.9              | 2.8                                  | 2.2              |             |

|                                                                                | GPIOB                                              | 3.0              | 2.9                                  | 2.2              |             |

|                                                                                | GPIOC                                              | 2.9              | 2.8                                  | 2.2              |             |

|                                                                                | GPIOD                                              | 3.1              | 3.0                                  | 2.3              |             |

|                                                                                | GPIOE                                              | 3.1              | 3.0                                  | 2.3              |             |

|                                                                                | GPIOF                                              | 2.9              | 2.8                                  | 2.2              |             |

|                                                                                | GPIOG                                              | 2.9              | 2.8                                  | 2.2              |             |

|                                                                                | GPIOH                                              | 3.1              | 3.1                                  | 2.4              |             |

|                                                                                | GPIOI                                              | 3.0              | 2.9                                  | 2.2              |             |

| AHB1                                                                           | GPIOJ                                              | 2.9              | 2.9                                  | 2.2              |             |

| (up to                                                                         | GPIOK                                              | 2.8              | 2.8                                  | 2.4              | µA/MHz      |

| AHB1<br>(up to<br>216 MHz)                                                     | CRC                                                | 1.0              | 0.9                                  | 0.8              |             |

|                                                                                | BKPSRAM                                            | 0.9              | 0.9                                  | 0.7              |             |

|                                                                                | DMA1                                               | 3.17 x N + 11.63 | 3.08 x N + 11.39                     | 2.6 x N + 9.64   |             |

|                                                                                | DMA2                                               | 3.33 x N + 12.84 | 3.27 x N + 11.84                     | 2.75 x N + 10.10 |             |

|                                                                                | DMA2D                                              | 77.7             | 76.3                                 | 63.5             |             |

|                                                                                | ETH_MAC<br>ETH_MAC_TX<br>ETH_MAC_RX<br>ETH_MAC_PTP | 40.1             | 39.5                                 | 32.8             |             |

|                                                                                | OTG_HS                                             | 58.5             | 57.4                                 | 48.1             |             |

|                                                                                | OTG_HS+ULPI                                        | 58.5             | 57.4                                 | 48.1             |             |

|                                                                                | DCMI                                               | 2.9              | 2.8                                  | 2.1              |             |

|                                                                                | JPEG                                               | 74.8             | 73.4                                 | 61.9             |             |

| (up to                                                                         | CRYP                                               | 1.9              | 1.7                                  | 1.4              | µA/MHz      |

| 216 MHz)                                                                       | HASH                                               | 4.5              | 4.4                                  | 3.6              | μΑνινιπΖ    |

|                                                                                | RNG                                                | 6.7              | 6.7                                  | 5.4              |             |

|                                                                                | USB_OTG_FS                                         | 32.4             | 31.9                                 | 26.7             |             |

| AHB3                                                                           | FMC                                                | 18.6             | 18.2                                 | 15.1             | µA/MHz      |

| (up to<br>216 MHz)<br>AHB2<br>(up to<br>216 MHz)<br>AHB3<br>(up to<br>216 MHz) | QSPI                                               | 22.3             | 21.8                                 | 18.1             | μι νινιι ιΖ |

| B                                                                              | us matrix <sup>(2)</sup>                           | 3.94             | 3.25                                 | 2.12             | µA/MHz      |

Table 39. Peripheral current consumption

#### 5.3.10 Internal clock source characteristics

The parameters given in *Table 45* and *Table 46* are derived from tests performed under ambient temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

#### High-speed internal (HSI) RC oscillator

|                                     |                                       |                                      | -   |     |     |      |

|-------------------------------------|---------------------------------------|--------------------------------------|-----|-----|-----|------|

| Symbol                              | Parameter                             | Conditions                           | Min | Тур | Max | Unit |

| f <sub>HSI</sub>                    | Frequency                             | -                                    | -   | 16  | -   | MHz  |

| 100                                 | HSI user trimming step <sup>(2)</sup> | -                                    | -   | -   | 1   | %    |

|                                     |                                       | $T_A = -40$ to 105 °C <sup>(3)</sup> | - 8 | -   | 4.5 | %    |

| ACC <sub>HSI</sub>                  | Accuracy of the HSI oscillator        | $T_A = -10$ to 85 °C <sup>(3)</sup>  | - 4 | -   | 4   | %    |

| 10045                               |                                       | $T_A = 25 \ ^{\circ}C^{(4)}$         | - 1 | -   | 1   | %    |

| t <sub>su(HSI)</sub> <sup>(2)</sup> | HSI oscillator startup time           | -                                    | -   | 2.2 | 4   | μs   |

| I <sub>DD(HSI)</sub> <sup>(2)</sup> |                                       | -                                    | -   | 60  | 80  | μA   |

| Table 45. HSI oscillator characteristics (1 | able 45 | HSLO | scillator | charact | teristics <sup>1</sup> | (1) |

|---------------------------------------------|---------|------|-----------|---------|------------------------|-----|

|---------------------------------------------|---------|------|-----------|---------|------------------------|-----|

1. V<sub>DD</sub> = 3.3 V, T<sub>A</sub> = –40 to 105 °C unless otherwise specified.

2. Guaranteed by design.

3. Guaranteed by characterization results.

4. Factory calibrated, parts not soldered.

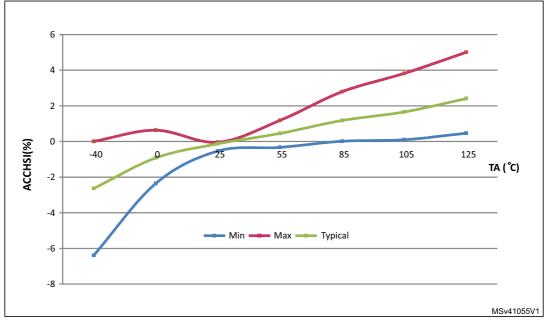

#### Figure 32. ACCHSI versus temperature

1. Guaranteed by characterization results.

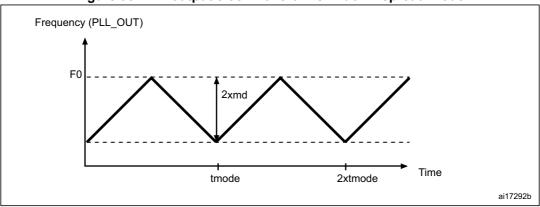

Figure 35. PLL output clock waveforms in down spread mode

#### 5.3.13 MIPI D-PHY characteristics

The parameters given in *Table 51* and *Table 52* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                                | Parameter                                                                   | Conditions         | Min  | Тур | Max     | Unit |  |

|---------------------------------------|-----------------------------------------------------------------------------|--------------------|------|-----|---------|------|--|

| Hi-Speed Input/Output Characteristics |                                                                             |                    |      |     |         |      |  |

| U <sub>INST</sub>                     | UI instantaneous                                                            | -                  | 2    | -   | 12.5    | ns   |  |

| V <sub>CMTX</sub>                     | HS transmit common mode voltage                                             | -                  | 150  | 200 | 250     |      |  |

| ΔV <sub>CMTX</sub>                    | $V_{\mbox{CMTX}}$ mismatch when output is Differential-1 or Differential-0  | -                  | -    | -   | 5       |      |  |

| V <sub>OD</sub>                       | HS transmit differential voltage                                            | -                  | 140  | 200 | 270     | mV   |  |

| ΔV <sub>OD</sub>                      | V <sub>OD</sub> mismatch when output is<br>Differential-1 or Differential-0 | -                  | -    | -   | 14      |      |  |

| V <sub>OHHS</sub>                     | HS output high voltage                                                      | -                  | -    | -   | 360     |      |  |

| Z <sub>OS</sub>                       | Single ended output<br>impedance                                            | -                  | 40   | 50  | 62.5    | Ω    |  |

| ΔZ <sub>OS</sub>                      | Single ended output<br>impedance mismatch                                   | -                  | -    | -   | 10      | %    |  |

| t <sub>HSr</sub> & t <sub>HSf</sub>   | 20%-80% rise and fall time                                                  | -                  | 100  | -   | 0.35*UI | ps   |  |

|                                       | LP Receiver                                                                 | Input Characteris  | tics |     |         |      |  |

| V <sub>IL</sub>                       | Logic 0 input voltage (not in<br>ULP State)                                 | -                  | -    | -   | 550     |      |  |

| V <sub>IL-ULPS</sub>                  | Logic 0 input voltage in ULP<br>State                                       | -                  | -    | -   | 300     | mV   |  |

| V <sub>IH</sub>                       | Input high level voltage                                                    | -                  | 880  | -   | -       |      |  |

| V <sub>hys</sub>                      | Voltage hysteresis                                                          | -                  | 25   | -   | -       |      |  |

|                                       | LP Emitter (                                                                | Dutput Characteris | tics |     |         |      |  |

Table 51. MIPI D-PHY characteristics<sup>(1)</sup>

| -      |                              | <b>,</b> ADO                                                                                                       |     |                    |      |

|--------|------------------------------|--------------------------------------------------------------------------------------------------------------------|-----|--------------------|------|

| Symbol | Parameter                    | Test conditions                                                                                                    | Тур | Max <sup>(1)</sup> | Unit |

| ET     | Total unadjusted error       |                                                                                                                    | ±4  | ±7                 |      |

| EO     | Offset error                 | f <sub>ADC</sub> =36 MHz,                                                                                          | ±2  | ±3                 |      |

| EG     | Gain error                   | V <sub>DDA</sub> = 2.4 to 3.6 V,<br>V <sub>REF</sub> = 1.7 to 3.6 V<br>V <sub>DDA</sub> - V <sub>REF</sub> < 1.2 V | ±3  | ±6                 | LSB  |

| ED     | Differential linearity error |                                                                                                                    | ±2  | ±3                 |      |

| EL     | Integral linearity error     |                                                                                                                    | ±3  | ±6                 |      |

Table 74. ADC static accuracy at f<sub>ADC</sub> = 36 MHz

1. Guaranteed by characterization results.

| Table 75. ADC dynamic accuracy at f <sub>ADC</sub> = 18 MHz - limited test conditions <sup>(1)</sup> |  |

|------------------------------------------------------------------------------------------------------|--|

|------------------------------------------------------------------------------------------------------|--|

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =18 MHz     | 10.3 | 10.4 | -   | bits |

| SINAD  | Signal-to-noise and distortion ratio | $V_{DDA} = V_{REF+} = 1.7 V$ | 64   | 64.2 | -   |      |

| SNR    | Signal-to-noise ratio                | Input Frequency = 20 KHz     | 64   | 65   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 67 | - 72 | -   |      |

1. Guaranteed by characterization results.

#### Table 76. ADC dynamic accuracy at $f_{ADC}$ = 36 MHz - limited test conditions<sup>(1)</sup>

| Symbol | Parameter                            | Test conditions              | Min  | Тур  | Max | Unit |

|--------|--------------------------------------|------------------------------|------|------|-----|------|

| ENOB   | Effective number of bits             | f <sub>ADC</sub> =36 MHz     | 10.6 | 10.8 | -   | bits |

| SINAD  | Signal-to noise and distortion ratio | $V_{DDA} = V_{REF+} = 3.3 V$ | 66   | 67   | -   |      |

| SNR    | Signal-to noise ratio                | Input Frequency = 20 KHz     | 64   | 68   | -   | dB   |

| THD    | Total harmonic distortion            | Temperature = 25 °C          | - 70 | - 72 | -   |      |

1. Guaranteed by characterization results.

Note: ADC accuracy vs. negative injection current: injecting a negative current on any analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to analog pins which may potentially inject negative currents.

Any positive injection current within the limits specified for  $I_{INJ(PIN)}$  and  $\Sigma I_{INJ(PIN)}$  in Section 5.3.20 does not affect the ADC accuracy.

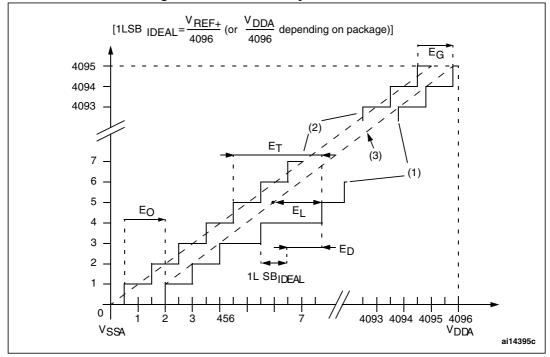

Figure 41. ADC accuracy characteristics

- 1. See also Table 73.

- 2. Example of an actual transfer curve.

- 3. Ideal transfer curve.

- 4 End point correlation line.

$E_T$  = Total Unadjusted Error: maximum deviation between the actual and the ideal transfer curves. EO = Offset Error: deviation between the first actual transition and the first ideal one. 5.

EG = Gain Error: deviation between the last ideal transition and the last actual one. ED = Differential Linearity Error: maximum deviation between actual steps and the ideal one. EL = Integral Linearity Error: maximum deviation between any actual transition and the end point correlation line.

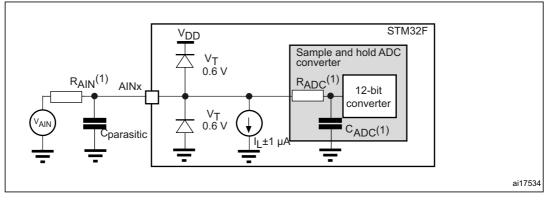

- Refer to Table 71 for the values of  $\mathsf{R}_{AIN},\,\mathsf{R}_{ADC}$  and  $\mathsf{C}_{ADC}$ 1.

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 5 pF). A high  $C_{parasitic}$  value downgrades conversion accuracy. To remedy this, f<sub>ADC</sub> should be reduced. 2.

| Symbol                      | Symbol Parameter                         |                          | Max | Unit |

|-----------------------------|------------------------------------------|--------------------------|-----|------|

| t <sub>(CLK)</sub>          | FMC_CLK period                           | 2T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)        | -                        | 2   |      |

| t <sub>(CLKH-NExH)</sub>    | FMC_CLK high to FMC_NEx high (x= 02)     | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low              | -                        | 0.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high             | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)     | -                        | 2.5 |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | T <sub>HCLK</sub>        | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                        | 1.5 |      |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> + 1    | -   |      |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                        | 3.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | -                        | 2   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> + 1    | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 3.5                      | -   |      |

Table 111. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

#### NAND controller waveforms and timings

*Figure 69* through *Figure 72* represent synchronous waveforms, and *Table 112* and *Table 113* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

|         |                         |                                   | •           |     | •           |      |

|---------|-------------------------|-----------------------------------|-------------|-----|-------------|------|

| Symbol  | Parameter               | Conditions                        | Min         | Тур | Мах         | Unit |

| tw(CKH) | Quad-SPI clock high and |                                   | t(CK)/2 - 1 | -   | t(CK)/2     |      |

| tw(CKL) | low time                | -                                 | t(CK)/2     | -   | t(CK)/2 + 1 |      |

| ts(IN)  | Data input setup time   |                                   | 0.5         | -   | -           |      |

| th(IN)  | Data input hold time    | -                                 | 3           | -   | -           | ns   |

| tv(OUT) | Data output valid time  | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>  | -           | 1.5 | 3.5         |      |

|         |                         | 1.71 V <v<sub>DD&lt;3.6 V</v<sub> | -           | 1.5 | 2           |      |

| th(OUT) | Data output hold time   | -                                 | 0.5         | -   | -           |      |

Table 118. Quad-SPI characteristics (continued)in SDR mode<sup>(1)</sup> (continued)

1. Guaranteed by characterization results.

| Symbol                | Parameter                   | Conditions                                     | Min                           | Тур                           | Max                           | Unit    |

|-----------------------|-----------------------------|------------------------------------------------|-------------------------------|-------------------------------|-------------------------------|---------|

|                       |                             | 2.7 V <v<sub>DD&lt;3.6 V<br/>CL=20 pF</v<sub>  | -                             | -                             | 80                            |         |

| Fck1/t(CK)            | Quad-SPI clock<br>frequency | 1.8 V <v<sub>DD&lt;3.6 V<br/>CL=15 pF</v<sub>  | -                             | -                             | 80                            | MH<br>z |

|                       |                             | 1.71 V <v<sub>DD&lt;3.6 V<br/>CL=10 pF</v<sub> | -                             | -                             | 80                            |         |

| tw(CKH)               | Quad-SPI clock high         |                                                | t(CK)/2 - 1                   | -                             | t(CK)/2                       |         |

| tw(CKL)               | and low time                | -                                              | t(CK)/2                       | -                             | t(CK)/2<br>+ 1                |         |

| ts(IN),               | Data input actus time       | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | 0.75                          | -                             | -                             |         |

| tsf(IN)               | Data input setup time       | 1.71 V <v<sub>DD&lt;2 V</v<sub>                | 0.5                           | -                             | -                             |         |

| thr(IN),              | Data input hold time        | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | 2                             | -                             | -                             |         |

| thf(IN)               | Data input hold time        | 1.71 V <v<sub>DD&lt;2 V</v<sub>                | 3                             | -                             | -                             |         |

|                       |                             | 2.7 V <v<sub>DD&lt;3.6 V</v<sub>               | -                             | 8.5                           | 10                            | ns      |

| tvr(OUT),<br>tvf(OUT) | Data output valid time      | 1.71 V <v<sub>DD&lt;3.6 V<br/>DHHC=0</v<sub>   | -                             | 8                             | 12                            |         |

|                       |                             | DHHC=1<br>Pres=1, 2                            | -                             | T <sub>HCLK</sub> /2 +<br>1.5 | T <sub>HCLK</sub> /2<br>+ 2.5 |         |

| thr(OUT)              |                             | DHHC=0                                         | 7.5                           | -                             | -                             | ]       |

| thr(OUT),<br>thf(OUT) | Data output hold time       | DHHC=1<br>Pres=1, 2                            | T <sub>HCLK</sub> /2<br>+ 0.5 | -                             | -                             |         |

| Table 119. | Quad SPI | characteristics in | DDR mode <sup>(1)</sup> |

|------------|----------|--------------------|-------------------------|

|------------|----------|--------------------|-------------------------|

1. Guaranteed by characterization results.

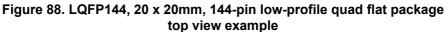

#### LQFP144 device marking

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering samples to run qualification activity.

# 6.5 WLCSP 180-bump, 5.5 x 6 mm, wafer level chip scale package information

e1 A1 BALL LOCATION // bbb Z D G -DETAIL A e2 F A1 ORIENTATION REFERENCE -▶lel A2 -A3 TOP VIEW BOTTOM VIEW SIDE VIEW BUMP 🛆 eee Z Ż Notes 1&2 øb(180x) Øccc@ZXY Øddd@Z SEATING PLANE DETAIL A ROTATED 90° A05G\_WLCSP180\_ME\_V1

Figure 95. WLCSP 180-bump, 5.5 x 6 mm, 0.4 mm pitch wafer level chip scale package outline

1. Drawing is not to scale.

## 7 Ordering information

#### Table 136. Ordering information scheme Example: STM32 F 77x V GΤ 6 ххх **Device family** STM32 = ARM-based 32-bit microcontroller Product type F = general-purpose **Device subfamily** 777= STM32F777xx, USB OTG FS/HS, camera interface, Ethernet, LCD-TFT, cryptographic acceleration 778 = STM32F778Ax, USB OTG FS/HS, camera interface, DSI host, WLCSP with internal regulator OFF, cryptographic acceleration 779= STM32F779xx, USB OTG FS/HS, camera interface, Ethernet, DSI host, cryptographic acceleration Pin count V = 100 pins Z = 144 pins I = 176 pins A = 180 pins B = 208 pins N = 216 pins Flash memory size G = 1024 Kbytes of Flash memory I = 2048 Kbytes of Flash memory Package T = LQFP K = UFBGA H = TFBGA Y = WLCSP **Temperature range** 6 = Industrial temperature range, -40 to 85 °C. 7 = Industrial temperature range, -40 to 105 °C. Options

xxx = programmed parts

TR = tape and reel

For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST sales office.