Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                                                          |

|----------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                                   |

| Core Processor             | ARM® Cortex®-M7                                                                                          |

| Core Size                  | 32-Bit Single-Core                                                                                       |

| Speed                      | 216MHz                                                                                                   |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB OTG |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                        |

| Number of I/O              | 129                                                                                                      |

| Program Memory Size        | 2MB (2M x 8)                                                                                             |

| Program Memory Type        | FLASH                                                                                                    |

| EEPROM Size                | -                                                                                                        |

| RAM Size                   | 512K x 8                                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type            | Internal                                                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type              | Surface Mount                                                                                            |

| Package / Case             | 180-UFBGA, WLCSP                                                                                         |

| Supplier Device Package    | 180-WLCSP (5.5x6)                                                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f779aiy6tr                                  |

|                            |                                                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.3 Embedded Flash memory

The STM32F777xx, STM32F778Ax and STM32F779xx devices embed a Flash memory of up to 2 Mbytes available for storing programs and data. The Flash interface features:

- Single /or Dual bank operating modes,

- Read-While-Write (RWW) in Dual bank mode.

#### 2.4 CRC (cyclic redundancy check) calculation unit

The CRC (cyclic redundancy check) calculation unit is used to get a CRC code using a configurable generator polynomial value and size.

Among other applications, CRC-based techniques are used to verify data transmission or storage integrity. In the scope of the EN/IEC 60335-1 standard, they offer a means of verifying the Flash memory integrity. The CRC calculation unit helps compute a signature of the software during runtime, to be compared with a reference signature generated at link-time and stored at a given memory location.

#### 2.5 Embedded SRAM

All the devices feature:

- System SRAM up to 512 Kbytes:

- SRAM1 on AHB bus Matrix: 368 Kbytes

- SRAM2 on AHB bus Matrix: 16 Kbytes

- DTCM-RAM on TCM interface (Tighly Coupled Memory interface): 128 Kbytes for critical real-time data.

- Instruction RAM (ITCM-RAM) 16 Kbytes:

- It is mapped on TCM interface and reserved only for CPU Execution/Instruction useful for critical real-time routines.

The Data TCM RAM is accessible by the GP-DMAs and peripherals DMAs through specific AHB slave of the CPU. The instruction TCM RAM is reserved only for CPU. It is accessed at CPU clock speed with 0 wait states.

• 4 Kbytes of backup SRAM

This area is accessible only from the CPU. Its content is protected against possible unwanted write accesses, and is retained in Standby or VBAT mode.

#### 2.6 AXI-AHB bus matrix

The STM32F777xx, STM32F778Ax and STM32F779xx system architecture is based on 2 sub-systems:

- An AXI to multi AHB bridge converting AXI4 protocol to AHB-Lite protocol:

- 3x AXI to 32-bit AHB bridges connected to AHB bus matrix

- 1x AXI to 64-bit AHB bridge connected to the embedded Flash memory

- A multi-AHB Bus-Matrix

- The 32-bit multi-AHB bus matrix interconnects all the masters (CPU, DMAs, Ethernet, USB HS, LCD-TFT, and DMA2D) and the slaves (Flash memory, RAM,

#### 2.13 JPEG codec (JPEG)

The JPEG codec provides an fast and simple hardware compressor and decompressor of JPEG images with full management of JPEG headers.

The JPEG codec main features:

- 8-bit/channel pixel depths

- Single clock per pixel encoding and decoding

- Support for JPEG header generation and parsing

- Up to four programmable quantization tables

- Fully programmable Huffman tables (two AC and two DC)

- Fully programmable minimum coded unit (MCU)

- Encode/decode support (non simultaneous)

- Single clock Huffman coding and decoding

- Two-channel interface: Pixel/Compress In, Pixel/Compressed Out

- Stallable design

- Support for single, greyscale component

- Functionality to enable/disable header processing

- Internal register interface

- Fully synchronous design

- Configured for high-speed decode mode

#### 2.14 External interrupt/event controller (EXTI)

The external interrupt/event controller consists of 25 edge-detector lines used to generate interrupt/event requests. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the Internal APB2 clock period. Up to 168 GPIOs can be connected to the 16 external interrupt lines.

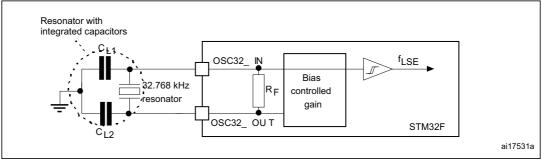

#### 2.15 Clocks and startup

On reset the 16 MHz internal HSI RC oscillator is selected as the default CPU clock. The 16 MHz internal RC oscillator is factory-trimmed to offer 1% accuracy. The application can then select as system clock either the RC oscillator or an external 4-26 MHz clock source. This clock can be monitored for failure. If a failure is detected, the system automatically switches back to the internal RC oscillator and a software interrupt is generated (if enabled). This clock source is input to a PLL thus allowing to increase the frequency up to 216 MHz. Similarly, full interrupt management of the PLL clock entry is available when necessary (for example if an indirectly used external oscillator fails).

Several prescalers allow the configuration of the two AHB buses, the high-speed APB (APB2) and the low-speed APB (APB1) domains. The maximum frequency of the two AHB buses is 216 MHz while the maximum frequency of the high-speed APB domains is 108 MHz. The maximum allowed frequency of the low-speed APB domain is 54 MHz.

|         |         |          | I       | Pin N   | umbe     | ər                      |         |                |          |                                |          |               |            |                                                                                                                     |                                            |

|---------|---------|----------|---------|---------|----------|-------------------------|---------|----------------|----------|--------------------------------|----------|---------------|------------|---------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

|         | S       | TM32     | :F777   | xx      |          |                         |         | F778/<br>F779: |          | reset                          |          |               |            |                                                                                                                     |                                            |

| LQFP100 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176 | LQFP208        | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes      | Alternate functions                                                                                                 | Additional<br>functions                    |

| 3       | 3       | B1       | 3       | 3       | A1       | C12                     | 3       | 3              | A1       | PE4                            | I/O      | FT            | -          | TRACED1, SPI4_NSS,<br>SAI1_FS_A,<br>DFSDM1_DATIN3,<br>FMC_A20, DCMI_D4,<br>LCD_B0, EVENTOUT                         | -                                          |

| 4       | 4       | B2       | 4       | 4       | B1       | D12                     | 4       | 4              | B1       | PE5                            | I/O      | FT            | -          | TRACED2, TIM9_CH1,<br>SPI4_MISO, SAI1_SCK_A,<br>DFSDM1_CKIN3,<br>FMC_A21, DCMI_D6,<br>LCD_G0, EVENTOUT              | -                                          |

| 5       | 5       | В3       | 5       | 5       | B2       | E11                     | 5       | 5              | B2       | PE6                            | I/O      | FT            | -          | TRACED3, TIM1_BKIN2,<br>TIM9_CH2, SPI4_MOSI,<br>SAI1_SD_A,<br>SAI2_MCLK_B, FMC_A22,<br>DCMI_D7, LCD_G1,<br>EVENTOUT | -                                          |

| -       | -       | -        | -       | -       | G6       | -                       | -       | -              | G6       | VSS                            | S        | -             | -          | -                                                                                                                   | -                                          |

| -       | -       | -        | -       | -       | F5       | -                       | -       | -              | F5       | VDD                            | S        | -             | -          | -                                                                                                                   | -                                          |

| 6       | 6       | C1       | 6       | 6       | C1       | C13                     | 6       | 6              | C1       | VBAT                           | s        | -             | -          | -                                                                                                                   | -                                          |

| -       | -       | D2       | 7       | 7       | C2       | NC                      | 7       | 7              | C2       | PI8                            | 1/0      | FT            | (2)        | EVENTOUT                                                                                                            | RTC_TAMP<br>2/RTC_TS/<br>WKUP5             |

| 7       | 7       | D1       | 8       | 8       | D1       | D13                     | 8       | 8              | D1       | PC13                           | I/O      | FT            | (2)        | EVENTOUT                                                                                                            | RTC_TAMP<br>1/RTC_TS/<br>RTC_OUT/<br>WKUP4 |

| 8       | 8       | E1       | 9       | 9       | E1       | E12                     | 9       | 9              | E1       | PC14-<br>OSC32_I<br>N          | I/O      | FT            | (2)<br>(3) | EVENTOUT                                                                                                            | OSC32_IN                                   |

| 9       | 9       | F1       | 10      | 10      | F1       | E13                     | 10      | 10             | F1       | PC15-<br>OSC32_O<br>UT         | I/O      | FT            | (2)<br>(3) | EVENTOUT                                                                                                            | OSC32_OU<br>T                              |

| -       | -       | -        | -       | -       | G5       | -                       | -       | -              | G5       | VDD                            | S        | -             | -          | -                                                                                                                   | -                                          |

# Table 10. STM32F777xx, STM32F778Ax and STM32F779xx pin and ball definitions (continued)

Т

٦

|         |         |          | I       | Pin N   | umbe     | ər                      |              |         |          |                                |          |               |       |                                                                                                                                          |                         |

|---------|---------|----------|---------|---------|----------|-------------------------|--------------|---------|----------|--------------------------------|----------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         | S       | TM32     | F777    | xx      |          |                         | M321<br>M321 |         |          | reset                          |          |               |       |                                                                                                                                          |                         |

| LQFP100 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176      | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                      | Additional<br>functions |

| 65      | 98      | G14      | 117     | 140     | G14      | G8                      | 121          | 140     | G14      | PC8                            | I/O      | FT            | -     | TRACED1, TIM3_CH3,<br>TIM8_CH3, UART5_RTS,<br>USART6_CK,<br>FMC_NE2/FMC_NCE,<br>SDMMC1_D0, DCMI_D2,<br>EVENTOUT                          |                         |

| 66      | 99      | F14      | 118     | 141     | F14      | E1                      | 122          | 141     | F14      | PC9                            | I/O      | FT            | -     | MCO2, TIM3_CH4,<br>TIM8_CH4, I2C3_SDA,<br>I2S_CKIN, UART5_CTS,<br>QUADSPI_BK1_IO0,<br>LCD_G3, SDMMC1_D1,<br>DCMI_D3, LCD_B2,<br>EVENTOUT |                         |

| 67      | 100     | F15      | 119     | 142     | F15      | E2                      | 123          | 142     | F15      | PA8                            | I/O      | FT            | -     | MCO1, TIM1_CH1,<br>TIM8_BKIN2, I2C3_SCL,<br>USART1_CK,<br>OTG_FS_SOF, CAN3_RX,<br>UART7_RX, LCD_B3,<br>LCD_R6, EVENTOUT                  | -                       |

| 68      | 101     | E15      | 120     | 143     | E15      | F4                      | 124          | 143     | E15      | PA9                            | I/O      | FT            | -     | TIM1_CH2, I2C3_SMBA,<br>SPI2_SCK/I2S2_CK,<br>USART1_TX, DCMI_D0,<br>LCD_R5, EVENTOUT                                                     | OTG_FS_V<br>BUS         |

| 69      | 102     | D15      | 121     | 144     | D15      | F5                      | 125          | 144     | D15      | PA10                           | I/O      | FT            | -     | TIM1_CH3, USART1_RX,<br>LCD_B4, OTG_FS_ID,<br>MDIOS_MDIO, DCMI_D1,<br>LCD_B1, EVENTOUT                                                   | -                       |

| 70      | 103     | C15      | 122     | 145     | C15      | E3                      | 126          | 145     | C15      | PA11                           | I/O      | FT            | -     | TIM1_CH4,<br>SPI2_NSS/I2S2_WS,<br>UART4_RX,<br>USART1_CTS, CAN1_RX,<br>OTG_FS_DM, LCD_R4,<br>EVENTOUT                                    | -                       |

## Table 10. STM32F777xx, STM32F778Ax and STM32F779xx pin and ball definitions (continued)

| STM     |

|---------|

| 32F77   |

|         |

| STM32   |

| F778Ax  |

| STM32   |

| 2F779xx |

|         |

AF14

LCD

LCD\_G7

LCD B2

LCD B3

LCD\_B1

LCD R0

LCD\_B0

DCMI V

SYNC

DCMI\_D 2

DCMI\_D

3

\_

\_

-

FMC\_NE

2/FMC\_ NCE

FMC\_NE 3

-

FMC\_NE

4

FMC\_A2

4

FMC\_A2

5

FMC\_SD DCMI\_D NCAS 13

SDMMC2

\_D0

SDMMC2

\_D1

ETH MI

TX\_EN/E

TH\_RMII

TX EN

SDMMC2

\_D3

ETH MI

TXD0/ET

H RMII T

\_XD0\_ ETH\_MII\_

TXD1/ET

H\_RMII\_T

\_XD1\_

-

AF15

SYS

EVEN

TOUT

EVEN

TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN TOUT

EVEN

TOUT

EVEN

TOUT

Pinouts and pin description

|     |                           | Т        | able 12.                                   | STM32F                        |                                                        |                                                                | 778Ax a<br>bing (co                                                            |                                                               |                                                    | xx altern                                                              | ate                          |                                                |                  |

|-----|---------------------------|----------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|

| AF0 | AF1                       | AF2      | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             |

| SYS | 12C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI |

| -   | -                         | -        | -                                          | -                             | SPI6_NS<br>S                                           | -                                                              | SPDIF_R<br>X2                                                                  | USART6<br>_RTS                                                | -                                                  | -                                                                      | ETH_PPS<br>_OUT              | FMC_SD<br>CLK                                  | -                |

-

-

-

-

-

-

-

SPI1 MI

sō

SPI1 NS

S/I2S1

WS

SPI1\_SC

K/I251

CK

SPI6\_MI

sō

SPI6\_SC

ĸ

SPI6\_M

osī

-

-

-

-

-

-

-

-

SPDIF\_R

X3

-

SPDIF\_R

X0

SPDIF\_R

X1

-

-

-

QUADSP I\_BK2\_IO

2

LCD G3

-

LCD\_B4

-

QUADSP

I\_BK2\_IO

3

-

USART6

\_RX

-

-

USART6

\_RTS

USART6

USART6

\_TX

USART6

\_CTS

\_CTS

SAI2\_FS\_ B

SAI2\_SD\_ B

SDMMC2

\_D2

-

\_

\_

-

# DocID028294 Rev 4

101/255

Port

PG8

PG9

PG10

PG11

PG12

PG13

PG14

PG15

Port G

-

-

-

-

TRACED

0

TRACED

1

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

LPTIM1\_I N1

LPTIM1

OUT

LPTIM1\_E

TR

-

| လု   |

|------|

| ML   |

| 32F  |

| 11   |

| X    |

| ST   |

| FM3  |

| 2F7  |

| 78/  |

| ×    |

| STI  |

| M32  |

| F7   |

| 79x) |

| ×    |

Pinouts and pin description

|        |      | AF0 | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             | AF14          | AF       |

|--------|------|-----|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|---------------|----------|

| Po     | ort  | SYS | I2C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD           | s        |

| Port H | PH14 | -   | -                         | -            | TIM8_CH<br>2N                              | -                             | -                                                      | -                                                              | -                                                                              | UART4_<br>RX                                                  | CAN1_R<br>X                                        | -                                                                      | -                            | FMC_D2<br>2                                    | DCMI_D<br>4      | LCD_G3        | E'<br>T( |

| FOILH  | PH15 | -   | -                         | -            | TIM8_CH<br>3N                              | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>3                                    | DCMI_D<br>11     | LCD_G4        | E'<br>T( |

|        | PI0  | -   | -                         | TIM5_C<br>H4 | -                                          | -                             | SPI2_NS<br>S/I2S2_<br>WS                               | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>4                                    | DCMI_D<br>13     | LCD_G5        | E'<br>T( |

|        | PI1  | -   | -                         | -            | TIM8_BKI<br>N2                             | -                             | SPI2_SC<br>K/I2S2_<br>CK                               | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>5                                    | DCMI_D<br>8      | LCD_G6        | E<br>T   |

|        | PI2  | -   | -                         | -            | TIM8_CH<br>4                               | -                             | SPI2_MI<br>SO                                          | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>6                                    | DCMI_D<br>9      | LCD_G7        | E<br>T   |

|        | PI3  | -   | -                         | -            | TIM8_ET<br>R                               | -                             | SPI2_M<br>OSI/I2S2<br>_SD                              | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D2<br>7                                    | DCMI_D<br>10     | -             | E'<br>T( |

|        | Pl4  | -   | -                         | -            | TIM8_BKI<br>N                              | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_MC<br>K_A                                                         | -                            | FMC_NB<br>L2                                   | DCMI_D<br>5      | LCD_B4        | E<br>T   |

| Port I | PI5  | -   | -                         | -            | TIM8_CH<br>1                               | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_SC<br>K_A                                                         | -                            | FMC_NB<br>L3                                   | DCMI_V<br>SYNC   | LCD_B5        | E<br>T   |

|        | Pl6  | -   | -                         | -            | TIM8_CH<br>2                               | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_SD_<br>A                                                          | -                            | FMC_D2<br>8                                    | DCMI_D<br>6      | LCD_B6        | E'<br>T( |

|        | PI7  | -   | -                         | -            | TIM8_CH<br>3                               | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_FS_<br>A                                                          | -                            | FMC_D2<br>9                                    | DCMI_D<br>7      | LCD_B7        | E'<br>T( |

|        | PI8  | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | -                                              | -                | -             | E'<br>T( |

|        | PI9  | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | UART4_<br>RX                                                  | CAN1_R<br>X                                        | -                                                                      | -                            | FMC_D3<br>0                                    | -                | LCD_VS<br>YNC | E'<br>T( |

|        | PI10 | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | ETH_MII_<br>RX_ER            | FMC_D3<br>1                                    | -                | LCD_HS<br>YNC | E'<br>T( |

|        | PI11 | -   | -                         | -            | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | LCD_G6                                             | OTG_HS_<br>ULPI DIR                                                    | -                            | -                                              | -                | -             | E'<br>T( |

- 7. The over-drive mode is not supported when the internal regulator is OFF.

- 8. To sustain a voltage higher than VDD+0.3, the internal Pull-up and Pull-Down resistors must be disabled

- 9. If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ .

- 10. In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub>.

| Operating<br>power supply<br>range                | ADC operation                     | Maximum Flash<br>memory access<br>frequency with<br>no wait states<br>(f <sub>Flashmax</sub> ) | Maximum HCLK<br>frequency vs Flash<br>memory wait states<br>(1)(2) | I/O operation          | Possible Flash<br>memory<br>operations        |

|---------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------|-----------------------------------------------|

| $V_{DD}$ =1.7 to 2.1 V <sup>(3)</sup>             | Conversion time<br>up to 1.2 Msps | 20 MHz                                                                                         | 180 MHz with 8 wait<br>states and over-drive<br>OFF                | No I/O<br>compensation | 8-bit erase and<br>program<br>operations only |

| V <sub>DD</sub> = 2.1 to<br>2.4 V                 | Conversion time<br>up to 1.2 Msps | 22 MHz                                                                                         | 216 MHz with 9 wait<br>states and over-drive<br>ON                 | No I/O<br>compensation | 16-bit erase and program operations           |

| V <sub>DD</sub> = 2.4 to<br>2.7 V                 | Conversion time<br>up to 2.4 Msps | 24 MHz                                                                                         | 216 MHz with 8 wait<br>states and over-drive<br>ON                 | I/O compensation works | 16-bit erase and program operations           |

| $V_{DD} = 2.7 \text{ to}$<br>3.6 V <sup>(4)</sup> | Conversion time<br>up to 2.4 Msps | 30 MHz                                                                                         | 216 MHz with 6 wait<br>states and over-drive<br>ON                 | I/O compensation works | 32-bit erase and program operations           |

1. Applicable only when the code is executed from Flash memory. When the code is executed from RAM, no wait state is required.

Thanks to the ART accelerator on ITCM interface and L1-cache on AXI interface, the number of wait states given here does not impact the execution speed from Flash memory since the ART accelerator or L1-cache allows to achieve a performance equivalent to 0-wait state program execution.

- V<sub>DD</sub>/V<sub>DDA</sub> minimum value of 1.7 V is obtained with the use of an external power supply supervisor (refer to Section 2.18.2: Internal reset OFF).

- 4. The voltage range for USB full speed PHYs can drop down to 2.7 V. However the electrical characteristics of D- and D+ pins will be degraded between 2.7 and 3 V.

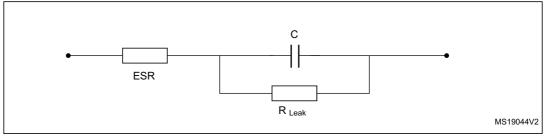

#### 5.3.2 VCAP1/VCAP2 external capacitor

Stabilization for the main regulator is achieved by connecting an external capacitor  $C_{EXT}$  to the VCAP1/VCAP2 pins.  $C_{EXT}$  is specified in *Table 19*.

#### Figure 27. External capacitor C<sub>EXT</sub>

1. Legend: ESR is the equivalent series resistance.

# Table 30. Typical and maximum current consumption in Run mode, code with data processing running from Flash memory (Dual bank mode) on ITCM interface (ART disabled), regulator ON

| Cumhal          | Demonster                        | Conditions                                   | £ (MIL-)                | True |           | Max <sup>(1)</sup> |           | 11   |

|-----------------|----------------------------------|----------------------------------------------|-------------------------|------|-----------|--------------------|-----------|------|

| Symbol          | Parameter                        | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | TA= 25 °C | TA=85 °C           | TA=105 °C | Unit |

|                 |                                  |                                              | 216                     | 191  | 218       | 255                | -         |      |

|                 |                                  |                                              | 200                     | 178  | 195       | 241                | 269       |      |

|                 |                                  |                                              | 180                     | 164  | 179       | 214                | 236       |      |

|                 |                                  | All peripherals<br>enabled <sup>(2)(3)</sup> | 168                     | 147  | 160       | 192                | 212       |      |

|                 |                                  |                                              | 144                     | 121  | 130       | 157                | 175       |      |

|                 |                                  |                                              | 60                      | 60   | 66        | 93                 | 111       |      |

|                 | Supply<br>current in<br>RUN mode |                                              | 25                      | 28   | 33        | 59                 | 77        | mA   |

| I <sub>DD</sub> |                                  |                                              | 216                     | 93   | 104       | 150                | -         |      |

|                 |                                  |                                              | 200                     | 87   | 97        | 144                | 171       |      |

|                 |                                  |                                              | 180                     | 83   | 92        | 126                | 148       |      |

|                 |                                  | All peripherals<br>disabled <sup>(3)</sup>   | 168                     | 75   | 82        | 114                | 134       |      |

|                 |                                  |                                              | 144                     | 65   | 71        | 97                 | 115       |      |

|                 |                                  |                                              | 60                      | 35   | 40        | 66                 | 84        |      |

|                 |                                  |                                              | 25                      | 16   | 20        | 47                 | 64        |      |

1. Guaranteed by characterization results, unless otherwise specified.

2. When analog peripheral blocks such as ADCs, DACs, HSE, LSE, HSI, or LSI are ON, an additional power consumption should be considered.

3. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| _        |                          |         | I <sub>DD</sub> (Typ) <sup>(1)</sup> | <u> </u> | Unit   |

|----------|--------------------------|---------|--------------------------------------|----------|--------|

|          | Peripheral               | Scale 1 | Scale 2                              | Scale 3  |        |

|          | TIM1                     | 24.1    | 23.8                                 | 19.6     |        |

|          | TIM8                     | 24.5    | 24.2                                 | 20.0     |        |

|          | USART1                   | 17.7    | 17.4                                 | 14.3     |        |

|          | USART6                   | 11.9    | 11.8                                 | 9.4      |        |

|          | ADC1 <sup>(5)</sup>      | 4.5     | 4.7                                  | 3.5      |        |

|          | ADC2 <sup>(5)</sup>      | 4.5     | 4.7                                  | 3.3      |        |

|          | ADC3 <sup>(5)</sup>      | 4.5     | 4.6                                  | 3.3      |        |

|          | SDMMC1                   | 8.4     | 8.3                                  | 6.9      |        |

| APB2     | SDMMC2                   | 8.2     | 8.2                                  | 6.4      |        |

|          | SPI1/I2S1 <sup>(3)</sup> | 3.9     | 3.6                                  | 3.1      |        |

|          | SPI4                     | 3.9     | 3.6                                  | 3.1      |        |

| (up to   | SYSCFG                   | 2.5     | 2.2                                  | 1.9      | µA/MHz |

| 108 MHz) | TIM9                     | 8.0     | 8.0                                  | 6.2      |        |

|          | TIM10                    | 5.0     | 5.1                                  | 3.7      | ]      |

|          | TIM11                    | 6.9     | 6.9                                  | 5.3      |        |

|          | SPI5                     | 2.7     | 2.8                                  | 1.8      |        |

|          | SPI6                     | 3.1     | 3.2                                  | 2.2      |        |

|          | SAI1                     | 3.2     | 3.3                                  | 2.2      |        |

|          | DFSDM1                   | 10.9    | 10.7                                 | 9.0      |        |

|          | SAI2                     | 3.9     | 3.9                                  | 2.8      | 1      |

|          | MDIO                     | 7.1     | 7.0                                  | 5.8      |        |

|          | LTDC                     | 51.2    | 50.3                                 | 41.8     |        |

|          | DSI                      | 8.5     | 8.4                                  | 8.1      |        |

Table 39. Peripheral current consumption (continued)

1. When the I/O compensation cell  $\,$  is ON,  $\rm I_{DD}$  typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.75 mA per DAC channel for the analog part.

5. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

|                                |                                         |                                                | -/ (  | oona |      |      |  |  |

|--------------------------------|-----------------------------------------|------------------------------------------------|-------|------|------|------|--|--|

| Symbol                         | Parameter                               | Conditions                                     | Min   | Тур  | Мах  | Unit |  |  |

| C. orit mov                    |                                         | LSEDRV[1:0]=00<br>Low drive capability         | -   - |      |      |      |  |  |

|                                | Maximum critical crystal g <sub>m</sub> | LSEDRV[1:0]=10<br>Medium low drive capability  | -     | -    | 0.75 | uA/V |  |  |

| Gm_cnt_max                     | Maximum childar crystar g <sub>m</sub>  | LSEDRV[1:0]=01<br>Medium high drive capability | -     | -    | 1.7  | μΑνν |  |  |

|                                |                                         | LSEDRV[1:0]=11<br>High drive capability        | -     | -    | 2.7  |      |  |  |

| t <sub>SU</sub> <sup>(2)</sup> | start-up time                           | $V_{DD}$ is stabilized                         | -     | 2    | -    | s    |  |  |

| Table 44. LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz) <sup>(1)</sup> (continued) |

|-----------------------------------------------------------------------------------------------------|

|-----------------------------------------------------------------------------------------------------|

1. Guaranteed by design.

Guaranteed by characterization results. t<sub>SU</sub> is the start-up time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturer.

#### 5.3.11 PLL characteristics

The parameters given in *Table 47* and *Table 48* are derived from tests performed under temperature and  $V_{DD}$  supply voltage conditions summarized in *Table 17*.

| Symbol                               | Parameter                                    | Condition                                                                                  | s                  | Min                 | Тур  | Мах          | Unit |

|--------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|---------------------|------|--------------|------|

| f <sub>PLL_IN</sub>                  | PLL input clock <sup>(1)</sup>               | -                                                                                          |                    | 0.95 <sup>(2)</sup> | 1    | 2.10         |      |

| f <sub>PLL_OUT</sub>                 | PLL multiplier output clock                  | -                                                                                          |                    | 24                  | -    | 216          |      |

| f <sub>PLL48_OUT</sub>               | 48 MHz PLL multiplier output<br>clock        | -                                                                                          |                    | -                   | 48   | 75           | MHz  |

| f <sub>VCO_OUT</sub>                 | PLL VCO output                               | -                                                                                          |                    | 100                 | -    | 432          |      |

| +                                    | PLL lock time                                | VCO freq = 192 N                                                                           | ЛНz                | 75                  | -    | 200          |      |

| t <sub>LOCK</sub>                    |                                              | VCO freq = 432 MHz                                                                         |                    | 100                 | -    | 300          | - µs |

|                                      |                                              |                                                                                            | RMS                | -                   | 25   | -            |      |

|                                      | Cycle-to-cycle jitter                        | System clock<br>216 MHz                                                                    | peak<br>to<br>peak | -                   | ±150 | -            | _    |

|                                      | Period Jitter                                |                                                                                            | RMS                | -                   | 15   | -            |      |

| Jitter <sup>(3)</sup>                |                                              |                                                                                            | peak<br>to<br>peak | -                   | ±200 | -            | ps   |

|                                      | Main clock output (MCO) for<br>RMII Ethernet | Cycle to cycle at 50 MHz<br>on 1000 samples<br>Cycle to cycle at 25 MHz<br>on 1000 samples |                    | -                   | 32   | -            | -    |

|                                      | Main clock output (MCO) for MII<br>Ethernet  |                                                                                            |                    | -                   | 40   | -            |      |

|                                      | Bit Time CAN jitter                          | Cycle to cycle at 1 MHz on 1000 samples                                                    |                    | -                   | 330  | -            |      |

| I <sub>DD(PLL)</sub> <sup>(4)</sup>  | PLL power consumption on V <sub>DD</sub>     | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                                   |                    | 0.15<br>0.45        | -    | 0.40<br>0.75 | mA   |

| I <sub>DDA(PLL)</sub> <sup>(4)</sup> | PLL power consumption on V <sub>DDA</sub>    | VCO freq = 192 M<br>VCO freq = 432 M                                                       |                    | 0.30<br>0.55        | -    | 0.40<br>0.85 | mA   |

| Table 47. | Main PLL | characteristics |

|-----------|----------|-----------------|

|-----------|----------|-----------------|

1. Take care of using the appropriate division factor M to obtain the specified PLL input clock values. The M factor is shared between PLL and PLLI2S.

2. Guaranteed by design.

3. The use of 2 PLLs in parallel could degraded the Jitter up to +30%.

4. Guaranteed by characterization results.

#### 5.3.16 Memory characteristics

#### Flash memory

The characteristics are given at TA = -40 to 105 °C unless otherwise specified.

The devices are shipped to customers with the Flash memory erased.

| Symbol                         | Parameter                                  | Conditions                                  | Min | Тур | Max | Unit |  |  |

|--------------------------------|--------------------------------------------|---------------------------------------------|-----|-----|-----|------|--|--|

| I <sub>DD</sub> Supply current | Write / Erase 8-bit mode, $V_{DD}$ = 1.7 V | -                                           | 14  | -   |     |      |  |  |

|                                | Supply current                             | Write / Erase 16-bit mode, $V_{DD}$ = 2.1 V | -   | 17  | -   | mA   |  |  |

|                                |                                            | Write / Erase 32-bit mode, $V_{DD}$ = 3.3 V | -   | 24  | -   |      |  |  |

#### Table 55. Flash memory characteristics

### Table 56. Flash memory programming (single bank configurationnDBANK=1)

| Symbol                  | Parameter                  | Conditions                                       | Min <sup>(1)</sup> | Тур  | Max <sup>(1)</sup> | Unit |

|-------------------------|----------------------------|--------------------------------------------------|--------------------|------|--------------------|------|

| t <sub>prog</sub>       | Word programming time      | Program/erase parallelism<br>(PSIZE) = x 8/16/32 | -                  | 16   | 100 <sup>(2)</sup> | μs   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 400  | 800                |      |

| t <sub>ERASE32KB</sub>  | Sector (32 KB) erase time  | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 250  | 600                | ms   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 200  | 500                |      |

| t <sub>erase128kb</sub> | Sector (128 KB) erase time | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 1100 | 2400               |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 800  | 1400               | ms   |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 500  | 1100               |      |

|                         | Sector (256 KB) erase time | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 2.1  | 4                  |      |

| t <sub>ERASE256KB</sub> |                            | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 1.5  | 2.6                | s    |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 1    | 2                  |      |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 8       | -                  | 16   | 32                 |      |

| t <sub>ME</sub>         | Mass erase time            | Program/erase<br>parallelism (PSIZE) = x 16      | -                  | 11   | 22                 | s    |

|                         |                            | Program/erase<br>parallelism (PSIZE) = x 32      | -                  | 8    | 16                 |      |

| Symbol            | Parameter           | Conditions                                  | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |

|-------------------|---------------------|---------------------------------------------|--------------------|-----|--------------------|------|

| t <sub>BE</sub>   | Bank erase time     | Program/erase<br>parallelism (PSIZE) = x 8  | -                  | 16  | 32                 |      |

|                   |                     | Program/erase<br>parallelism (PSIZE) = x 16 | -                  | 11  | 22                 | s    |

|                   |                     | Program/erase<br>parallelism (PSIZE) = x 32 | -                  | 8   | 16                 |      |

|                   | Programming voltage | 32-bit program operation                    | 2.7                | -   | 3                  | V    |

| V <sub>prog</sub> |                     | 16-bit program operation                    | 2.1                | -   | 3.6                | V    |

|                   |                     | 8-bit program operation                     | 1.7                | -   | 3.6                | V    |

# Table 57. Flash memory programming (dual bank configurationnDBANK=0) (continued)

1. Guaranteed by characterization results.

2. The maximum programming time is measured after 100K erase operations.

| Symbol Parameter                |                                                  | Conditions                   | Min <sup>(1)</sup> | Тур | Max <sup>(1)</sup> | Unit |  |  |  |

|---------------------------------|--------------------------------------------------|------------------------------|--------------------|-----|--------------------|------|--|--|--|

| t <sub>prog</sub>               | Double word programming                          |                              | -                  | 16  | 100 <sup>(2)</sup> | μs   |  |  |  |

| t <sub>ERASE32KB</sub>          | Sector (32 KB) erase time                        | T <sub>A</sub> = 0 to +40 °C | -                  | 180 | -                  |      |  |  |  |

| t <sub>ERASE128KB</sub>         | Sector (128 KB) erase time                       | V <sub>DD</sub> = 3.3 V      | -                  | 450 | -                  | ms   |  |  |  |

| t <sub>ERASE256KB</sub>         | Sector (256 KB) erase time                       | V <sub>PP</sub> = 8.5 V      | -                  | 900 | -                  |      |  |  |  |

| t <sub>ME</sub>                 | Mass erase time                                  |                              | -                  | 6.9 | -                  | s    |  |  |  |

| V <sub>prog</sub>               | Programming voltage                              | -                            | 2.7                | -   | 3.6                | V    |  |  |  |

| V <sub>PP</sub>                 | V <sub>PP</sub> voltage range                    | -                            | 7                  | -   | 9                  | V    |  |  |  |

| I <sub>PP</sub>                 | Minimum current sunk on the $V_{\text{PP}}$ pin  | -                            | 10                 | -   | -                  | mA   |  |  |  |

| t <sub>VPP</sub> <sup>(3)</sup> | Cumulative time during which $V_{PP}$ is applied | -                            | -                  | -   | 1                  | hour |  |  |  |

Table 58. Flash memory programming with V<sub>PP</sub>

1. Guaranteed by design.

2. The maximum programming time is measured after 100K erase operations.

3. V<sub>PP</sub> should only be connected during programming/erasing.

| Symbol           | Parameter      | Conditions                                                                              | Value<br>Min <sup>(1)</sup> | Unit    |

|------------------|----------------|-----------------------------------------------------------------------------------------|-----------------------------|---------|

| N <sub>END</sub> | Endurance      | $T_A = -40$ to +85 °C (6 suffix versions)<br>$T_A = -40$ to +105 °C (7 suffix versions) | 10                          | kcycles |

|                  |                | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 85 °C                                       | 30                          |         |

| t <sub>RET</sub> | Data retention | 1 kcycle <sup>(2)</sup> at T <sub>A</sub> = 105 °C                                      | 10                          | Years   |

|                  |                | 10 kcycles <sup>(2)</sup> at T <sub>A</sub> = 55 °C                                     | 20                          |         |

DocID028294 Rev 4

- 1. Guaranteed by characterization results.

- 2. Cycling performed over the whole temperature range.

#### 5.3.17 EMC characteristics

Susceptibility tests are performed on a sample basis during device characterization.

#### Functional EMS (electromagnetic susceptibility)

While a simple application is executed on the device (toggling 2 LEDs through I/O ports). the device is stressed by two electromagnetic events until a failure occurs. The failure is indicated by the LEDs:

- Electrostatic discharge (ESD) (positive and negative) is applied to all device pins until a functional disturbance occurs. This test is compliant with the IEC 61000-4-2 standard.

- FTB: A burst of fast transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100 pF capacitor, until a functional disturbance occurs. This test is compliant with the IEC 61000-4-4 standard.

A device reset allows normal operations to be resumed.

The test results are given in *Table 60*. They are based on the EMS levels and classes defined in application note AN1709.

| Symbol            | Parameter                                                                                                                         | Conditions                                                                                                      | Level/<br>Class |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                    | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> = +25 °C, f <sub>HCLK</sub> =<br>216 MHz, conforms to IEC 61000-<br>4-2 | 2B              |

| V <sub>FTB</sub>  | Fast transient voltage burst limits to be applied through 100 pF on $V_{DD}$ and $V_{SS}$ pins to induce a functional disturbance | V <sub>DD</sub> = 3.3 V, T <sub>A</sub> =+25 °C, f <sub>HCLK</sub> =<br>168 MHz, conforms to IEC 61000-<br>4-2  | 5A              |

#### Table 60. EMS characteristics

As a consequence, it is recommended to add a serial resistor (1 k $\Omega$ ) located as close as possible to the MCU to the pins exposed to noise (connected to tracks longer than 50 mm on PCB).

#### Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

Software recommendations

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

The SDA and SCL I/O requirements are met with the following restrictions:

- The SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and V<sub>DD</sub> is disabled, but is still present.

- The 20mA output drive requirement in Fast-mode Plus is not supported. This limits the maximum load Cload supported in Fm+, which is given by these formulas:

Tr(SDA/SCL)=0.8473xRpxCload

$R_p(min)= (VDD-V_{OL}(max))/I_{OL}(max)$

Where Rp is the I2C lines pull-up. Refer to Section 5.3.20: I/O port characteristics for the I2C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to *Table 84* for the analog filter characteristics:

| Symbol          | Parameter                                                              | Min               | Мах               | Unit |

|-----------------|------------------------------------------------------------------------|-------------------|-------------------|------|

| t <sub>AF</sub> | Maximum pulse width of spikes that are suppressed by the analog filter | 50 <sup>(2)</sup> | 70 <sup>(3)</sup> | ns   |

#### Table 84. I2C analog filter characteristics<sup>(1)</sup>

1. Guaranteed by characterization results.

2. Spikes with widths below  $t_{AF(min)}$  are filtered.

3. Spikes with widths above  $t_{AF(max)}$  are not filtered.

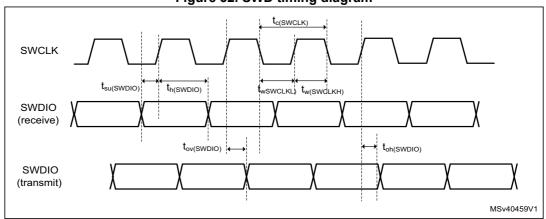

#### Figure 52. SWD timing diagram

#### SAI characteristics:

Unless otherwise specified, the parameters given in *Table 89* for SAI are derived from tests performed under the ambient temperature, f<sub>PCLKx</sub> frequency and VDD supply voltage conditions summarized in *Table 17*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 10

- Capacitive load C=30 pF

- Measurement points are performed at CMOS levels: 0.5V<sub>DD</sub>

Refer to Section 5.3.20: I/O port characteristics for more details on the input/output alternate function characteristics (SCK,SD,WS).

| Symbol                   | Parameter                          | Conditions                   | Min      | Max                   | Unit |

|--------------------------|------------------------------------|------------------------------|----------|-----------------------|------|

| f <sub>MCK</sub>         | SAI Main clock output              | -                            | 256 x 8K | 256xFs                | MHz  |

| E                        | SAI clock frequency <sup>(2)</sup> | Master data: 32 bits         | -        | 128xFs <sup>(3)</sup> | MHz  |

| F <sub>CK</sub>          | SAI Clock frequency                | Slave data: 32 bits          | -        | 128xFs                |      |

| +                        | FS valid time                      | Master mode<br>2.7≤VDD≤3.6V  | -        | 15                    |      |

| t <sub>v(FS)</sub>       |                                    | Master mode<br>1.71≤VDD≤3.6V | -        | 20                    |      |

| t <sub>su(FS)</sub>      | FS setup time                      | Slave mode                   | 7        | -                     |      |

| +                        | FS hold time                       | Master mode                  | 1        | -                     | ns   |

| t <sub>h(FS)</sub>       | FS noid time                       | Slave mode                   | 1        | -                     |      |

| t <sub>su(SD_A_MR)</sub> | Data input actus time              | Master receiver              | 3        | -                     |      |

| t <sub>su(SD_B_SR)</sub> | Data input setup time              | Slave receiver               | 3.5      | -                     |      |

| t <sub>h(SD_A_MR)</sub>  | Data input hold time               | Master receiver              | 5        | -                     |      |

| t <sub>h(SD_B_SR)</sub>  | Data input hold time               | Slave receiver               | 1        | -                     |      |

| Table | 89. | SAI | characteristics <sup>(</sup> | 1) |  |

|-------|-----|-----|------------------------------|----|--|

|-------|-----|-----|------------------------------|----|--|

| Symbol Parameter Min Max  |                                                         |                         |                          |      |  |

|---------------------------|---------------------------------------------------------|-------------------------|--------------------------|------|--|

| Cymbol                    |                                                         |                         |                          | Unit |  |

| t <sub>w(NE)</sub>        | FMC_NE low time                                         | 3T <sub>HCLK</sub> – 1  | 3T <sub>HCLK</sub> + 1   |      |  |

| $t_{v(NOE_NE)}$           | FMC_NEx low to FMC_NOE low                              | 2T <sub>HCLK</sub>      | 2T <sub>HCLK</sub> + 0.5 |      |  |

| t <sub>tw(NOE)</sub>      | FMC_NOE low time                                        | T <sub>HCLK</sub> – 1   | T <sub>HCLK</sub> + 1    |      |  |

| t <sub>h(NE_NOE)</sub>    | FMC_NOE high to FMC_NE high hold time                   | 0                       | -                        |      |  |

| t <sub>v(A_NE)</sub>      | FMC_NEx low to FMC_A valid                              | -                       | 0.5                      |      |  |

| t <sub>v(NADV_NE)</sub>   | FMC_NEx low to FMC_NADV low                             | 0                       | 0.5                      |      |  |

| t <sub>w(NADV)</sub>      | FMC_NADV low time                                       | Т <sub>НСLК</sub> – 0.5 | T <sub>HCLK</sub> +1     |      |  |

| t <sub>h(AD_NADV)</sub>   | FMC_AD(address) valid hold time after<br>FMC_NADV high) | T <sub>HCLK</sub> + 0.5 | -                        | ns   |  |

| t <sub>h(A_NOE)</sub>     | Address hold time after FMC_NOE high                    | T <sub>HCLK</sub> – 0.5 | -                        |      |  |

| t <sub>h(BL_NOE)</sub>    | FMC_BL time after FMC_NOE high                          | 0                       | -                        |      |  |

| t <sub>v(BL_NE)</sub>     | FMC_NEx low to FMC_BL valid                             | -                       | 0.5                      |      |  |

| t <sub>su(Data_NE)</sub>  | Data to FMC_NEx high setup time                         | T <sub>HCLK</sub> – 1   | -                        |      |  |

| t <sub>su(Data_NOE)</sub> | Data to FMC_NOE high setup time                         | T <sub>HCLK</sub> – 1   | -                        |      |  |

| t <sub>h(Data_NE)</sub>   | Data hold time after FMC_NEx high                       | 0                       | -                        |      |  |

| t <sub>h(Data_NOE)</sub>  | Data hold time after FMC_NOE high                       | 0                       | -                        |      |  |

Table 104. Asynchronous multiplexed PSRAM/NOR read timings<sup>(1)</sup>

1. Guaranteed by characterization results.

| Table 105. Asynchronous multiplexed PSRAM/NOR read-NWAIT timings <sup>(1)</sup> |  |

|---------------------------------------------------------------------------------|--|

|---------------------------------------------------------------------------------|--|

| ,                         |                                           |                          | U                        |      |

|---------------------------|-------------------------------------------|--------------------------|--------------------------|------|

| Symbol Parameter          |                                           | Min                      | Max                      | Unit |

| t <sub>w(NE)</sub>        | FMC_NE low time                           | 8T <sub>HCLK</sub> – 1   | 8T <sub>HCLK</sub> + 1   |      |

| t <sub>w(NOE)</sub>       | FMC_NWE low time                          | 5T <sub>HCLK</sub> – 1.5 | 5T <sub>HCLK</sub> + 0.5 | ns   |

| t <sub>su(NWAIT_NE)</sub> | FMC_NWAIT valid before FMC_NEx high       | 5T <sub>HCLK</sub> + 1.5 | -                        |      |

| t <sub>h(NE_NWAIT)</sub>  | FMC_NEx hold time after FMC_NWAIT invalid | 4T <sub>HCLK</sub> + 1   | -                        |      |

1. Guaranteed by characterization results.

| Symbol                      | Parameter Min                            |                          | Max | Unit |

|-----------------------------|------------------------------------------|--------------------------|-----|------|

| t <sub>(CLK)</sub>          | FMC_CLK period                           | 2T <sub>HCLK</sub> – 0.5 | -   |      |

| t <sub>d(CLKL-NExL)</sub>   | FMC_CLK low to FMC_NEx low (x=02)        | -                        | 2   |      |

| t <sub>(CLKH-NExH)</sub>    | FMC_CLK high to FMC_NEx high (x= 02)     | T <sub>HCLK</sub> + 0.5  | -   |      |

| t <sub>d(CLKL-NADVL)</sub>  | FMC_CLK low to FMC_NADV low              | -                        | 0.5 |      |

| t <sub>d(CLKL-NADVH)</sub>  | FMC_CLK low to FMC_NADV high             | 0                        | -   |      |

| t <sub>d(CLKL-AV)</sub>     | FMC_CLK low to FMC_Ax valid (x=1625)     | -                        | 2.5 |      |

| t <sub>d(CLKH-AIV)</sub>    | FMC_CLK high to FMC_Ax invalid (x=1625)  | T <sub>HCLK</sub>        | -   | ns   |

| t <sub>d(CLKL-NWEL)</sub>   | FMC_CLK low to FMC_NWE low               | -                        | 1.5 |      |

| t <sub>d(CLKH-NWEH)</sub>   | FMC_CLK high to FMC_NWE high             | T <sub>HCLK</sub> + 1    | -   |      |

| t <sub>d(CLKL-Data)</sub>   | FMC_D[15:0] valid data after FMC_CLK low | -                        | 3.5 |      |

| t <sub>d(CLKL-NBLL)</sub>   | FMC_CLK low to FMC_NBL low               | -                        | 2   |      |

| t <sub>d(CLKH-NBLH)</sub>   | FMC_CLK high to FMC_NBL high             | T <sub>HCLK</sub> + 1    | -   |      |

| t <sub>su(NWAIT-CLKH)</sub> | FMC_NWAIT valid before FMC_CLK high      | 2                        | -   |      |

| t <sub>h(CLKH-NWAIT)</sub>  | FMC_NWAIT valid after FMC_CLK high       | 3.5                      | -   |      |

Table 111. Synchronous non-multiplexed PSRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

#### NAND controller waveforms and timings

*Figure 69* through *Figure 72* represent synchronous waveforms, and *Table 112* and *Table 113* provide the corresponding timings. The results shown in this table are obtained with the following FMC configuration:

- COM.FMC\_SetupTime = 0x01;

- COM.FMC\_WaitSetupTime = 0x03;

- COM.FMC HoldSetupTime = 0x02;

- COM.FMC\_HiZSetupTime = 0x01;

- ATT.FMC\_SetupTime = 0x01;

- ATT.FMC WaitSetupTime = 0x03;

- ATT.FMC\_HoldSetupTime = 0x02;

- ATT.FMC\_HiZSetupTime = 0x01;

- Bank = FMC\_Bank\_NAND;

- MemoryDataWidth = FMC\_MemoryDataWidth\_16b;

- ECC = FMC\_ECC\_Enable;

- ECCPageSize = FMC\_ECCPageSize\_512Bytes;

- TCLRSetupTime = 0;

- TARSetupTime = 0.

In all timing tables, the  $T_{\text{HCLK}}$  is the HCLK clock period.

| Symbol                         | Parameter Min          |                          | Мах                      | Unit |

|--------------------------------|------------------------|--------------------------|--------------------------|------|

| t <sub>w(SDCLK)</sub>          | FMC_SDCLK period       | 2T <sub>HCLK</sub> – 0.5 | 2T <sub>HCLK</sub> + 0.5 |      |

| t <sub>d(SDCLKL_Data</sub> )   | Data output valid time | -                        | 2.5                      |      |

| t <sub>h(SDCLKL</sub> _Data)   | Data output hold time  | 0                        | -                        |      |

| $t_{d(SDCLKL_Add)}$            | Address valid time     | -                        | 2.5                      |      |

| t <sub>d(SDCLKL</sub> -SDNWE)  | SDNWE valid time       | -                        | 2.5                      |      |

| t <sub>h(SDCLKL-SDNWE)</sub>   | SDNWE hold time        | 0                        | -                        | ns   |

| t <sub>d(SDCLKL</sub> - SDNE)  | Chip select valid time | -                        | 0.5                      | 115  |

| $t_{h(SDCLKL-SDNE)}$           | Chip select hold time  | 0                        | -                        |      |

| t <sub>d(SDCLKL</sub> -SDNRAS) | SDNRAS valid time      | -                        | 1.5                      |      |

| t <sub>h(SDCLKL-SDNRAS)</sub>  | SDNRAS hold time       | 0                        | -                        |      |

| t <sub>d(SDCLKL-SDNCAS)</sub>  | SDNCAS valid time      | -                        | 1.5                      |      |

| t <sub>d(SDCLKL</sub> -SDNCAS) | SDNCAS hold time       | 0                        | -                        |      |

Table 117. LPSDR SDRAM write timings<sup>(1)</sup>

1. Guaranteed by characterization results.

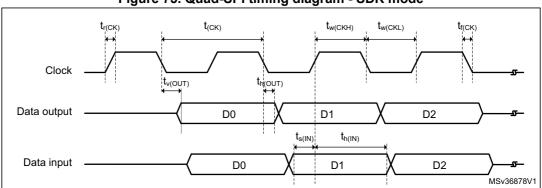

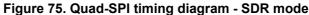

#### 5.3.31 Quad-SPI interface characteristics

Unless otherwise specified, the parameters given in *Table 118* and *Table 119* for Quad-SPI are derived from tests performed under the ambient temperature,  $f_{AHB}$  frequency and  $V_{DD}$  supply voltage conditions summarized in *Table 17: General operating conditions*, with the following configuration:

- Output speed is set to OSPEEDRy[1:0] = 11

- Capacitive load C = 20 pF

- Measurement points are done at CMOS levels: 0.5 x V<sub>DD</sub>

Refer to Section 5.3.20: I/O port characteristics for more details on the input/output alternate function characteristics.

| Symbol     | Parameter                   | Conditions                                     | Min | Тур | Мах | Unit |

|------------|-----------------------------|------------------------------------------------|-----|-----|-----|------|

| Fck1/t(CK) | Quad-SPI clock<br>frequency | 2.7 V≤ V <sub>DD</sub> <3.6 V<br>CL=20 pF      | -   | -   | 108 | MHz  |

|            |                             | 1.71 V <v<sub>DD&lt;3.6 V<br/>CL=15 pF</v<sub> | -   | -   | 100 |      |

Table 118. Quad-SPI characteristics in SDR mode<sup>(1)</sup>

#### 5.3.32 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 120* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 17*, with the following configuration: