Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                       |                                                                                                          |

|-------------------------------|----------------------------------------------------------------------------------------------------------|

| Product Status                | Active                                                                                                   |

| Core Processor                | ARM® Cortex®-M7                                                                                          |

| Core Size                     | 32-Bit Single-Core                                                                                       |

| Speed                         | 216MHz                                                                                                   |

| Connectivity                  | CANbus, EBI/EMI, Ethernet, I²C, IrDA, LINbus, MMC/SD/SDIO, QSPI, SAI, SPDIF, SPI, UART/USART, USB<br>OTG |

| Peripherals                   | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LCD, POR, PWM, WDT                                        |

| Number of I/O                 | 132                                                                                                      |

| Program Memory Size           | 2MB (2M x 8)                                                                                             |

| Program Memory Type           | FLASH                                                                                                    |

| EEPROM Size                   | · ·                                                                                                      |

| RAM Size                      | 512K x 8                                                                                                 |

| Voltage - Supply<br>(Vcc/Vdd) | 1.7V ~ 3.6V                                                                                              |

| Data Converters               | A/D 24x12b; D/A 2x12b                                                                                    |

| Oscillator Type               | Internal                                                                                                 |

| Operating Temperature         | -40°C ~ 85°C (TA)                                                                                        |

| Mounting Type                 | Surface Mount                                                                                            |

| Package / Case                | 176-LQFP                                                                                                 |

| Supplier Device Package       | 176-LQFP (24x24)                                                                                         |

| Purchase URL                  | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f779iit6                                    |

|                               |                                                                                                          |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Peri                         | pherals                      | STM32F   | 77xVx                                                     | STM32 | F77xZx | STM32 | F779Ax | STM32F778Ax        | STM32 | 2F77xlx | STM32 | F77xBx | STM32 | F77xNx |

|------------------------------|------------------------------|----------|-----------------------------------------------------------|-------|--------|-------|--------|--------------------|-------|---------|-------|--------|-------|--------|

| Flash memory in Kby          | ytes                         | 1024     | 2048                                                      | 1024  | 2048   | 1024  | 2048   | 2048               | 1024  | 2048    | 1024  | 2048   | 1024  | 2048   |

|                              | System                       |          |                                                           |       |        |       |        | 512(368+16+128)    | •     |         |       |        |       |        |

| SRAM in Kbytes               | Instruction                  |          |                                                           |       |        |       |        | 16                 |       |         |       |        |       |        |

|                              | Backup                       | 4        |                                                           |       |        |       |        |                    |       |         |       |        |       |        |

| FMC memory contro            | ller                         |          |                                                           |       |        |       |        | Yes <sup>(1)</sup> |       |         |       |        |       |        |

| Quad-SPI                     |                              |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

| Ethernet                     |                              |          | Ye                                                        | s     |        |       | Ν      | lo                 |       |         | Ye    | es     |       |        |

|                              | General-purpose              |          |                                                           |       |        |       |        | 10                 |       |         |       |        |       |        |

| <b>T</b> :                   | Advanced-control             |          |                                                           |       |        |       |        | 2                  |       |         |       |        |       |        |

| Timers                       | Basic                        |          |                                                           |       |        |       |        | 2                  |       |         |       |        |       |        |

|                              | Low-power                    |          |                                                           |       |        |       |        | 1                  |       |         |       |        |       |        |

| Random number ger            | nerator                      |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

|                              | SPI / I <sup>2</sup> S       | 4/3 (sim | 4/3 (simplex) <sup>(2)</sup> 6/3 (simplex) <sup>(2)</sup> |       |        |       |        |                    |       |         |       |        |       |        |

|                              | l <sup>2</sup> C             | 4        |                                                           |       |        |       |        |                    |       |         |       |        |       |        |

|                              | USART/UART                   |          |                                                           |       |        |       |        | 4/4                |       |         |       |        |       |        |

|                              | USB OTG FS                   |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

| Communication                | USB OTG HS                   |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

| interfaces                   | CAN                          |          |                                                           |       |        |       |        | 3                  |       |         |       |        |       |        |

|                              | SAI                          |          |                                                           |       |        |       |        | 2                  |       |         |       |        |       |        |

|                              | SPDIFRX                      |          |                                                           |       |        |       |        | 4 inputs           |       |         |       |        |       |        |

|                              | SDMMC1                       |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

|                              | SDMMC2                       |          |                                                           |       |        |       |        | Yes <sup>(3)</sup> |       |         |       |        |       |        |

| Camera interface             |                              |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

| MIPI-DSI Host <sup>(4)</sup> |                              |          | N                                                         | 0     |        |       |        |                    | Ye    | s       |       |        |       |        |

| LCD-TFT                      |                              |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

| Chrom-ART Accelera           | rom-ART Accelerator™ (DMA2D) |          | Yes                                                       |       |        |       |        |                    |       |         |       |        |       |        |

| JPEG codec                   | EG codec                     |          |                                                           |       |        |       |        | Yes                |       |         |       |        |       |        |

| Cryptography                 |                              | Yes      |                                                           |       |        |       |        |                    |       |         |       |        |       |        |

16/255

DocID028294 Rev 4

STM32F777xx STM32F778Ax STM32F779xx

Description

#### 1.1 Full compatibility throughout the family

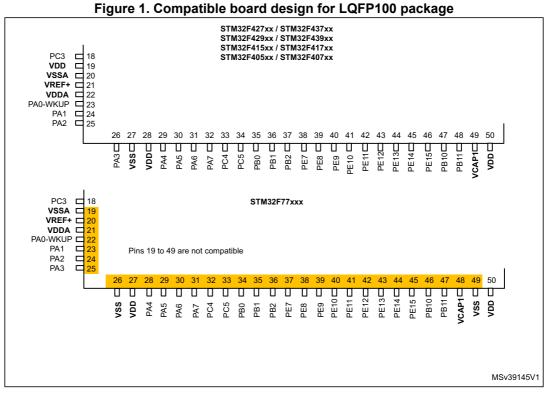

The STM32F777xx, STM32F778Ax and STM32F779xx devices are fully pin-to-pin, compatible with the STM32F4xxxx devices, allowing the user to try different peripherals, and reaching higher performances (higher frequency) for a greater degree of freedom during the development cycle.

*Figure 1* gives compatible board designs between the STM32F7xx and STM32F4xx families.

The STM32F77x LQFP144, LQFP176, LQFP208, TFBGA216, UFBGA176 packages are fully pin to pin compatible with STM32F4xx devices.

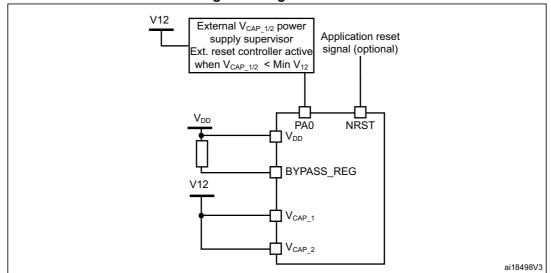

#### Figure 8. Regulator OFF

The following conditions must be respected:

- V<sub>DD</sub> should always be higher than V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to avoid current injection between power domains.

- If the time for V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> to reach V<sub>12</sub> minimum value is faster than the time for V<sub>DD</sub> to reach 1.7 V, then PA0 should be kept low to cover both conditions: until V<sub>CAP\_1</sub> and V<sub>CAP\_2</sub> reach V<sub>12</sub> minimum value and until V<sub>DD</sub> reaches 1.7 V (see *Figure 9*).

- Otherwise, if the time for  $V_{CAP_1}$  and  $V_{CAP_2}$  to reach  $V_{12}$  minimum value is slower than the time for  $V_{DD}$  to reach 1.7 V, then PA0 could be asserted low externally (see *Figure 10*).

- If  $V_{CAP_1}$  and  $V_{CAP_2}$  go below  $V_{12}$  minimum value and  $V_{DD}$  is higher than 1.7 V, then a reset must be asserted on PA0 pin.

- *Note:* The minimum value of V<sub>12</sub> depends on the maximum frequency targeted in the application.

| Timer<br>type        | Timer           | Counter<br>resolution | Counter<br>type         | Prescaler<br>factor                      | DMA<br>request<br>generation | Capture/<br>compare<br>channels | Complem<br>entary<br>output | Max<br>interface<br>clock<br>(MHz) | Max<br>timer<br>clock<br>(MHz) <sup>(1)</sup> |

|----------------------|-----------------|-----------------------|-------------------------|------------------------------------------|------------------------------|---------------------------------|-----------------------------|------------------------------------|-----------------------------------------------|

| Advanced<br>-control | TIM1,<br>TIM8   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | Yes                         | 108                                | 216                                           |

|                      | TIM2,<br>TIM5   | 32-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes 4                        |                                 | No                          | 54                                 | 108/216                                       |

|                      | TIM3,<br>TIM4   | 16-bit                | Up,<br>Down,<br>Up/down | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 4                               | No                          | 54                                 | 108/216                                       |

| General              | TIM9            | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 2                               | No                          | 108                                | 216                                           |

| purpose              | TIM10,<br>TIM11 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 1                               | No                          | 108                                | 216                                           |

|                      | TIM12           | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 2                               | No                          | 54                                 | 108/216                                       |

|                      | TIM13,<br>TIM14 | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | No                           | 1                               | No                          | 54                                 | 108/216                                       |

| Basic                | TIM6,<br>TIM7   | 16-bit                | Up                      | Any<br>integer<br>between 1<br>and 65536 | Yes                          | 0                               | No                          | 54                                 | 108/216                                       |

| Table 6. | Timer | feature | comparison |

|----------|-------|---------|------------|

| 10.010 0 |       |         |            |

1. The maximum timer clock is either 108 or 216 MHz depending on TIMPRE bit configuration in the RCC\_DCKCFGR register.

### 2.48 DSI Host (DSIHOST)

The DSI Host is a dedicated peripheral for interfacing with MIPI<sup>®</sup> DSI compliant displays. It includes a dedicated video interface internally connected to the LTDC and a generic APB interface that can be used to transmit information to the display.

These interfaces are as follows:

- LTDC interface:

- Used to transmit information in Video mode, in which the transfers from the host processor to the peripheral take the form of a real-time pixel stream (DPI).

- Through a customized for mode, this interface can be used to transmit information in full bandwidth in the Adapted Command mode (DBI).

- APB slave interface:

- Allows the transmission of generic information in Command mode, and follows a proprietary register interface.

- Can operate concurrently with either LTDC interface in either Video mode or Adapted Command mode.

- Video mode pattern generator:

- Allows the transmission of horizontal/vertical color bar and D-PHY BER testing pattern without any kind of stimuli.

The DSI Host main features:

- Compliant with MIPI<sup>®</sup> Alliance standards

- Interface with MIPI<sup>®</sup> D-PHY

- Supports all commands defined in the MIPI<sup>®</sup> Alliance specification for DCS:

- Transmission of all Command mode packets through the APB interface

- Transmission of commands in low-power and high-speed during Video mode

- Supports up to two D-PHY data lanes

- Bidirectional communication and escape mode support through data lane 0

- Supports non-continuous clock in D-PHY clock lane for additional power saving

- Supports Ultra Low-power mode with PLL disabled

- ECC and Checksum capabilities

- Support for End of Transmission Packet (EoTp)

- Fault recovery schemes

- 3D transmission support

- Configurable selection of system interfaces:

- AMBA APB for control and optional support for Generic and DCS commands

- Video Mode interface through LTDC

- Adapted Command mode interface through LTDC

- Independently programmable Virtual Channel ID in

- Video mode

- Adapted Command mode

- APB Slave

#### Video Mode interfaces features:

• LTDC interface color coding mappings into 24-bit interface:

#### Figure 20. STM32F779xx TFBGA216 ballout

1. The above figure shows the package top view.

|         |         |          | I       | Pin N   | umbe     | ər                      |               |         |          |                                |          |               |       |                                                                                                                                                       |                         |

|---------|---------|----------|---------|---------|----------|-------------------------|---------------|---------|----------|--------------------------------|----------|---------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|         | S       | TM32     | :F777   | xx      |          |                         | FM32I<br>FM32 |         |          | reset                          |          |               |       |                                                                                                                                                       |                         |

| LQFP100 | LQFP144 | UFBGA176 | LQFP176 | LQFP208 | TFBGA216 | WLCSP180 <sup>(1)</sup> | LQFP176       | LQFP208 | TFBGA216 | Pin name (function after reset | Pin type | I/O structure | Notes | Alternate functions                                                                                                                                   | Additional<br>functions |

| 40      | 63      | R9       | 73      | 84      | R9       | J6                      | 73            | 84      | R9       | PE10                           | I/O      | FT            | -     | TIM1_CH2N,<br>DFSDM1_DATIN4,<br>UART7_CTS,<br>QUADSPI_BK2_IO3,<br>FMC_D7, EVENTOUT                                                                    | -                       |

| 41      | 64      | P10      | 74      | 85      | P10      | K6                      | 74            | 85      | P10      | PE11                           | I/O      | FT            | -     | TIM1_CH2, SPI4_NSS,<br>DFSDM1_CKIN4,<br>SAI2_SD_B, FMC_D8,<br>LCD_G3, EVENTOUT                                                                        | -                       |

| 42      | 65      | R10      | 75      | 86      | R10      | L6                      | 75            | 86      | R10      | PE12                           | I/O      | FT            | -     | TIM1_CH3N, SPI4_SCK,<br>DFSDM1_DATIN5,<br>SAI2_SCK_B, FMC_D9,<br>LCD_B4, EVENTOUT                                                                     | -                       |

| 43      | 66      | N11      | 76      | 87      | R12      | P6                      | 76            | 87      | R12      | PE13                           | I/O      | FT            | -     | TIM1_CH3, SPI4_MISO,<br>DFSDM1_CKIN5,<br>SAI2_FS_B, FMC_D10,<br>LCD_DE, EVENTOUT                                                                      | -                       |

| 44      | 67      | P11      | 77      | 88      | P11      | N6                      | 77            | 88      | P11      | PE14                           | I/O      | FT            | -     | TIM1_CH4, SPI4_MOSI,<br>SAI2_MCLK_B, FMC_D11,<br>LCD_CLK, EVENTOUT                                                                                    | -                       |

| 45      | 68      | R11      | 78      | 89      | R11      | M6                      | 78            | 89      | R11      | PE15                           | I/O      | FT            | -     | TIM1_BKIN, FMC_D12,<br>LCD_R7, EVENTOUT                                                                                                               | -                       |

| 46      | 69      | R12      | 79      | 90      | P12      | K5                      | 79            | 90      | P12      | PB10                           | I/O      | FT            | -     | TIM2_CH3, I2C2_SCL,<br>SPI2_SCK/I2S2_CK,<br>DFSDM1_DATIN7,<br>USART3_TX,<br>QUADSPI_BK1_NCS,<br>OTG_HS_ULPI_D3,<br>ETH_MII_RX_ER,<br>LCD_G4, EVENTOUT | -                       |

### Table 10. STM32F777xx, STM32F778Ax and STM32F779xx pin and ball definitions (continued)

#### Pinouts and pin description

- NC (not-connected) pins are not bonded. They must be configured by software to output push-pull and forced to 0 in the output data register to avoid an extra current consumption in low-power modes. list of pins: PI8, PI12, PI13, PI14, PF6, PF7, PF8, PF9, PC2, PC3, PC4, PC5, PI15, PJ0, PJ1, PJ2, PJ3, PJ4, PJ5, PH6, PH7, PJ12, PJ13, PJ14, PJ15, PG14, PK3, PK4, PK5, PK6 and PK7.

- PC13, PC14, PC15 and Pl8 are supplied through the power switch. Since the switch only sinks a limited amount of current (3 mA), the use of GPIOs PC13 to PC15 and Pl8 in output mode is limited: - The speed should not exceed 2 MHz with a maximum load of 30 pF. - These I/Os must not be used as a current source (e.g. to drive an LED).

- 3. FT = 5 V tolerant except when in analog mode or oscillator mode (for PC14, PC15, PH0 and PH1).

- 4. If the device is in regulator OFF/internal reset ON mode (BYPASS\_REG pin is set to VDD), then PA0 is used as an internal reset (active low).

- 5. Internally connected to VDD or VSS depending on part number.

| σ        |

|----------|

| Б.       |

| ō        |

| Ċ,       |

| ជ        |

| <u>o</u> |

| Ξ        |

| đ        |

| -        |

| ĭ        |

|          |

| ð        |

| õ        |

| ö        |

| ž.       |

| Ē        |

| Ē.       |

| 0        |

| 3        |

STM32F777xx STM32F778Ax STM32F779xx

## Table 12. STM32F777xx, STM32F778Ax and STM32F779xx alternate function mapping

|        |      |      |                           |              |                                            |                               | -                                                      | anotion                                                        | тарри                                                                          |                                                               |                                                    |                                                                        |                                                 |                                                |                  |               |              |

|--------|------|------|---------------------------|--------------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------|------------------------------------------------|------------------|---------------|--------------|

|        |      | AF0  | AF1                       | AF2          | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                                            | AF12                                           | AF13             | AF14          | AF15         |

| Po     | ort  | SYS  | 12C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5     | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/O<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH                    | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD           | SYS          |

|        | PA0  | -    | TIM2_C<br>H1/TIM2<br>_ETR | TIM5_C<br>H1 | TIM8_ET<br>R                               | -                             | -                                                      | -                                                              | USART2<br>_CTS                                                                 | UART4_<br>TX                                                  | -                                                  | SAI2_SD_<br>B                                                          | ETH_MII_<br>CRS                                 | -                                              | -                | -             | EVEN<br>TOUT |

|        | PA1  | -    | TIM2_C<br>H2              | TIM5_C<br>H2 | -                                          | -                             | -                                                      | -                                                              | USART2<br>_RTS                                                                 | UART4_<br>RX                                                  | QUADSP<br>I_BK1_IO<br>3                            | SAI2_MC<br>K_B                                                         | ETH_MII_<br>RX_CLK/<br>ETH_RMI<br>I_REF_C<br>LK | -                                              | -                | LCD_R2        | EVEN<br>TOUT |

|        | PA2  | -    | TIM2_C<br>H3              | TIM5_C<br>H3 | TIM9_CH<br>1                               | -                             | -                                                      | -                                                              | USART2<br>_TX                                                                  | SAI2_SC<br>K_B                                                | -                                                  | -                                                                      | ETH_MDI<br>O                                    | MDIOS_<br>MDIO                                 | -                | LCD_R1        | EVEN<br>TOUT |

|        | PA3  | -    | TIM2_C<br>H4              | TIM5_C<br>H4 | TIM9_CH<br>2                               | -                             | -                                                      | -                                                              | USART2<br>_RX                                                                  | -                                                             | LCD_B2                                             | OTG_HS_<br>ULPI_D0                                                     | ETH_MII_<br>COL                                 | -                                              | -                | LCD_B5        | EVEN<br>TOUT |

|        | PA4  | -    | -                         | -            | -                                          | -                             | SPI1_NS<br>S/I2S1_<br>WS                               | SPI3_NS<br>S/I2S3_<br>WS                                       | USART2<br>_CK                                                                  | SPI6_NS<br>S                                                  | -                                                  | -                                                                      | -                                               | OTG_HS<br>_SOF                                 | DCMI_H<br>SYNC   | LCD_VS<br>YNC | EVEN<br>TOUT |

| Port A | PA5  | -    | TIM2_C<br>H1/TIM2<br>_ETR | -            | TIM8_CH<br>1N                              | -                             | SPI1_SC<br>K/I2S1_<br>CK                               | -                                                              | -                                                                              | SPI6_SC<br>K                                                  | -                                                  | OTG_HS_<br>ULPI_CK                                                     | -                                               | -                                              | -                | LCD_R4        | EVEN<br>TOUT |

|        | PA6  | -    | TIM1_B<br>KIN             | TIM3_C<br>H1 | TIM8_BKI<br>N                              | -                             | SPI1_MI<br>SO                                          | -                                                              | -                                                                              | SPI6_MI<br>SO                                                 | TIM13_C<br>H1                                      | -                                                                      | -                                               | MDIOS_<br>MDC                                  | DCMI_PI<br>XCLK  | LCD_G2        | EVEN<br>TOUT |

|        | PA7  | -    | TIM1_C<br>H1N             | TIM3_C<br>H2 | TIM8_CH<br>1N                              | -                             | SPI1_M<br>OSI/I2S1<br>_SD                              | -                                                              | -                                                                              | SPI6_MO<br>SI                                                 | TIM14_C<br>H1                                      | -                                                                      | ETH_MII_<br>RX_DV/E<br>TH_RMII_<br>CRS_DV       | FMC_SD<br>NWE                                  | -                | -             | EVEN<br>TOUT |

|        | PA8  | MCO1 | TIM1_C<br>H1              | -            | TIM8_BKI<br>N2                             | I2C3_SC<br>L                  | -                                                      | -                                                              | USART1<br>_CK                                                                  | -                                                             | -                                                  | OTG_FS_<br>SOF                                                         | CAN3_R<br>X                                     | UART7_<br>RX                                   | LCD_B3           | LCD_R6        | EVEN<br>TOUT |

|        | PA9  | -    | TIM1_C<br>H2              | -            | -                                          | I2C3_SM<br>BA                 | SPI2_SC<br>K/I2S2_<br>CK                               | -                                                              | USART1<br>_TX                                                                  | -                                                             | -                                                  | -                                                                      | -                                               | -                                              | DCMI_D<br>0      | LCD_R5        | EVEN<br>TOUT |

|        | PA10 | -    | TIM1_C<br>H3              | -            | -                                          | -                             | -                                                      | -                                                              | USART1<br>_RX                                                                  | -                                                             | LCD_B4                                             | OTG_FS_<br>ID                                                          | -                                               | MDIOS_<br>MDIO                                 | DCMI_D<br>1      | LCD_B1        | EVEN<br>TOUT |

92/255

DocID028294 Rev 4

Pinouts and pin description

STM32F777xx STM32F778Ax STM32F779xx

|        |      | AF0         | AF1                       | AF2      | AF3                                        | AF4                           | AF5                                                    | AF6                                                            | AF7                                                                            | AF8                                                           | AF9                                                | AF10                                                                   | AF11                         | AF12                                           | AF13             | AF14        | AF1         |

|--------|------|-------------|---------------------------|----------|--------------------------------------------|-------------------------------|--------------------------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|------------------------------|------------------------------------------------|------------------|-------------|-------------|

| Po     | ort  | SYS         | I2C4/UA<br>RT5/TIM<br>1/2 | TIM3/4/5 | TIM8/9/10/<br>11/LPTIM<br>1/DFSDM<br>1/CEC | I2C1/2/3/<br>4/USART<br>1/CEC | SPI1/I2S<br>1/SPI2/I2<br>S2/SPI3/<br>I2S3/SPI<br>4/5/6 | SPI2/I2S<br>2/SPI3/I2<br>S3/SAI1/<br>I2C4/UA<br>RT4/DF<br>SDM1 | SPI2/I2S<br>2/SPI3/I2<br>S3/SPI6/<br>USART1/<br>2/3/UART<br>5/DFSDM<br>1/SPDIF | SPI6/SAI<br>2/USART<br>6/UART4/<br>5/7/8/OT<br>G_FS/SP<br>DIF | CAN1/2/T<br>IM12/13/<br>14/QUAD<br>SPI/FMC/<br>LCD | SAI2/QU<br>ADSPI/S<br>DMMC2/D<br>FSDM1/0<br>TG2_HS/<br>OTG1_FS<br>/LCD | I2C4/CAN<br>3/SDMM<br>C2/ETH | UART7/<br>FMC/SD<br>MMC1/M<br>DIOS/OT<br>G2_FS | DCMI/L<br>CD/DSI | LCD         | SYS         |

|        | PE4  | TRACED<br>1 | -                         | -        | -                                          | -                             | SPI4_NS<br>S                                           | SAI1_FS<br>_A                                                  | -                                                                              | -                                                             | -                                                  | DFSDM1_<br>DATAIN3                                                     | -                            | FMC_A2<br>0                                    | DCMI_D<br>4      | LCD_B0      | EVE<br>TOU  |

|        | PE5  | TRACED<br>2 | -                         | -        | TIM9_CH<br>1                               | -                             | SPI4_MI<br>SO                                          | SAI1_SC<br>K_A                                                 | -                                                                              | -                                                             | -                                                  | DFSDM1_<br>CKIN3                                                       | -                            | FMC_A2<br>1                                    | DCMI_D<br>6      | LCD_G0      | EVEI<br>TOU |

|        | PE6  | TRACED<br>3 | TIM1_B<br>KIN2            | -        | TIM9_CH<br>2                               | -                             | SPI4_M<br>OSI                                          | SAI1_SD<br>_A                                                  | -                                                                              | -                                                             | -                                                  | SAI2_MC<br>K_B                                                         | -                            | FMC_A2<br>2                                    | DCMI_D<br>7      | LCD_G1      | EVE<br>TOU  |

|        | PE7  | -           | TIM1_ET<br>R              | -        | -                                          | -                             | -                                                      | DFSDM1<br>_DATAIN<br>_2                                        | -                                                                              | UART7_<br>Rx                                                  | -                                                  | QUADSPI<br>_BK2_IO0                                                    | -                            | FMC_D4                                         | -                | -           | EVE<br>TOU  |

|        | PE8  | -           | TIM1_C<br>H1N             | -        | -                                          | -                             | -                                                      | DFSDM1<br>_CKIN2                                               | -                                                                              | UART7_T<br>x                                                  | -                                                  | QUADSPI<br>_BK2_IO1                                                    | -                            | FMC_D5                                         | -                | -           | EVE<br>TOU  |

|        | PE9  | -           | TIM1_C<br>H1              | -        | -                                          | -                             | -                                                      | DFSDM1<br>_CKOUT                                               | -                                                                              | UART7_<br>RTS                                                 | -                                                  | QUADSPI<br>_BK2_IO2                                                    | -                            | FMC_D6                                         | -                | -           | EVE<br>TOU  |

| Port E | PE10 | -           | TIM1_C<br>H2N             | -        | -                                          | -                             | -                                                      | DFSDM1<br>_DATAIN<br>_4                                        | -                                                                              | UART7_<br>CTS                                                 | -                                                  | QUADSPI<br>_BK2_IO3                                                    | -                            | FMC_D7                                         | -                | -           | EVE<br>TOU  |

|        | PE11 | -           | TIM1_C<br>H2              | -        | -                                          | -                             | SPI4_NS<br>S                                           | DFSDM1<br>_CKIN4                                               | -                                                                              | -                                                             | -                                                  | SAI2_SD_<br>B                                                          | -                            | FMC_D8                                         | -                | LCD_G3      | EVE<br>TOU  |

|        | PE12 | -           | TIM1_C<br>H3N             | -        | -                                          | -                             | SPI4_SC<br>K                                           | DFSDM1<br>_DATAIN<br>5                                         | -                                                                              | -                                                             | -                                                  | SAI2_SC<br>K_B                                                         | -                            | FMC_D9                                         | -                | LCD_B4      | EVE<br>TOU  |

|        | PE13 | -           | TIM1_C<br>H3              | -        | -                                          | -                             | SPI4_MI<br>SO                                          | DFSDM1<br>_CKIN5                                               | -                                                                              | -                                                             | -                                                  | SAI2_FS_<br>B                                                          | -                            | FMC_D1<br>0                                    | -                | LCD_DE      | EVE<br>TOU  |

|        | PE14 | -           | TIM1_C<br>H4              | -        | -                                          | -                             | SPI4_M<br>OSI                                          | -                                                              | -                                                                              | -                                                             | -                                                  | SAI2_MC<br>K_B                                                         | -                            | FMC_D1<br>1                                    | -                | LCD_CL<br>K | EVE<br>TOL  |

|        | PE15 | -           | TIM1_B<br>KIN             | -        | -                                          | -                             | -                                                      | -                                                              | -                                                                              | -                                                             | -                                                  | -                                                                      | -                            | FMC_D1<br>2                                    | -                | LCD_R7      | EVE<br>TOL  |

#### Table 12 STM22E777xx STM22E778Ax and STM22E770xx alternate

98/255

DocID028294 Rev 4

N

#### Typical and maximum current consumption

The MCU is placed under the following conditions:

- All I/O pins are in input mode with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load).

- All peripherals are disabled except if it is explicitly mentioned.

- The Flash memory access time is adjusted both to f<sub>HCLK</sub> frequency and V<sub>DD</sub> range (see *Table 18: Limitations depending on the operating power supply range*).

- When the regulator is ON, the voltage scaling and over-drive mode are adjusted to f<sub>HCLK</sub> frequency as follows:

- Scale 3 for  $f_{HCLK} \le 144 \text{ MHz}$

- Scale 2 for 144 MHz <  $f_{HCLK} \le$  168 MHz

- Scale 1 for 168 MHz <  $f_{HCLK} \le 216$  MHz. The over-drive is only ON at 216 MHz.

- When the regulator is OFF, the V12 is provided externally as described in *Table 17: General operating conditions*:

- The system clock is HCLK,  $f_{PCLK1} = f_{HCLK}/4$ , and  $f_{PCLK2} = f_{HCLK}/2$ .

- External clock frequency is 25 MHz and PLL is ON when f<sub>HCLK</sub> is higher than 25 MHz.

- The typical current consumption values are obtained for 1.7 V  $\leq V_{DD} \leq 3.6$  V voltage range and for T<sub>A</sub>= 25 °C unless otherwise specified.

- The maximum values are obtained for  $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$  voltage range and a maximum ambient temperature (T<sub>A</sub>) unless otherwise specified.

- For the voltage range  $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$ , the maximum frequency is 180 MHz.

### Table 24. Typical and maximum current consumption in Run mode, code with data processing<br/>running from ITCM RAM, regulator ON

| Symbol          | Doromotor              | Conditions                                   | £ (MALI_)               | Turn |                        | Max <sup>(1)</sup>     |                         | Unit               |                    |  |

|-----------------|------------------------|----------------------------------------------|-------------------------|------|------------------------|------------------------|-------------------------|--------------------|--------------------|--|

| Symbol          | Parameter              | Conditions                                   | f <sub>HCLK</sub> (MHz) | Тур  | T <sub>A</sub> = 25 °C | T <sub>A</sub> = 85 °C | T <sub>A</sub> = 105 °C | Unit               |                    |  |

|                 |                        |                                              | 216                     | 193  | 221 <sup>(4)</sup>     | 258 <sup>(4)</sup>     | -                       |                    |                    |  |

|                 |                        | All peripherals<br>enabled <sup>(2)(3)</sup> | 200                     | 179  | 207                    | 244                    | 279                     |                    |                    |  |

|                 |                        |                                              |                         | A11  | 180                    | 159                    | 176 <sup>(4)</sup>      | 210 <sup>(4)</sup> | 238 <sup>(4)</sup> |  |

|                 |                        |                                              | 168                     | 142  | 156                    | 187                    | 211                     |                    |                    |  |

|                 |                        |                                              | 144                     | 122  | 135                    | 167                    | 190                     |                    |                    |  |

|                 | Supply                 |                                              | 60                      | 49   | 55                     | 81                     | 103                     |                    |                    |  |

|                 |                        |                                              | 25                      | 23   | 28                     | 54                     | 76                      | m۸                 |                    |  |

| I <sub>DD</sub> | current in<br>RUN mode |                                              | 216                     | 95   | 107 <sup>(4)</sup>     | 153 <sup>(4)</sup>     | -                       | mA                 |                    |  |

|                 |                        |                                              | 200                     | 88   | 100                    | 146                    | 180                     |                    |                    |  |

|                 |                        |                                              | 180                     | 78   | 88 <sup>(4)</sup>      | 122 <sup>(4)</sup>     | 147 <sup>(4)</sup>      |                    |                    |  |

|                 |                        | All peripherals disabled <sup>(3)</sup>      | 168                     | 70   | 78                     | 109                    | 133                     |                    |                    |  |

|                 |                        |                                              | 144                     | 60   | 68                     | 99                     | 123                     |                    |                    |  |

|                 |                        |                                              | 60                      | 24   | 29                     | 55                     | 76                      |                    |                    |  |

|                 |                        |                                              | 25                      | 12   | 16                     | 42                     | 63                      |                    |                    |  |

1. Guaranteed by characterization results, unless otherwise specified.

| _        |                          |         | I <sub>DD</sub> (Typ) <sup>(1)</sup> | <u> </u> | Unit   |

|----------|--------------------------|---------|--------------------------------------|----------|--------|

|          | Peripheral               | Scale 1 | Scale 2                              | Scale 3  | Unit   |

|          | TIM1                     | 24.1    | 23.8                                 | 19.6     |        |

|          | TIM8                     | 24.5    | 24.2                                 | 20.0     |        |

|          | USART1                   | 17.7    | 17.4                                 | 14.3     |        |

|          | USART6                   | 11.9    | 11.8                                 | 9.4      |        |

|          | ADC1 <sup>(5)</sup>      | 4.5     | 4.7                                  | 3.5      |        |

|          | ADC2 <sup>(5)</sup>      | 4.5     | 4.7                                  | 3.3      |        |

|          | ADC3 <sup>(5)</sup>      | 4.5     | 4.6                                  | 3.3      |        |

|          | SDMMC1                   | 8.4     | 8.3                                  | 6.9      |        |

|          | SDMMC2                   | 8.2     | 8.2                                  | 6.4      |        |

|          | SPI1/I2S1 <sup>(3)</sup> | 3.9     | 3.6                                  | 3.1      |        |

| APB2     | SPI4                     | 3.9     | 3.6                                  | 3.1      |        |

| (up to   | SYSCFG                   | 2.5     | 2.2                                  | 1.9      | µA/MHz |

| 108 MHz) | TIM9                     | 8.0     | 8.0                                  | 6.2      |        |

|          | TIM10                    | 5.0     | 5.1                                  | 3.7      |        |

|          | TIM11                    | 6.9     | 6.9                                  | 5.3      |        |

|          | SPI5                     | 2.7     | 2.8                                  | 1.8      |        |

|          | SPI6                     | 3.1     | 3.2                                  | 2.2      |        |

|          | SAI1                     | 3.2     | 3.3                                  | 2.2      |        |

|          | DFSDM1                   | 10.9    | 10.7                                 | 9.0      |        |

|          | SAI2                     | 3.9     | 3.9                                  | 2.8      | 1      |

|          | MDIO                     | 7.1     | 7.0                                  | 5.8      |        |

|          | LTDC                     | 51.2    | 50.3                                 | 41.8     |        |

|          | DSI                      | 8.5     | 8.4                                  | 8.1      |        |

Table 39. Peripheral current consumption (continued)

1. When the I/O compensation cell  $\,$  is ON,  $\rm I_{DD}$  typical value increases by 0.22 mA.

2. The BusMatrix is automatically active when at least one master is ON.

3. To enable an I2S peripheral, first set the I2SMOD bit and then the I2SE bit in the SPI\_I2SCFGR register.

4. When the DAC is ON and EN1/2 bits are set in DAC\_CR register, add an additional power consumption of 0.75 mA per DAC channel for the analog part.

5. When the ADC is ON (ADON bit set in the ADC\_CR2 register), add an additional power consumption of 1.73 mA per ADC for the analog part.

| Symbol                                  | Parameter                                    | Conditions                                                              |                    | Min                 | Тур          | Max          | Unit |

|-----------------------------------------|----------------------------------------------|-------------------------------------------------------------------------|--------------------|---------------------|--------------|--------------|------|

| f <sub>PLLI2S_IN</sub>                  | PLLI2S input clock <sup>(1)</sup>            | -                                                                       |                    | 0.95 <sup>(2)</sup> | 1            | 2.10         |      |

| f <sub>PLLI2SP_OUT</sub>                | PLLI2S multiplier output clock for SPDIFRX   | -                                                                       |                    | -                   | -            | 216          |      |

| f <sub>PLLI2SQ_OUT</sub>                | PLLI2S multiplier output clock for SAI       | -                                                                       | -                  | -                   | 216          | MHz          |      |

| f <sub>PLLI2SR_OUT</sub>                | PLLI2S multiplier output clock for I2S       | -                                                                       |                    | -                   | -            | 216          |      |

| f <sub>VCO_OUT</sub>                    | PLLI2S VCO output                            | -                                                                       |                    | 100                 | -            | 432          |      |

| +                                       | PLLI2S lock time                             | VCO freq = 192 MHz                                                      | 2                  | 75                  | -            | 200          |      |

| t <sub>LOCK</sub>                       |                                              | VCO freq = 432 MHz                                                      |                    | 100                 | -            | 300          | μs   |

|                                         |                                              | Cycle to cycle at                                                       | RMS                | -                   | 90           | -            |      |

|                                         | Master I2S clock jitter                      | 12.288 MHz on<br>48KHz period,<br>N=432, R=5                            | peak<br>to<br>peak | -                   | ±280         | -            | ps   |

| Jitter <sup>(3)</sup>                   |                                              | Average frequency of<br>12.288 MHz<br>N = 432, R = 5<br>on 1000 samples | f                  | -                   | 90           | -            | ps   |

|                                         | WS I2S clock jitter                          | Cycle to cycle at 48 KHz<br>on 1000 samples                             |                    | -                   | 400          | -            | ps   |

| I <sub>DD(PLLI2S)</sub> <sup>(4)</sup>  | PLLI2S power consumption on $V_{DD}$         | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                | 0.15<br>0.45       | -                   | 0.40<br>0.75 | mA           |      |

| I <sub>DDA(PLLI2S)</sub> <sup>(4)</sup> | PLLI2S power consumption on V <sub>DDA</sub> | VCO freq = 192 MHz<br>VCO freq = 432 MHz                                |                    | 0.30<br>0.55        | -            | 0.40<br>0.85 | mA   |

Table 48. PLLI2S characteristics

1. Take care of using the appropriate division factor M to have the specified PLL input clock values.

2. Guaranteed by design.

3. Value given with main PLL running.

4. Guaranteed by characterization results.

| Symbol                   | Parameter                                     | Conditions | Min                 | Тур | Max  | Unit |

|--------------------------|-----------------------------------------------|------------|---------------------|-----|------|------|

| f <sub>PLLSAI_IN</sub>   | PLLSAI input clock <sup>(1)</sup>             | -          | 0.95 <sup>(2)</sup> | 1   | 2.10 |      |

| fpllsaip_out             | PLLSAI multiplier output clock for 48 MHz     | -          | -                   | 48  | 75   |      |

| fpllsaiq_out             | PLLSAI multiplier output clock<br>for SAI     | -          | -                   | -   | 216  | MHz  |

| f <sub>PLLSAIR_OUT</sub> | PLLSAI multiplier output clock<br>for LCD-TFT | -          | -                   | -   | 216  |      |

| f <sub>vco_оит</sub>     | PLLSAI VCO output                             | -          | 100                 | -   | 432  |      |

| Symbol                         | Parameter                                                                                                   | Parameter Conditions                                                                                                                                       |                                     | Мах                | Unit |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------------------|------|

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pinCMOS port(2) $I_{IO}$ = +8 mA2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 |                                                                                                                                                            | Min<br>-                            | 0.4                |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin<br>except PC14                                                     | CMOS port <sup>(2)</sup><br>$I_{IO} = -8 \text{ mA}$<br>2.7 V $\leq V_{DD} \leq 3.6 \text{ V}$                                                             | V <sub>DD</sub> – 0.4               | _                  | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for PC14                                                                          | $\begin{array}{l} \text{CMOS port}^{(2)} \\ \text{I}_{\text{IO}} = -2 \text{ mA} \\ \text{2.7 V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V} \end{array}$ | V <sub>DD</sub> – 0.4               |                    |      |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                     | $\begin{array}{c} \text{TTL port}^{(2)}\\ \text{I}_{\text{IO}} = +8\text{mA}\\ \text{2.7 V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V} \end{array}$      | -                                   | 0.4                | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                        | $\begin{array}{c} \text{TTL port}^{(2)} \\ \text{I}_{\text{IO}} = -8\text{mA} \\ \text{2.7 V} \leq \text{V}_{\text{DD}} \leq 3.6 \text{ V} \end{array}$    | 2.4                                 | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                     | $I_{IO}$ = +20 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                             | -                                   | 1.3 <sup>(4)</sup> | N    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                        | $I_{IO}$ = -20 mA<br>2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                             | V <sub>DD</sub> -1.3 <sup>(4)</sup> | -                  | V    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                     | $I_{IO} = +6 \text{ mA}$ $1.8 \text{ V} \le \text{V}_{DD} \le 3.6 \text{ V}$                                                                               | -                                   | 0.4 <sup>(4)</sup> | v    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                        | $I_{IO} = -6 \text{ mA}$<br>1.8 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                                                      | V <sub>DD</sub> -0.4 <sup>(4)</sup> | -                  | v    |

| V <sub>OL</sub> <sup>(1)</sup> | Output low level voltage for an I/O pin                                                                     | $I_{IO} = +4 \text{ mA}$ $1.7 \text{ V} \le V_{DD} \le 3.6 \text{V}$                                                                                       | -                                   | 0.4 <sup>(5)</sup> |      |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for an I/O pin except PC14                                                        | $I_{IO} = -4 \text{ mA}$ $1.7 \text{ V} \le V_{DD} \le 3.6 \text{V}$                                                                                       | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  | V    |

| V <sub>OH</sub> <sup>(3)</sup> | Output high level voltage for PC14                                                                          | $I_{IO} = -1 \text{ mA}$ $1.7 \text{ V} \le \text{V}_{DD} \le 3.6 \text{V}$                                                                                | V <sub>DD</sub> -0.4 <sup>(5)</sup> | -                  |      |

Table 66. Output voltage characteristics

1. The I<sub>IO</sub> current sunk by the device must always respect the absolute maximum rating specified in *Table 15*. and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. TTL and CMOS outputs are compatible with JEDEC standards JESD36 and JESD52.

3. The I<sub>IO</sub> current sourced by the device must always respect the absolute maximum rating specified in Table 15 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>.

- 4. Based on characterization data.

- 5. Guaranteed by design.

#### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 39* and *Table 67*, respectively.

| Symbol                            | Parameter               | Conditions | Min | Тур | Max | Unit   |

|-----------------------------------|-------------------------|------------|-----|-----|-----|--------|

| T <sub>Coeff</sub> <sup>(2)</sup> | Temperature coefficient | -          | -   | 30  | 50  | ppm/°C |

| t <sub>START</sub> <sup>(2)</sup> | Startup time            | -          | -   | 6   | 10  | μs     |

Table 80. internal reference voltage (continued)

1. Shortest sampling time can be determined in the application by multiple iterations.

2. Guaranteed by design.

#### Table 81. Internal reference voltage calibration values

| Symbol                                                                              | Parameter | Memory address            |

|-------------------------------------------------------------------------------------|-----------|---------------------------|

| $V_{REFIN_{CAL}}$ Raw data acquired at temperature of 30 °C <sub>VDDA</sub> = 3.3 V |           | 0x1FF0 F44A - 0x1FF0 F44B |

#### 5.3.28 DAC electrical characteristics

| Symbol                            | Parameter                                                | Min                | Тур | Max                         | Unit | Comments                                                                                                                |

|-----------------------------------|----------------------------------------------------------|--------------------|-----|-----------------------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>DDA</sub>                  | Analog supply voltage                                    | 1.7 <sup>(1)</sup> | -   | 3.6                         | V    | -                                                                                                                       |

| V <sub>REF+</sub>                 | Reference supply voltage                                 | 1.7 <sup>(1)</sup> | -   | 3.6                         | V    | $V_{REF+} \le V_{DDA}$                                                                                                  |

| V <sub>SSA</sub>                  | Ground                                                   | 0                  | -   | 0                           | V    | -                                                                                                                       |

| R <sub>LOAD</sub> <sup>(2)</sup>  | Resistive load with buffer ON                            | 5                  | -   | -                           | kΩ   | -                                                                                                                       |

| R <sub>0</sub> <sup>(2)</sup>     | Impedance output with buffer<br>OFF                      | -                  | -   | 15                          | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and $V_{SS}$ to have a 1% accuracy is 1.5 M $\Omega$ |

| C <sub>LOAD</sub> <sup>(2)</sup>  | Capacitive load                                          | -                  | -   | 50                          | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                         |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage with buffer ON                     | 0.2                | -   | -                           | V    | It gives the maximum output excursion of the DAC.<br>It corresponds to 12-bit input code                                |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage with buffer ON                    | -                  | -   | V <sub>DDA</sub> -<br>0.2   | V    | (0x0E0) to (0xF1C) at V <sub>REF+</sub> = 3.6 V and<br>(0x1C7) to (0xE38) at V <sub>REF+</sub> = 1.7 V                  |

| DAC_OUT<br>min <sup>(2)</sup>     | Lower DAC_OUT voltage<br>with buffer OFF                 | -                  | 0.5 | -                           | mV   | It gives the maximum output excursion of                                                                                |

| DAC_OUT<br>max <sup>(2)</sup>     | Higher DAC_OUT voltage<br>with buffer OFF                | -                  | -   | V <sub>REF+</sub> -<br>1LSB | V    | the DAC.                                                                                                                |

| I <sub>VREF+</sub> <sup>(4)</sup> | DAC DC V <sub>REF</sub> current consumption in quiescent | -                  | 170 | 240                         | μA   | With no load, worst code (0x800) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

| VREF+` ′                          | mode (Standby mode)                                      | -                  | 50  | 75                          | μΑ   | With no load, worst code (0xF1C) at<br>V <sub>REF+</sub> = 3.6 V in terms of DC<br>consumption on the inputs            |

#### Table 82. DAC characteristics

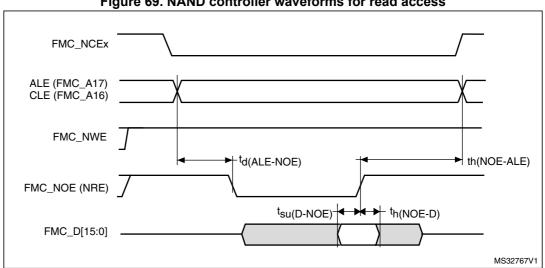

Figure 69. NAND controller waveforms for read access

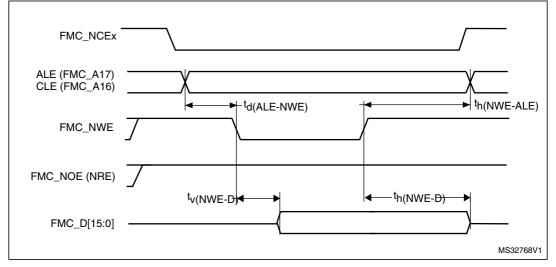

Figure 70. NAND controller waveforms for write access

#### 5.3.32 Camera interface (DCMI) timing specifications

Unless otherwise specified, the parameters given in *Table 120* for DCMI are derived from tests performed under the ambient temperature,  $f_{HCLK}$  frequency and  $V_{DD}$  supply voltage summarized in *Table 17*, with the following configuration:

- DCMI\_PIXCLK polarity: falling

- DCMI\_VSYNC and DCMI\_HSYNC polarity: high

- Data formats: 14 bits

14

| Symbol                                           | Parameter                                     |     | Max | Unit |  |  |

|--------------------------------------------------|-----------------------------------------------|-----|-----|------|--|--|

| -                                                | Frequency ratio DCMI_PIXCLK/f <sub>HCLK</sub> |     | 0.4 |      |  |  |

| DCMI_PIXCLK                                      | Pixel clock input                             | -   | 54  | MHz  |  |  |

| D <sub>Pixel</sub>                               | Pixel clock input duty cycle                  | 30  | 70  | %    |  |  |

| t <sub>su(DATA)</sub>                            | Data input setup time                         | 2   | -   |      |  |  |

| t <sub>h(DATA)</sub>                             | Data input hold time                          | 0.5 | -   |      |  |  |

| t <sub>su(HSYNC)</sub><br>t <sub>su(VSYNC)</sub> | DCMI_HSYNC/DCMI_VSYNC input setup time        |     | -   | ns   |  |  |

| t <sub>h(HSYNC)</sub><br>t <sub>h(VSYNC)</sub>   |                                               |     | _   |      |  |  |

1. Guaranteed by characterization results.

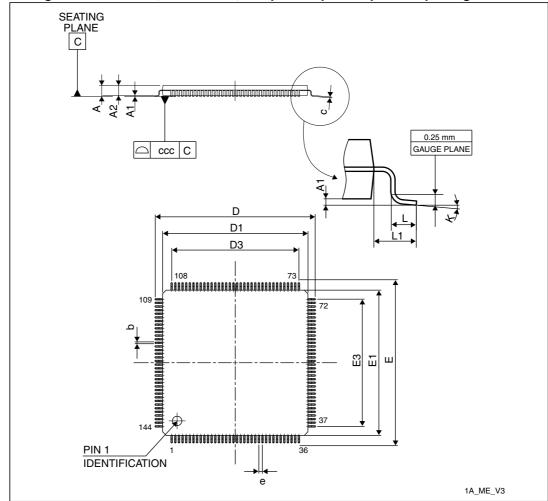

|        |        |             | data   |                       |        |        |  |

|--------|--------|-------------|--------|-----------------------|--------|--------|--|

| Symbol |        | millimeters |        | inches <sup>(1)</sup> |        |        |  |

|        | Min    | Тур         | Мах    | Min                   | Тур    | Мах    |  |

| А      | -      | -           | 1.600  | -                     | -      | 0.0630 |  |

| A1     | 0.050  | -           | 0.150  | 0.0020                | -      | 0.0059 |  |

| A2     | 1.350  | 1.400       | 1.450  | 0.0531                | 0.0551 | 0.0571 |  |

| b      | 0.170  | 0.220       | 0.270  | 0.0067                | 0.0087 | 0.0106 |  |

| с      | 0.090  | -           | 0.200  | 0.0035                | -      | 0.0079 |  |

| D      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| D1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| D3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| E      | 15.800 | 16.000      | 16.200 | 0.6220                | 0.6299 | 0.6378 |  |

| E1     | 13.800 | 14.000      | 14.200 | 0.5433                | 0.5512 | 0.5591 |  |

| E3     | -      | 12.000      | -      | -                     | 0.4724 | -      |  |

| е      | -      | 0.500       | -      | -                     | 0.0197 | -      |  |

| L      | 0.450  | 0.600       | 0.750  | 0.0177                | 0.0236 | 0.0295 |  |

| L1     | -      | 1.000       | -      | -                     | 0.0394 | -      |  |

| k      | 0°     | 3.5°        | 7°     | 0°                    | 3.5°   | 7°     |  |

| ссс    | -      | -           | 0.080  | -                     | -      | 0.0031 |  |

### Table 125. LQPF100, 14 x 14 mm 100-pin low-profile quad flat package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

# 6.2 LQFP144 20 x 20 mm, low-profile quad flat package information

Figure 86. LQFP144, 20 x 20 mm, 144-pin low-profile quad flat package outline

1. Drawing is not to scale.

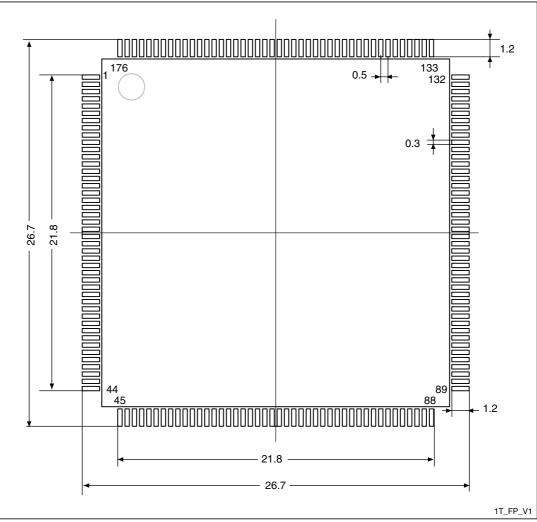

Figure 90. LQFP176, 24 x 24 mm, 176-pin low-profile quad flat package recommended footprint

1. Dimensions are expressed in millimeters.