#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

-XF

| Product Status                  | Obsolete                                                   |

|---------------------------------|------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                             |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                             |

| Speed                           | 266MHz                                                     |

| Co-Processors/DSP               | -                                                          |

| RAM Controllers                 | DDR2                                                       |

| Graphics Acceleration           | No                                                         |

| Display & Interface Controllers | -                                                          |

| Ethernet                        | 10/100/1000Mbps (3)                                        |

| SATA                            | -                                                          |

| USB                             | USB 2.0 (1)                                                |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                           |

| Operating Temperature           | -40°C ~ 105°C (TA)                                         |

| Security Features               | -                                                          |

| Package / Case                  | 473-LFBGA                                                  |

| Supplier Device Package         | 473-MAPBGA (19x19)                                         |

| Purchase URL                    | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mpc8308cvmadd |

|                                 |                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Characteristic                                                                                                                                                                                   | Symbol                                | Recommended Value <sup>1</sup>                                                                                              | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|

| SerDes internal digital power                                                                                                                                                                    | XCOREV <sub>DD</sub>                  | 1.0 V ± 50 mV                                                                                                               | V    |

| SerDes internal digital power                                                                                                                                                                    | XCOREV <sub>SS</sub>                  | 0.0                                                                                                                         | V    |

| SerDes I/O digital power                                                                                                                                                                         | XPADV <sub>DD</sub>                   | 1.0 V ± 50 mV                                                                                                               | V    |

| SerDes analog power for PLL                                                                                                                                                                      | SDAV <sub>DD</sub>                    | 1.0 V ± 50 mV                                                                                                               | V    |

| SerDes analog power for PLL                                                                                                                                                                      | SDAV <sub>SS</sub>                    | 0                                                                                                                           | V    |

| SerDes I/O digital power                                                                                                                                                                         | XPADV <sub>SS</sub>                   | 0                                                                                                                           | V    |

| Core supply voltage                                                                                                                                                                              | V <sub>DD</sub>                       | 1.0 V ± 50 mV                                                                                                               | V    |

| Analog supply for e300 core APLL <sup>2</sup>                                                                                                                                                    | AV <sub>DD1</sub>                     | 1.0 V ± 50 mV                                                                                                               | V    |

| Analog supply for system APLL <sup>2</sup>                                                                                                                                                       | AV <sub>DD2</sub>                     | 1.0 V ± 50 mV                                                                                                               | V    |

| DDR2 DRAM I/O voltage                                                                                                                                                                            | GV <sub>DD</sub>                      | 1.8 V ± 100 mV                                                                                                              | V    |

| Differential reference voltage for DDR controller                                                                                                                                                | MV <sub>REF</sub>                     | $\begin{array}{c} \text{GVDD/2} \text{ (}0.49\times\text{GV}_{DD}\text{ to}\\ 0.51\times\text{GV}_{DD}\text{)} \end{array}$ | V    |

| Standard I/O voltage (Local bus, DUART, system control and power management, eSDHC, USB, I <sup>2</sup> C, Interrupt, Ethernet management, SPI, Miscellaneous and JTAG I/O voltage) <sup>3</sup> | NV <sub>DD</sub>                      | 3.3 V ± 300 mV                                                                                                              | V    |

| eTSEC IO supply <sup>4,5</sup>                                                                                                                                                                   | LV <sub>DD1</sub> , LV <sub>DD2</sub> | 2.5 V ± 125 mV<br>3.3 V ± 300 mV                                                                                            | V    |

| Analog and digital ground                                                                                                                                                                        | V <sub>SS</sub>                       | 0.0                                                                                                                         | V    |

| Operating temperature range <sup>6</sup>                                                                                                                                                         | T <sub>A</sub> /T <sub>J</sub>        | Standard = 0 to 105<br>Extended = -40 to 105                                                                                | °C   |

#### **Table 2. Recommended Operating Conditions**

#### Notes:

<sup>1</sup> GV<sub>DD</sub>, NV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

<sup>2</sup> This voltage is the input to the filter discussed in Section 23.2, "PLL Power Supply Filtering," and not necessarily the voltage at the AV<sub>DD</sub> pin, which may be reduced from V<sub>DD</sub> by the filter.

$^{3}$  NV<sub>DD</sub> here refers to NV<sub>DDA</sub>, NV<sub>DDB</sub>, NV<sub>DDG</sub>, NV<sub>DDH</sub>, NV<sub>DDJ</sub> and NV<sub>DDP\_K</sub> from the ball map.

<sup>4</sup> The max value of supply voltage should be selected based on the RGMII mode. The lower range applies to RGMII mode.

$^5\,$  LV\_{DD1} here refers to NV\_{DDC} and LV\_{DD2} refers to NV\_{DDF} from the ball map.

<sup>6</sup> Minimum temperature is specified with  $T_A$ ; Maximum temperature is specified with  $T_J$ .

This table describes a typical scenario where blocks with the stated percentage of utilization and impedances consume the amount of power described.

| Interface                                              | Parameter                                        | GV <sub>DD</sub><br>(1.8 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DD</sub> /<br>(3.3 V) | LV <sub>DD</sub><br>(2.5 V) | Unit | Comments      |

|--------------------------------------------------------|--------------------------------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|------|---------------|

| DDR2<br>R <sub>s</sub> = 22 Ω<br>R <sub>t</sub> = 75 Ω | 250 MHz<br>32 bits+ECC<br>266 MHz<br>32 bits+ECC | 0.302<br>0.309              | _                           | _                             | _                           | W    | _             |

| Local bus I/O load = 20 pF                             | 62.5 MHz<br>66 MHZ                               | _                           | 0.038<br>0.040              | _                             | —                           | W    | —             |

| TSEC I/O load = 20 pF                                  | MII, 25 MHz                                      | _                           | —                           | 0.008                         | —                           | W    | 2 controllers |

|                                                        | RGMII, 125 MHz                                   | _                           | —                           | 0.078                         | 0.044                       | W    |               |

| eSDHC IO Load = 40 pF                                  | 50 MHz                                           |                             | —                           | 0.008                         | —                           | W    | —             |

| USB IO Load = 20 pF                                    | 60 MHz                                           | _                           | —                           | 0.012                         |                             | W    | —             |

| Other I/O                                              | —                                                | _                           | 0.017                       | _                             | —                           | W    | —             |

Table 5. MPC8308 Typical I/O Power Dissipation

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the device.

### 4.1 DC Electrical Characteristics

This table provides the system clock input (SYS\_CLK\_IN) DC electrical specifications for the device.

Table 6. SYS\_CLK\_IN DC Electrical Characteristics

| Parameter                | Condition                          | Symbol          | Min  | Мах                    | Unit |

|--------------------------|------------------------------------|-----------------|------|------------------------|------|

| Input high voltage       | —                                  | V <sub>IH</sub> | 2.4  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage        | —                                  | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| SYS_CLK_IN input current | $0 \ V \ \leq V_{IN} \leq NV_{DD}$ | I <sub>IN</sub> |      | ±10                    | μΑ   |

This table provides the RTC clock input (RTC\_PIT\_CLOCK) DC electrical specifications for the device.

Table 7. RTC\_PIT\_CLOCK DC Electrical Characteristics

| Parameter          | Condition | Symbol          | Min            | Max | Unit |

|--------------------|-----------|-----------------|----------------|-----|------|

| Input high voltage | _         | V <sub>IH</sub> | 3.3 V – 400 mV |     | V    |

| Input low voltage  | _         | V <sub>IL</sub> | 0              | 0.4 | V    |

### 4.2 AC Electrical Characteristics

The primary clock source for the device is SYS\_CLK\_IN. This table provides the system clock input (SYS\_CLK\_IN) AC timing specifications for the device.

# 6 DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR2 SDRAM interface. Note that DDR2 SDRAM is  $GV_{DD}(typ) = 1.8 V$ .

### 6.1 DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Мах                       | Unit | Note |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.7                       | 1.9                       | V    | 1    |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 \times GV_{DD}$     | V    | 2    |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | —    |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | _    |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | _                         | mA   |      |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | —                         | mA   | —    |

Table 13. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  ${\rm GV}_{\rm DD}$  is expected to be within 50 mV of the DRAM  ${\rm GV}_{\rm DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver.

Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter/Condition                          | Symbol           | Min | Мах | Unit | Notes |

|----------------------------------------------|------------------|-----|-----|------|-------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1     |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1     |

Note:

1. This parameter is sampled.  $GV_{DD} = 1.8 \text{ V} \pm 0.090 \text{ V}$ , f = 1 MHz, T<sub>A</sub> = 25°C,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition              | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μΑ   | 1    |

Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must be able to supply up to 500  $\mu\text{A}$  current.

### 6.2 DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR2 SDRAM interface.

### 6.2.1 DDR2 SDRAM Input AC Timing Specifications

This table provides input AC timing specifications for the DDR2 SDRAM when GV<sub>DD</sub>(typ)=1.8 V.

Table 16. DDR2 SDRAM Input AC Timing Specifications for 1.8 V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.8 ± 100 mV

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.45 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.45 | —                        | V    |       |

This table provides input AC timing specifications for the DDR2 SDRAM interface.

#### Table 17. DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $GV_{DD}$  of 1.8± 100 mV

| Parameter                                    | Symbol              | Min  | Мах | Unit | Notes  |

|----------------------------------------------|---------------------|------|-----|------|--------|

| Controller skew for MDQS—MDQ/MECC<br>266 MHz | <sup>t</sup> CISKEW | -875 | 875 | ps   | 1, 2,3 |

#### Notes:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ or MECC signal is called  $t_{DISKEW}$ . This can be determined by the following equation:  $t_{DISKEW} = +/-(T/4 - abs(t_{CISKEW}))$  where T is the clock period and  $abs(t_{CISKEW})$  is the absolute value of  $t_{CISKEW}$ .

3. Memory controller ODT value of 150  $\Omega$  is recommended

#### DDR2 SDRAM

| Parameter                                       | Symbol <sup>1</sup>                         | Min                     | Max                    | Unit | Notes |

|-------------------------------------------------|---------------------------------------------|-------------------------|------------------------|------|-------|

| MDQ//MDM/MECC output setup with respect to MDQS | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS |                         |                        | ps   | 5     |

| 266 MHz                                         |                                             | 900                     |                        |      |       |

| MDQ//MDM/MECC output hold with respect to MDQS  | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> |                         | _                      | ps   | 5     |

| 266 MHz                                         |                                             | 1100                    |                        |      |       |

| MDQS preamble start                             | t <sub>DDKHMP</sub>                         | 0.75 x t <sub>MCK</sub> | _                      | ns   | 6     |

| MDQS epilogue end                               | t <sub>DDKHME</sub>                         | 0.4 x t <sub>MCK</sub>  | 0.6 x t <sub>MCK</sub> | ns   | 6     |

#### Table 18. DDR2 SDRAM Output AC Timing Specifications (continued)

Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ/MECC/MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. For a description and understanding of the timing modifications enabled by use of these bits, see the MPC8308 PowerQUICC II Pro Processor Reference Manual.

- 5. Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

| Parameters           | Symbol           | Conditions                |                        | Min       | Мах                    | Unit |

|----------------------|------------------|---------------------------|------------------------|-----------|------------------------|------|

| Supply voltage 2.5 V | LV <sub>DD</sub> |                           | _                      | 2.37      | 2.63                   | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -1.0 mA | LV <sub>DD</sub> = Min | 2.00      | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 1.0 mA  | LV <sub>DD</sub> = Min | VSS - 0.3 | 0.40                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                         | LV <sub>DD</sub> = Min | 1.7       | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                         | LV <sub>DD</sub> = Min | -0.3      | 0.70                   | V    |

| Input high current   | I <sub>IH</sub>  | $V_{IN}^{1} = LV_{DD}$    |                        | _         | 15                     | μA   |

| Input low current    | IIL              | V                         | IN <sup>1</sup> = VSS  | -15       | _                      | μΑ   |

#### Table 22. RGMII DC Electrical Characteristics

Note:

1.  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

### 8.2 MII and RGMII AC Timing Specifications

The AC timing specifications for MII and RGMII are presented in this section.

### 8.2.1 MII AC Timing Specifications

This section describes the MII transmit and receive AC timing specifications.

### 8.2.1.1 MII Transmit AC Timing Specifications

This table provides the MII transmit AC timing specifications.

#### Table 23. MII Transmit AC Timing Specifications

At recommended operating conditions with  $LV_{DDA}/LV_{DDB}$  /NV<sub>DD</sub> of 3.3 V ± 0.3V.

| Parameter/Condition                                                   | Symbol <sup>1</sup>                 | Min | Тур | Мах | Unit |

|-----------------------------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| TX_CLK clock period 10 Mbps                                           | t <sub>MTX</sub>                    | _   | 400 | _   | ns   |

| TX_CLK clock period 100 Mbps                                          | t <sub>MTX</sub>                    | _   | 40  | _   | ns   |

| TX_CLK duty cycle                                                     | t <sub>MTXH</sub> /t <sub>MTX</sub> | 35  | _   | 65  | %    |

| TX_CLK to MII data TXD[3:0], TX_ER, TX_EN delay                       | t <sub>MTKHDX</sub>                 | 1   | 5   | 15  | ns   |

| TX_CLK data clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MTXR</sub>                   | 1.0 | _   | 4.0 | ns   |

| TX_CLK data clock fall V <sub>IH</sub> (max) to V <sub>IL</sub> (min) | t <sub>MTXF</sub>                   | 1.0 | _   | 4.0 | ns   |

Note:

The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>MTKHDX</sub> symbolizes MII transmit timing (MT) for the time t<sub>MTX</sub> clock reference (K) going high (H) until data outputs (D) are invalid (X). Note that, in general, the clock reference symbol representation is based on two to three letters representing the clock of a particular functional. For example, the subscript of t<sub>MTX</sub> represents the MII(M) transmit (TX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

#### USB

#### Table 28. GPIO DC Electrical Characteristics (continued)

| Characteristic    | Symbol          | Condition                                         | Min  | Max | Unit |

|-------------------|-----------------|---------------------------------------------------|------|-----|------|

| Input low voltage | V <sub>IL</sub> | —                                                 | -0.3 | 0.8 | V    |

| Input current     | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{IN} \leq \text{NVDD}$ | _    | ± 5 | μΑ   |

### 8.4.2 IEEE 1588 Timer AC Specifications

This table provides the IEEE 1588 timer AC specifications.

#### Table 29. IEEE 1588 Timer AC Specifications

| Parameter                    | Symbol              | Min | Max | Unit | Notes |

|------------------------------|---------------------|-----|-----|------|-------|

| Timer clock cycle time       | t <sub>TMRCK</sub>  | 0   | 70  | MHz  | 1     |

| Input setup to timer clock   | t <sub>TMRCKS</sub> | —   | —   | —    | 2, 3  |

| Input hold from timer clock  | t <sub>TMRCKH</sub> | —   | —   | —    | 2, 3  |

| Output clock to output valid | t <sub>GCLKNV</sub> | 0   | 6   | ns   | —     |

| Timer alarm to output valid  | t <sub>TMRAL</sub>  | —   | —   | —    | 2     |

Note:

1. The timer can operate on rtc\_clock or tmr\_clock. These clocks get muxed and any one of them can be selected.

2. Asynchronous signals.

3. Inputs need to be stable at least one TMR clock.

## 9 USB

### 9.1 USB Dual-Role Controllers

This section provides the AC and DC electrical specifications for the USB-ULPI interface.

### 9.1.1 USB DC Electrical Characteristics

This table lists the DC electrical characteristics for the USB interface.

#### Table 30. USB DC Electrical Characteristics

| Parameter                                            | Symbol          | Min        | Мах        | Unit |

|------------------------------------------------------|-----------------|------------|------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2          | LVDD + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3       | 0.8        | V    |

| Input current                                        | I <sub>IN</sub> | —          | ±5         | μA   |

| High-level output voltage, I <sub>OH</sub> = -100 μA | V <sub>OH</sub> | LVDD – 0.2 | —          | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA   | V <sub>OL</sub> | —          | 0.2        | V    |

Note:

1. The symbol  $V_{IN}$ , in this case, represents the NV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

#### High-Speed Serial Interfaces (HSSI)

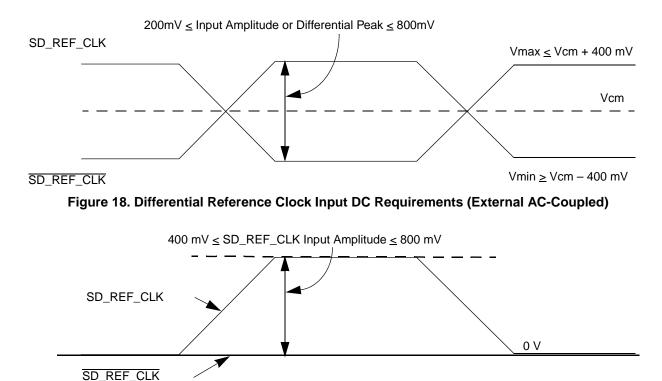

Figure 19. Single-Ended Reference Clock Input DC Requirements

### 10.2.3 Interfacing with Other Differential Signaling Levels

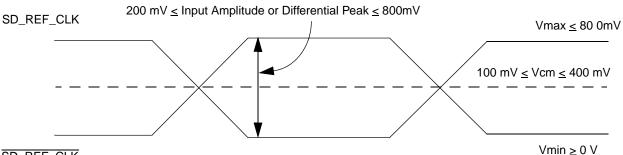

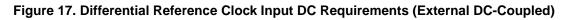

With on-chip termination to XCOREVSS, the differential reference clocks inputs are high-speed current steering logic (HCSL) compatible and DC coupled.

Many other low voltage differential type outputs like low-voltage differential signaling (LVDS) can be used but may need to be AC-coupled due to the limited common mode input range allowed (100–400 mV) for DC-coupled connection.

LVPECL outputs can produce signal with too large amplitude and may need to be DC-biased at clock driver output first, then followed with series attenuation resistor to reduce the amplitude, in addition to AC-coupling.

#### Table 32. SerDes Reference Clock AC Parameters (continued)

At recommended operating conditions with XCOREVDD= 1.0V  $\pm$  5%

| Parameter                                                                | Symbol                | Min | Max | Unit | Notes |

|--------------------------------------------------------------------------|-----------------------|-----|-----|------|-------|

| Rising edge rate (SD_REF_CLK) to falling edge rate (SD_REF_CLK) matching | Rise-Fall<br>Matching | _   | 20  | %    | 1, 4  |

#### Notes:

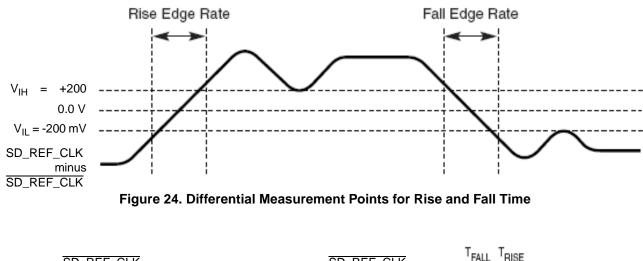

1. Measurement taken from single ended waveform.

2. Measurement taken from differential waveform.

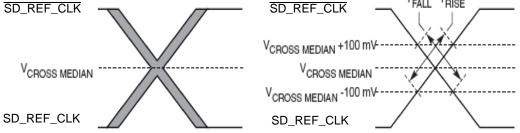

3. Measured from –200 mV to +200 mV on the differential waveform (derived from SD\_REF\_CLK minus SD\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing (Figure 24).

4. Matching applies to rising edge rate for SD\_REF\_CLK and falling edge rate for SD\_REF\_CLK. It is measured using a 200 mV window centered on the median cross point where SD\_REF\_CLK rising meets SD\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of SD\_REF\_CLK should be compared to the Fall Edge Rate of SD\_REF\_CLK, the maximum allowed difference should not exceed 20% of the slowest edge rate (See Figure 25).

#### Figure 25. Single-Ended Measurement Points for Rise and Fall Time Matching

The other detailed AC requirements of the SerDes reference clocks is defined by each interface protocol based on application usage. For detailed information, see the following sections:

• Section 11.2, "AC Requirements for PCI Express SerDes Clocks"

# 15 I<sup>2</sup>C

This section describes the DC and AC electrical characteristics for the  $I^2C$  interface.

### **15.1** I<sup>2</sup>C DC Electrical Characteristics

This table provides the DC electrical characteristics for the  $I^2C$  interface.

#### Table 43. I<sup>2</sup>C DC Electrical Characteristics

At recommended operating conditions with NV\_{DD} of 3.3 V  $\pm$  0.3 V.

| Parameter                                                                                                   | Symbol              | Min                    | Мах                                | Unit | Notes |

|-------------------------------------------------------------------------------------------------------------|---------------------|------------------------|------------------------------------|------|-------|

| Input high voltage level                                                                                    | V <sub>IH</sub>     | $0.7 	imes NV_{DD}$    | NV <sub>DD</sub> + 0.3             | V    | —     |

| Input low voltage level                                                                                     | V <sub>IL</sub>     | -0.3                   | $0.3 \times \text{NV}_{\text{DD}}$ | V    | —     |

| Low level output voltage                                                                                    | V <sub>OL</sub>     | 0                      | $0.2 \times \text{NV}_{\text{DD}}$ | V    | 1     |

| High level output voltage                                                                                   | V <sub>OH</sub>     | 0.8 x NV <sub>DD</sub> | $NV_{DD} + 0.3$                    | V    | —     |

| Output fall time from $V_{IH}(\text{min})$ to $V_{IL}(\text{max})$ with a bus capacitance from 10 to 400 pF | t <sub>I2KLKV</sub> | $20 + 0.1 \times C_B$  | 250                                | ns   | 2     |

| Pulse width of spikes which must be suppressed by the input filter                                          | t <sub>I2KHKL</sub> | 0                      | 50                                 | ns   | 3     |

| Capacitance for each I/O pin                                                                                | CI                  | —                      | 10                                 | pF   | —     |

| Input current, (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> )                                        | I <sub>IN</sub>     | —                      | ± 5                                | μΑ   | —     |

#### Notes:

1. Output voltage (open drain or open collector) condition = 3 mA sink current.

2.  $C_B$  = capacitance of one bus line in pF.

3. For information on the digital filter used, see the MPC8308 PowerQUICC II Pro Processor Reference Manual.

### 15.2 I<sup>2</sup>C AC Electrical Specifications

This table provides the AC timing parameters for the  $I^2C$  interface.

#### Table 44. I<sup>2</sup>C AC Electrical Specifications

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 43).

| Parameter                                                                                    | Symbol <sup>1</sup> | Min | Max              | Unit |

|----------------------------------------------------------------------------------------------|---------------------|-----|------------------|------|

| SCL clock frequency                                                                          | f <sub>I2C</sub>    | 0   | 400              | kHz  |

| Low period of the SCL clock                                                                  | t <sub>I2CL</sub>   | 1.3 | —                | μS   |

| High period of the SCL clock                                                                 | t <sub>I2CH</sub>   | 0.6 | —                | μS   |

| Setup time for a repeated START condition                                                    | t <sub>I2SVKH</sub> | 0.6 | _                | μs   |

| Hold time (repeated) START condition (after this period, the first clock pulse is generated) | t <sub>I2SXKL</sub> | 0.6 | _                | μs   |

| Data setup time                                                                              | t <sub>I2DVKH</sub> | 100 | _                | ns   |

| Data hold time:                                                                              | t <sub>I2DXKL</sub> |     |                  | μs   |

| I <sup>2</sup> C bus devices                                                                 |                     | 02  | 0.9 <sup>3</sup> |      |

| Fall time of both SDA and SCL signals <sup>5</sup>                                           | t <sub>I2CF</sub>   | —   | 300              | ns   |

### 16 Timers

This section describes the DC and AC electrical specifications for the timers.

### **16.1 Timers DC Electrical Characteristics**

This table provides the DC electrical characteristics for the MPC8308 timers pins, including TIN, TOUT, and TGATE.

| Characteristic      | Symbol          | Condition                      | Min  | Max             | Unit |

|---------------------|-----------------|--------------------------------|------|-----------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA      | 2.4  | —               | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA       | _    | 0.5             | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA       | _    | 0.4             | V    |

| Input high voltage  | V <sub>IH</sub> | —                              | 2.1  | $NV_{DD} + 0.3$ | V    |

| Input low voltage   | V <sub>IL</sub> | —                              | -0.3 | 0.8             | V    |

| Input current       | I <sub>IN</sub> | $0~V \leq V_{IN} \leq NV_{DD}$ | _    | ± 5             | μΑ   |

Table 45. Timers DC Electrical Characteristics

### 16.2 Timers AC Timing Specifications

This table provides the timers input and output AC timing specifications.

**Table 46. Timers Input AC Timing Specifications**

| Characteristic                    | Symbol <sup>1</sup> | Min | Unit |

|-----------------------------------|---------------------|-----|------|

| Timers inputs—minimum pulse width | t <sub>TIWID</sub>  | 20  | ns   |

Notes:

1. Timers inputs and outputs are asynchronous to any visible clock. Timers outputs should be synchronized before use by any external synchronous logic. Timers inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation

This figure provides the AC test load for the Timers.

Figure 47. Timers AC Test Load

- 2. Dimensions and tolerances per ASME Y14.5M-1994.

- 3. Maximum solder ball diameter measured parallel to datum A.

- 4. Datum A, the seating plane, is determined by the spherical crowns of the solder balls.

### 20.3 Pinout Listings

This table provides the pin-out listing for the MPC8308, MAPBGA package.

#### Table 53. MPC8308 Pinout Listing

| Signal       | Package Pin Number              | Pin<br>Type | Power<br>Supply      | Note |

|--------------|---------------------------------|-------------|----------------------|------|

|              | DDR Memory Controller Interface |             |                      |      |

| MEMC_MDQ[0]  | V6                              | I/O         | ${\rm GV}_{\rm DDA}$ | —    |

| MEMC_MDQ[1]  | Y4                              | I/O         | GV <sub>DDA</sub>    | —    |

| MEMC_MDQ[2]  | AB3                             | I/O         | GV <sub>DDA</sub>    | —    |

| MEMC_MDQ[3]  | AA3                             | I/O         | ${\rm GV}_{\rm DDA}$ | —    |

| MEMC_MDQ[4]  | AA2                             | I/O         | GV <sub>DDA</sub>    | -    |

| MEMC_MDQ[5]  | AA1                             | I/O         | GV <sub>DDA</sub>    | —    |

| MEMC_MDQ[6]  | W4                              | I/O         | GV <sub>DDA</sub>    | —    |

| MEMC_MDQ[7]  | Y2                              | I/O         | GV <sub>DDA</sub>    | —    |

| MEMC_MDQ[8]  | W3                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[9]  | W1                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[10] | Y1                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[11] | W2                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[12] | U4                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[13] | U3                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[14] | V4                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[15] | U6                              | I/O         | GV <sub>DDA</sub>    | _    |

| MEMC_MDQ[16] | Т3                              | I/O         | GV <sub>DDB</sub>    | _    |

| MEMC_MDQ[17] | T2                              | I/O         | GV <sub>DDB</sub>    | _    |

| MEMC_MDQ[18] | R4                              | I/O         | GV <sub>DDB</sub>    | _    |

| MEMC_MDQ[19] | R3                              | I/O         | GV <sub>DDB</sub>    | _    |

| MEMC_MDQ[20] | P4                              | I/O         | GV <sub>DDB</sub>    | _    |

| MEMC_MDQ[21] | N6                              | I/O         | GV <sub>DDB</sub>    | —    |

| MEMC_MDQ[22] | P2                              | I/O         | GV <sub>DDB</sub>    | —    |

| MEMC_MDQ[23] | P1                              | I/O         | GV <sub>DDB</sub>    | —    |

| MEMC_MDQ[24] | N4                              | I/O         | GV <sub>DDB</sub>    | —    |

| MEMC_MDQ[25] | N3                              | I/O         | GV <sub>DDB</sub>    | 1    |

| MEMC_MDQ[26] | N2                              | I/O         | GV <sub>DDB</sub>    | _    |

| Signal       | Package Pin Number | Pin<br>Type | Power<br>Supply   | Note     |

|--------------|--------------------|-------------|-------------------|----------|

| MEMC_MDQ[27] | M6                 | I/O         | GV <sub>DDB</sub> | _        |

| MEMC_MDQ[28] | M2                 | I/O         | GV <sub>DDB</sub> | _        |

| MEMC_MDQ[29] | M3                 | I/O         | GV <sub>DDB</sub> |          |

| MEMC_MDQ[30] | L2                 | I/O         | GV <sub>DDB</sub> |          |

| MEMC_MDQ[31] | L3                 | I/O         | GV <sub>DDB</sub> |          |

| MEMC_MDM[0]  | AB2                | 0           | GV <sub>DDA</sub> |          |

| MEMC_MDM[1]  | V3                 | 0           | GV <sub>DDA</sub> |          |

| MEMC_MDM[2]  | P3                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MDM[3]  | M7                 | 0           | GV <sub>DDB</sub> | —        |

| MEMC_MDM[8]  | K2                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MDQS[0] | AC3                | I/O         | GV <sub>DDA</sub> |          |

| MEMC_MDQS[1] | V1                 | I/O         | GV <sub>DDA</sub> |          |

| MEMC_MDQS[2] | R1                 | I/O         | GV <sub>DDB</sub> |          |

| MEMC_MDQS[3] | M1                 | I/O         | GV <sub>DDB</sub> |          |

| MEMC_MDQS[8] | K1                 | I/O         | GV <sub>DDB</sub> |          |

| MEMC_MBA[0]  | C3                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MBA[1]  | B2                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MBA[2]  | H4                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA0     | C2                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA1     | D2                 | 0           | GV <sub>DDB</sub> | _        |

| MEMC_MA2     | D3                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA3     | D4                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA4     | E4                 | 0           | GV <sub>DDB</sub> | _        |

| MEMC_MA5     | F4                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA6     | E2                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA7     | E1                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA8     | F2                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA9     | F3                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA10    | C1                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA11    | F7                 | 0           | GV <sub>DDB</sub> |          |

| MEMC_MA12    | G2                 | 0           | GV <sub>DDB</sub> | <b>—</b> |

| MEMC_MA13    | G3                 | 0           | GV <sub>DDB</sub> | _        |

| MEMC_MWE     | D5                 | 0           | GV <sub>DDB</sub> | 1        |

| MEMC_MRAS    | B4                 | 0           | GV <sub>DDB</sub> |          |

Package and Pin Listings

| Signal            | Package Pin Number             | Pin<br>Type | Power<br>Supply     | Note |

|-------------------|--------------------------------|-------------|---------------------|------|

| MEMC_MCAS         | C5                             | 0           | GV <sub>DDB</sub>   | _    |

| MEMC_MCS[0]       | B6                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MCS[1]       | C6                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MCKE         | H3                             | 0           | GV <sub>DDB</sub>   | 3    |

| MEMC_MCK [0]      | A3                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MCK [1]      | U2                             | 0           | GV <sub>DDB</sub>   | _    |

| MEMC_MCK [2]      | G1                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MCK [0]      | A4                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MCK [1]      | U1                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MCK [2]      | H1                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MODT[0]      | A5                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MODT[1]      | B5                             | 0           | GV <sub>DDB</sub>   |      |

| MEMC_MECC[0]      | L4                             | I/O         | GV <sub>DDB</sub>   |      |

| MEMC_MECC[1]      | L6                             | I/O         | GV <sub>DDB</sub>   | _    |

| MEMC_MECC[2]      | K4                             | I/O         | GV <sub>DDB</sub>   | _    |

| MEMC_MECC[3]      | K3                             | I/O         | GV <sub>DDB</sub>   |      |

| MEMC_MECC[4]      | J2                             | I/O         | GV <sub>DDB</sub>   | _    |

| MEMC_MECC[5]      | K6                             | I/O         | GV <sub>DDB</sub>   | _    |

| MEMC_MECC[6]      | J3                             | I/O         | GV <sub>DDB</sub>   |      |

| MEMC_MECC[7]      | J6                             | I/O         | GV <sub>DDB</sub>   |      |

| MV <sub>REF</sub> | G6                             | I           | GV <sub>DDB</sub>   |      |

|                   | Local Bus Controller Interface |             |                     | 1    |

| LD0               | U18                            | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD1               | V18                            | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD2               | U16                            | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD3               | Y20                            | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD4               | AA21                           | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD5               | AC22                           | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD6               | V17                            | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD7               | AB21                           | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD8               | Y19                            | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD9               | AA20                           | I/O         | NV <sub>DDP_K</sub> | 8    |

| LD10              | Y17                            | I/O         | NV <sub>DDP_K</sub> | 8    |

#### Table 53. MPC8308 Pinout Listing (continued)

| Signal              | Package Pin Number | Pin<br>Type | Power<br>Supply     | Note |

|---------------------|--------------------|-------------|---------------------|------|

| IIC_SCL1            | A9                 | I/O         | NV <sub>DDA</sub>   | 2    |

| IIC_SDA2/CKSTOP_OUT | D10                | I/O         | NV <sub>DDA</sub>   | 2    |

| IIC_SCL2/CKSTOP_IN  | C10                | I/O         | NV <sub>DDA</sub>   | 2    |

|                     | Interrupts         |             |                     | I    |

| IRQ[0]/MCP_IN       | A17                | I           | NV <sub>DDB</sub>   | _    |

| IRQ[1]/MCP_OUT      | F16                | I/O         | NV <sub>DDB</sub>   | _    |

| IRQ[2] /CKSTOP_OUT  | B17                | I/O         | NV <sub>DDB</sub>   | _    |

| IRQ[3] /CKSTOP_IN   | A18                | I           | NV <sub>DDB</sub>   | _    |

|                     | JTAG               |             |                     | I    |

| ТСК                 | Y7                 | I           | NV <sub>DDP_K</sub> | —    |

| TDI                 | U9                 | I           | NV <sub>DDP_K</sub> | 4    |

| TDO                 | AC5                | 0           | NV <sub>DDP_K</sub> | 3    |

| TMS                 | AA6                | I           | NV <sub>DDP_K</sub> | 4    |

| TRST                | V8                 | I           | NV <sub>DDP_K</sub> | 4    |

|                     | TEST               |             |                     | I    |

| TEST_MODE           | AC6                | I           | NV <sub>DDP_K</sub> | 5    |

|                     | System Control     |             |                     |      |

| HRESET              | AA9                | I/O         | NV <sub>DDP_K</sub> | 1    |

| PORESET             | AA8                | I           | NV <sub>DDP_K</sub> | —    |

| SRESET              | AB7                | I/O         | NV <sub>DDP_K</sub> | _    |

|                     | Clocks             |             |                     |      |

| SYS_CLK_IN          | AC8                | 1           | NV <sub>DDP_K</sub> |      |

| RTC_PIT_CLOCK       | AA23               | I           | NV <sub>DDJ</sub>   | _    |

|                     | MISC               |             |                     |      |

| QUIESCE             | AA7                | 0           | NV <sub>DDP_K</sub> |      |

| THERMO              | AC7                | I           | NV <sub>DDP_K</sub> | 6    |

|                     | ETSEC1             |             |                     | I    |

| TSEC1_COL           | B20                | I           | NV <sub>DDC</sub>   | —    |

| TSEC1_CRS           | B21                | I           | NV <sub>DDC</sub>   | —    |

| TSEC1_GTX_CLK       | F18                | 0           | NV <sub>DDC</sub>   | 3    |

| TSEC1_RX_CLK        | A22                | I           | NV <sub>DDC</sub>   | -    |

| TSEC1_RX_DV         | D21                | I           | NV <sub>DDC</sub>   | 1 —  |

| TSEC1_RXD[3]        | C22                | I           | NV <sub>DDC</sub>   | 1 —  |

| TSEC1_RXD[2]        | C21                | I           | NV <sub>DDC</sub>   | - 1  |

This table provides the operating frequencies for the device under recommended operating conditions (Table 2).

| Characteristic <sup>1</sup>                      | Maximum Operating Frequency | Unit |

|--------------------------------------------------|-----------------------------|------|

| e300 core frequency ( <i>core_clk</i> )          | 400                         | MHz  |

| Coherent system bus frequency ( <i>csb_clk</i> ) | 133                         | MHz  |

| DDR2 memory bus frequency (MCK) <sup>2</sup>     | 133                         | MHz  |

| Local bus frequency (LCLK0) <sup>3</sup>         | 66                          | MHz  |

Table 55. Operating Frequencies for MPC8308

Notes:

1. The SYS\_CLK\_IN frequency, RCWL[SPMF], and RCWL[COREPLL] settings must be chosen such that the resulting *csb\_clk*, MCK, LCLK0, and *core\_clk* frequencies do not exceed their respective maximum or minimum operating frequencies.

2. The DDR data rate is 2x the DDR memory bus frequency.

3. The local bus frequency is 1/2, 1/4, or 1/8 of the *lbc\_clk* frequency (depending on LCCR[CLKDIV]) which is in turn, 1x or 2x the *csb\_clk* frequency (depending on RCWL[LBCM]).

### 21.2 System PLL Configuration

The system PLL is controlled by the RCWL[SPMF] parameter. This table shows the multiplication factor encodings for the system PLL.

| RCWL[SPMF] | csb_clk: SYS_CLK_IN |

|------------|---------------------|

| 0000       | Reserved            |

| 0001       | Reserved            |

| 0010       | 2 : 1               |

| 0011       | 3 : 1               |

| 0100       | 4 : 1               |

| 0101       | 5 : 1               |

| 0110–1111  | Reserved            |

Table 56. System PLL Ratio

As described in Section 21, "Clocking," the LBCM, DDRCM, and SPMF parameters in the reset configuration word low select the ratio between the primary clock input (SYS\_CLK\_IN) and the internal coherent system bus clock (*csb\_clk*). This table shows the expected frequency values for the CSB frequency for select *csb\_clk* to SYS\_CLK\_IN ratios.

Table 57. CSB Frequency Options

| SPMF<br><i>csb_clk</i> :Input Clock Ratio |     | Input C | lock Frequency (I | MHz)  |

|-------------------------------------------|-----|---------|-------------------|-------|

|                                           |     | 25      | 33.33             | 66.67 |

| 0010                                      | 2:1 |         |                   | 133   |

| 0100                                      | 4:1 |         | 133               |       |

| 0101                                      | 5:1 | 125     | 167               |       |

### 23.3 Decoupling Recommendations

Due to large address and data buses, and high operating frequencies, the device can generate transient power surges and high frequency noise in its power supply, especially while driving large capacitive loads. This noise must be prevented from reaching other components in the MPC8308 system, and the MPC8308 itself requires a clean, tightly regulated source of power. Therefore, it is recommended that the system designer place at least one decoupling capacitor at each  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$  and  $LV_{DD}$  pin of the device. These decoupling capacitors should receive their power from separate  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$ , and  $V_{SS}$  power planes in the PCB, utilizing short traces to minimize inductance. Capacitors may be placed directly under the device using a standard escape pattern. Others may surround the part.

These capacitors should have a value of 0.01 or 0.1  $\mu$ F. Only ceramic SMT (surface mount technology) capacitors should be used to minimize lead inductance, preferably 0402 or 0603 sizes.

In addition, it is recommended that there be several bulk storage capacitors distributed around the PCB, feeding the  $V_{DD}$ ,  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$  planes, to enable quick recharging of the smaller chip capacitors. These bulk capacitors should have a low ESR (equivalent series resistance) rating to ensure the quick response time necessary. They should also be connected to the power and ground planes through two vias to minimize inductance. Suggested bulk capacitors—100 to 330  $\mu$ F (AVX TPS tantalum or Sanyo OSCON). However, customers should work directly with their power regulator vendor for best values and types of bulk capacitors.

### 23.4 Connection Recommendations

To ensure reliable operation, it is highly recommended to connect unused inputs to an appropriate signal level. Unused active low inputs should be tied to  $NV_{DD}$ ,  $GV_{DD}$ ,  $LV_{DD}$  as required. Unused active high inputs should be connected to VSS. All NC (no-connect) signals must remain unconnected.

Power and ground connections must be made to all external  $V_{DD}$ ,  $NV_{DD}$ ,  $AV_{DD1}$ ,  $AV_{DD2}$ ,  $GV_{DD}$ ,  $LV_{DD}$  and  $V_{SS}$  pins of the device.

### 23.5 Output Buffer DC Impedance

The device drivers are characterized over process, voltage, and temperature. For all buses, the driver is a push-pull single-ended driver type (open drain for I<sup>2</sup>C, MDIO and HRESET)

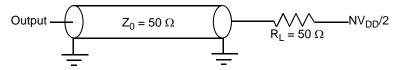

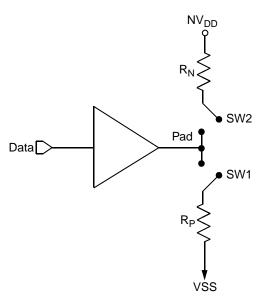

To measure  $Z_0$  for the single-ended drivers, an external resistor is connected from the chip pad to  $NV_{DD}$  or  $V_{SS}$ . Then, the value of each resistor is varied until the pad voltage is  $NV_{DD}/2$  (Figure 55). The output impedance is the average of two components, the resistances of the pull-up and pull-down devices. When data is held high, SW1 is closed (SW2 is open), and  $R_P$  is trimmed until the voltage at the pad equals  $NV_{DD}/2$ .  $R_P$  then becomes the resistance of the pull-up devices.  $R_P$  and  $R_N$  are designed to be close to each other in value. Then,  $Z_0 = (R_P + R_N)/2$ .

#### System Design Information

Figure 55. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal NV<sub>DD</sub>, 105°C.

| Table 6 | 60. Im | pedance | Characteristics |

|---------|--------|---------|-----------------|

|---------|--------|---------|-----------------|

| Impedance      | Local Bus, Ethernet, DUART, Control,<br>Configuration, Power Management | DDR DRAM  | Symbol         | Unit |

|----------------|-------------------------------------------------------------------------|-----------|----------------|------|

| R <sub>N</sub> | 42 Target                                                               | 20 Target | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 42 Target                                                               | 20 Target | Z <sub>0</sub> | Ω    |

**Note:** Nominal supply voltages. See Table 2,  $T_i = 105^{\circ}C$ .

### 23.6 Configuration Pin Muxing

The device provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 K $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While **PORESET** is asserted however, these pins are treated as inputs. The value presented on these pins while **PORESET** is asserted, is latched when **PORESET** deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.

### 23.7 Pull-Up Resistor Requirements

The device requires high resistance pull-up resistors (10 k $\Omega$  is recommended) on open drain type pins including I<sup>2</sup>C, Ethernet management MDIO, HRESET and IPIC (integrated programmable interrupt controller).

Correct operation of the JTAG interface requires configuration of a group of system control pins as demonstrated in Figure 56. Care must be taken to ensure that these pins are maintained at a valid deasserted state under normal operating conditions because most have asynchronous behavior and spurious assertion, which give unpredictable results.

# 24 Ordering Information

This section presents ordering information for the devices discussed in this document, and it shows an example of how the parts are marked. Ordering information for the devices fully covered by this document is provided in Section 24.1, "Part Numbers Fully Addressed by This Document."

### 24.1 Part Numbers Fully Addressed by This Document

This table provides the Freescale part numbering nomenclature for the MPC8308 family. Note that the individual part numbers correspond to a maximum processor core frequency. For available frequencies, contact your local Freescale sales office. In addition to the maximum processor core frequency, the part numbering scheme also includes the maximum effective DDR memory speed. Each part number also contains a revision code which refers to the die mask revision number.

| MPC             | nnnn               | С                                         | VM                         | AD                                           | D                | Α                                          |

|-----------------|--------------------|-------------------------------------------|----------------------------|----------------------------------------------|------------------|--------------------------------------------|

| Product<br>Code | Part<br>Identifier | Temperature<br>Range <sup>1,4</sup>       | Package <sup>2</sup>       | e300 Core<br>Frequency <sup>3</sup>          | DDR<br>Frequency | Revision<br>Level                          |

| MPC             | 8308               | Blank = 0 to<br>105°C<br>C = -40 to 105°C | VM = Pb-free 473<br>MAPBGA | AD = 266 MHz<br>AF = 333 MHz<br>AG = 400 MHz | D = 266 MHz      | Contact local<br>Freescale<br>sales office |

#### Table 61. Part Numbering Nomenclature

Notes:

1. Contact local Freescale office on availability of parts with C temperature range.

2. See Section 20, "Package and Pin Listings," for more information on available package types.

3. Processor core frequencies supported by parts addressed by this specification only. Not all parts described in this specification support all core frequencies. Additionally, parts addressed by Part Number Specifications may support other maximum core frequencies

4. Minimum temperature is specified with  $T_A$ ; Maximum temperature is specified with  $T_J$

# 25 Document Revision History

This table summarizes a revision history for this document.

| Table 63 | . Document | Revision | History |

|----------|------------|----------|---------|

|----------|------------|----------|---------|

| Rev.<br>Number | Date    | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3              | 10/2011 | <ul> <li>In Section 2.1.4, "Power Sequencing," changed description.</li> <li>In Table 53, updated GPIOs pins as I/O.</li> <li>In Table 54, removed PCI Express = csb_clk/2 and csb_clk/3 options.</li> <li>In Table 61, added note 4.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2              | 02/2011 | <ul> <li>Added NV<sub>DDJ</sub> to Note-7 in Table 1.</li> <li>In Table 2,<br/>Added Note-2<br/>Added NV<sub>DDJ</sub> to Note-3<br/>Added "Extended Temperature range from -40 to 105 °C, in the last row of the table<br/>Changed "characteristic name Junction temperature" to "Operating temperature range"</li> <li>In Table 4, Note-3, changed ambient temperature to junction temperature, T<sub>J</sub> = 105° C</li> <li>In Table 18,<br/>t<sub>DDKHCS</sub> changed from 3.15ns to 2.5ns<br/>t<sub>DDKHMP</sub> and t<sub>DDKHME</sub> values updated</li> <li>In Figure 6, corrected t<sub>DDKHMP</sub> &amp; t<sub>DDKHME</sub> waveform</li> <li>In Table 53,<br/>Y23 Package Pin Number changed from NC to V<sub>DD</sub> signal group<br/>TSEC2_CRS is muxed with GPIO[0], shown as TSEC2_CRS/ GPIO[0]</li> <li>In Table 58, note-1, core_clk maximum operating frequency 333 MHz replaced with 400 MHz</li> </ul> |

| 1              | 06/2010 | • In Table 4, $T_A = 105$ replaced with $T_J = 105$<br>• In Table 8, $f_{SYS\_CLK\_IN}$ (Max) = 66 replaced with 66.67 and $t_{SYS\_CLK\_IN}$ (Min) = 15.15 replaced with 15<br>• In Table 53, TSEC1_TMR_RX_ESFD replaced with TSEC2_TMR_RX_ESFD<br>TSEC1_TMR_TX_ESFD replaced with TSEC2_TMR_TX_ESFD<br>TSEC0_TMR_RX_ESFD replaced with TSEC1_TMR_RX_ESFD<br>TSEC0_TMR_TX_ESFD replaced with TSEC1_TMR_RX_ESFD<br>• In Table 56, rows from 1000 to 1111 removed<br>• In Table 57, SPMF 5:1 Option 167 MHz added.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0              | 05/2010 | Initial release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |