#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Last Time Buy                                                          |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | PowerPC e300c3                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 333MHz                                                                 |

| Co-Processors/DSP               | ·                                                                      |

| RAM Controllers                 | DDR2                                                                   |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | 10/100/1000Mbps (3)                                                    |

| SATA                            | -                                                                      |

| USB                             | USB 2.0 (1)                                                            |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                       |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                     |

| Security Features               | -                                                                      |

| Package / Case                  | 473-LFBGA                                                              |

| Supplier Device Package         | 473-MAPBGA (19x19)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mpc8308cvmafda |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

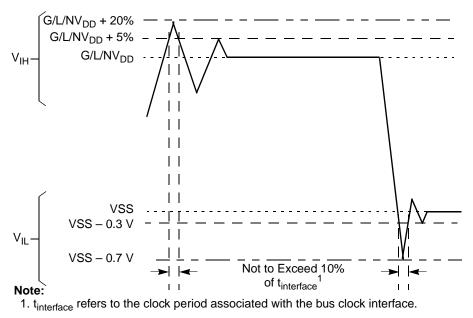

This figure shows the undershoot and overshoot voltages at the interfaces of the device.

Figure 2. Overshoot/Undershoot Voltage for GVDD/NVDD/LVDD

### 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths.

| Driver Type                                                         | Output Impedance ( $\Omega$ ) | Supply Voltage               |

|---------------------------------------------------------------------|-------------------------------|------------------------------|

| Local bus interface utilities signals                               | 42                            | NV <sub>DD</sub> = 3.3 V     |

| DDR2 signals <sup>1</sup>                                           | 18                            | GV <sub>DD</sub> = 1.8 V     |

| DUART, system control, I <sup>2</sup> C, JTAG, eSDHC, GPIO,SPI, USB | 42                            | NV <sub>DD</sub> = 3.3 V     |

| eTSEC signals                                                       | 42                            | LV <sub>DD</sub> = 2.5/3.3 V |

Table 3. Output Drive Capability

Output Impedance can also be adjusted through configurable options in DDR Control Driver Register (DDRCDR). For more information, see the *MPC8308 PowerQUICC II Pro Processor Reference Manual*.

### 2.1.4 Power Sequencing

It is required to apply the core supply voltage ( $V_{DD}$ ) before the I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. The core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V; see Figure 3.

If this recommendation is not observed and I/O voltages are supplied before the core voltage, there might be a period of time that all input and output pins are actively driven and cause contention and excessive current. To overcome side effects of this condition, the application environment may require tuning of external pull-up or pull-down resistors on particular signals to lesser values.

### 5.2 **RESET AC Electrical Characteristics**

This table provides the reset initialization AC timing specifications.

#### **Table 11. RESET Initialization Timing Specifications**

| Parameter/Condition                                                                                        | Min | Max | Unit                    | Notes |

|------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|-------|

| Required assertion time of HRESET (input) to activate reset flow                                           | 32  |     | t <sub>SYS_CLK_IN</sub> | 1     |

| Required assertion time of PORESET with stable power and clock applied to SYS_CLK_IN                       | 32  | —   | t <sub>SYS_CLK_IN</sub> | —     |

| HRESET assertion (output)                                                                                  | 512 |     | t <sub>SYS_CLK_IN</sub> | 1     |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:3]) with respect to negation of PORESET | 4   | —   | <sup>t</sup> sys_clk_in | —     |

| Input hold time for POR configuration signals with respect to negation of HRESET                           | 0   |     | ns                      | _     |

| Time for the device to turn off POR configuration signal drivers with respect to the assertion of HRESET   | —   | 4   | ns                      | 2     |

| Time for the device to turn on POR configuration signal drivers with respect to the negation of HRESET     | 1   | —   | ns                      | 1, 2  |

#### Notes:

1.  $t_{SYS\_CLK\_IN}$  is the clock period of the input clock applied to SYS\_CLK\_IN.

2. POR configuration signals consists of CFG\_RESET\_SOURCE[0:3].

This table provides the PLL lock times.

#### Table 12. PLL Lock Times

| Parameter/Condition     | Min | Мах | Unit | Note |

|-------------------------|-----|-----|------|------|

| System PLL lock time    | —   | 100 | μs   | —    |

| e300 core PLL lock time | —   | 100 | μs   | —    |

This table provides the current draw characteristics for MV<sub>REF</sub>.

Table 15. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition              | Symbol             | Min | Max | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> |     | 500 | μΑ   | 1    |

Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must be able to supply up to 500  $\mu\text{A}$  current.

### 6.2 DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR2 SDRAM interface.

### 6.2.1 DDR2 SDRAM Input AC Timing Specifications

This table provides input AC timing specifications for the DDR2 SDRAM when GV<sub>DD</sub>(typ)=1.8 V.

Table 16. DDR2 SDRAM Input AC Timing Specifications for 1.8 V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.8 ± 100 mV

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Notes |

|-----------------------|-----------------|--------------------------|--------------------------|------|-------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.45 | V    | —     |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.45 | —                        | V    |       |

This table provides input AC timing specifications for the DDR2 SDRAM interface.

#### Table 17. DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $GV_{DD}$  of 1.8± 100 mV

| Parameter                                    | Symbol              | Min  | Мах | Unit | Notes  |

|----------------------------------------------|---------------------|------|-----|------|--------|

| Controller skew for MDQS—MDQ/MECC<br>266 MHz | <sup>t</sup> CISKEW | -875 | 875 | ps   | 1, 2,3 |

#### Notes:

1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[n] and any corresponding bit that is captured with MDQS[n]. This should be subtracted from the total timing budget.

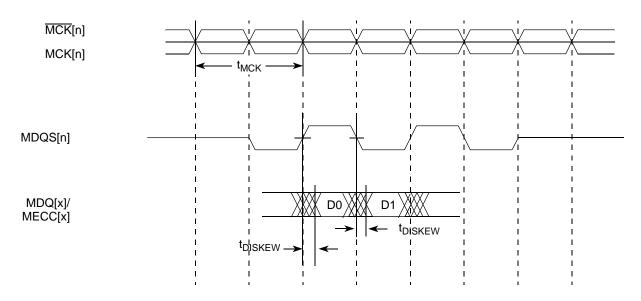

2. The amount of skew that can be tolerated from MDQS to a corresponding MDQ or MECC signal is called  $t_{DISKEW}$ . This can be determined by the following equation:  $t_{DISKEW} = +/-(T/4 - abs(t_{CISKEW}))$  where T is the clock period and  $abs(t_{CISKEW})$  is the absolute value of  $t_{CISKEW}$ .

3. Memory controller ODT value of 150  $\Omega$  is recommended

#### DDR2 SDRAM

This figure illustrates the DDR2 input timing diagram showing the  $t_{\text{DISKEW}}$  timing parameter.

Figure 4. Timing Diagram for t<sub>DISKEW</sub>

### 6.2.2 DDR2 SDRAM Output AC Timing Specifications

| Parameter                                 | Symbol <sup>1</sup> | Min  | Max | Unit | Notes |

|-------------------------------------------|---------------------|------|-----|------|-------|

| MCK[n] cycle time, MCK[n]/MCK[n] crossing | t <sub>MCK</sub>    | 7.5  | 10  | ns   | 2     |

| ADDR/CMD output setup with respect to MCK | t <sub>DDKHAS</sub> |      | —   | ns   | 3     |

| 266 MHz                                   |                     | 2.9  |     |      |       |

| ADDR/CMD output hold with respect to MCK  | t <sub>DDKHAX</sub> |      |     | ns   | 3     |

| 266 MHz                                   |                     | 2.33 |     |      |       |

| MCS[n] output setup with respect to MCK   | t <sub>DDKHCS</sub> |      |     | ns   | 3     |

| 266 MHz                                   |                     | 2.5  |     |      |       |

| MCS[n] output hold with respect to MCK    | t <sub>DDKHCX</sub> |      | _   | ns   | 3     |

| 266 MHz                                   |                     | 3.15 |     |      |       |

| MCK to MDQS Skew                          | t <sub>DDKHMH</sub> | -0.6 | 0.6 | ns   | 4     |

#### Table 18. DDR2 SDRAM Output AC Timing Specifications

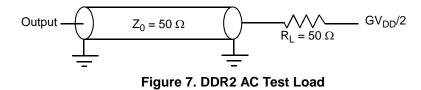

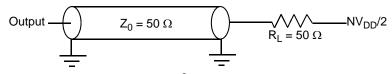

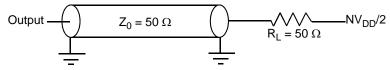

This figure provides the AC test load for the DDR2 bus.

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

### 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

| Parameter                                                           | Symbol          | Min                    | Мах                    | Unit |

|---------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                            | V <sub>IH</sub> | 2.1                    | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage NVDD                                        | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$                  | V <sub>OH</sub> | NV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$                    | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> ) | I <sub>IN</sub> | —                      | ± 5                    | μΑ   |

#### Table 19. DUART DC Electrical Characteristics

### 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

Table 20. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Notes |

|-------------------|-------------|------|-------|

| Minimum baud rate | 256         | baud | —     |

| Maximum baud rate | > 1,000,000 | baud | 1     |

| Oversample rate   | 16          |      | 2     |

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management. MPC8308 supports dual Ethernet controllers.

### 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RGMII Electrical Characteristics

The electrical characteristics specified here apply to all the media independent interface (MII) and reduced gigabit media independent interface (RGMII), signals except management data input/output (MDIO) and management data clock (MDC). The RGMII interface is defined for 2.5 V, while the MII interface can be operated at 3.3 V. The RGMII interface follows the Hewlett-Packard reduced pin-count interface for Gigabit Ethernet Physical Layer Device Specification Version 1.2a (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.3, "Ethernet Management Interface Electrical Characteristics."

### 8.1.1 eTSEC DC Electrical Characteristics

All MII and RGMII drivers and receivers comply with the DC parametric attributes specified in Table 21 and Table 22. The RGMII signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

| Parameter            | Symbol           | Conditions                                      |                        | Min  | Max                    | Unit |

|----------------------|------------------|-------------------------------------------------|------------------------|------|------------------------|------|

| Supply voltage 3.3 V | LV <sub>DD</sub> | —                                               |                        | 3.0  | 3.6                    | V    |

| Output high voltage  | V <sub>OH</sub>  | I <sub>OH</sub> = -4.0 mA                       | LV <sub>DD</sub> = Min | 2.40 | LV <sub>DD</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>  | I <sub>OL</sub> = 4.0 mA                        | LV <sub>DD</sub> = Min | VSS  | 0.50                   | V    |

| Input high voltage   | V <sub>IH</sub>  | —                                               | _                      | 2.1  | LV <sub>DD</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>  | —                                               | _                      | -0.3 | 0.90                   | V    |

| Input high current   | I <sub>IH</sub>  | V <sub>IN</sub> <sup>1</sup> = LV <sub>DD</sub> |                        | —    | 40                     | μΑ   |

| Input low current    | Ι <sub>ΙL</sub>  | V <sub>IN</sub>                                 | <sup>1</sup> = VSS     | -600 | —                      | μA   |

#### Table 21. MII DC Electrical Characteristics

#### Note:

1. The symbol  $V_{IN}$ , in this case, represents the LV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

#### Ethernet: Three-Speed Ethernet, MII Management

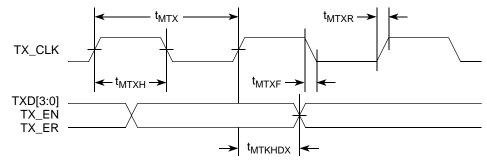

This figure shows the MII transmit AC timing diagram.

Figure 8. MII Transmit AC Timing Diagram

#### 8.2.1.2 **MII Receive AC Timing Specifications**

This table provides the MII receive AC timing specifications.

#### Table 24. MII Receive AC Timing Specifications

At recommended operating conditions with  $LV_{DD}$  /NV<sub>DD</sub> of 3.3 V ± 0.3V.

| Parameter/Condition                                              | Symbol <sup>1</sup>                 | Min  | Тур | Мах | Unit |

|------------------------------------------------------------------|-------------------------------------|------|-----|-----|------|

| RX_CLK clock period 10 Mbps                                      | t <sub>MRX</sub>                    | _    | 400 | _   | ns   |

| RX_CLK clock period 100 Mbps                                     | t <sub>MRX</sub>                    | —    | 40  | —   | ns   |

| RX_CLK duty cycle                                                | t <sub>MRXH</sub> /t <sub>MRX</sub> | 35   | _   | 65  | %    |

| RXD[3:0], RX_DV, RX_ER setup time to RX_CLK                      | t <sub>MRDVKH</sub>                 | 10.0 | _   | —   | ns   |

| RXD[3:0], RX_DV, RX_ER hold time to RX_CLK                       | t <sub>MRDXKH</sub>                 | 10.0 | _   | —   | ns   |

| RX_CLK clock rise V <sub>IL</sub> (min) to V <sub>IH</sub> (max) | t <sub>MRXR</sub>                   | 1.0  | _   | 4.0 | ns   |

| RX_CLK clock fall time $V_{IH}(max)$ to $V_{IL}(min)$            | t <sub>MRXF</sub>                   | 1.0  | _   | 4.0 | ns   |

#### Note:

1. The symbols used for timing specifications herein follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>MRDVKH</sub> symbolizes MII receive timing (MR) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>MRX</sub> clock reference</sub> (K) going to the high (H) state or setup time. Also, t<sub>MRDXKL</sub> symbolizes MII receive timing (GR) with respect to the time data input signals (D) went invalid (X) relative to the t<sub>MRX</sub> clock reference (K) going to the low (L) state or hold time. Note that, in general, the clock reference symbol representation is based on three letters representing the clock of a particular functional. For example, the subscript of t<sub>MRX</sub> represents the MII (M) receive (RX) clock. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

#### USB

#### Table 28. GPIO DC Electrical Characteristics (continued)

| Characteristic    | Symbol          | Condition                                         | Min  | Max | Unit |

|-------------------|-----------------|---------------------------------------------------|------|-----|------|

| Input low voltage | V <sub>IL</sub> | —                                                 | -0.3 | 0.8 | V    |

| Input current     | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{IN} \leq \text{NVDD}$ | _    | ± 5 | μΑ   |

### 8.4.2 IEEE 1588 Timer AC Specifications

This table provides the IEEE 1588 timer AC specifications.

#### Table 29. IEEE 1588 Timer AC Specifications

| Parameter                    | Symbol              | Min | Max | Unit | Notes |

|------------------------------|---------------------|-----|-----|------|-------|

| Timer clock cycle time       | t <sub>TMRCK</sub>  | 0   | 70  | MHz  | 1     |

| Input setup to timer clock   | t <sub>TMRCKS</sub> | —   | —   | —    | 2, 3  |

| Input hold from timer clock  | t <sub>TMRCKH</sub> | —   | —   | —    | 2, 3  |

| Output clock to output valid | t <sub>GCLKNV</sub> | 0   | 6   | ns   | —     |

| Timer alarm to output valid  | t <sub>TMRAL</sub>  | —   | —   | —    | 2     |

Note:

1. The timer can operate on rtc\_clock or tmr\_clock. These clocks get muxed and any one of them can be selected.

2. Asynchronous signals.

3. Inputs need to be stable at least one TMR clock.

# 9 USB

### 9.1 USB Dual-Role Controllers

This section provides the AC and DC electrical specifications for the USB-ULPI interface.

### 9.1.1 USB DC Electrical Characteristics

This table lists the DC electrical characteristics for the USB interface.

#### Table 30. USB DC Electrical Characteristics

| Parameter                                            | Symbol          | Min        | Мах        | Unit |

|------------------------------------------------------|-----------------|------------|------------|------|

| High-level input voltage                             | V <sub>IH</sub> | 2          | LVDD + 0.3 | V    |

| Low-level input voltage                              | V <sub>IL</sub> | -0.3       | 0.8        | V    |

| Input current                                        | I <sub>IN</sub> | —          | ±5         | μA   |

| High-level output voltage, I <sub>OH</sub> = -100 μA | V <sub>OH</sub> | LVDD – 0.2 | —          | V    |

| Low-level output voltage, I <sub>OL</sub> = 100 μA   | V <sub>OL</sub> | —          | 0.2        | V    |

Note:

1. The symbol  $V_{IN}$ , in this case, represents the NV<sub>IN</sub> symbol referenced in Table 1 and Table 2.

#### High-Speed Serial Interfaces (HSSI)

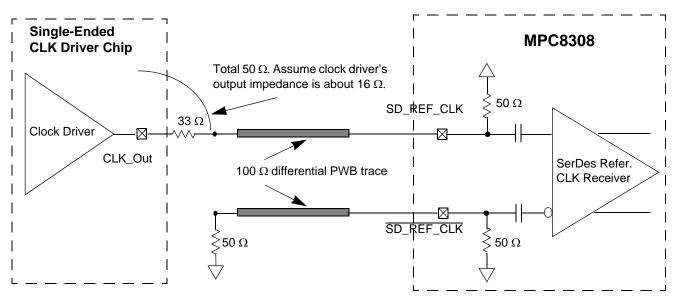

This figure shows the SerDes reference clock connection reference circuits for a single-ended clock driver. It assumes the DC levels of the clock driver are compatible with the device's SerDes reference clock input's DC requirement.

Figure 23. Single-Ended Connection (Reference Only)

### **10.2.4 AC Requirements for SerDes Reference Clocks**

The clock driver selected should provide a high quality reference clock with low phase noise and cycle-to-cycle jitter. Phase noise less than 100 kHz can be tracked by the PLL and data recovery loops and is less of a problem. Phase noise above 15 MHz is filtered by the PLL. The most problematic phase noise occurs in the 1–15 MHz range. The source impedance of the clock driver should be 50  $\Omega$  to match the transmission line and reduce reflections which are a source of noise to the system.

This table describes some AC parameters for PCI Express protocol.

| Table 32. SerDes | S Reference | <b>Clock AC</b> | Parameters |

|------------------|-------------|-----------------|------------|

|------------------|-------------|-----------------|------------|

At recommended operating conditions with XCOREVDD=  $1.0V \pm 5\%$

| Parameter                       | Symbol          | Min  | Max  | Unit | Notes |

|---------------------------------|-----------------|------|------|------|-------|

| Rising Edge Rate                | Rise Edge Rate  | 1.0  | 4.0  | V/ns | 2, 3  |

| Falling Edge Rate               | Fall Edge Rate  | 1.0  | 4.0  | V/ns | 2, 3  |

| Differential Input High Voltage | V <sub>IH</sub> | +200 |      | mV   | 2     |

| Differential Input Low Voltage  | V <sub>IL</sub> | —    | -200 | mV   | 2     |

#### NOTE

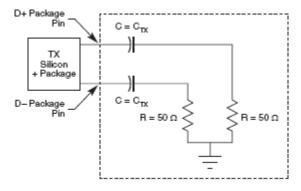

The reference impedance for return loss measurements is  $50 \Omega$  to ground for both the D+ and D- line (that is, as measured by a Vector Network Analyzer with 50  $\Omega$  probes—see Figure 29). Note that the series capacitors, C<sub>PEACCTX</sub>, are optional for the return loss measurement.

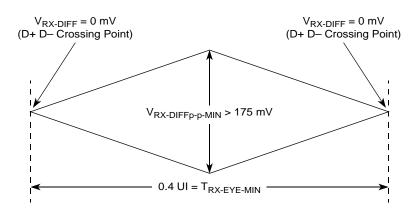

Figure 28. Minimum Receiver Eye Timing and Voltage Compliance Specification

#### **11.5.1** Compliance Test and Measurement Load

The AC timing and voltage parameters must be verified at the measurement point, as specified within 0.2 inches of the package pins, into a test/measurement load shown in Figure 29.

#### NOTE

The allowance of the measurement point to be within 0.2 inches of the package pins is meant to acknowledge that package/board routing may benefit from D+ and D– not being exactly matched in length at the package pin boundary.

Figure 29. Compliance Test/Measurement Load

### 12 Enhanced Local Bus

This section describes the DC and AC electrical specifications for the enhanced local bus interface.

### 13.2.2 Full Speed Input Path (Read)

This figure provides the data and command input timing diagram.

Figure 36. Full Speed Input Path

### 13.3 eSDHC AC Timing Specifications

This table provides the eSDHC AC timing specifications.

#### Table 40. eSDHC AC Timing Specifications for High Speed Mode

At recommended operating conditions NV<sub>DD</sub> = 3.3 V  $\pm$  300 mV.

| Parameter                                           | Symbol <sup>1</sup>                         | Min | Мах | Unit | Notes |

|-----------------------------------------------------|---------------------------------------------|-----|-----|------|-------|

| SD_CLK clock frequency—high speed mode              | f <sub>sнscк</sub>                          | 0   | 50  | MHz  | 3     |

| SD_CLK clock cycle                                  | t <sub>SHSCK</sub>                          | 20  | —   | ns   | _     |

| SD_CLK clock frequency—identification mode          | fsidck                                      | 0   | 400 | kHz  | _     |

| SD_CLK clock low time                               | t <sub>SHSCKL</sub>                         | 7   | —   | ns   | 2     |

| SD_CLK clock high time                              | t <sub>sнscкн</sub>                         | 7   | —   | ns   | 2     |

| SD_CLK clock rise and fall times                    | t <sub>SHSCKR∕</sub><br>t <sub>SHSCKF</sub> | —   | 3   | ns   | 2     |

| Input setup times: SD_CMD, SD_DATx                  | t <sub>SHSIVKH</sub>                        | 3   | —   | ns   | 2     |

| Input hold times: SD_CMD, SD_DATx                   | t <sub>SHSIXKH</sub>                        | 2   | —   | ns   | 2     |

| Output delay time: SD_CLK to SD_CMD, SD_DATx valid  | t <sub>SHSKHOV</sub>                        | 3   | —   | ns   | 2     |

| Output Hold time: SD_CLK to SD_CMD, SD_DATx invalid | t <sub>SHSKHOX</sub>                        | -3  | —   | ns   | 2     |

| SD Card Input Setup                                 | t <sub>ISU</sub>                            | 6   | —   | ns   | 3     |

| SD Card Input Hold                                  | t <sub>IH</sub>                             | 2   | —   | ns   | 3     |

#### Enhanced Secure Digital Host Controller (eSDHC)

#### Table 40. eSDHC AC Timing Specifications for High Speed Mode (continued)

At recommended operating conditions NV<sub>DD</sub> =  $3.3 \text{ V} \pm 300 \text{ mV}$ .

| Parameter            | Symbol <sup>1</sup> | Min | Max | Unit | Notes |

|----------------------|---------------------|-----|-----|------|-------|

| SD Card Output Valid | t <sub>ODLY</sub>   | _   | 14  | ns   | 3     |

| SD Card Output Hold  | t <sub>OH</sub>     | 2.5 | _   | ns   | 3     |

### Notes:

The symbols used for timing specifications herein follow the pattern of  $t_{(first three letters of functional block)(signal)(state) (reference)(state)}$  for inputs and  $t_{(first three letters of functional block)(reference)(state)(signal)(state)}$  for outputs. For example,  $t_{SFSIXKH}$  symbolizes eSDHC full mode speed device timing (SFS) input (I) to go invalid (X) with respect to the clock reference (K) going to high (H). Also  $t_{SFSKHOV}$  symbolizes eSDHC full speed timing (SFS) for the clock reference (K) to go high (H), with respect to the output (O) going valid (V) or data output valid time. Note that, in general, the clock reference symbol representation is based on five letters representing the clock of a particular functional. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

- <sup>2</sup> Measured at capacitive load of 40 pF.

- <sup>3</sup> For reference only, according to the SD card specifications.

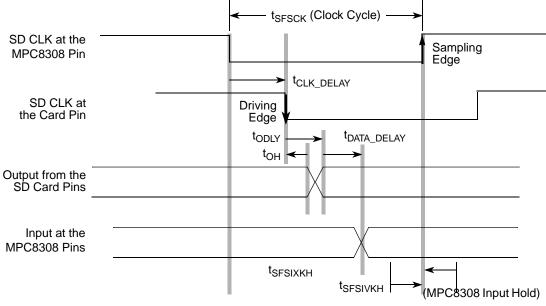

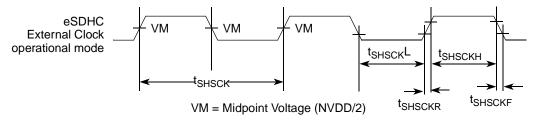

This figure provides the eSDHC clock input timing diagram.

Figure 37. eSDHC Clock Input Timing Diagram

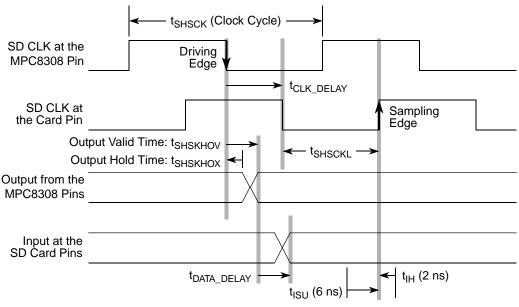

### 13.3.1 High Speed Output Path (Write)

This figure provides the data and command output timing diagram.

Figure 38. High Speed Output Path

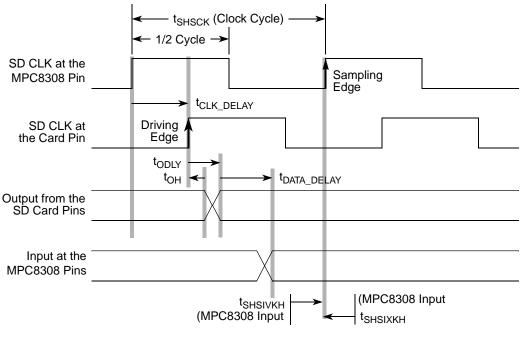

### 13.3.2 High Speed Input Path (Read)

This figure provides the data and command input timing diagram.

Figure 39. High Speed Input Path

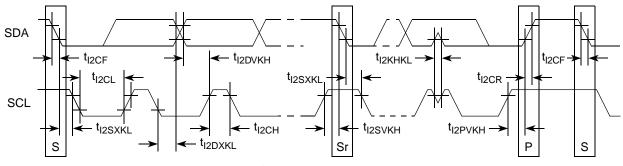

I<sup>2</sup>C

#### Table 44. I<sup>2</sup>C AC Electrical Specifications (continued)

All values refer to  $V_{IH}$  (min) and  $V_{IL}$  (max) levels (see Table 43).

| Parameter                                                                       | Symbol <sup>1</sup> | Min                                | Max | Unit |

|---------------------------------------------------------------------------------|---------------------|------------------------------------|-----|------|

| Setup time for STOP condition                                                   | t <sub>I2PVKH</sub> | 0.6                                | _   | μS   |

| Bus free time between a STOP and START condition                                | t <sub>I2KHDX</sub> | 1.3                                | _   | μS   |

| Noise margin at the LOW level for each connected device (including hysteresis)  | V <sub>NL</sub>     | $0.1 \times \text{NV}_{\text{DD}}$ | _   | V    |

| Noise margin at the HIGH level for each connected device (including hysteresis) | V <sub>NH</sub>     | $0.2 \times \text{NV}_{\text{DD}}$ | _   | V    |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state) (reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. For example, t<sub>I2DVKH</sub> symbolizes I<sup>2</sup>C timing (I2) with respect to the time data input signals (D) reach the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. Also, t<sub>I2SXKL</sub> symbolizes I<sup>2</sup>C timing (I2) for the time that the data with respect to the start condition (S) went invalid (X) relative to the t<sub>I2C</sub> clock reference (K) going to the stop condition (P) reaching the valid state (V) relative to the t<sub>I2C</sub> clock reference (K) going to the high (H) state or setup time. For rise and fall times, the latter convention is used with the appropriate letter: R (rise) or F (fall).

</sub>

- 2. The device provides a hold time of at least 300 ns for the SDA signal (referred to the V<sub>IHmin</sub> of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum  $t_{I2DXKL}$  has only to be met if the device does not stretch the LOW period ( $t_{I2CL}$ ) of the SCL signal.

- 4.  $C_B$  = capacitance of one bus line in pF.

- 5. The device does not follow the  $l^2$ *C-BUS Specifications, Version 2.1,* regarding the t<sub>I2CF</sub> AC parameter.

This figure provides the AC test load for the  $I^2C$ .

Figure 45. I<sup>2</sup>C AC Test Load

This figure shows the AC timing diagram for the  $I^2C$  bus.

Figure 46. I<sup>2</sup>C Bus AC Timing Diagram

GPIO

# 17 GPIO

This section describes the DC and AC electrical specifications for the GPIO of MPC8308

### 17.1 GPIO DC Electrical Characteristics

This table provides the DC electrical characteristics for the GPIO.

Characteristic Condition Symbol Min Max Unit Output high voltage V VOH  $I_{OH} = -8.0 \text{ mA}$ 2.4 \_\_\_\_ V Output low voltage VOL  $I_{OL} = 8.0 \text{ mA}$ 0.5 Output low voltage  $V_{OL}$ 0.4 V  $I_{OI} = 3.2 \text{ mA}$ \_\_\_\_ Input high voltage 2.1  $NV_{DD} + 0.3$ V VIH Input low voltage  $V_{IL}$ -0.30.8 V Input current  $0~V \leq V_{IN} \leq NV_{DD}$ μΑ  $I_{IN}$ \_\_\_\_ ± 5

#### Table 47. GPIO DC Electrical Characteristic

### 17.2 GPIO AC Timing Specifications

This table provides the GPIO input and output AC timing specifications.

Table 48. GPIO Input AC Timing Specifications

| Characteristic                  | Symbol <sup>1</sup> | Min | Unit |

|---------------------------------|---------------------|-----|------|

| GPIO inputs—minimum pulse width | t <sub>PIWID</sub>  | 20  | ns   |

Note:

1. GPIO inputs and outputs are asynchronous to any visible clock. GPIO outputs should be synchronized before use by any external synchronous logic. GPIO inputs are required to be valid for at least t<sub>PIWID</sub> ns to ensure proper operation.

This figure provides the AC test load for the GPIO.

Figure 48. GPIO AC Test Load

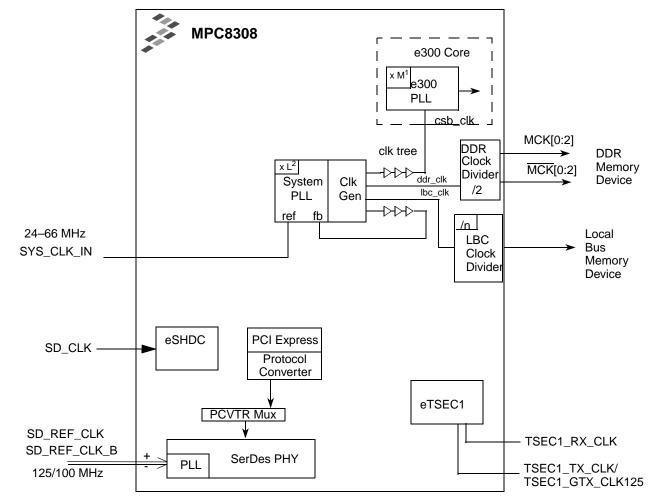

# 21 Clocking

This figure shows the internal distribution of clocks within the device.

<sup>1</sup> Multiplication factor M = 1, 1.5, 2, 2.5, and 3. Value is decided by RCWLR[COREPLL].

<sup>2</sup> Multiplication factor L = 2, 3, 4, 5 and 6. Value is decided by RCWLR[SPMF].

#### Figure 53. MPC8308 Clock Subsystem

The following external clock sources are utilized on the MPC8308:

- System clock (SYS\_CLK\_IN)

- Ethernet Clock (TSEC1\_RX\_CLK/TSEC1\_TX\_CLK/TSEC1\_GTX\_CLK125 for eTSEC)

- SerDes PHY clock

- eSHDC clock (SD\_CLK)

For more information, see the SerDes chapter in the *MPC8308 PowerQUICC II Pro Processor Reference Manual.*

All clock inputs can be supplied using an external canned oscillator, a clock generation chip, or some other source that provides a standard CMOS square wave input.

Thermal

### 21.3 Core PLL Configuration

RCWL[COREPLL] selects the ratio between the internal coherent system bus clock (*csb\_clk*) and the e300 core clock (*core\_clk*). This table shows the encodings for RCWL[COREPLL]. COREPLL values that are not listed in this table should be considered as reserved.

#### NOTE

Core VCO frequency = core frequency  $\times$  VCO divider. The VCO divider, which is determined by RCWLR[COREPLL], must be set properly so that the core VCO frequency is in the range of 400–800 MHz.

| RCW | L[COREF | PLL] | core_clk: csb_clk Ratio <sup>1</sup>                           | VCO Divider (VCOD) <sup>2</sup>                                |

|-----|---------|------|----------------------------------------------------------------|----------------------------------------------------------------|

| 0–1 | 2–5     | 6    | Core_cik. CSD_cik Ralio                                        |                                                                |

| nn  | 0000    | 0    | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) | PLL bypassed<br>(PLL off, <i>csb_clk</i> clocks core directly) |

| 11  | nnnn    | n    | n/a                                                            | n/a                                                            |

| 00  | 0001    | 0    | 1:1                                                            | 2                                                              |

| 01  | 0001    | 0    | 1:1                                                            | 4                                                              |

| 10  | 0001    | 0    | 1:1                                                            | 8                                                              |

| 00  | 0001    | 1    | 1.5:1                                                          | 2                                                              |

| 01  | 0001    | 1    | 1.5:1                                                          | 4                                                              |

| 10  | 0001    | 1    | 1.5:1                                                          | 8                                                              |

| 00  | 0010    | 0    | 2:1                                                            | 2                                                              |

| 01  | 0010    | 0    | 2:1                                                            | 4                                                              |

| 10  | 0010    | 0    | 2:1                                                            | 8                                                              |

| 00  | 0010    | 1    | 2.5:1                                                          | 2                                                              |

| 01  | 0010    | 1    | 2.5:1                                                          | 4                                                              |

| 10  | 0010    | 1    | 2.5:1                                                          | 8                                                              |

| 00  | 0011    | 0    | 3:1                                                            | 2                                                              |

| 01  | 0011    | 0    | 3:1                                                            | 4                                                              |

| 10  | 0011    | 0    | 3:1                                                            | 8                                                              |

#### Table 58. e300 Core PLL Configuration

Note:

<sup>1</sup> For any *core\_clk:csb\_clk* ratios, the *core\_clk* must not exceed its maximum operating frequency of 400 MHz.

<sup>2</sup> Core VCO frequency = core frequency × VCO divider. Note that VCO divider has to be set properly so that the core VCO frequency is in the range of 400–800 MHz.

# 22 Thermal

This section describes the thermal specifications of the device.

### 22.1 Thermal Characteristics

This table provides the package thermal characteristics for the 473,  $19 \times 19$  mm MAPBGA.

| Characteristic                         | Board Type              | Symbol               | Value | Unit | Note    |

|----------------------------------------|-------------------------|----------------------|-------|------|---------|

| Junction to Ambient Natural Convection | Single layer board (1s) | $R_{	ext{	heta}JA}$  | 42    | °C/W | 1, 2    |

| Junction to Ambient Natural Convection | Four layer board (2s2p) | $R_{	ext{	heta}JA}$  | 27    | °C/W | 1, 2, 3 |

| Junction to Ambient (@200 ft/min)      | Single layer board (1s) | $R_{	ext{	heta}JMA}$ | 35    | °C/W | 1, 3    |

| Junction to Ambient (@200 ft/min)      | Four layer board (2s2p) | $R_{	ext{	heta}JMA}$ | 24    | °C/W | 1, 3    |

| Junction to Board                      | —                       | $R_{	heta JB}$       | 17    | °C/W | 4       |

| Junction to Case                       | —                       | $R_{	ext{	heta}JC}$  | 9     | °C/W | 5       |

| Junction to Package Top                | Natural Convection      | $\Psi_{JT}$          | 2     | °C/W | 6       |

#### Notes:

1. Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.

- 2. Per JEDEC JESD51-2 with the single layer board horizontal. Board meets JESD51-9 specification.

- 3. Per JEDEC JESD51-6 with the board horizontal.

- 4. Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.

- 5. Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

- 6. Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

### 22.2 Thermal Management Information

For the following sections,  $P_D = (V_{DD} \times I_{DD}) + P_{I/O}$ , where  $P_{I/O}$  is the power dissipation of the I/O drivers.

# 22.2.1 Estimation of Junction Temperature with Junction-to-Ambient Thermal Resistance

An estimation of the chip junction temperature, T<sub>J</sub>, can be obtained from the equation:

$$T_J = T_A + (R_{\theta JA} \times P_D)$$

where:

$T_I$  = junction temperature (°C)

$T_A$  = ambient temperature for the package (°C)

$R_{\theta JA}$  = junction-to-ambient thermal resistance (°C/W)

$P_D$  = power dissipation in the package (W)

The junction-t-ambient thermal resistance is an industry standard value that provides a quick and easy estimation of thermal performance. As a general statement, the value obtained on a single layer board is

System Design Information

# 23 System Design Information

This section provides electrical and thermal design recommendations for successful application of the device

### 23.1 System Clocking

The device includes two PLLs.

- 1. The platform PLL generates the platform clock from the externally supplied SYS\_CLK\_IN input. The frequency ratio between the platform and SYS\_CLK\_IN is selected using the platform PLL ratio configuration bits as described in Section 21.2, "System PLL Configuration."

- 2. The e300 core PLL generates the core clock as a slave to the platform clock. The frequency ratio between the e300 core clock and the platform clock is selected using the e300 PLL ratio configuration bits as described in Section 21.3, "Core PLL Configuration."

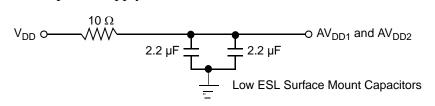

### 23.2 PLL Power Supply Filtering

Each of the PLLs listed above is provided with power through independent power supply pins ( $AV_{DD1}$  for core PLL and  $AV_{DD2}$  for the platform PLL). The  $AV_{DD}$  level should always be equivalent to  $V_{DD}$ , and preferably these voltages are derived directly from  $V_{DD}$  through a low pass filter scheme such as the following.

There are a number of ways to reliably provide power to the PLLs, but the recommended solution is to provide independent filter circuits as illustrated in Figure 54, one to each of the two  $AV_{DD}$  pins. By providing independent filters to each PLL the opportunity to cause noise injection from one PLL to the other is reduced.

This circuit is intended to filter noise in the PLLs' resonant frequency range from a 500 kHz to 10 MHz range. It should be built with surface mount capacitors with minimum effective series inductance (ESL). Consistent with the recommendations of Dr. Howard Johnson in *High Speed Digital Design: A Handbook of Black Magic* (Prentice Hall, 1993), multiple small capacitors of equal value are recommended over a single large value capacitor.

Each circuit should be placed as close as possible to the specific  $AV_{DD}$  pin being supplied to minimize noise coupled from nearby circuits. It should be possible to route directly from the capacitors to the  $AV_{DD}$  pin, which is on the periphery of package, without the inductance of vias.

This figure shows the PLL power supply filter circuits.

Figure 54. PLL Power Supply Filter Circuit

#### System Design Information

Figure 55. Driver Impedance Measurement

The value of this resistance and the strength of the driver's current source can be found by making two measurements. First, the output voltage is measured while driving logic 1 without an external differential termination resistor. The measured voltage is  $V_1 = R_{source} \times I_{source}$ . Second, the output voltage is measured while driving logic 1 with an external precision differential termination resistor of value  $R_{term}$ . The measured voltage is  $V_2 = (1/(1/R_1 + 1/R_2)) \times I_{source}$ . Solving for the output impedance gives  $R_{source} = R_{term} \times (V_1/V_2 - 1)$ . The drive current is then  $I_{source} = V_1/R_{source}$ .

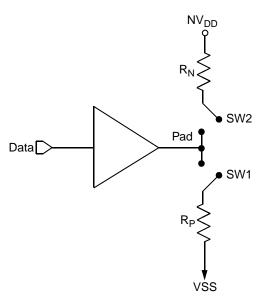

This table summarizes the signal impedance targets. The driver impedance are targeted at minimum  $V_{DD}$ , nominal NV<sub>DD</sub>, 105°C.

| Table 6 | 60. Im | pedance | Characteristics |

|---------|--------|---------|-----------------|

|---------|--------|---------|-----------------|

| Impedance      | Local Bus, Ethernet, DUART, Control,<br>Configuration, Power Management | DDR DRAM  | Symbol         | Unit |

|----------------|-------------------------------------------------------------------------|-----------|----------------|------|

| R <sub>N</sub> | 42 Target                                                               | 20 Target | Z <sub>0</sub> | Ω    |

| R <sub>P</sub> | 42 Target                                                               | 20 Target | Z <sub>0</sub> | Ω    |

**Note:** Nominal supply voltages. See Table 2,  $T_i = 105^{\circ}C$ .

### 23.6 Configuration Pin Muxing

The device provides the user with power-on configuration options which can be set through the use of external pull-up or pull-down resistors of 4.7 K $\Omega$  on certain output pins (see customer visible configuration pins). These pins are generally used as output only pins in normal operation.

While **PORESET** is asserted however, these pins are treated as inputs. The value presented on these pins while **PORESET** is asserted, is latched when **PORESET** deasserts, at which time the input receiver is disabled and the I/O circuit takes on its normal function. Careful board layout with stubless connections to these pull-up/pull-down resistors coupled with the large value of the pull-up/pull-down resistor should minimize the disruption of signal quality or speed for output pins thus configured.