Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                   |

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 1K x 8                                                                     |

| RAM Size                   | 4K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3865axa-019 |

# PSoC<sup>®</sup> 3: CY8C38 Automotive Family Datasheet

For more details on the peripherals see the "Example Peripherals" section on page 40 of this data sheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 40 of this data sheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features [5]:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±2 LSB

- DNL less than ±1 LSB

- SINAD better than 83 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors. The output of the ADC can optionally feed the programmable DFB through the DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user-defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths. In addition to the ADC, DACs, and DFB, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- □ Programmable gain amplifiers

- Mixers

- Other similar analog components

See the "Analog Subsystem" section on page 51 of this data sheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 67 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the VDDIO pins. Every GPIO has analog I/O, LCD drive<sup>[6]</sup>, CapSense<sup>[7]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow VOH to be set independently of Vddio when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 33 of this data sheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the clock base for the system, and has 1-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 62 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate clock frequencies up to 67 MHz from the IMO, external crystal, or external reference clock.

#### Notes

- 5. Refer Electrical Specifications on page 65 for the detailed ADC specification across entire voltage range and temperature.

- 6. This feature on select devices only. See Ordering Information on page 135 for details.

- GPIOs with opamp outputs are not recommended for use with CapSense.

**Table 4-3. Data Transfer Instructions**

|      | Mnemonic       | Description                                            | Bytes | Cycles |

|------|----------------|--------------------------------------------------------|-------|--------|

| MOV  | A,Rn           | Move register to accumulator                           | 1     | 1      |

| MOV  | A,Direct       | Move direct byte to accumulator                        | 2     | 2      |

| MOV  | A,@Ri          | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV  | A,#data        | Move immediate data to accumulator                     | 2     | 2      |

| MOV  | Rn,A           | Move accumulator to register                           | 1     | 1      |

| MOV  | Rn,Direct      | Move direct byte to register                           | 2     | 3      |

| MOV  | Rn, #data      | Move immediate data to register                        | 2     | 2      |

| MOV  | Direct, A      | Move accumulator to direct byte                        | 2     | 2      |

| MOV  | Direct, Rn     | Move register to direct byte                           | 2     | 2      |

| MOV  | Direct, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV  | Direct, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV  | Direct, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV  | @Ri, A         | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV  | @Ri, Direct    | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV  | @Ri, #data     | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV  | DPTR, #data16  | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVO | A, @A+DPTR     | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVO | C A, @A + PC   | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX | ( A,@Ri        | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX | A, @DPTR       | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX | ( @Ri, A       | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX | @DPTR, A       | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH | Direct         | Push direct byte onto stack                            | 2     | 3      |

| POP  | Direct         | Pop direct byte from stack                             | 2     | 2      |

| XCH  | A, Rn          | Exchange register with accumulator                     | 1     | 2      |

| XCH  | A, Direct      | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH  | A, @Ri         | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD | A, @Ri         | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

Table 4-4. Boolean Instructions

| Mnemonic   | Description             | Bytes | Cycles |

|------------|-------------------------|-------|--------|

| CLR C      | Clear carry             | 1     | 1      |

| CLR bit    | Clear direct bit        | 2     | 3      |

| SETB C     | Set carry               | 1     | 1      |

| SETB bit   | Set direct bit          | 2     | 3      |

| CPL C      | Complement carry        | 1     | 1      |

| CPL bit    | Complement direct bit   | 2     | 3      |

| ANL C, bit | AND direct bit to carry | 2     | 2      |

Document Number: 001-54683 Rev. \*K Page 13 of 146

# PSoC® 3: CY8C38 Automotive Family Datasheet

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data

phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase 'subchains' can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

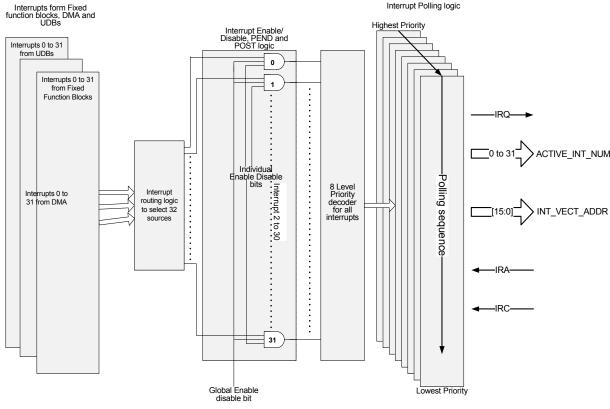

#### 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty-two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

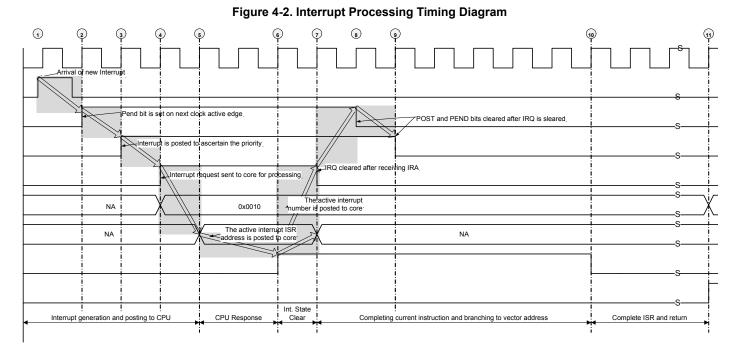

Figure 4-2 on page 18 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 19 shows the interrupt structure and priority polling.

Document Number: 001-54683 Rev. \*K Page 17 of 146

#### **Notes**

- 1: Interrupt triggered asynchronous to the clock

- 2: The PEND bit is set on next active clock edge to indicate the interrupt arrival

- 3: POST bit is set following the PEND bit

- 4: Interrupt request and the interrupt number sent to CPU core after evaluation priority (Takes 3 clocks)

- 5: ISR address is posted to CPU core for branching

- 6: CPU acknowledges the interrupt request

- 7: ISR address is read by CPU for branching

- 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core

- 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ISR location (Takes 7 cycles)

- 11: IRC is set to indicate the completion of ISR, Active int. status is restored with previous status

The total interrupt latency (ISR execution)

- = POST + PEND + IRQ + IRA + Completing current instruction and branching

- = 1+1+1+2+7 cycles

- = 12 cycles

Figure 4-3. Interrupt Structure

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are

direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

Document Number: 001-54683 Rev. \*K Page 19 of 146

## 5. Memory

#### 5.1 Static RAM

CY8C38 SRAM is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 24. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

### 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for ECC. If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

#### 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a bootloader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports,

protecting your application from external access (see the "Device Security" section on page 63). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

Table 5-1. Flash Protection

| Protection Setting | Allowed                                              | Not Allowed                              |

|--------------------|------------------------------------------------------|------------------------------------------|

| Unprotected        | External read and write<br>+ internal read and write | _                                        |

| Factory<br>Upgrade | External write + internal read and write             | External read                            |

| Field Upgrade      | Internal read and write                              | External read and write                  |

| Full Protection    | Internal read                                        | External read and write + internal write |

#### **Disclaimer**

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as 'unbreakable'. Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

### 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C38 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The CPU can not execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see Section 6.3.1) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. Also, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

## 6. System Integration

## 6.1 Clocking System

The clocking system generates, divides, and distributes clocks throughout the PSoC system. For the majority of systems, no external crystal is required. The IMO and PLL together can generate up to a 66 MHz clock, accurate to ±1 percent over voltage and temperature. Additional internal and external clock sources allow each design to optimize accuracy, power, and cost. Any of the clock sources can be used to generate other clock frequencies in the 16-bit clock dividers and UDBs for anything the user wants, for example a UART baud rate generator.

Clock generation and distribution is automatically configured through the PSoC Creator IDE graphical interface. This is based on the complete system's requirements. It greatly speeds the design process. PSoC Creator allows you to build clocking systems with minimal input. You can specify desired clock frequencies and accuracies, and the software locates or builds a clock that meets the required specifications. This is possible because of the programmability inherent in PSoC.

Key features of the clocking system include:

- Seven general purpose clock sources

- □ 3- to 62-MHz IMO, ±1% at 3 MHz

- 4- to 25-MHz external crystal oscillator (MHzECO)

- □ Clock doubler provides a doubled clock frequency output for the USB block, see USB Clock Domain on page 28.

- DSI signal from an external I/O pin or other logic

- ${\tt \ \, 24-to}$  67-MHz fractional PLL sourced from IMO, MHzECO, or DSI

- □ 1-kHz, 33-kHz, 100-kHz ILO for WDT and sleep timer □ 32.768-kHz external crystal oscillator (kHzECO) for RTC

- IMO has a USB mode that auto locks to the USB bus clock requiring no external crystal for USB (USB equipped parts only)

- Independently sourced clock in all clock dividers

- Eight 16-bit clock dividers for the digital system

- Four 16-bit clock dividers for the analog system

- Dedicated 16-bit divider for the bus clock

- Dedicated 4-bit divider for the CPU clock

- Automatic clock configuration in PSoC Creator

Table 6-1. Oscillator Summary

| Source  | Fmin   | Tolerance at Fmin                | Fmax    | Tolerance at Fmax   | Startup Time                         |

|---------|--------|----------------------------------|---------|---------------------|--------------------------------------|

| IMO     | 3 MHz  | ±1% over voltage and temperature | 62 MHz  | ±7%                 | 13 µs max                            |

| MHzECO  | 4 MHz  | Crystal dependent                | 25 MHz  | Crystal dependent   | 5 ms typ, max is crystal dependent   |

| DSI     | 0 MHz  | Input dependent                  | 66 MHz  | Input dependent     | Input dependent                      |

| PLL     | 24 MHz | Input dependent                  | 67 MHz  | Input dependent     | 250 μs max                           |

| Doubler | 48 MHz | Input dependent                  | 48 MHz  | Input dependent     | 1 µs max                             |

| ILO     | 1 kHz  | <b>-50%</b> , <b>+100%</b>       | 100 kHz | <i>–</i> 55%, +100% | 15 ms max in lowest power mode       |

| kHzECO  | 32 kHz | Crystal dependent                | 32 kHz  | Crystal dependent   | 500 ms typ, max is crystal dependent |

Document Number: 001-54683 Rev. \*K Page 26 of 146

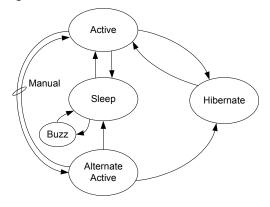

Figure 6-5. Power Mode Transitions

#### 6.2.1.1 Active Mode

Active mode is the primary operating mode of the device. When in active mode, the active configuration template bits control which available resources are enabled or disabled. When a resource is disabled, the digital clocks are gated, analog bias currents are disabled, and leakage currents are reduced as appropriate. User firmware can dynamically control subsystem power by setting and clearing bits in the active configuration template. The CPU can disable itself, in which case the CPU is automatically reenabled at the next wakeup event.

When a wakeup event occurs, the global mode is always returned to active, and the CPU is automatically enabled, regardless of its template settings. Active mode is the default global power mode upon boot.

#### 6.2.1.2 Alternate Active Mode

Alternate Active mode is very similar to Active mode. In alternate active mode, fewer subsystems are enabled, to reduce power consumption. One possible configuration is to turn off the CPU and flash, and run peripherals at full speed.

### 6.2.1.3 Sleep Mode

Sleep mode reduces power consumption when a resume time of 15  $\mu s$  is acceptable. The wake time is used to ensure that the regulator outputs are stable enough to directly enter active mode.

#### 6.2.1.4 Hibernate Mode

In hibernate mode nearly all of the internal functions are disabled. Internal voltages are reduced to the minimal level to keep vital systems alive. Configuration state is preserved in hibernate mode and SRAM memory is retained. GPIOs configured as digital outputs maintain their previous values and external GPIO pin interrupt settings are preserved. The device can only return from hibernate mode in response to an external I/O interrupt. The resume time from hibernate mode is less than  $100~\mu s$ .

To achieve an extremely low current, the hibernate regulator has limited capacity. This limits the frequency of any signal present on the input pins - no GPIO should toggle at a rate greater than 10 kHz while in hibernate mode. If pins must be toggled at a high rate while in a low power mode, use sleep mode instead.

#### 6.2.1.5 Wakeup Events

Wakeup events are configurable and can come from an interrupt or device reset. A wakeup event restores the system to active mode. Firmware enabled interrupt sources include internally generated interrupts, power supervisor, central timewheel, and I/O interrupts. Internal interrupt sources can come from a variety of peripherals, such as analog comparators and UDBs. The central timewheel provides periodic interrupts to allow the system to wake up, poll peripherals, or perform real-time functions. Reset event sources include the external reset I/O pin (XRES), WDT, and precision reset (PRES).

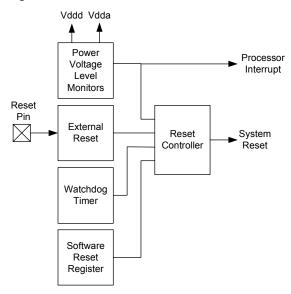

#### 6.3 Reset

CY8C38 has multiple internal and external reset sources available. The reset sources are:

- Power source monitoring The analog and digital power voltages, VDDA, VDDD, VCCA, and VCCD are monitored in several different modes during power up, active mode, and sleep mode (buzzing). If any of the voltages goes outside predetermined ranges then a reset is generated. The monitors are programmable to generate an interrupt to the processor under certain conditions before reaching the reset thresholds.

- External The device <u>can</u> be reset from <u>an</u> external source by pulling the reset pin (XRES) low. The XRES pin includes an internal pull-up to VDDIO1. VDDD, VDDA, and VDDIO1 must all have voltage applied before the part comes out of reset.

- Watchdog timer A watchdog timer monitors the execution of instructions by the processor. If the watchdog timer is not reset by firmware within a certain period of time, the watchdog timer generates a reset.

- Software The device can be reset under program control.

Figure 6-6. Resets

The term **device reset** indicates that the processor as well as analog and digital peripherals and registers are reset.

A reset status register shows some of the resets or power voltage monitoring interrupts. The program may examine this register to

# PSoC® 3: CY8C38 Automotive Family Datasheet

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- □ Separate I/O supplies and voltages for up to four groups of I/O

- □ Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- □ Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

- □ LCD segment drive on LCD equipped devices

- □ CapSense<sup>[13]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- □ Higher drive strength than GPIO

- □ Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- No analog input, CapSense, or LCD capability

- Over voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- □ Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- □ Digital output (CMOS) drive mode

- □ Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

Independent of the ALU operation, these functions are available:

- Shift left

- Shift right

- Nibble swap

- Bitwise OR mask

#### 7.2.2.3 Conditionals

Each datapath has two compares, with bit masking options. Compare operands include the two accumulators and the two data registers in a variety of configurations. Other conditions include zero detect, all ones detect, and overflow. These conditions are the primary datapath outputs, a selection of which can be driven out to the UDB routing matrix. Conditional computation can use the built in chaining to neighboring UDBs to operate on wider data widths without the need to use routing resources.

#### 7.2.2.4 Variable MSB

The most significant bit of an arithmetic and shift function can be programmatically specified. This supports variable width CRC and PRS functions, and in conjunction with ALU output masking, can implement arbitrary width timers, counters and shift blocks.

#### 7.2.2.5 Built in CRC/PRS

The datapath has built-in support for single cycle CRC computation and PRS generation of arbitrary width and arbitrary polynomial. CRC/PRS functions longer than 8 bits may be implemented in conjunction with PLD logic, or built in chaining may be use to extend the function into neighboring UDBs.

#### 7.2.2.6 Input/Output FIFOs

Each datapath contains two four-byte deep FIFOs, which can be independently configured as an input buffer (system bus writes to the FIFO, datapath internal reads the FIFO), or an output buffer (datapath internal writes to the FIFO, the system bus reads from the FIFO). The FIFOs generate status that are selectable as datapath outputs and can therefore be driven to the routing, to interact with sequencers, interrupts, or DMA.

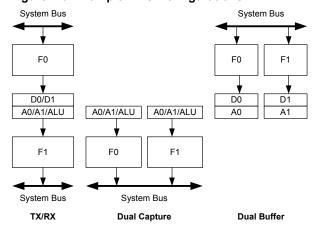

Figure 7-5. Example FIFO Configurations

#### 7.2.2.7 Chaining

The datapath can be configured to chain conditions and signals such as carries and shift data with neighboring datapaths to create higher precision arithmetic, shift, CRC/PRS functions.

#### 7.2.2.8 Time Multiplexing

In applications that are over sampled, or do not need high clock rates, the single ALU block in the datapath can be efficiently shared with two sets of registers and condition generators. Carry and shift out data from the ALU are registered and can be selected as inputs in subsequent cycles. This provides support for 16-bit functions in one (8-bit) datapath.

### 7.2.2.9 Datapath I/O

There are six inputs and six outputs that connect the datapath to the routing matrix. Inputs from the routing provide the configuration for the datapath operation to perform in each cycle, and the serial data inputs. Inputs can be routed from other UDB blocks, other device peripherals, device I/O pins, and so on. The outputs to the routing can be selected from the generated conditions, and the serial data outputs. Outputs can be routed to other UDB blocks, device peripherals, interrupt and DMA controller, I/O pins, and so on.

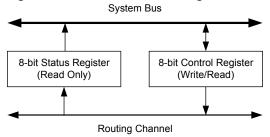

#### 7.2.3 Status and Control Module

The primary purpose of this circuitry is to coordinate CPU firmware interaction with internal UDB operation.

Figure 7-6. Status and Control Registers

The bits of the control register, which may be written to by the system bus, are used to drive into the routing matrix, and thus provide firmware with the opportunity to control the state of UDB processing. The status register is read-only and it allows internal UDB state to be read out onto the system bus directly from internal routing. This allows firmware to monitor the state of UDB processing. Each bit of these registers has programmable connections to the routing matrix and routing connections are made depending on the requirements of the application.

## 7.2.3.1 Usage Examples

As an example of control input, a bit in the control register can be allocated as a function enable bit. There are multiple ways to enable a function. In one method the control bit output would be routed to the clock control block in one or more UDBs and serve as a clock enable for the selected UDB blocks. A status example is a case where a PLD or datapath block generated a condition, such as a "compare true" condition that is captured and latched by the status register and then read (and cleared) by CPU firmware.

## 7.8 I<sup>2</sup>C

The I<sup>2</sup>C peripheral provides a synchronous two wire interface designed to interface the PSoC device with a two wire I<sup>2</sup>C serial communication bus. It is compatible [16] with I2C Standard-mode, Fast-mode, and Fast-mode Plus devices as defined in the NXP I2C-bus specification and user manual (UM10204). The I2C bus I/O may be implemented with GPIO or SIO in open-drain modes. Additional I<sup>2</sup>C interfaces can be instantiated using Universal Digital Blocks (UDBs) in PSoC Creator, as required.

To eliminate the need for excessive CPU intervention and overhead, I<sup>2</sup>C specific support is provided for status detection and generation of framing bits.  ${}^{12}\text{C}$  operates as a slave, a master, or multimaster (Slave and Master). In slave mode, the unit always listens for a start condition to begin sending or receiving data. Master mode supplies the ability to generate the Start and Stop conditions and initiate transactions. Multimaster mode provides clock synchronization and arbitration to allow multiple masters on the same bus. If Master mode is enabled and Slave mode is not enabled, the block does not generate interrupts on externally generated Start conditions. I<sup>2</sup>C interfaces through DSI routing and allows direct connections to any GPIO or SIO pins.

I<sup>2</sup>C provides hardware address detect of a 7-bit address without CPU intervention. Additionally the device can wake from low-power modes on a 7-bit hardware address match. If wakeup functionality is required, I<sup>2</sup>C pin connections are limited to the two special sets of SIO pins.

I<sup>2</sup>C features include:

- Slave and master, transmitter, and receiver operation

- Byte processing for low CPU overhead

- Interrupt or polling CPU interface

- Support for bus speeds up to 1 Mbps

- 7 or 10-bit addressing (10-bit addressing requires firmware

- SMBus operation (through firmware support SMBus supported in hardware in UDBs)

- 7-bit hardware address compare

- Wake from low-power modes on address match

- Glitch filtering (active and alternate-active modes only)

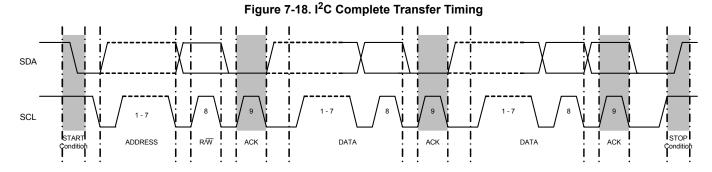

Data transfers follow the format shown in Figure 7-18. After the START condition (S), a slave address is sent. This address is 7 bits long followed by an eighth bit which is a data direction bit (R/W) - a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

### Notes

Document Number: 001-54683 Rev. \*K

<sup>16.</sup> The I<sup>2</sup>C peripheral is non-compliant with the NXP I<sup>2</sup>C specification in the following areas: analog glitch filter, I/O V<sub>OL</sub>/I<sub>OL</sub>, I/O hysteresis. The I<sup>2</sup>C Block has a digital glitch filter (not available in sleep mode). The Fast-mode minimum fall-time specification can be met by setting the I/Os to slow speed mode. See the I/O Electrical Specifications in "Inputs and Outputs" section on page 74 for details.

<sup>17.</sup> Fixed-block I<sup>2</sup>C does not support undefined bus conditions, nor does it support Repeated Start in Slave mode. These conditions should be avoided, or the UDB-based I<sup>2</sup>C component should be used instead.

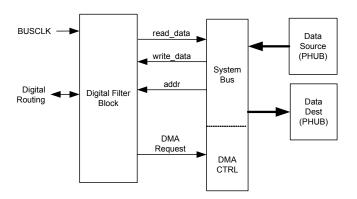

### 7.9 Digital Filter Block

Some devices in the CY8C38 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one bus clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The heart of the DFB is a datapath (DP), which is the numerical calculation unit of the DFB. The DP is a 24-bit fixed-point numerical processor containing a 48-bit multiply and accumulate function (MAC), a multi-function ALU, sample and coefficient data RAMs as well as data routing, shifting, holding and rounding functions.

In the MAC, two 24-bit values can be multiplied and the result added to the 48-bit accumulator in each bus clock cycle. The MAC is the only portion of the DP that is wider than 24 bits. All results from the MAC are passed on to the ALU as 24-bit values representing the high-order 24 bits in the accumulator shifted by one (bits 46:23). The MAC assumes an implied binary point after the most significant bit.

The DP also contains an optimized ALU that supports add, subtract, comparison, threshold, absolute value, squelch, saturation, and other functions. The DP unit is controlled by seven control fields totaling 18 bits coming from the DFB Controller. For more information see the TRM.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

Figure 7-19. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

## 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

Document Number: 001-54683 Rev. \*K Page 51 of 146

## 11.3.2 Analog Core Regulator

## Table 11-5. Analog Core Regulator DC Specifications

| Parameter | Description                | Conditions                                      | Min | Тур  | Max | Units |

|-----------|----------------------------|-------------------------------------------------|-----|------|-----|-------|

| Vdda      | Input voltage              |                                                 | 1.8 | -    | 5.5 | V     |

| Vcca      | Output voltage             |                                                 | -   | 1.80 | -   | V     |

|           | Regulator output capacitor | ±10%, X5R ceramic or better (X7R for Ta > 85°C) | -   | 1    | -   | μF    |

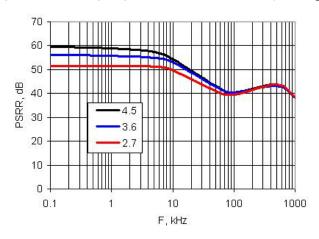

Figure 11-5. Analog Regulator PSRR vs Frequency and  $V_{\rm DD}$

Document Number: 001-54683 Rev. \*K Page 73 of 146

Table 11-7. GPIO AC Specifications

| Parameter | Description                                                                 | Conditions                                                                                            | Min | Тур | Max | Units |

|-----------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| TriseF    | Rise time in Fast Strong Mode <sup>[30]</sup>                               | 3 V Vddio Cload = 25 pF                                                                               | _   | _   | 12  | ns    |

| TfallF    | Fall time in Fast Strong Mode <sup>[30]</sup>                               | 3 V Vddio Cload = 25 pF                                                                               | _   | _   | 12  | ns    |

| TriseS    | Rise time in Slow Strong Mode <sup>[30]</sup>                               | 3 V Vddio Cload = 25 pF                                                                               | _   | -   | 60  | ns    |

| TfallS    | Fall time in Slow Strong Mode <sup>[30]</sup>                               | 3 V Vddio Cload = 25 pF                                                                               | -   | _   | 60  | ns    |

|           | GPIO output operating frequency                                             |                                                                                                       |     |     |     |       |

|           | $3 \text{ V} \leq \text{Vddio} \leq 5.5 \text{ V}$ , fast strong drive mode | 90/10% Vddio into 25 pF, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                              | -   | -   | 33  | MHz   |

|           |                                                                             | 90/10% Vddio into 25 pF, -40°C ≤<br>Ta ≤ 125°C and Tj ≤ 150°C                                         | -   | -   | 24  | MHz   |

|           | 1.71 V ≤ Vddio < 3 V, fast strong drive mode                                | 90/10% Vddio into 25 pF, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                              | -   | -   | 20  | MHz   |

| Fgpioout  |                                                                             | 90/10% Vddio into 25 pF, -40°C ≤<br>Ta ≤ 125°C and Tj ≤ 150°C                                         | -   | -   | 16  | MHz   |

|           | $3 \text{ V} \leq \text{Vddio} \leq 5.5 \text{ V}$ , slow strong drive mode | 90/10% Vddio into 25 pF, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                              | -   | -   | 7   | MHz   |

|           |                                                                             | 90/10% Vddio into 25 pF, -40°C ≤<br>Ta ≤ 125°C and Tj ≤ 150°C                                         | -   | -   | 7   | MHz   |

|           | 1.71 V ≤ Vddio < 3 V, slow strong drive mode                                | 90/10% Vddio into 25 pF, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                              | -   | -   | 3.5 | MHz   |

|           |                                                                             | 90/10% Vddio into 25 pF, -40°C ≤<br>Ta ≤ 125°C and Tj ≤ 150°C                                         | -   | -   | 3.5 | MHz   |

|           | GPIO input operating frequency                                              |                                                                                                       |     | -   |     | 1.    |

| Fgpioin   | 1.71 V ≤ Vddio ≤ 5.5 V                                                      | 90/10% better than 60/40 duty cycle, $-40^{\circ}C \le Ta \le 85^{\circ}C$ and $Tj \le 100^{\circ}C$  | -   | -   | 66  | MHz   |

|           |                                                                             | 90/10% better than 60/40 duty cycle, $-40^{\circ}C \le Ta \le 125^{\circ}C$ and $Tj \le 150^{\circ}C$ | -   | -   | 50  | MHz   |

Document Number: 001-54683 Rev. \*K Page 76 of 146

## 11.5 Analog Peripherals

Specifications are valid for -40  $^{\circ}$  C  $\leq$  Ta  $\leq$  125  $^{\circ}$  C and Tj  $\leq$  150  $^{\circ}$  C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.5.1 Opamp

Table 11-15. Opamp DC Specifications

| Parameter       | Description                                 | Conditions                                                                                                                  | Min       | Тур  | Max          | Units   |

|-----------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------|------|--------------|---------|

| Vioff           | Input offset voltage                        | $-40^{\circ}\text{C} \le \text{Ta} \le 85^{\circ}\text{C} \text{ and Tj} \le 100^{\circ}\text{C}$                           | -         | -    | ±2.5         | mV      |

| VIOII           | Input onset voltage                         | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C                                                                                           | -         | -    | ±5.0         | mV      |

| TCVos           | Input offset voltage drift with temperature | Power mode = high                                                                                                           | _         | _    | ±30          | μV / °C |

| Ge1             | Gain error, unity gain buffer mode          | Rload = 1 kΩ                                                                                                                | -         | -    | <u>+</u> 0.1 | %       |

| Vi              | Input voltage range                         |                                                                                                                             | Vssa      | -    | Vdda         | mV      |

| Vo              | Output voltage range                        | Output load = 1 mA                                                                                                          | Vssa + 50 | -    | Vdda - 50    | mV      |

| lout            | Output current                              | Output voltage is between Vssa +500 mV and Vdda -500 mV, and Vdda > 2.7 V, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 25        | -    | -            | mA      |

|                 |                                             | Output voltage is between Vssa +500 mV and Vdda -500 mV, and Vdda > 2.7 V, -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 20        | -    | -            | mA      |

| lout            | Output current                              | Output voltage is between Vssa<br>+500 mV and Vdda -500 mV, and<br>Vdda > 1.7 V and Vdda < 2.7 V                            | 16        | -    | -            | mA      |

| I <sub>DD</sub> | Quiescent current                           | Power mode = min                                                                                                            | ı         | 250  | 400          | μA      |

|                 |                                             | Power mode = low                                                                                                            | _         | 250  | 400          | μA      |

|                 |                                             | Power mode = med                                                                                                            | _         | 330  | 950          | μA      |

|                 |                                             | Power mode = high                                                                                                           | _         | 1000 | 2500         | μA      |

| CMRR            | Common mode rejection ratio <sup>[30]</sup> |                                                                                                                             | 80        | _    | _            | dB      |

| PSRR            | Power supply rejection ratio                | Vdda ≥ 2.7 V                                                                                                                | 85        | _    | _            | dB      |

|                 |                                             | Vdda < 2.7 V                                                                                                                | 70        | _    | _            | dB      |

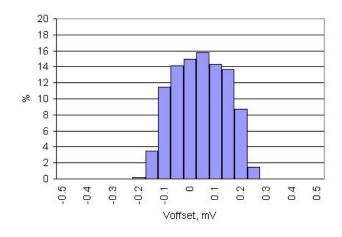

Figure 11-16. Opamp Voffset Histogram, 3388 samples/847 parts, 25 °C, Vdda = 5 V

### 11.6.2 Counter

## Table 11-43. Counter DC Specifications

| Parameter | Description               | Conditions                                      | Min | Тур | Max | Units |

|-----------|---------------------------|-------------------------------------------------|-----|-----|-----|-------|

|           | Block current consumption | 16-bit counter, at listed input clock frequency | _   | _   | _   | μΑ    |

|           | 3 MHz                     |                                                 | -   | 15  | _   | μA    |

|           | 12 MHz                    |                                                 | -   | 60  | -   | μΑ    |

|           | 50 MHz                    |                                                 | -   | 260 | _   | μA    |

|           | 67 MHz                    |                                                 | _   | 350 | _   | μΑ    |

## Table 11-44. Counter AC Specifications

| Parameter | Description                   | Conditions                        | Min | Тур | Max                | Units |

|-----------|-------------------------------|-----------------------------------|-----|-----|--------------------|-------|

|           | Operating frequency           | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | DC  | -   | 67 <sup>[48]</sup> | MHz   |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | DC  | -   | 50                 | MHz   |

|           | Capture pulse                 | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 21  | -   | -                  | ns    |

|           | Resolution                    | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 21  | -   | -                  | ns    |

|           | Pulse width                   | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 21  | -   | -                  | ns    |

|           | Pulse width (external)        | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 30  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 42  | -   | -                  | ns    |

|           | Enable pulse width            | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 21  | -   | -                  | ns    |

|           | Enable pulse width (external) | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 30  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 42  | -   | -                  | ns    |

|           | Reset pulse width             | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 21  | -   | -                  | ns    |

|           | Reset pulse width (external)  | -40°C ≤ Ta ≤ 85°C and Tj ≤ 100°C  | 30  | -   | -                  | ns    |

|           |                               | -40°C ≤ Ta ≤ 125°C and Tj ≤ 150°C | 42  | -   | -                  | ns    |

48. Applicable at -40°C to 85°C; 50 MHz at -40°C to 125°C.

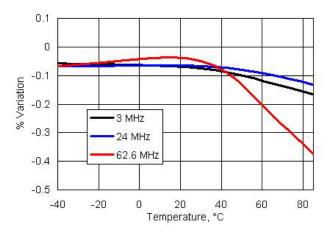

Figure 11-68. IMO Frequency Variation vs. Temperature

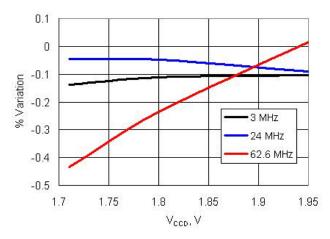

Figure 11-69. IMO Frequency Variation vs.  $V_{\rm CC}$

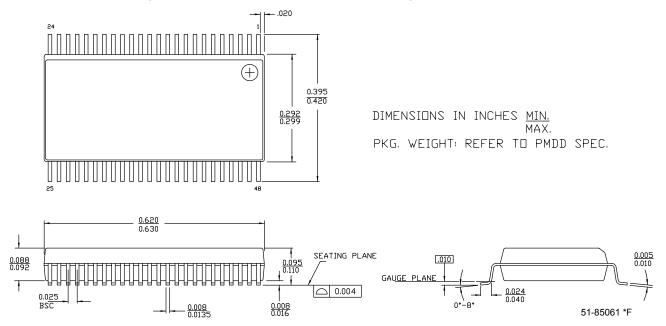

# 13. Packaging

Table 13-1. Package Characteristics

| Parameter       | Description                            | Conditions | Min | Тур   | Max | Units |

|-----------------|----------------------------------------|------------|-----|-------|-----|-------|

| T <sub>A</sub>  | Operating ambient temperature          |            | -40 | 25.00 | 125 | °C    |

| T <sub>J</sub>  | Operating junction temperature         |            | -40 | -     | 150 | °C    |

| $T_{JA}$        | Package θ <sub>JA</sub> (48-pin SSOP)  |            | _   | 49    | -   | °C/W  |

| T <sub>JA</sub> | Package θ <sub>JA</sub> (100-pin TQFP) |            | _   | 34    | _   | °C/W  |

| T <sub>JC</sub> | Package θ <sub>JC</sub> (48-pin SSOP)  |            | _   | 24    | _   | °C/W  |

| T <sub>JC</sub> | Package θ <sub>JC</sub> (100-pin TQFP) |            | _   | 10    | _   | °C/W  |

Table 13-2. Solder Reflow Peak Temperature

| Package      | Maximum Peak<br>Temperature | Maximum Time at Peak<br>Temperature |

|--------------|-----------------------------|-------------------------------------|

| 48-pin SSOP  | 260 °C                      | 30 seconds                          |

| 100-pin TQFP | 260 °C                      | 30 seconds                          |

Table 13-3. Package Moisture Sensitivity Level (MSL), IPC/JEDEC J-STD-2

| Package      | MSL   |

|--------------|-------|

| 48-pin SSOP  | MSL 3 |

| 100-pin TQFP | MSL 3 |

Figure 13-1. 48-pin SSOP (300 Mils) O483 Package Outline, 51-85061

# 17. Revision History

| Description Title: PSoC <sup>®</sup> 3: CY8C38 Automotive Family Datasheet, Programmable System-on-Chip (PSoC <sup>®</sup> ) Document Number: 001-54683 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev.                                                                                                                                                    | ECN     | Submission<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| **                                                                                                                                                      | 2742918 | 07/23/09           | VIVG /<br>PYRS     | New data sheet for PSoC 3 Automotive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| *A                                                                                                                                                      | 2750090 | 08/10/09           | SHEA               | Minor ECN to correct title on first page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *B                                                                                                                                                      | 2800070 | 01/05/10           | SECA               | Added Tio_init parameter and updated Tstartup values. Updated PGA and UGB AC Specs table and changed gain error condition in PGA DC table. Added PCB Layout and PCB Schematic figures. Updated Figure 1-1 and Figure 8-1. Removed 12-Bit Del-Sig ADC table.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *C                                                                                                                                                      | 2921624 | 04/26/2010         | MKEA               | Updated Active Mode Idd values in Table 11-2 Updated Boost AC and DC specifications Updated solder paste reflow temperature (Table 11-3) Moved Filo spec from ILO DC to ILO AC table Updated Figure 7-14, Interrupt and DMA processing Added Bytes column in Tables 4-1 and 4-5 Updated Figure 6-3, Power mode transitions Updated JTAG and SWD specifications Updated Interrupt Vector table Updated Sales links Updated PCB Schematic Updated Vbias spec Added UDBs subsection under 11.6 Digital Peripherals Updated lout parameter in LCD Direct Drive DC Specs table Added Load regulation and Line regulation parameters to Inductive Boost Regulator DC Specifications table Updated Icc parameter in LCD Direct Drive DC Specs table Updated Icc parameter in LCD Direct Drive DC Specs table Updated Icc parameter in AC Specifications table Updated Tstartup parameter in AC Specifications table Updated LVD in Tables 6-2 and 6-3 In page 1, updated internal oscillator range under Precision programmable clocking to start from 3 MHz Updated Pin Descriptions section and modified Figures 6-6, 6-8, 6-9 Added PLL intermediate frequency row with footnote in PLL AC Specs table Added bullets on CapSense in page 1; added CapSense column in Section Updated Figure 2-6 (PCB Layout) Updated Tstartup values in Table 11-3 Updated IMO frequency Updated Section 5.2 and Table 11-2 to correct suggestion of execution from Flash Updated Vref specs in Table 11-21. Updated UpAC uncompensated gain error in Table 11-25. Updated Tresp, high and low power modes, in Table 11-24. Updated SNR condition in Table 6-3 and Tsleep in Table 11-3. Updated SNR condition in Table 6-3 and Tsleep in Table 11-3. Updated SNR condition in Table 6-3 and Tsleep in Table 11-3. |

| *D                                                                                                                                                      | 3490311 | 01/11/2012         | GIR                | Updated Figure 6-7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |