#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                   |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB            |

| Peripherals                | CapSense, DMA, LCD, POR, PWM, WDT                                          |

| Number of I/O              | 62                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 100-LQFP                                                                   |

| Supplier Device Package    | 100-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866axa-040 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- □ Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

LCD segment drive on LCD equipped devices

- □ CapSense<sup>[13]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- □ No analog input, CapSense, or LCD capability

- Dver voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

<sup>13.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

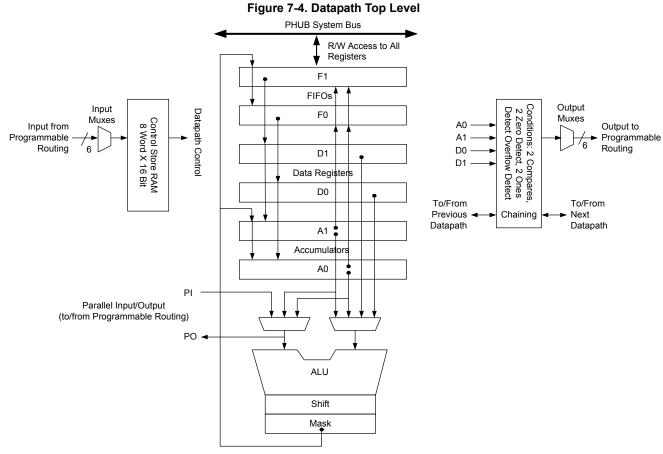

#### 7.2.2 Datapath Module

The datapath contains an 8-bit single cycle ALU, with associated compare and condition generation logic. This datapath block is optimized to implement embedded functions, such as timers, counters, integrators, PWMs, PRS, CRC, shifters and dead band generators and many others.

### 7.2.2.1 Working Registers

The datapath contains six primary working registers, which are accessed by CPU firmware or DMA during normal operation.

| Table 7-1. | Working | Datapath | Registers |

|------------|---------|----------|-----------|

|------------|---------|----------|-----------|

| Name      | Function       | Description                                                                                                                                                                                                                 |

|-----------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 and A1 | Accumulators   | These are sources and sinks for the ALU and also sources for the compares.                                                                                                                                                  |

| D0 and D1 | Data Registers | These are sources for the ALU and sources for the compares.                                                                                                                                                                 |

| F0 and F1 | FIFOs          | These are the primary interface<br>to the system bus. They can be a<br>data source for the data registers<br>and accumulators or they can<br>capture data from the<br>accumulators or ALU. Each FIFO<br>is four bytes deep. |

### 7.2.2.2 Dynamic Datapath Configuration RAM

Dynamic configuration is the ability to change the datapath function and internal configuration on a cycle-by-cycle basis, under sequencer control. This is implemented using the 8-word × 16-bit configuration RAM, which stores eight unique 16-bit wide configurations. The address input to this RAM controls the sequence, and can be routed from any block connected to the UDB routing matrix, most typically PLD logic, I/O pins, or from the outputs of this or other datapath blocks.

### ALU

The ALU performs eight general purpose functions. They are: Increment

- Decrement

- Add

- Subtract

- Logical AND

- Logical OR

- Logical XOR

- Pass, used to pass a value through the ALU to the shift register, mask, or another UDB register.

### 7.2.3.2 Clock Generation

Each subcomponent block of a UDB including the two PLDs, the datapath, and Status and Control, has a clock selection and control block. This promotes a fine granularity with respect to allocating clocking resources to UDB component blocks and allows unused UDB resources to be used by other functions for maximum system efficiency.

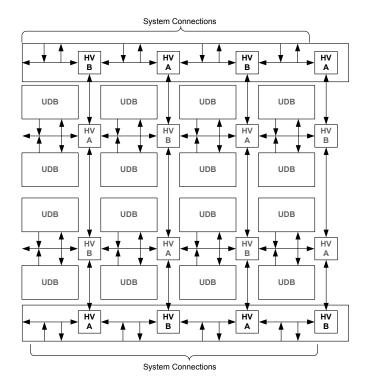

### 7.3 UDB Array Description

Figure 7-7 shows an example of a 16 UDB array. In addition to the array core, there are a DSI routing interfaces at the top and bottom of the array. Other interfaces that are not explicitly shown include the system interfaces for bus and clock distribution. The UDB array includes multiple horizontal and vertical routing channels each comprised of 96 wires. The wire connections to UDBs, at horizontal/vertical intersection and at the DSI interface are highly permutable providing efficient automatic routing in PSoC Creator. Additionally the routing allows wire by wire segmentation along the vertical and horizontal routing to further increase routing flexibility and capability.

#### Figure 7-7. Digital System Interface Structure

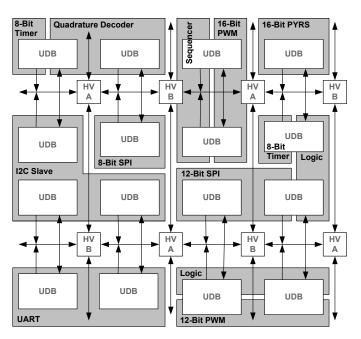

#### 7.3.1 UDB Array Programmable Resources

Figure 7-8 shows an example of how functions are mapped into a bank of 16 UDBs. The primary programmable resources of the UDB are two PLDs, one datapath and one status/control register. These resources are allocated independently, because they have independently selectable clocks, and therefore unused blocks are allocated to other unrelated functions. An example of this is the 8-bit timer in the upper left corner of the array. This function only requires one datapath in the UDB, and therefore the PLD resources may be allocated to another function. A function such as a Quadrature Decoder may require more PLD logic than one UDB can supply and in this case can utilize the unused PLD blocks in the 8-bit Timer UDB. Programmable resources in the UDB array are generally homogeneous so functions can be mapped to arbitrary boundaries in the array.

#### Figure 7-8. Function Mapping Example in a Bank of UDBs

# 7.4 DSI Routing Interface Description

The DSI routing interface is a continuation of the horizontal and vertical routing channels at the top and bottom of the UDB array core. It provides general purpose programmable routing between device peripherals, including UDBs, I/Os, analog peripherals, interrupts, DMA and fixed function peripherals.

Figure 7-9 illustrates the concept of the digital system interconnect, which connects the UDB array routing matrix with other device peripherals. Any digital core or fixed function peripheral that needs programmable routing is connected to this interface.

Signals in this category include:

- Interrupt requests from all digital peripherals in the system.

- DMA requests from all digital peripherals in the system.

- Digital peripheral data signals that need flexible routing to I/Os.

- Digital peripheral data signals that need connections to UDBs.

- Connections to the interrupt and DMA controllers.

- Connection to I/O pins.

- Connection to analog system digital signals.

#### DMA IO Port Timer Global Interrupt CAN 120 Counters Controller Controller Pins Clocks Digital System Routing I/F **UDB ARRAY** Digital System Routing I/F Global IO Port SC/CT EMIF Del-Sig DACs Comparators Clocks Pins Blocks

#### Figure 7-9. Digital System Interconnect

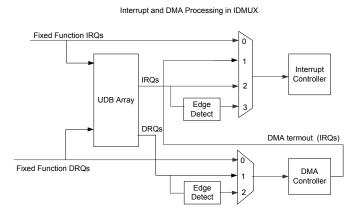

Interrupt and DMA routing is very flexible in the CY8C38 programmable architecture. In addition to the numerous fixed function peripherals that can generate interrupt requests, any data signal in the UDB array routing can also be used to generate a request. A single peripheral may generate multiple independent interrupt requests simplifying system and firmware design. Figure 7-10 shows the structure of the IDMUX (Interrupt/DMA Multiplexer).

#### Figure 7-10. Interrupt and DMA Processing in the IDMUX

#### 7.4.1 I/O Port Routing

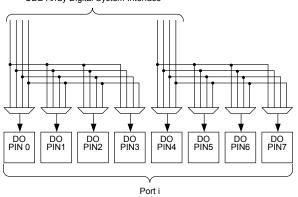

There are a total of 20 DSI routes to a typical 8-bit I/O port, 16 for data and four for drive strength control.

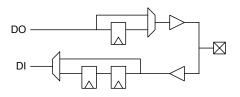

When an I/O pin is connected to the routing, there are two primary connections available, an input and an output. In conjunction with drive strength control, this can implement a bidirectional I/O pin. A data output signal has the option to be single synchronized (pipelined) and a data input signal has the option to be double synchronized. The synchronization clock is the master clock (see Figure 6-1). Normally all inputs from pins are synchronized as this is required if the CPU interacts with the signal or any signal derived from it. Asynchronous inputs have rare uses. An example of this is a feed through of combinational PLD logic from input pins to output pins.

### Figure 7-11. I/O Pin Synchronization Routing

Figure 7-12. I/O Pin Output Connectivity

8 IO Data Output Connections from the UDB Array Digital System Interface

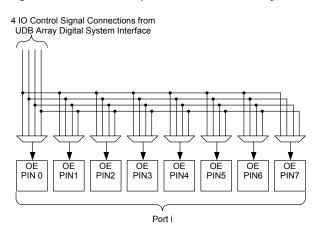

There are four more DSI connections to a given I/O port to implement dynamic output enable control of pins. This connectivity gives a range of options, from fully ganged 8-bits controlled by one signal, to up to four individually controlled pins. The output enable signal is useful for creating tri-state bidirectional pins and buses.

#### Figure 7-13. I/O Pin Output Enable Connectivity

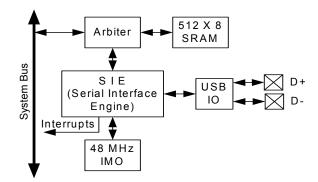

### 7.6 USB

PSoC includes a dedicated Full-Speed (12 Mbps) USB 2.0 transceiver supporting all four USB transfer types: control, interrupt, bulk, and isochronous. PSoC Creator provides full configuration support. USB interfaces to hosts through two dedicated USBIO pins, which are detailed in the "I/O System and Routing" section on page 33.

USB includes the following features:

- Eight unidirectional data endpoints

- One bidirectional control endpoint 0 (EP0)

- Shared 512-byte buffer for the eight data endpoints

- Dedicated 8-byte buffer for EP0

- Three memory modes

- Manual memory management with no DMA access

- Manual memory management with manual DMA access

- Automatic memory management with automatic DMA access

- Internal 3.3-V regulator for transceiver

- Internal 48-MHz main oscillator mode that auto locks to USB bus clock, requiring no external crystal for USB (USB equipped parts only)

- Interrupts on bus and each endpoint event, with device wakeup

- USB reset, suspend, and resume operations

- Bus-powered and self-powered modes

#### Figure 7-16. USB

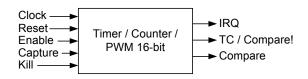

#### 7.7 Timers, Counters, and PWMs

The timer/counter/PWM peripheral is a 16-bit dedicated peripheral providing three of the most common embedded peripheral features. As almost all embedded systems use some combination of timers, counters, and PWMs. Four of them have been included on this PSoC device family. Additional and more advanced functionality timers, counters, and PWMs can also be instantiated in UDBs as required. PSoC Creator allows you to choose the timer, counter, and PWM features that they require. The tool set utilizes the most optimal resources available.

The timer/counter/PWM peripheral can select from multiple clock sources, with input and output signals connected through the DSI routing. DSI routing allows input and output connections to any device pin and any internal digital signal accessible through the DSI. Each of the four instances has a compare output, terminal count output (optional complementary compare output), and programmable interrupt request line. The Timer/Counter/PWMs are configurable as free running, one shot, or Enable input controlled. The peripheral has timer reset and capture inputs, and a kill input for control of the comparator outputs. The peripheral supports full 16-bit capture.

Timer/Counter/PWM features include:

- 16-bit Timer/Counter/PWM (down count only)

- Selectable clock source

- PWM comparator (configurable for LT, LTE, EQ, GTE, GT)

- Period reload on start, reset, and terminal count

- Interrupt on terminal count, compare true, or capture

- Dynamic counter reads

- Timer capture mode

- Count while enable signal is asserted mode

- Free run mode

- One Shot mode (stop at end of period)

- Complementary PWM outputs with deadband

- PWM output kill

#### Figure 7-17. Timer/Counter/PWM

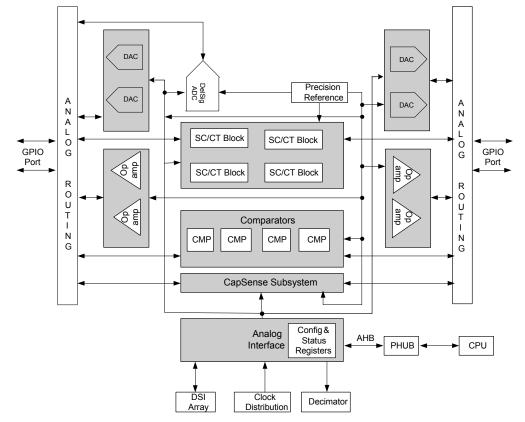

Figure 8-1. Analog Subsystem Block Diagram

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions (PGA, transimpedance amplifier, voltage DAC, current DAC, and so on). The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

### 8.1 Analog Routing

The CY8C38 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

#### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

#### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C38 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C38, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2 on page 53.

### Table 11-2. DC Specifications (continued)

| Parameter                                                                                                                                                                         | Description                                                                                                                                                                                                      | Conditions                                             |            | Min | Тур  | Мах | Units |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------|-----|------|-----|-------|

|                                                                                                                                                                                   | Sleep Mode <sup>[26]</sup>                                                                                                                                                                                       |                                                        |            |     |      |     |       |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  | V <sub>DD</sub> = V <sub>DDIO</sub> = 4.5 V–5.5 V      | T = -40 °C | -   | 1.1  | 2.3 | μA    |

|                                                                                                                                                                                   | CPU OFF                                                                                                                                                                                                          |                                                        | T = 25 °C  | -   | 1.1  | 2.2 | μA    |

|                                                                                                                                                                                   | RTC = ON (= ECO32K ON, in low<br>power mode)<br>Sleep timer = ON (= ILO ON at<br>1 kHz) $^{[27]}$<br>WDT = OFF<br>I <sup>2</sup> C Wake = OFF<br>Comparator = OFF<br>POR = ON<br>SIO Pins in single ended input, |                                                        | T = 85 °C  | -   | 15   | 30  | μA    |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  |                                                        | T = 125 °C | -   | 20.3 | 30  | μA    |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  | V <sub>DD</sub> = V <sub>DDIO</sub> = 2.7 V–3.6 V      | T=-40 °C   | -   | 1    | 2.2 | μA    |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  |                                                        | T = 25 °C  | -   | 1    | 2.1 | μA    |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  |                                                        | T = 85 °C  | -   | 12   | 28  | μA    |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  |                                                        | T = 125 °C | -   | 18.5 | 28  | μA    |

|                                                                                                                                                                                   | unregulated output mode                                                                                                                                                                                          | V <sub>CC</sub> = V <sub>DDIO</sub> =<br>1.71 V–1.95 V | T = 25 °C  | _   | 2.2  | 4.2 | μA    |

|                                                                                                                                                                                   |                                                                                                                                                                                                                  | 1.71 V–1.95 V                                          | T = 125 °C | _   | 16.2 | 28  | μA    |

|                                                                                                                                                                                   | Comparator = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>$I^2C$ Wake = OFF<br>POR = ON<br>SIO Pins in single ended input,<br>unregulated output mode                                       | V <sub>DD</sub> = V <sub>DDIO</sub> = 2.7 V–3.6 V      |            | _   | 2.2  | 2.7 | μA    |

| I <sup>2</sup> C Wake = ON<br>CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>Comparator = OFF<br>POR = ON<br>SIO Pins in single ended inp<br>unregulated output mode | CPU = OFF<br>RTC = OFF<br>Sleep timer = OFF<br>WDT = OFF<br>Comparator = OFF<br>POR = ON<br>SIO Pins in single ended input,                                                                                      | V <sub>DD</sub> = V <sub>DDIO</sub> = 2.7 V–3.6 V      | T = 25 °C  | _   | 2.2  | 2.8 | μA    |

Notes

26. If Vccd and Vcca are externally regulated, the voltage difference between Vccd and Vcca must be less than 50 mV. 27. Sleep timer generates periodic interrupts to wake up the CPU. This specification applies only to those times that the CPU is off.

### Table 11-2. DC Specifications (continued)

| Parameter         | Description                                                                                                                                                                 | Conditions                                             |            | Min | Тур | Max | Units |  |  |

|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------|-----|-----|-----|-------|--|--|

|                   | Hibernate Mode <sup>[28]</sup>                                                                                                                                              |                                                        |            |     |     |     |       |  |  |

|                   | Hibernate mode current<br>All regulators and oscillators off.<br>SRAM retention<br>GPIO interrupts are active<br>SIO Pins in single ended input,<br>unregulated output mode | V <sub>DD</sub> = V <sub>DDIO</sub> = 4.5 V–5.5 V      | T=-40 °C   | -   | 0.2 | 1.6 | μA    |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 25 °C  | -   | 0.5 | 1.5 | μA    |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 85 °C  | -   | 4.1 | 5.3 | μA    |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 125 °C | -   | 6.3 | 10  | μA    |  |  |

|                   |                                                                                                                                                                             | V <sub>DD</sub> = V <sub>DDIO</sub> = 2.7 V–3.6 V      | T = -40 °C | -   | 0.2 | 1.5 | μA    |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 25 °C  | -   | 0.2 | 1.5 | μA    |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 85 °C  | -   | 3.2 | 4.2 | μA    |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 125 °C | -   | 6   | 10  | μA    |  |  |

|                   |                                                                                                                                                                             | V <sub>CC</sub> = V <sub>DDIO</sub> =<br>1.71 V–1.95 V | T = -40 °C | _   | 0.2 | 1.5 | μA    |  |  |

|                   | 1.71 V–1.95 V                                                                                                                                                               | T = 25 °C                                              | -          | 0.2 | 1.5 | μA  |       |  |  |

|                   |                                                                                                                                                                             | T = 85 °C                                              | -          | 2.8 | 4.3 | μA  |       |  |  |

|                   |                                                                                                                                                                             |                                                        | T = 125 °C | -   | 5.4 | 10  | μA    |  |  |

| I <sub>DDAR</sub> | Analog current consumption while device is reset <sup>[29]</sup>                                                                                                            | V <sub>DDA</sub> <u>≤</u> 3.6 V                        |            | -   | 0.3 | 1   | mA    |  |  |

|                   | while device is reset <sup>[29]</sup>                                                                                                                                       | V <sub>DDA</sub> > 3.6 V                               |            | -   | 1.4 | 3.3 | mA    |  |  |

| IDDDR             | Digital current consumption while device is reset <sup>[29]</sup>                                                                                                           | V <sub>DDD</sub> <u>&lt;</u> 3.6 V                     |            | -   | 1.1 | 6   | mA    |  |  |

|                   | device is reset <sup>[29]</sup>                                                                                                                                             | V <sub>DDD</sub> > 3.6 V                               |            | -   | 0.7 | 6   | mA    |  |  |

| I <sub>IB</sub>   | Input bias current <sup>[29]</sup>                                                                                                                                          |                                                        | T = 25 °C  | -   | 10  | -   | pА    |  |  |

Notes

28. If Vccd and Vcca are externally regulated, the voltage difference between Vccd and Vcca must be less than 50 mV.

29. Based on device characterization (not production tested). USBIO pins tied to ground (V<sub>SSD</sub>).

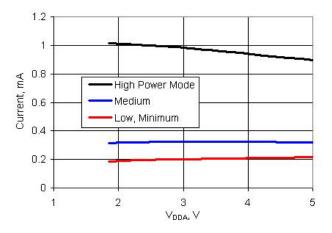

# Figure 11-20. Opamp Operating Current vs Vdda and Power Mode

## Table 11-16. Opamp AC Specifications

| Parameter      | Description            | Conditions                                   | Min | Тур | Max | Units         |

|----------------|------------------------|----------------------------------------------|-----|-----|-----|---------------|

| GBW            | Gain-bandwidth product | Power mode = minimum, 15 pF<br>load          | 1   | _   | -   | MHz           |

|                |                        | Power mode = low, 15 pF load                 | 2   | -   | -   | MHz           |

|                |                        | Power mode = medium, 200 pF<br>load          | 1   | _   | _   | MHz           |

|                |                        | Power mode = high, 200 pF load               | 2.5 | -   | -   | MHz           |

| SR             | Slew rate, 20% - 80%   | Power mode = low, 15 pF load                 | 1.1 | -   | _   | V/µs          |

|                |                        | Power mode = medium, 200 pF<br>load          | 0.9 | _   | _   | V/µs          |

|                |                        | Power mode = high, 200 pF load               | 3   | -   | -   | V/µs          |

| e <sub>n</sub> | Input noise density    | Power mode = high, Vdda = 5 V,<br>at 100 kHz | _   | 45  | _   | nV/sqrtH<br>z |

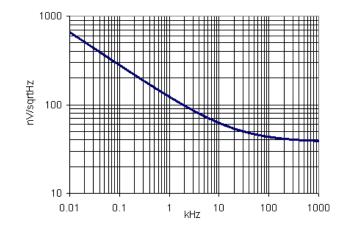

Figure 11-21. Opamp Noise vs Frequency, Power Mode = High, Vdda = 5 V

| Table 11-17. | 20-bit Delta-sigma  | ADC DC | Specifications | (continued)  |

|--------------|---------------------|--------|----------------|--------------|

|              | Lo bit Donta orgina |        | opeointoutione | (contantaca) |

| Parameter          | Description                                                                     | Conditions                                         | Min | Тур                 | Max  | Units |

|--------------------|---------------------------------------------------------------------------------|----------------------------------------------------|-----|---------------------|------|-------|

| Rin_Buff           | ADC input resistance                                                            | Input buffer used                                  | 10  | -                   | _    | MΩ    |

| Rin_ADC16          | ADC input resistance                                                            | Input buffer bypassed, 16-bit,<br>Range = ±1.024 V | _   | 74 <sup>[37]</sup>  | _    | kΩ    |

| Rin_ADC12          | ADC input resistance                                                            | Input buffer bypassed, 12 bit,<br>Range = ±1.024 V | -   | 148 <sup>[37]</sup> | _    | kΩ    |

| Vextref            | ADC external reference input voltage                                            | Pins P0[3], P3[2]                                  | 0.9 | -                   | 1.3  | V     |

| Current Co         | nsumption                                                                       |                                                    |     |                     |      |       |

| I <sub>DD_20</sub> | I <sub>DDD</sub> + I <sub>DDA</sub> Current consumption, 20 bit <sup>[38]</sup> | 187 sps, unbuffered                                | -   | -                   | 1.5  | mA    |

| I <sub>DD_16</sub> | I <sub>DDD</sub> + I <sub>DDA</sub> Current consumption, 16 bit <sup>[38]</sup> |                                                    | -   | -                   | 1.5  | mA    |

| I <sub>DD_12</sub> | I <sub>DDD</sub> + I <sub>DDA</sub> Current consumption, 12 bit <sup>[38]</sup> | 192 ksps, unbuffered                               | -   | -                   | 1.95 | mA    |

| I <sub>BUFF</sub>  | Buffer current consumption <sup>[38]</sup>                                      |                                                    | _   | _                   | 2.5  | mA    |

Notes

37. By using switched capacitors at the ADC input an effective input resistance is created. Holding the gain and number of bits constant, the resistance is proportional to the inverse of the clock frequency. This value is calculated, not measured. For more information see the Technical Reference Manual.

38. Based on device characterization (Not production tested).

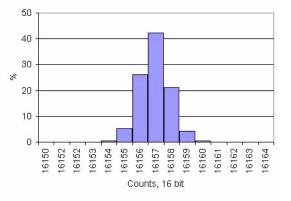

Figure 11-27. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Int Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Table 11-20. Delta-sigma ADC RMS Noise in Counts vs. Input Range and Sample Rate, 16-bit, Internal Reference, Single Ended

| Sample rate, | Input Voltage Range |               |              |               |  |  |

|--------------|---------------------|---------------|--------------|---------------|--|--|

| sps          | 0 to VREF           | 0 to VREF x 2 | VSSA to VDDA | 0 to VREF x 6 |  |  |

| 2000         | 1.21                | 1.02          | 1.14         | 0.99          |  |  |

| 3000         | 1.28                | 1.15          | 1.25         | 1.22          |  |  |

| 6000         | 1.36                | 1.22          | 1.38         | 1.22          |  |  |

| 12000        | 1.44                | 1.33          | 1.43         | 1.40          |  |  |

| 24000        | 1.67                | 1.50          | 1.43         | 1.53          |  |  |

| 48000        | 1.91                | 1.60          | 1.85         | 1.67          |  |  |

| Sample rate, | Input Voltage Range |           |           |               |            |  |

|--------------|---------------------|-----------|-----------|---------------|------------|--|

| sps          | ±VREF               | ±VREF / 2 | ±VREF / 4 | ±VREF / 8     | ±VREF / 16 |  |

| 2000         | 0.56                | 0.65      | 0.74      | 1.02          | 1.77       |  |

| 4000         | 0.58                | 0.72      | 0.81      | 1.10          | 1.98       |  |

| 8000         | 0.53                | 0.72      | 0.82      | 1.12          | 2.18       |  |

| 15625        | 0.58                | 0.72      | 0.85      | 1.13          | 2.20       |  |

| 32000        | 0.60                | 0.76      | INVA      | LID OPERATING | REGION     |  |

| 43750        | 0.58                | 0.75      |           |               |            |  |

| 48000        | 0.59                |           |           |               |            |  |

| Table 11-22. Delta-sigma ADC RMS Noise in Counts vs. Input Range and Sample Rate, 20-bit, External Reference, Single |  |

|----------------------------------------------------------------------------------------------------------------------|--|

| Ended                                                                                                                |  |

| Sample rate, |           | Input Voltage Range |              |               |  |  |  |

|--------------|-----------|---------------------|--------------|---------------|--|--|--|

| sps          | 0 to VREF | 0 to VREF x 2       | VSSA to VDDA | 0 to VREF x 6 |  |  |  |

| 8            | 1.28      | 1.24                | 6.02         | 0.97          |  |  |  |

| 23           | 1.33      | 1.28                | 6.09         | 0.98          |  |  |  |

| 45           | 1.77      | 1.26                | 6.28         | 0.96          |  |  |  |

| 90           | 1.65      | 0.91                | 6.84         | 0.95          |  |  |  |

| 187          | 1.87      | 1.06                | 7.97         | 1.01          |  |  |  |

### 11.5.7 VDAC

### Table 11-30. VDAC (Voltage Digital-to-Analog Converter) DC Specifications

| Parameter       | Description                         | Conditions            | Min      | Тур  | Max       | Units     |

|-----------------|-------------------------------------|-----------------------|----------|------|-----------|-----------|

| Resolution      |                                     |                       | -        | 8    | -         | 1         |

| -               | Output resistance <sup>[30]</sup>   |                       | <b>I</b> |      |           | -         |

| Rout            | High                                | Vout = 4 V            | -        | 16   | -         | kΩ        |

|                 | Low                                 | Vout = 1 V            | -        | 4    | -         | kΩ        |

| Vout            | Output voltage range, code = 255    | 1 V scale             | _        | 1.02 | _         | V         |

|                 |                                     | 4 V scale, Vdda = 5 V | _        | 4.08 | -<br>±2.5 | V         |

| INL             | Integral nonlinearity               | 1 V scale             | _        | ±2.1 | ±2.5      | LSB       |

| DNL             | Differential nonlinearity           | 1 V scale             | _        | ±0.3 | ±1        | LSB       |

|                 | Monotonicity                        |                       | _        | -    | ±1<br>Yes | _         |

| Eg              | Gain error                          | 1 V scale,            | _        | -    | ±2.5      | %         |

|                 |                                     | 4 V scale             | _        | -    | ±2.5      | %         |

| TC_Eg           | Temperature coefficient, gain error | 1 V scale,            | _        | -    | 0.03      | %FSR / °C |

|                 |                                     | 4 V scale             | _        | -    | 0.03      | %FSR / °C |

| VDAC_ICC        | Operating current                   | Low speed mode        | _        | - 1  | 100       | μA        |

|                 |                                     | High speed mode       | —        | -    | 500       | μA        |

| V <sub>OS</sub> | Zero scale error                    |                       | -        | 0    | ±0.9      | LSB       |

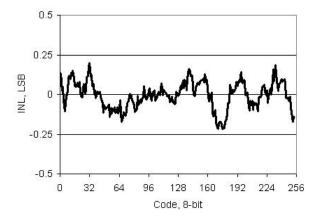

Figure 11-46. VDAC INL vs Input Code, 1 V Mode

# 11.5.12 LCD Direct Drive

### Table 11-39. LCD Direct Drive DC Specifications

| Parameter           | Description                                                                         | Conditions                                                                                                                                                                                       | Min | Тур                       | Max  | Units |

|---------------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|------|-------|

| I <sub>CC</sub>     | LCD system operating current                                                        | Device sleep mode with wakeup at<br>400-Hz rate to refresh LCDs, bus<br>clock = 3 Mhz, Vddio = Vdda = 3 V,<br>4 commons, 16 segments, 1/4 duty<br>cycle, 50 Hz frame rate, no glass<br>connected | -   | 38                        | -    | μA    |

| I <sub>CC_SEG</sub> | Current per segment driver                                                          | Strong drive mode                                                                                                                                                                                | -   | 260                       | -    | μA    |

| V <sub>BIAS</sub>   | LCD bias range (V <sub>BIAS</sub> refers to the main output voltage(V0) of LCD DAC) | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | 2   | -                         | 5    | V     |

|                     | LCD bias step size                                                                  | $V_{DDA} \ge 3 \text{ V} \text{ and } V_{DDA} \ge V_{BIAS}$                                                                                                                                      | -   | 9.1 ×<br>V <sub>DDA</sub> | -    | mV    |

|                     | LCD capacitance per<br>segment/common driver                                        | Drivers may be combined                                                                                                                                                                          | -   | 500                       | 5000 | pF    |

|                     | Long term segment offset                                                            |                                                                                                                                                                                                  | -   | -                         | 20   | mV    |

| I <sub>OUT</sub>    | Output drive current per segment driver)                                            | Vddio = 5.5V, strong drive mode                                                                                                                                                                  | 355 | -                         | 710  | μA    |

### Table 11-40. LCD Direct Drive AC Specifications

| Parameter        | Description    | Conditions | Min | Тур | Max | Units |

|------------------|----------------|------------|-----|-----|-----|-------|

| f <sub>LCD</sub> | LCD frame rate |            | 10  | 50  | 150 | Hz    |

## 11.7 Memory

Specifications are valid for  $-40^{\circ}$ C  $\leq$  Ta  $\leq 125^{\circ}$ C and Tj  $\leq 150^{\circ}$ C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

11.7.1 Flash

### Table 11-55. Flash DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Мах | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage | Vddd pin   | 1.71 | -   | 5.5 | V     |

#### Table 11-56. Flash AC Specifications

| Parameter | Description                                         | Conditions                                                                                        | Min | Тур | Max                                                                                       | Units   |

|-----------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|-----|-----|-------------------------------------------------------------------------------------------|---------|

| Twrite    | Block write time (erase + program)                  | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                                                   | -   | -   | 15                                                                                        | ms      |

|           |                                                     | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 140°C                                                  | -   | -   | 15                                                                                        | ms      |

| Terase    | Block erase time                                    | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                                                   | -   | -   | 15                                                                                        | ms      |

|           |                                                     | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 140°C                                                  | -   | -   | 10                                                                                        | ms      |

|           | Block program time                                  | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                                                   | -   | -   | 5                                                                                         | ms      |

|           |                                                     | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 140°C                                                  | -   | -   | 5                                                                                         | ms      |

| Tbulk     | Bulk erase time (16 KB to 64 KB) <sup>[53]</sup>    | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                                                   | -   | -   | 35                                                                                        | ms      |

|           |                                                     | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 140°C                                                  | -   | -   | 35                                                                                        | ms      |

|           | Sector erase time (8 KB to 16 KB) <sup>[53]</sup>   | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                                                   | -   | -   | 15         15         10         10         5         35         35         15         15 | ms      |

|           |                                                     | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 140°C                                                  | -   | -   |                                                                                           | ms      |

|           | Total device program time<br>(including JTAG, etc.) | No overhead <sup>[54]</sup>                                                                       | -   | -   | 5                                                                                         | seconds |

|           | Flash data retention time <sup>[55]</sup>           | Average ambient temp.<br>T <sub>A</sub> ≤ 55 °C,<br>100 K erase/program cycles                    | 20  | -   | -                                                                                         | years   |

|           |                                                     | Retention period measured from last erase cycle after 100k progra/erase cycles at $T_A \le 85$ °C | 10  | -   | _                                                                                         |         |

Notes

53. ECC not included.

54. See PSoC<sup>®</sup> 3 Device Programming Specifications for a description of a low-overhead method of programming PSoC 3 flash. (Please take care of Foot note numbers)

55. Cypress provides a retention calculator to calculate the retention lifetime based on customers' individual temperature profiles for operation over the -40 °C to +125 °C ambient temperature range. Contact customercare@cypress.com.

### 11.7.2 EEPROM

#### Table 11-57. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Мах | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | -   | 5.5 | V     |

#### Table 11-58. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                                  | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                             | -   | 2   | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, T <sub>A</sub> ≤ 25 °C,<br>1M erase/program cycles    | 20  | -   | -   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C,<br>100 K erase/program cycles | 20  | -   | -   |       |

|                    |                                                                             | Average ambient temp. T <sub>A</sub> ≤ 85 °C,<br>10 K erase/program cycles  | 10  | -   | -   |       |

### 11.7.3 Nonvolatile Latches (NVL)

### Table 11-59. NVL DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Мах | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage | Vddd pin   | 1.71 | -   | 5.5 | V     |

### Table 11-60. NVL AC Specifications

| Parameter | Description             | Conditions           | Min | Тур | Max | Units                       |

|-----------|-------------------------|----------------------|-----|-----|-----|-----------------------------|

|           | NVL endurance           | Programmed at 25°C   | 1K  | -   | -   | program/<br>erase<br>cycles |

|           |                         | Programmed at 0-70°C | 100 | -   | -   | program/<br>erase<br>cycles |

|           | NVL data retention time | Programmed at 55°C   | 20  | -   | -   | years                       |

|           |                         | Programmed at 0-70°C | 10  | -   | -   | years                       |

### 11.7.4 SRAM

#### Table 11-61. SRAM DC Specifications

| Parameter | Description            | Conditions | Min | Тур | Мах | Units |

|-----------|------------------------|------------|-----|-----|-----|-------|

| Vsram     | SRAM retention voltage |            | 1.2 | -   | -   | V     |

### Table 11-62. SRAM AC Specifications

| Parameter | Description              | Conditions                                       | Min | Тур | Мах | Units |

|-----------|--------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Fsram     | SRAM operating frequency | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | DC  | -   | 67  | MHz   |

|           |                          | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | DC  | -   | 50  | MHz   |

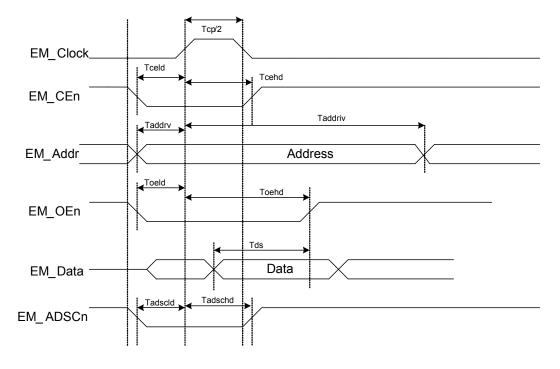

Figure 11-63. Synchronous Read Cycle Timing

Table 11-65. Synchronous Read Cycle Specifications

| Parameter | Description                       | Conditions          | Min     | Тур | Max | Units |

|-----------|-----------------------------------|---------------------|---------|-----|-----|-------|

| Т         | EMIF clock period <sup>[57]</sup> | $Vdda \geq 3.3 \ V$ | 30.3    | _   | -   | ns    |

| Tcp/2     | EM_Clock pulse high               |                     | T/2     | -   | -   | ns    |

| Tceld     | EM_CEn low to EM_Clock high       |                     | 5       | -   | -   | ns    |

| Tcehd     | EM_Clock high to EM_CEn high      |                     | T/2 – 5 | -   | -   | ns    |

| Taddrv    | EM_Addr valid to EM_Clock high    |                     | 5       | -   | -   | ns    |

| Taddriv   | EM_Clock high to EM_Addr invalid  |                     | T/2 – 5 | -   | -   | ns    |

| Toeld     | EM_OEn low to EM_Clock high       |                     | 5       | -   | -   | ns    |

| Toehd     | EM_Clock high to EM_OEn high      |                     | Т       | -   | -   | ns    |

| Tds       | Data valid before EM_OEn high     |                     | T + 15  | -   | -   | ns    |

| Tadscld   | EM_ADSCn low to EM_Clock high     |                     | 5       | -   | -   | ns    |

| Tadschd   | EM_Clock high to EM_ADSCn high    |                     | T/2 – 5 | -   | -   | ns    |

# 11.8 PSoC System Resources

Specifications are valid for -40°C  $\leq$  Ta  $\leq$  125°C and Tj  $\leq$  150°C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.8.1 POR with Brown Out

For brown out detect in regulated mode, Vddd and Vdda must be  $\geq$  2.0 V. Brown out detect is available in externally regulated mode. Table 11-67. Precise Power On Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | -   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | -   | 1.66 | V     |

### Table 11-68. Precise Power On Reset (PRES) with Brown Out AC Specifications

| Parameter | Description                                   | Conditions | Min | Тур | Мах | Units |

|-----------|-----------------------------------------------|------------|-----|-----|-----|-------|

| PRES_TR   | Response time                                 |            | -   | -   | 0.5 | μs    |

|           | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | -   | V/sec |

### 11.8.2 Voltage Monitors

#### Table 11-69. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Мах  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

#### Table 11-70. Voltage Monitors AC Specifications

| Parameter |                               | Conditions | Min | Тур | Мах | Units |

|-----------|-------------------------------|------------|-----|-----|-----|-------|

|           | Response time <sup>[59]</sup> |            | -   | -   | 1   | μs    |

### 11.9.2 Internal Low Speed Oscillator

### Table 11-77. ILO DC Specifications

| Parameter       | Description                       | Conditions                                       | Min | Тур | Max | Units |

|-----------------|-----------------------------------|--------------------------------------------------|-----|-----|-----|-------|

|                 | Operating current <sup>[64]</sup> | F <sub>OUT</sub> = 1 kHz                         | -   | -   | 1.7 | μA    |

| I <sub>CC</sub> |                                   | F <sub>OUT</sub> = 33 kHz                        | -   | -   | 2.6 | μA    |

|                 |                                   | F <sub>OUT</sub> = 100 kHz                       | -   | -   | 2.6 | μA    |

|                 | Leakage current <sup>[64]</sup>   | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | -   | 2.0 | 15  | nA    |

|                 |                                   | Power down mode                                  |     |     |     |       |

|                 | Leakage current <sup>[64]</sup>   | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | -   | -   | 200 | nA    |

|                 |                                   | Power down mode                                  |     |     |     |       |

# Table 11-78. ILO AC Specifications

| Parameter | Description                 | Conditions                                       | Min | Тур | Мах | Units |

|-----------|-----------------------------|--------------------------------------------------|-----|-----|-----|-------|

|           | Startup time                | Turbo mode                                       | -   | -   | 2   | ms    |

|           | ILO frequencies (trimmed)   | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  |     |     |     |       |

|           | 100 kHz                     |                                                  | 45  | 100 | 200 | kHz   |

| Filo      | 1 kHz                       |                                                  | 0.5 | 1   | 2   | kHz   |

| FIIO      | ILO frequencies (untrimmed) | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  |     |     |     |       |

|           | 100 kHz                     |                                                  | 30  | 100 | 300 | kHz   |

|           | 1 kHz                       |                                                  | 0.3 | 1   | 3.5 | kHz   |

|           | ILO frequencies (trimmed)   | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C |     |     |     |       |

|           | 100 kHz                     |                                                  | 45  | -   | 450 | kHz   |

| Filo      | 1 kHz                       |                                                  | 0.5 | -   | 5   | kHz   |

| FIIO      | ILO frequencies (untrimmed) | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C |     |     |     |       |

|           | 100 kHz                     |                                                  | 150 | -   | 500 | kHz   |

|           | 1 kHz                       |                                                  | 0.3 | -   | 6.5 | kHz   |

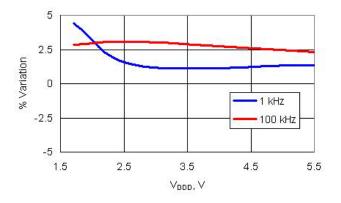

#### Figure 11-70. ILO Frequency Variation vs. V<sub>DD</sub>

Note 64. This value is calculated, not measured.

65. Based on device characterization (Not production tested).

# **16. Document Conventions**

### 16.1 Units of Measure

### Table 16-1. Units of Measure

| Symbol | Unit of Measure        |

|--------|------------------------|

| °C     | degree Celsius         |

| dB     | decibels               |

| fF     | femtofarads            |

| Hz     | hertz                  |

| KB     | 1024 bytes             |

| kbps   | kilobits per second    |

| Khr    | kilohours              |

| kHz    | kilohertz              |

| kΩ     | kilohms                |

| ksps   | kilosamples per second |

| LSB    | least significant bit  |

| Mbps   | megabits per second    |

| MHz    | megahertz              |

| MΩ     | megaohms               |

| Msps   | megasamples per second |

| μA     | microamperes           |

| μF     | microfarads            |

| μH     | microhenrys            |

| μs     | microseconds           |

| μV     | microvolts             |

| μW     | microwatts             |

| mA     | milliamperes           |

| ms     | milliseconds           |

| mV     | millivolts             |

| nA     | nanoamperes            |

| ns     | nanoseconds            |

| nV     | nanovolts              |

| Ω      | ohms                   |

| pF     | picofarads             |

| ppm    | parts per million      |

| ps     | picoseconds            |

| S      | seconds                |

| sps    | samples per second     |

| sqrtHz | square root of hertz   |

| V      | volts                  |

# 18. Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

| Products                 |                           |

|--------------------------|---------------------------|

| Automotive               | cypress.com/go/automotive |

| Clocks & Buffers         | cypress.com/go/clocks     |

| Interface                | cypress.com/go/interface  |

| Lighting & Power Control | cypress.com/go/powerpsoc  |

|                          | cypress.com/go/plc        |

| Memory                   | cypress.com/go/memory     |

| PSoC                     | cypress.com/go/psoc       |

| Touch Sensing            | cypress.com/go/touch      |

| USB Controllers          | cypress.com/go/USB        |

| Wireless/RF              | cypress.com/go/wireless   |

|                          |                           |

# **PSoC<sup>®</sup> Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP

Cypress Developer Community Community | Forums | Blogs | Video | Training

Technical Support cypress.com/go/support

© Cypress Semiconductor Corporation, 2006-2014. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

#### Document Number: 001-54683 Rev. \*K

#### Revised March 3, 2014

Page 146 of 146

CapSense<sup>®</sup>, PSoC<sup>®</sup> 3, PSoC<sup>®</sup> 5, and PSoC<sup>®</sup> Creator™ are trademarks and PSoC<sup>®</sup> is a registered trademark of Cypress Semiconductor Corp. ARM is a registered trademark, and Keil, and RealView are trademarks, of ARM Limited. All other trademarks or registered trademarks referenced herein are property of the respective corporations.