Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART                         |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866pva-005 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C38 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as 1.8 V  $\pm$  5%, 2.5 V  $\pm$ 10%, 3.3 V  $\pm$  10%, or 5.0 V  $\pm$  10%, or directly from a wide range of battery types.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a 1- $\mu$ A sleep mode with RTC. In the second mode, the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 29 of this data sheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 60 of this data sheet.

## 2. Pinouts

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 through Figure 2-4 show the pins that are powered by each VDDIO.

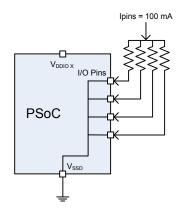

Each VDDIO may source up to 100 mA <sup>[8]</sup> total to its associated I/O pins, as shown in Figure 2-1.

#### Figure 2-1. VDDIO Current Limit

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA  $^{[8]}$  total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

For the 48-pin devices, the set of I/O pins associated with VDDIO0 plus VDDIO2 may sink up to 100 mA<sup>[8]</sup> total. The set of I/O pins associated with VDDIO1 plus VDDIO3 may sink up to a total of 100 mA.

Note

The 100 mA source/ sink current per Vddio is valid only for temperature range of -40 °C to +85 °C. For extended temperature range of -40 °C to +125 °C, the maximum source or sink current per Vddio is 40 mA.

| (SIO) P12[2]<br>(SIO) P12[3]<br>(Opamp2OUT, GPIO) P0[0]<br>(Opamp0UT, GPIO) P0[1]<br>(Opamp0+, GPIO) P0[2]<br>(Opamp2+, GPIO) P0[3]<br>(Opamp2+, GPIO) P0[4]<br>(IDAC0, GPIO) P0[5]<br>(IDAC2, GPIO) P0[6]<br>(VCCD<br>VSSD<br>VDDD<br>(GPIO) P2[3]<br>(GPIO) P2[4]<br>VDD02 | 2<br>3<br>4<br>5<br>6<br>7-<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16 | Lines show<br>VDDIO to I/C<br>supply<br>association<br>SSOP | 47<br>46<br>45<br>44<br>43<br>42<br>-41<br>40<br>39<br>38<br>37<br>-36<br>35<br>34<br>33 | VDDA<br>VSSA<br>VCCA<br>P15[3] (GPIO, KHZ XTAL: XI)<br>P15[2] (GPIO, KHZ XTAL: XO)<br>P12[1] (SIO, I2C1: SDA)<br>P12[0] (SIO, I2C1: SCL)<br>VDDIO3<br>P15[1] (GPIO, MHZ XTAL: XI)<br>P15[0] (GPIO, MHZ XTAL: XO)<br>VCCD<br>VSSD<br>VDDD<br>P15[7] (USBIO, D-, SWDCK)<br>[9]<br>P15[6] (USBIO, D-, SWDCK)<br>[9]<br>P15[6] (GPIO)<br>P16[6] (GPIO) |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (GPIO) P2[3] 🗖                                                                                                                                                                                                                                                               | 15<br>16<br>17-<br>18<br>19<br>20<br>21<br>22<br>23                             |                                                             | 34<br>33<br>32<br>-31<br>30<br>29<br>28<br>27<br>26                                      | ■ P15[7] (USBIO, D-, SWDCK)<br>■ P15[6] (USBIO, D+, SWDIO)                                                                                                                                                                                                                                                                                         |

#### Figure 2-3. 48-pin SSOP Part Pinout

### 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

#### Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | А             | Clear accumulator                     | 1     | 1      |

| CPL | А             | Complement accumulator                | 1     | 1      |

| RL  | А             | Rotate accumulator left               | 1     | 1      |

| RLC | А             | Rotate accumulator left through carry | 1     | 1      |

| RR  | А             | Rotate accumulator right              | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PΑ            | Swap nibbles within accumulator       | 1     | 1      |

#### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed

addressing mode. Table 4-3 lists the various data transfer instructions available.

#### 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 lists the available Boolean instructions.

#### 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

### Table 4-5. Jump Instructions

| Mnemonic             | Description                                                  | Bytes | Cycles |

|----------------------|--------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                     | 2     | 4      |

| LCALL addr16         | Long subroutine call                                         | 3     | 4      |

| RET                  | Return from subroutine                                       | 1     | 4      |

| RETI                 | Return from interrupt                                        | 1     | 4      |

| AJMP addr11          | Absolute jump                                                | 2     | 3      |

| LJMP addr16          | Long jump                                                    | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                               | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                  | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                               | 2     | 4      |

| CJNE A, Direct, rel  | Compare direct byte to accumulator and jump if not equal     | 3     | 5      |

| CJNE A, #data, rel   | Compare immediate data to accumulator and jump if not equal  | 3     | 4      |

| CJNE Rn, #data, rel  | Compare immediate data to register and jump if not equal     | 3     | 4      |

| CJNE @Ri, #data, rel | Compare immediate data to indirect RAM and jump if not equal | 3     | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                      | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                   | 3     | 5      |

| NOP                  | No operation                                                 | 1     | 1      |

#### 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data

#### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

### 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

#### Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and Real Time Clock functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 on page 31 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels.

| Power Modes         | Description                                                                                                                                                                                                                    | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks         | Regulator                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all<br>peripherals available<br>(programmable)                                                                                                                                                      | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off                  | Manual register<br>entry                   | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                                          | Manual register<br>entry                   | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO            | Both digital and analog<br>regulators buzzed.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used. |

| Hibernate           | All subsystems automatically<br>disabled<br>Lowest power consuming mode<br>with all peripherals and internal<br>regulators disabled, except<br>hibernate regulator is enabled<br>Configuration and memory<br>contents retained | Manual register<br>entry                   | PICU                                                    |                       | Only hibernate regulator<br>active.                                                                                               |

#### Table 6-2. Power Modes

### Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | -              | 1.2 mA <sup>[12]</sup> | Yes               | All                  | All                 | All                        | -                                                       | All               |

| Alternate<br>Active | _              | -                      | User<br>defined   | All                  | All                 | All                        | -                                                       | All               |

| Sleep               | <15 µs         | 1 μΑ                   | No                | l <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

Note

12. Bus clock off. Execute from cache at 6 MHz. See Table 11-2 on page 66.

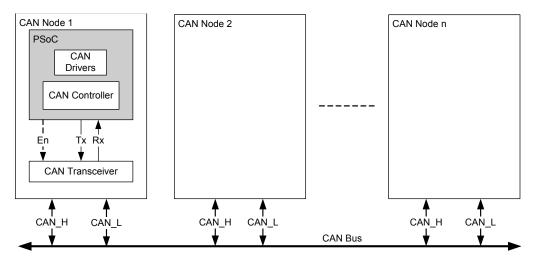

## 7.5 CAN

The CAN peripheral is a fully functional controller area network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

#### Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- □ Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- □ 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE, and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- a Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- Fixed priority

- Message transmissions abort capability

#### 7.5.2 Software Tools Support

- CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

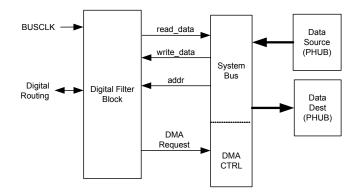

### 7.9 Digital Filter Block

Some devices in the CY8C38 family of devices have a dedicated HW accelerator block used for digital filtering. The DFB has a dedicated multiplier and accumulator that calculates a 24-bit by 24-bit multiply accumulate in one bus clock cycle. This enables the mapping of a direct form FIR filter that approaches a computation rate of one FIR tap for each clock cycle. The MCU can implement any of the functions performed by this block, but at a slower rate that consumes MCU bandwidth.

The heart of the DFB is a datapath (DP), which is the numerical calculation unit of the DFB. The DP is a 24-bit fixed-point numerical processor containing a 48-bit multiply and accumulate function (MAC), a multi-function ALU, sample and coefficient data RAMs as well as data routing, shifting, holding and rounding functions.

In the MAC, two 24-bit values can be multiplied and the result added to the 48-bit accumulator in each bus clock cycle. The MAC is the only portion of the DP that is wider than 24 bits. All results from the MAC are passed on to the ALU as 24-bit values representing the high-order 24 bits in the accumulator shifted by one (bits 46:23). The MAC assumes an implied binary point after the most significant bit.

The DP also contains an optimized ALU that supports add, subtract, comparison, threshold, absolute value, squelch, saturation, and other functions. The DP unit is controlled by seven control fields totaling 18 bits coming from the DFB Controller. For more information see the TRM.

The PSoC Creator interface provides a wizard to implement FIR and IIR digital filters with coefficients for LPF, BPF, HPF, Notch and arbitrary shape filters. 64 pairs of data and coefficients are stored. This enables a 64 tap FIR filter or up to 4 16 tap filters of either FIR or IIR formulation.

#### Figure 7-19. DFB Application Diagram (pwr/gnd not shown)

The typical use model is for data to be supplied to the DFB over the system bus from another on-chip system data source such as an ADC. The data typically passes through main memory or is directly transferred from another chip resource through DMA. The DFB processes this data and passes the result to another on chip resource such as a DAC or main memory through DMA on the system bus.

Data movement in or out of the DFB is typically controlled by the system DMA controller but can be moved directly by the MCU.

## 8. Analog Subsystem

The analog programmable system creates application specific combinations of both standard and advanced analog signal processing blocks. These blocks are then interconnected to each other and also to any pin on the device, providing a high level of design flexibility and IP security. The features of the analog subsystem are outlined here to provide an overview of capabilities and architecture.

- Flexible, configurable analog routing architecture provided by analog globals, analog mux bus, and analog local buses.

- High resolution delta-sigma ADC.

- Up to four 8-bit DACs that provide either voltage or current output.

- Four comparators with optional connection to configurable LUT outputs.

- Up to four configurable switched capacitor/continuous time (SC/CT) blocks for functions that include opamp, unity gain buffer, programmable gain amplifier, transimpedance amplifier, and mixer.

- Up to four opamps for internal use and connection to GPIO that can be used as high current output buffers.

- CapSense subsystem to enable capacitive touch sensing.

- Precision reference for generating an accurate analog voltage for internal analog blocks.

### 8.3.2 LUT

The CY8C38 family of devices contains four LUTs. The LUT is a two input, one output lookup table that is driven by any one or two of the comparators in the chip. The output of any LUT is routed to the digital system interface of the UDB array. From the digital system interface of the UDB array, these signals can be connected to UDBs, DMA controller, I/O, or the interrupt controller.

The LUT control word written to a register sets the logic function on the output. The available LUT functions and the associated control word is shown in Table 8-2.

| Control Word | Output (A and B are LUT inputs) |

|--------------|---------------------------------|

| 0000b        | <b>FALSE</b> ('0')              |

| 0001b        | A AND B                         |

| 0010b        | A AND (NOT B)                   |

| 0011b        | A                               |

| 0100b        | (NOT A) AND B                   |

| 0101b        | В                               |

| 0110b        | A XOR B                         |

| 0111b        | A OR B                          |

| 1000b        | A NOR B                         |

| 1001b        | A XNOR B                        |

| 1010b        | NOT <b>B</b>                    |

| 1011b        | A OR (NOT B)                    |

| 1100b        | NOT A                           |

| 1101b        | (NOT <b>A</b> ) OR <b>B</b>     |

| 1110b        | A NAND B                        |

| 1111b        | <b>TRUE</b> ('1')               |

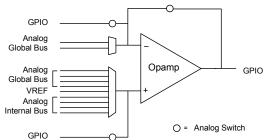

### 8.4 Opamps

The CY8C38 family of devices contain up to four general purpose opamps in a device.

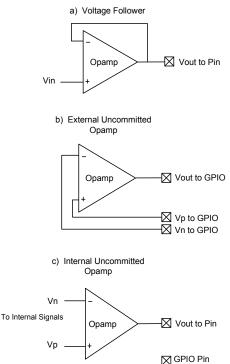

#### Figure 8-6. Opamp

The opamp is uncommitted and can be configured as a gain stage or voltage follower, or output buffer on external or internal signals.

See Figure 8-7. In any configuration, the input and output signals can all be connected to the internal global signals and monitored with an ADC, or comparator. The configurations are implemented with switches between the signals and GPIO pins.

### Figure 8-7. Opamp Configurations

The opamp has three speed modes, slow, medium, and fast. The slow mode consumes the least amount of quiescent power and the fast mode consumes the most power. The inputs are able to swing rail-to-rail. The output swing is capable of rail-to-rail operation at low current output, within 50 mV of the rails. When driving high current loads (about 25 mA) the output voltage may only get within 500 mV of the rails.

### 8.5 Programmable SC/CT Blocks

The CY8C38 family of devices contains up to four switched capacitor/continuous time (SC/CT) blocks in a device. Each switched capacitor/continuous time block is built around a single rail-to-rail high bandwidth opamp.

Switched capacitor is a circuit design technique that uses capacitors plus switches instead of resistors to create analog functions. These circuits work by moving charge between capacitors by opening and closing different switches. Nonoverlapping in phase clock signals control the switches, so that not all switches are ON simultaneously.

The PSoC Creator tool offers a user friendly interface, which allows you to easily program the SC/CT blocks. Switch control and clock phase control configuration is done by PSoC Creator so users only need to determine the application use parameters such as gain, amplifier polarity, V<sub>REF</sub> connection, and so on.

The same opamps and block interfaces are also connectable to an array of resistors which allows the construction of a variety of continuous time functions.

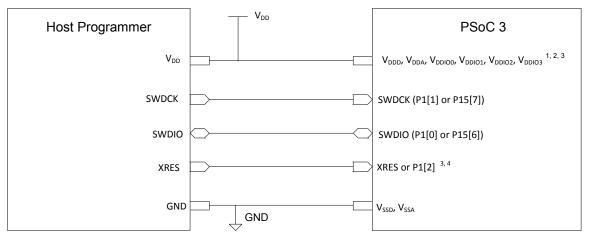

### 9.2 Serial Wire Debug Interface

The SWD interface is the preferred alternative to the JTAG interface. It requires only two pins instead of the four or five needed by JTAG. SWD provides all of the programming and debugging features of JTAG at the same speed. SWD does not provide access to scan chains or device chaining. The SWD clock frequency can be up to 1/3 of the CPU clock frequency.

SWD uses two pins, either two of the JTAG pins (TMS and TCK) or the USBIO D+ and D– pins. The USBIO pins are useful for in system programming of USB solutions that would otherwise require a separate programming connector. One pin is used for the data clock and the other is used for data input and output.

SWD can be enabled on only one of the pin pairs at a time. This only happens if, within 8  $\mu$ s (key window) after reset, that pin pair (JTAG or USB) receives a predetermined sequence of 1s and 0s. SWD is used for debugging or for programming the flash memory.

The SWD interface can be enabled from the JTAG interface or disabled, allowing its pins to be used as GPIO. Unlike JTAG, the SWD interface can always be reacquired on any device during the key window. It can then be used to reenable the JTAG interface, if desired. When using SWD or JTAG pins as standard GPIO, make sure that the GPIO functionality and PCB circuits do not interfere with SWD or JTAG use.

#### Figure 9-2. SWD Interface Connections between PSoC 3 and Programmer

- <sup>1</sup> The voltage levels of the Host Programmer and the PSoC 3 voltage domains involved in Programming should be the same. XRES pin (XRES\_N or P1[2]) is powered by V<sub>DDI01</sub>. The USB SWD pins are powered by V<sub>DDD</sub>. So for Programming using the USB SWD pins with XRES pin, the V<sub>DDD</sub>, V<sub>DDI01</sub> of PSoC 3 should be at the same voltage level as Host V<sub>DD</sub>. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer. The Port 1 SWD pins are powered by V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 should be at same voltage level as host V<sub>DD</sub> for Port 1 SWD programming. Rest of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI01</sub>, V<sub>DDI01</sub>. So V<sub>DDI01</sub> of PSoC 3 voltage domains (V<sub>DDA</sub>, V<sub>DDI02</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programming. Rest of PSoC 3 voltage domains (V<sub>DDD</sub>, V<sub>DDA</sub>, V<sub>DDI00</sub>, V<sub>DDI02</sub>, V<sub>DDI03</sub>) need not be at the same voltage level as host Programmer.

- Vdda must be greater than or equal to all other power supplies (Vddd, Vddio's) in PSoC 3.

- <sup>3</sup> For Power cycle mode Programming, XRES pin is not required. But the Host programmer must have the capability to toggle power (Vddd, Vdda, All Vddio's) to PSoC 3. This may typically require external interface circuitry to toggle power which will depend on the programming setup. The power supplies can be brought up in any sequence, however, once stable, VDDA must be greater than or equal to all other supplies.

- <sup>4</sup> P1[2] will be configured as XRES by default only for 48-pin devices (without dedicated XRES pin). For devices with dedicated XRES pin, P1[2] is GPIO pin by default. So use P1[2] as Reset pin only for 48pin devices, but use dedicated XRES pin for rest of devices.

# 10. Development Support

The CY8C38 family has a rich set of documentation, development tools, and online resources to assist you during your development process. Visit psoc.cypress.com/getting-started to find out more.

### 10.1 Documentation

A suite of documentation, supports the CY8C38 family to ensure that you can find answers to your questions quickly. This section contains a list of some of the key documents.

**Software User Guide**: A step-by-step guide for using PSoC Creator. The software user guide shows you how the PSoC Creator build process works in detail, how to use source control with PSoC Creator, and much more.

**Component data sheets**: The flexibility of PSoC allows the creation of new peripherals (components) long after the device has gone into production. Component data sheets provide all of the information needed to select and use a particular component, including a functional description, API documentation, example code, and AC/DC specifications.

**Application Notes**: PSoC application notes discuss a particular application of PSoC in depth; examples include brushless DC motor control and on-chip filtering. Application notes often include example projects in addition to the application note document.

**Technical Reference Manual**: The Technical Reference Manual (TRM) contains all the technical detail you need to use a PSoC device, including a complete description of all PSoC registers.

### 10.2 Online

In addition to print documentation, the Cypress PSoC forums connect you with fellow PSoC users and experts in PSoC from around the world, 24 hours a day, 7 days a week.

### 10.3 Tools

With industry standard cores, programming, and debugging interfaces, the CY8C38 family is part of a development tool ecosystem. Visit us at www.cypress.com/go/psoccreator for the latest information on the revolutionary, easy to use PSoC Creator IDE, supported third party compilers, programmers, debuggers, and development kits.

## Table 11-9. SIO AC Specifications

| Parameter | Description                                                                          | Conditions                                                                                            | Min | Тур | Max                        | Units |

|-----------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|----------------------------|-------|

| TriseF    | Rise time in Fast Strong Mode (90/10%) <sup>[30]</sup>                               | Cload = 25 pF, Vddio = 3.3 V                                                                          | -   | -   | 12                         | ns    |

| TfallF    | Fall time in Fast Strong Mode (90/10%) <sup>[30]</sup>                               | Cload = 25 pF, Vddio = 3.3 V                                                                          | -   | -   | 12                         | ns    |

| TriseS    | Rise time in Slow Strong Mode (90/10%) <sup>[30]</sup>                               | Cload = 25 pF, Vddio = 3.0 V                                                                          | -   | -   | 80                         | ns    |

| TfallS    | Fall time in Slow Strong Mode (90/10%) <sup>[30]</sup>                               | Cload = 25 pF, Vddio = 3.0 V                                                                          | -   | -   | 70                         | ns    |

|           | SIO output operating frequency                                                       | · · · · · · · · · · · · · · · · · · ·                                                                 |     |     |                            |       |

|           | 3.3 V < Vddio < 5.5 V, Unregulated<br>output (GPIO) mode, fast strong                | 90/10% Vddio into 25 pF, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                              | -   | -   | 33                         | MHz   |

|           | drive mode                                                                           | 90/10% Vddio into 25 pF, -40°C ≤<br>Ta ≤ 125°C and Tj ≤ 150°C                                         | -   | -   | 24                         | MHz   |

|           | 1.71 V < Vddio < 3.3 V, Unregulated<br>output (GPIO) mode, fast strong<br>drive mode | 90/10% Vddio into 25 pF                                                                               | -   | -   | 16                         | MHz   |

| Fsioout   | 3.3 V < Vddio < 5.5 V, Unregulated<br>output (GPIO) mode, slow strong<br>drive mode  | 90/10% Vddio into 25 pF                                                                               | -   | -   | 5                          | MHz   |

|           | 1.71 V < Vddio < 3.3 V, Unregulated<br>output (GPIO) mode, slow strong<br>drive mode | 90/10% Vddio into 25 pF                                                                               | -   | -   | 80<br>70<br>33<br>24<br>16 | MHz   |

|           | 3.3 V < Vddio < 5.5 V, Regulated output mode, fast strong drive mode                 | Output continuously switching into 25 pF                                                              | -   | -   |                            | MHz   |

|           | 1.71 V < Vddio < 3.3 V, Regulated output mode, fast strong drive mode                | Output continuously switching into 25 pF                                                              | -   | -   |                            | MHz   |

|           | 1.71 V < Vddio < 5.5 V, Regulated<br>output mode, slow strong drive<br>mode          | Output continuously switching into 25 pF                                                              | -   | -   | 2.5                        | MHz   |

|           | SIO input operating frequency                                                        |                                                                                                       |     |     | I                          |       |

| Fsioin    | 1.71 V <u>&lt;</u> Vddio ≤ 5.5 V                                                     | 90/10% better than 60/40 duty cycle, -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                  | -   | -   | 66                         | MHz   |

|           | 1.71 V <u>V</u> VUUO <u>5</u> .5 V                                                   | 90/10% better than 60/40 duty cycle, $-40^{\circ}C \le Ta \le 125^{\circ}C$ and Tj $\le 150^{\circ}C$ | -   | -   | 50                         | MHz   |

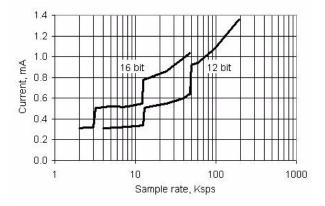

### 11.5.2 Delta-Sigma ADC

Unless otherwise specified, operating conditions are:

- Operation in continuous sample mode

- fclk = 3.072 MHz for resolution = 16 to 20 bits; fclk = 6.144 MHz for resolution = 8 to 15 bits

- Reference = 1.024 V internal reference bypassed on P3.2 or P0.3

- Unless otherwise specified, all charts and graphs show typical values

### Table 11-17. 20-bit Delta-sigma ADC DC Specifications

| Parameter | Description                                                       | Conditions                                                                  | Min              | Тур | Max                  | Units  |

|-----------|-------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------|-----|----------------------|--------|

|           | Resolution                                                        |                                                                             | 8                | -   | 20                   | bits   |

|           | Number of channels, single ended                                  |                                                                             | -                | -   | No. of<br>GPIO       | -      |

|           | Number of channels, differential                                  | Differential pair is formed using a pair of GPIOs.                          | _                | -   | No. of<br>GPIO/2     | -      |

|           | Monotonic                                                         | Yes                                                                         | -                | -   | -                    | -      |

| Ge        | Gain error                                                        | Buffered, buffer gain = 1, Range =<br>±1.024 V, 16-bit mode, 25 °C          | _                | -   | ±0.2                 | %      |

| Gd        | Gain drift                                                        | Buffered, buffer gain = 1, Range =<br>±1.024 V, 16-bit mode                 | _                | -   | 50                   | ppm/°C |

| Vos       | Input offset voltage                                              | Buffered, 16-bit mode,<br>full voltage range                                | _                | -   | ±0.2                 | mV     |

| V03       | input onset voltage                                               | Buffered, 16-bit mode,<br>V <sub>DDA</sub> = 1.8 V <u>+</u> 5%              | _                | -   | ±0.1                 | mV     |

| TCVos     | Temperature coefficient, input offset voltage                     | Buffer gain = 1, 16-bit,<br>Range = ±1.024 V                                | _                | -   | 1                    | µV/°C  |

|           | Input voltage range, single ended <sup>[36]</sup>                 |                                                                             | $V_{SSA}$        | -   | V <sub>DDA</sub>     | V      |

|           | Input voltage range, differential unbuf-<br>fered <sup>[36]</sup> |                                                                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub>     | V      |

|           | Input voltage range, differential, buffered <sup>[36]</sup>       |                                                                             | V <sub>SSA</sub> | -   | V <sub>DDA</sub> – 1 | V      |

| PSRRb     | Power supply rejection ratio, buffered <sup>[36]</sup>            | Buffer gain = 1, 16-bit,<br>Range = ±1.024 V                                | 90               | -   | -                    | dB     |

| CMRRb     | Common mode rejection ratio, buffered <sup>[36]</sup>             | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V                                | 85               | -   | -                    | dB     |

| INL20     | Integral non linearity <sup>[36]</sup>                            | Range = ±1.024 V, unbuffered                                                | -                | -   | ±32                  | LSB    |

| DNL20     | Differential non linearity <sup>[36]</sup>                        | Range = ±1.024 V, unbuffered                                                | -                | -   | ±1                   | LSB    |

| INL16     | Integral non linearity <sup>[36]</sup>                            | Range = $\pm 1.024$ V, unbuffered;<br>2.7 V $\leq V_{DDA} \leq 5.5$ V range | -                | -   | ±2                   | LSB    |

|           |                                                                   | 1.71 V ≤ V <sub>DDA</sub> < 2.7 V range                                     | -2.1             | -   | +2.7                 | LSB    |

| DNL16     | Differential non linearity <sup>[36]</sup>                        | Range = ±1.024 V, unbuffered;<br>2.7 V ≤ V <sub>DDA</sub> ≤ 5.5 V range     | -                | -   | ±1                   | LSB    |

|           |                                                                   | 1.71 V ≤ V <sub>DDA</sub> < 2.7 V range                                     | -1               | -   | +1.1                 | LSB    |

| INL12     | Integral non linearity <sup>[36]</sup>                            | Range = ±1.024 V, unbuffered                                                | -                | -   | ±1                   | LSB    |

| DNL12     | Differential non linearity <sup>[36]</sup>                        | Range = ±1.024 V, unbuffered                                                | -                | -   | ±1                   | LSB    |

| INL8      | Integral non linearity <sup>[36]</sup>                            | Range = ±1.024 V, unbuffered                                                | _                | -   | ±1                   | LSB    |

| DNL8      | Differential non linearity <sup>[36]</sup>                        | Range = ±1.024 V, unbuffered                                                | _                | -   | ±1                   | LSB    |

#### Note

36. Based on device characterization (not production tested).

### Table 11-18. Delta-sigma ADC AC Specifications

| Parameter    | Description                                                       | Conditions                                   | Min | Тур | Max    | Units   |

|--------------|-------------------------------------------------------------------|----------------------------------------------|-----|-----|--------|---------|

|              | Startup time                                                      |                                              | 1   | -   | 4      | Samples |

| THD          | Total harmonic distortion <sup>[38]</sup>                         | Buffer gain = 1, 16 bit,<br>Range = ±1.024 V | -   | -   | 0.0040 | %       |

| 20-Bit Resol | ution Mode                                                        |                                              |     |     |        | •       |

| SR20         | Sample rate <sup>[38]</sup>                                       | Range = ±1.024 V, unbuffered                 | 7.8 | _   | 187    | sps     |

| BW20         | Input bandwidth at max sample rate <sup>[38]</sup>                | Range = ±1.024 V, unbuffered                 | 1   | 40  | -      | Hz      |

| 16-Bit Resol | ution Mode                                                        |                                              |     |     |        |         |

| SR16         | Sample rate <sup>[38]</sup>                                       | Range = ±1.024 V, unbuffered                 | 2   | _   | 48     | ksps    |

| BW16         | Input bandwidth at max sample rate <sup>[38]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 11  | -      | kHz     |

| SINAD16int   | Signal to noise ratio, 16-bit, internal reference <sup>[38]</sup> | Range = ±1.024V, unbuffered                  | 79  | -   | -      | dB      |

| SINAD16ext   | Signal to noise ratio, 16-bit, external reference <sup>[38]</sup> | Range = ±1.024 V, unbuffered                 | 83  | -   | -      | dB      |

| 12-Bit Resol | ution Mode                                                        |                                              |     |     |        |         |

| SR12         | Sample rate, continuous, high power <sup>[38]</sup>               | Range = ±1.024 V, unbuffered                 | 4   | _   | 192    | ksps    |

| BW12         | Input bandwidth at max sample rate <sup>[38]</sup>                | Range = ±1.024 V, unbuffered                 | 1   | 44  | -      | kHz     |

| SINAD12int   | Signal to noise ratio, 12-bit, internal reference <sup>[38]</sup> | Range = ±1.024 V, unbuffered                 | 66  | -   | -      | dB      |

| 8-Bit Resolu | tion Mode                                                         |                                              |     |     |        | •       |

| SR8          | Sample rate, continuous, high power <sup>[38]</sup>               | Range = ±1.024 V, unbuffered                 | 8   | _   | 384    | ksps    |

| BW8          | Input bandwidth at max sample rate <sup>[38]</sup>                | Range = ±1.024 V, unbuffered                 | -   | 88  | -      | kHz     |

| SINAD8int    | Signal to noise ratio, 8-bit, internal reference <sup>[38]</sup>  | Range = ±1.024 V, unbuffered                 | 43  | _   | -      | dB      |

### Table 11-19. Delta-sigma ADC Sample Rates, Range = ±1.024 V

| Resolution, | Conti | nuous                  | Multi-       | Sample | Multi-Sa | mple Turbo |

|-------------|-------|------------------------|--------------|--------|----------|------------|

| Bits        | Min   | Max                    | Min          | Max    | Min      | Max        |

| 8           | 8000  | 384000                 | 1911         | 91701  | 1829     | 87771      |

| 9           | 6400  | 307200                 | 74024        | 1489   | 71441    |            |

| 10          | 5566  | 267130                 | 1348         | 64673  | 1307     | 62693      |

| 11          | 4741  | 4741 227555 1154 55351 |              |        | 1123     | 53894      |

| 12          | 4000  | 000 192000 978 46900   |              | 46900  | 956      | 45850      |

| 13          | 3283  | 157538                 | 88 806 38641 |        | 791      | 37925      |

| 14          | 2783  | 133565                 | 685          | 32855  | 674      | 32336      |

| 15          | 2371  | 113777                 | 585          | 28054  | 577      | 27675      |

| 16          | 2000  | 48000                  | 495          | 11861  | 489      | 11725      |

| 17          | 500   | 12000                  | 124          | 2965   | 282      | 6766       |

| 18          | 125   | 3000                   | 31           | 741    | 105      | 2513       |

| 19          | 16    | 375                    | 4            | 93     | 15       | 357        |

| 20          | 8     | 187.5                  | 2            | 46     | 8        | 183        |

### Figure 11-24. Delta-sigma ADC IDD vs sps, Range = ±1.024 V, Continuous Sample Mode, Input Buffer Bypassed

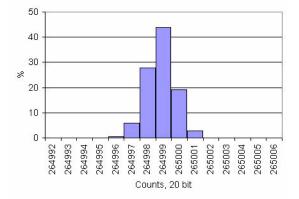

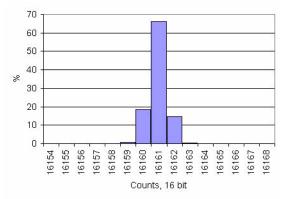

Figure 11-25. Delta-sigma ADC Noise Histogram, 1000 Samples, 20-Bit, 187 sps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

Figure 11-26. Delta-sigma ADC Noise Histogram, 1000 Samples, 16-bit, 48 ksps, Ext Ref, V<sub>IN</sub> = V<sub>REF</sub>/2, Range = ±1.024 V

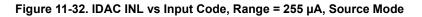

### 11.5.6 IDAC

All specifications are based on use of the low-resistance IDAC output pins (see Pin Descriptions on page 9 for details). See the IDAC component data sheet in PSoC Creator for full electrical specifications and APIs.

Unless otherwise specified, all charts and graphs show typical values.

| Parameter        | Description                           | Conditions                                                                                                                                   | Min | Тур    | Max  | Units  |  |

|------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|--------|--|

| Resolution       |                                       |                                                                                                                                              | -   | 8      | -    |        |  |

| I <sub>OUT</sub> | Output current at code = 255          | $\begin{array}{l} \mbox{Range} = 2.04 \mbox{ mA, code} = 255, \\ \mbox{V}_{\mbox{DDA}} \geq 2.7 \mbox{ V, Rload} = 600 \ \Omega \end{array}$ | _   | 2.04   | _    | mA     |  |

|                  |                                       | Range = 2.04 mA, high speed mode, code = 255, V_{DDA} $\leq$ 2.7 V, Rload = 300 $\Omega$                                                     | -   | 2.04   | -    | mA     |  |

|                  |                                       | Range = 255 $\mu$ A, code = 255, Rload<br>= 600 $\Omega$                                                                                     | -   | 255    | -    | μA     |  |

|                  |                                       | Range = 31.875 $\mu$ A, code = 255,<br>Rload = 600 $\Omega$                                                                                  | -   | 31.875 | _    | μA     |  |

|                  | Monotonicity                          |                                                                                                                                              | -   | -      | Yes  |        |  |

| INL              | Integral nonlinearity                 | Sink mode, range = 255 $\mu$ A, Codes<br>8 – 255, Rload = 2.4 k $\Omega$ , Cload =<br>15 pF                                                  | _   | ±0.9   | ±1   | LSB    |  |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Codes 8 – 255, Rload = 2.4 k $\Omega$ ,<br>Cload = 15 pF                                                | -   | ±1.2   | ±1.6 | LSB    |  |

| DNL              | Differential nonlinearity             | Sink mode, range = 255 $\mu$ A, Rload<br>= 2.4 kΩ, Cload = 15 pF                                                                             | _   | ±0.3   | ±1   | LSB    |  |

|                  |                                       | Source mode, range = 255 $\mu$ A,<br>Rload = 2.4 k $\Omega$ , Cload = 15 pF                                                                  | -   | ±0.3   | ±1   | LSB    |  |

| Ezs              | Zero scale error                      | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C                                                                                              | -   | 0      | ±1   | LSB    |  |

|                  |                                       | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C                                                                                             | -   | -      | ±2   | LSB    |  |

| Eg               | Gain error                            | Range = 2.04 mA, 25 °C                                                                                                                       | -   | -      | ±2.5 | %      |  |

|                  |                                       | Range = 255 µA, 25 ° C                                                                                                                       | -   | -      | ±2.5 | %      |  |

|                  |                                       | Range = 31.875 µA, 25 ° C                                                                                                                    | -   | -      | ±3.5 | %      |  |

| TC_Eg            | Temperature coefficient of gain error | Range = 2.04 mA                                                                                                                              | -   | -      | 0.04 | % / °C |  |

|                  |                                       | Range = 255 µA                                                                                                                               | _   | _      | 0.04 | % / °C |  |

|                  |                                       | Range = 31.875 µA                                                                                                                            | _   | -      | 0.05 | % / °C |  |

| Vcompliance      | Dropout voltage, source or sink mode  | Voltage headroom at max current,<br>Rload to Vdda or Rload to Vssa,<br>Vdiff from Vdda                                                       | 1   | -      | -    | V      |  |

| Parameter       | Description                 | Conditions                                        | Min | Тур | Max | Units |

|-----------------|-----------------------------|---------------------------------------------------|-----|-----|-----|-------|

| I <sub>DD</sub> | Operating current, code = 0 | Low speed mode, source mode, range = 31.875 µA    | -   | 44  | 100 | μA    |

|                 |                             | Low speed mode, source mode, range = 255 $\mu$ A, | -   | 33  | 100 | μA    |

|                 |                             | Low speed mode, source mode,<br>range = 2.04 mA   | -   | 33  | 100 | μA    |

|                 |                             | Low speed mode, sink mode,<br>range = 31.875 µA   | -   | 36  | 100 | μA    |

|                 |                             | 33                                                | 100 | μA  |     |       |

|                 |                             | Low speed mode, sink mode,<br>range = 2.04 mA     | -   | 33  | 100 | μA    |

|                 |                             | High speed mode, source mode, range = 31.875 μA   | -   | 310 | 500 | μA    |

|                 |                             | High speed mode, source mode, range = 255 $\mu$ A | -   | 305 | 500 | μA    |

|                 |                             | High speed mode, source mode, range = 2.04 mA     | -   | 305 | 500 | μA    |

|                 |                             | High speed mode, sink mode,<br>range = 31.875 μA  | -   | 310 | 500 | μA    |

|                 |                             | High speed mode, sink mode, range = 255 $\mu$ A   | -   | 300 | 500 | μA    |

|                 |                             | High speed mode, sink mode,<br>range = 2.04 mA    | -   | 300 | 500 | μA    |

### Table 11-28. IDAC (Current Digital-to-Analog Converter) DC Specifications (continued)

### 11.6.3 Pulse Width Modulation

### Table 11-45. PWM DC Specifications

| Parameter | Description               | Min                                            | Тур | Max | Units |    |

|-----------|---------------------------|------------------------------------------------|-----|-----|-------|----|

|           | Block current consumption | 16-bit PWM, at listed input clock<br>frequency | -   | -   | -     | μA |

|           | 3 MHz                     |                                                | -   | 15  | -     | μA |

|           | 12 MHz                    |                                                | _   | 60  | -     | μA |

|           | 50 MHz                    |                                                | -   | 260 | -     | μA |

|           | 67 MHz                    |                                                | _   | 350 | _     | μA |

### Table 11-46. Pulse Width Modulation (PWM) AC Specifications

| Parameter | Description                   | Conditions                                       | Min | Тур | Max                | Units |

|-----------|-------------------------------|--------------------------------------------------|-----|-----|--------------------|-------|

|           | Operating frequency           | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | DC  | -   | 67 <sup>[49]</sup> | MHz   |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | DC  | -   | 50                 | MHz   |

|           | Pulse width                   | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 21  | -   | -                  | ns    |

|           | Pulse width (external)        | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 30  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 42  | -   | -                  | ns    |

|           | Kill pulse width              | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 21  | -   | -                  | ns    |

|           | Kill pulse width (external)   | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 30  |     |                    | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 42  | -   | -                  | ns    |

|           | Enable pulse width            | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 21  | -   | -                  | ns    |

|           | Enable pulse width (external) | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 30  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 42  | -   | -                  | ns    |

|           | Reset pulse width             | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 15  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 21  | -   | -                  | ns    |

|           | Reset pulse width (external)  | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | 30  | -   | -                  | ns    |

|           |                               | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | 42  | -   | -                  | ns    |

49. Applicable at -40°C to 85°C; 50 MHz at -40°C to 125°C.

### 11.8 PSoC System Resources

Specifications are valid for -40°C  $\leq$  Ta  $\leq$  125°C and Tj  $\leq$  150°C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

### 11.8.1 POR with Brown Out

For brown out detect in regulated mode, Vddd and Vdda must be  $\geq$  2.0 V. Brown out detect is available in externally regulated mode. Table 11-67. Precise Power On Reset (PRES) with Brown Out DC Specifications

| Parameter | Description          | Conditions   | Min  | Тур | Max  | Units |

|-----------|----------------------|--------------|------|-----|------|-------|

| PRESR     | Rising trip voltage  | Factory trim | 1.64 | -   | 1.68 | V     |

| PRESF     | Falling trip voltage |              | 1.62 | -   | 1.66 | V     |

### Table 11-68. Precise Power On Reset (PRES) with Brown Out AC Specifications

| Parameter | Description                                   | Conditions | Min | Тур | Мах | Units |  |

|-----------|-----------------------------------------------|------------|-----|-----|-----|-------|--|

| PRES_TR   | Response time                                 |            | -   | -   | 0.5 | μs    |  |

|           | V <sub>DDD</sub> /V <sub>DDA</sub> droop rate | Sleep mode | -   | 5   | -   | V/sec |  |

### 11.8.2 Voltage Monitors

#### Table 11-69. Voltage Monitors DC Specifications

| Parameter | Description              | Conditions | Min  | Тур  | Мах  | Units |

|-----------|--------------------------|------------|------|------|------|-------|

| LVI       | Trip voltage             |            |      |      |      |       |

|           | LVI_A/D_SEL[3:0] = 0000b |            | 1.68 | 1.73 | 1.77 | V     |

|           | LVI_A/D_SEL[3:0] = 0001b |            | 1.89 | 1.95 | 2.01 | V     |

|           | LVI_A/D_SEL[3:0] = 0010b |            | 2.14 | 2.20 | 2.27 | V     |

|           | LVI_A/D_SEL[3:0] = 0011b |            | 2.38 | 2.45 | 2.53 | V     |

|           | LVI_A/D_SEL[3:0] = 0100b |            | 2.62 | 2.71 | 2.79 | V     |

|           | LVI_A/D_SEL[3:0] = 0101b |            | 2.87 | 2.95 | 3.04 | V     |

|           | LVI_A/D_SEL[3:0] = 0110b |            | 3.11 | 3.21 | 3.31 | V     |

|           | LVI_A/D_SEL[3:0] = 0111b |            | 3.35 | 3.46 | 3.56 | V     |

|           | LVI_A/D_SEL[3:0] = 1000b |            | 3.59 | 3.70 | 3.81 | V     |

|           | LVI_A/D_SEL[3:0] = 1001b |            | 3.84 | 3.95 | 4.07 | V     |

|           | LVI_A/D_SEL[3:0] = 1010b |            | 4.08 | 4.20 | 4.33 | V     |

|           | LVI_A/D_SEL[3:0] = 1011b |            | 4.32 | 4.45 | 4.59 | V     |

|           | LVI_A/D_SEL[3:0] = 1100b |            | 4.56 | 4.70 | 4.84 | V     |

|           | LVI_A/D_SEL[3:0] = 1101b |            | 4.83 | 4.98 | 5.13 | V     |

|           | LVI_A/D_SEL[3:0] = 1110b |            | 5.05 | 5.21 | 5.37 | V     |

|           | LVI_A/D_SEL[3:0] = 1111b |            | 5.30 | 5.47 | 5.63 | V     |

| HVI       | Trip voltage             |            | 5.57 | 5.75 | 5.92 | V     |

#### Table 11-70. Voltage Monitors AC Specifications

| Parameter |                               | Conditions | Min | Тур | Мах | Units |  |

|-----------|-------------------------------|------------|-----|-----|-----|-------|--|

|           | Response time <sup>[59]</sup> |            | -   | -   | 1   | μs    |  |

## 12. Ordering Information

In addition to the features listed in Table 12-1, every CY8C38 device includes: a precision on-chip voltage reference, precision oscillators, Flash, ECC, DMA, a fixed function I<sup>2</sup>C, 4 KB trace RAM, JTAG/SWD programming and debug, external memory interface, and more. In addition to these features, the flexible UDBs and Analog Subsection support a wide range of peripherals. To assist you in selecting the ideal part, PSoC Creator makes a part recommendation after you choose the components required by your application. All CY8C38 derivatives incorporate device and Flash security in user-selectable security levels; see TRM for details.

| Table 12-1. | <b>CY8C38</b> Fa | milv with | Single C  | vcle 8051 |

|-------------|------------------|-----------|-----------|-----------|

|             | 01000010         |           | olingic o |           |

|                 | Ν               | ICU        | Cor       | е           |                   | A              | hal | og         |                     |        |     |          |                      | Dig              | gital  |          |           | I/O  | [70] |       |          |                         |

|-----------------|-----------------|------------|-----------|-------------|-------------------|----------------|-----|------------|---------------------|--------|-----|----------|----------------------|------------------|--------|----------|-----------|------|------|-------|----------|-------------------------|

| Part Number     | CPU Speed (MHz) | Flash (KB) | SRAM (KB) | EEPROM (KB) | LCD Segment Drive | ADC            | DAC | Comparator | SC/CT Analog Blocks | Opamps | DFB | CapSense | UDBs <sup>[69]</sup> | 16-bit Timer/PWM | FS USB | CAN 2.0b | Total I/O | GPIO | SIO  | USBIO | Package  | JTAG ID <sup>[71]</sup> |

| 32 KB Flash     |                 |            |           |             |                   |                |     |            |                     |        |     |          |                      |                  |        |          |           |      |      |       |          |                         |

| CY8C3845PVE-173 | 50              | 32         | 4         | 1           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | ~   | ~        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-SSOP  | 0x1E0AD069              |

| CY8C3865AXA-018 | 67              | 32         | 4         | 1           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | ~   | ~        | 20                   | 4                | -      | -        | 70        | 62   | 8    | 0     | 100-TQFP | 0x1E012069              |

| CY8C3865AXA-019 | 67              | 32         | 4         | 1           | 5                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | >   | 5        | 20                   | 4                | ~      | -        | 72        | 62   | 8    | 2     | 100-TQFP | 0x1E013069              |

| CY8C3865PVA-060 | 67              | 32         | 4         | 1           | >                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | >   | 5        | 20                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-SSOP  | 0x1E03C069              |

| CY8C3865PVA-063 | 67              | 32         | 4         | 1           | >                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | 5   | 5        | 20                   | 4                | >      | -        | 31        | 25   | 4    | 2     | 48-SSOP  | 0x1E03F069              |

| 64 KB Flash     |                 |            |           |             |                   |                |     |            |                     |        |     |          |                      |                  |        |          |           |      |      |       |          |                         |

| CY8C3846AXE-175 | 50              | 64         | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | ~   | ٢        | 24                   | 4                | -      | ٢        | 70        | 62   | 8    | 0     | 100-TQFP | 0x1E0AF069              |

| CY8C3846AXE-176 | 50              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | 2   | ٢        | 24                   | 4                | ~      | ٢        | 72        | 62   | 8    | 2     | 100-TQFP | 0x1E0B0069              |

| CY8C3846PVE-174 | 50              | 64         | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | ~   | ٢        | 24                   | 4                | -      | ٢        | 29        | 25   | 4    | 0     | 48-SSOP  | 0x1E0AE069              |

| CY8C3866AXA-035 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | >   | ٢        | 24                   | 4                | I      | 2        | 70        | 62   | 8    | 0     | 100-TQFP | 0x1E023069              |

| CY8C3866AXA-038 | 67              | 64         | 8         | 2           | 2                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | 2   | ۲        | 24                   | 4                | -      | -        | 70        | 62   | 8    | 0     | 100-TQFP | 0x1E026069              |

| CY8C3866AXA-039 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | ~   | ٢        | 24                   | 4                | ~      | 1        | 72        | 62   | 8    | 2     | 100-TQFP | 0x1E027069              |

| CY8C3866AXA-040 | 67              | 64         | 8         | 2           | ~                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | ~   | ~        | 24                   | 4                | ~      | ~        | 72        | 62   | 8    | 2     | 100-TQFP | 0x1E028069              |

| CY8C3866AXA-055 | 67              | 64         | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 4      | ~   | 2        | 24                   | 4                | -      | ~        | 70        | 62   | 8    | 0     | 100-TQFP | 0x1E037069              |

| CY8C3866PVA-005 | 67              | 64         | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | >   | >        | 24                   | 4                | -      | -        | 29        | 25   | 4    | 0     | 48-SSOP  | 0x1E005069              |

| CY8C3866PVA-021 | 67              | 64         | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | ~   | ~        | 24                   | 4                | ~      | -        | 31        | 25   | 4    | 2     | 48-SSOP  | 0x1E015069              |

| CY8C3866PVA-047 | 67              | 64         | 8         | 2           | -                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | >   | 2        | 24                   | 4                | -      | ~        | 29        | 25   | 4    | 0     | 48-SSOP  | 0x1E02F069              |

| CY8C3866PVA-070 | 67              | 64         | 8         | 2           | >                 | 20-bit Del-Sig | 4   | 4          | 4                   | 2      | >   | ~        | 24                   | 4                | -      | ~        | 29        | 25   | 4    | 0     | 48-SSOP  | 0x1E046069              |

Notes

71. The JTAG ID has three major fields. The most significant nibble (left digit) is the version, followed by a 2 byte part number and a 3 nibble manufacturer ID.

<sup>69.</sup> UDBs support a wide variety of functionality including SPI, LIN, UART, timer, counter, PWM, PRS, and others. Individual functions may use a fraction of a UDB or multiple UDBs. Multiple functions can share a single UDB. See the "Example Peripherals" section on page 40 for more information on how UDBs may be used.

70. The I/O Count includes all types of digital I/O: GPIO, SIO, and the two USB I/O. See the ""I/O System and Routing" section on page 33" for details on the functionality of each of these types of I/O.

Description

Table 14-1. Acronyms Used in this Document (continued)

Acronym

| Acronym           | Description                                                  |

|-------------------|--------------------------------------------------------------|

| PHUB              | peripheral hub                                               |

| PHY               | physical layer                                               |