#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | 8051                                                                       |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 67MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, LINbus, SPI, UART/USART, USB                    |

| Peripherals                | CapSense, DMA, POR, PWM, WDT                                               |

| Number of I/O              | 25                                                                         |

| Program Memory Size        | 64KB (64K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 5.5V                                                               |

| Data Converters            | A/D 16x20b; D/A 4x8b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 48-BSSOP (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 48-SSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c3866pva-021 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Program branching instructions

#### 4.3.1 Instruction Set Summary

#### 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. Table 4-1 lists the different arithmetic instructions.

| Mnemonic       | Description                                          | Bytes | Cycles |

|----------------|------------------------------------------------------|-------|--------|

| ADD A,Rn       | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct   | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri      | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data    | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn      | Add register to accumulator with carry               | 1     | 1      |

| ADDC A, Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri     | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data   | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn      | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A, Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri     | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data   | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A          | Increment accumulator                                | 1     | 1      |

| INC Rn         | Increment register                                   | 1     | 2      |

| INC Direct     | Increment direct byte                                | 2     | 3      |

| INC @Ri        | Increment indirect RAM                               | 1     | 3      |

| DEC A          | Decrement accumulator                                | 1     | 1      |

| DEC Rn         | Decrement register                                   | 1     | 2      |

| DEC Direct     | Decrement direct byte                                | 2     | 3      |

| DEC @Ri        | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR       | Increment data pointer                               | 1     | 1      |

| MUL            | Multiply accumulator and B                           | 1     | 2      |

| DIV            | Divide accumulator by B                              | 1     | 6      |

| DAA            | Decimal adjust accumulator                           | 1     | 3      |

#### Table 4-1. Arithmetic Instructions

#### Table 4-3. Data Transfer Instructions

| Mn        | nemonic      | Description                                            | Bytes | Cycles |

|-----------|--------------|--------------------------------------------------------|-------|--------|

| MOV A,F   | ٦n           | Move register to accumulator                           | 1     | 1      |

| MOV A,E   | Direct       | Move direct byte to accumulator                        | 2     | 2      |

| MOV A,@   | @Ri          | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV A,#   | #data        | Move immediate data to accumulator                     | 2     | 2      |

| MOV Rn    | ı,A          | Move accumulator to register                           | 1     | 1      |

| MOV Rn    | ,Direct      | Move direct byte to register                           | 2     | 3      |

| MOV Rn    | i, #data     | Move immediate data to register                        | 2     | 2      |

| MOV Dir   | rect, A      | Move accumulator to direct byte                        | 2     | 2      |

| MOV Dir   | rect, Rn     | Move register to direct byte                           | 2     | 2      |

| MOV Dir   | rect, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV Dir   | rect, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV Dir   | rect, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV @F    | Ri, A        | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV @F    | Ri, Direct   | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @F    | Ri, #data    | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV DP    | PTR, #data16 | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVC A,   | @A+DPTR      | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A,   | @A + PC      | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A,(  | @Ri          | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A,   | @DPTR        | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @I   | Ri, A        | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @I   | DPTR, A      | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH Dire | rect         | Push direct byte onto stack                            | 2     | 3      |

| POP Dir   | rect         | Pop direct byte from stack                             | 2     | 2      |

| XCH A,    | Rn           | Exchange register with accumulator                     | 1     | 2      |

| XCH A,    | Direct       | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A,    | @Ri          | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A,   | @Ri          | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

## Table 4-4. Boolean Instructions

| Mnemonic   | Description             | Bytes | Cycles |

|------------|-------------------------|-------|--------|

| CLR C      | Clear carry             | 1     | 1      |

| CLR bit    | Clear direct bit        | 2     | 3      |

| SETB C     | Set carry               | 1     | 1      |

| SETB bit   | Set direct bit          | 2     | 3      |

| CPL C      | Complement carry        | 1     | 1      |

| CPL bit    | Complement direct bit   | 2     | 3      |

| ANL C, bit | AND direct bit to carry | 2     | 2      |

## 6.2.1 Power Modes

PSoC 3 devices have four different power modes, as shown in Table 6-2 and Table 6-3. The power modes allow a design to easily provide required functionality and processing power while simultaneously minimizing power consumption and maximizing battery life in low-power and portable devices.

PSoC 3 power modes, in order of decreasing power consumption are:

- Active

- Alternate Active

- Sleep

- Hibernate

#### Active is the main processing mode. Its functionality is configurable. Each power controllable subsystem is enabled or disabled by using separate power configuration template registers. In alternate active mode, fewer subsystems are enabled, reducing power. In sleep mode most resources are disabled regardless of the template settings. Sleep mode is optimized to provide timed sleep intervals and Real Time Clock functionality. The lowest power mode is hibernate, which retains register and SRAM state, but no clocks, and allows wakeup only from I/O pins. Figure 6-5 on page 31 illustrates the allowable transitions between power modes. Sleep and hibernate modes should not be entered until all VDDIO supplies are at valid voltage levels.

| Power Modes         | Description                                                                                                                                                                                                                    | <b>Entry Condition</b>                     | Wakeup Source                                           | Active Clocks         | Regulator                                                                                                                         |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Active              | Primary mode of operation, all<br>peripherals available<br>(programmable)                                                                                                                                                      | Wakeup, reset,<br>manual register<br>entry | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Alternate<br>Active | Similar to Active mode, and is<br>typically configured to have<br>fewer peripherals active to<br>reduce power. One possible<br>configuration is to use the UDBs<br>for processing, with the CPU<br>turned off                  | Manual register<br>entry                   | Any interrupt                                           | Any<br>(programmable) | All regulators available.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used.                     |

| Sleep               | All subsystems automatically disabled                                                                                                                                                                                          | Manual register<br>entry                   | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | ILO/kHzECO            | Both digital and analog<br>regulators buzzed.<br>Digital and analog<br>regulators can be disabled<br>if external regulation used. |

| Hibernate           | All subsystems automatically<br>disabled<br>Lowest power consuming mode<br>with all peripherals and internal<br>regulators disabled, except<br>hibernate regulator is enabled<br>Configuration and memory<br>contents retained | Manual register<br>entry                   | PICU                                                    |                       | Only hibernate regulator<br>active.                                                                                               |

#### Table 6-2. Power Modes

## Table 6-3. Power Modes Wakeup Time and Power Consumption

| Sleep<br>Modes      | Wakeup<br>Time | Current<br>(typ)       | Code<br>Execution | Digital<br>Resources | Analog<br>Resources | Clock Sources<br>Available | Wakeup Sources                                          | Reset<br>Sources  |

|---------------------|----------------|------------------------|-------------------|----------------------|---------------------|----------------------------|---------------------------------------------------------|-------------------|

| Active              | -              | 1.2 mA <sup>[12]</sup> | Yes               | All                  | All                 | All                        | -                                                       | All               |

| Alternate<br>Active | _              | -                      | User<br>defined   | All                  | All                 | All                        | -                                                       | All               |

| Sleep               | <15 µs         | 1 μΑ                   | No                | l <sup>2</sup> C     | Comparator          | ILO/kHzECO                 | Comparator,<br>PICU, I <sup>2</sup> C, RTC,<br>CTW, LVD | XRES, LVD,<br>WDR |

| Hibernate           | <100 µs        | 200 nA                 | No                | None                 | None                | None                       | PICU                                                    | XRES              |

Note

12. Bus clock off. Execute from cache at 6 MHz. See Table 11-2 on page 66.

## 6.4 I/O System and Routing

PSoC I/Os are extremely flexible. Every GPIO has analog and digital I/O capability. All I/Os have a large number of drive modes, which are set at POR. PSoC also provides up to four individual I/O voltage domains through the VDDIO pins.

There are two types of I/O pins on every device; those with USB provide a third type. Both GPIO and SIO provide similar digital functionality. The primary differences are their analog capability and drive strength. Devices that include USB also provide two USBIO pins that support specific USB functionality as well as limited GPIO capability.

All I/O pins are available for use as digital inputs and outputs for both the CPU and digital peripherals. In addition, all I/O pins can generate an interrupt. The flexible and advanced capabilities of the PSoC I/O, combined with any signal to any pin routability, greatly simplify circuit design and board layout. All GPIO pins can be used for analog input, CapSense<sup>[13]</sup>, and LCD segment drive, while SIO pins are used for voltages in excess of VDDA and for programmable output voltages.

- Features supported by both GPIO and SIO:

- User programmable port reset state

- Separate I/O supplies and voltages for up to four groups of I/O

- Digital peripherals use DSI to connect the pins

- □ Input or output or both for CPU and DMA

- Eight drive modes

- Every pin can be an interrupt source configured as rising edge, falling edge or both edges. If required, level sensitive interrupts are supported through the DSI

- Dedicated port interrupt vector for each port

- Slew rate controlled digital output drive mode

- Access port control and configuration registers on either port basis or pin basis

- Separate port read (PS) and write (DR) data registers to avoid read modify write errors

- □ Special functionality on a pin by pin basis

- Additional features only provided on the GPIO pins:

LCD segment drive on LCD equipped devices

- □ CapSense<sup>[13]</sup>

- Analog input and output capability

- □ Continuous 100 µA clamp current capability

- □ Standard drive strength down to 1.7 V

- Additional features only provided on SIO pins:

- Higher drive strength than GPIO

- Hot swap capability (5 V tolerance at any operating V<sub>DD</sub>)

- Programmable and regulated high input and output drive levels down to 1.2 V

- □ No analog input, CapSense, or LCD capability

- Dver voltage tolerance up to 5.5 V

- □ SIO can act as a general purpose analog comparator

- USBIO features:

- □ Full speed USB 2.0 compliant I/O

- Highest drive strength for general purpose use

- □ Input, output, or both for CPU and DMA

- □ Input, output, or both for digital peripherals

- Digital output (CMOS) drive mode

- Each pin can be an interrupt source configured as rising edge, falling edge, or both edges

<sup>13.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

#### 7.1.3 Example System Function Components

The following is a sample of the system function components available in PSoC Creator for the CY8C38 family. The exact amount of hardware resources (UDBs, DFB taps, SC/CT blocks, routing, RAM, flash) used by a component varies with the features selected in PSoC Creator for the component.

- CapSense

- LCD drive

- LCD control

- Filters

7.1.4 Designing with PSoC Creator

#### 7.1.4.1 More Than a Typical IDE

A successful design tool allows for the rapid development and deployment of both simple and complex designs. It reduces or eliminates any learning curve. It makes the integration of a new design into the production stream straightforward.

PSoC Creator is that design tool.

PSoC Creator is a full featured Integrated Development Environment (IDE) for hardware and software design. It is optimized specifically for PSoC devices and combines a modern, powerful software development platform with a sophisticated graphical design tool. This unique combination of tools makes PSoC Creator the most flexible embedded design platform available.

Graphical design entry simplifies the task of configuring a particular part. You can select the required functionality from an extensive catalog of components and place it in your design. All components are parameterized and have an editor dialog that allows you to tailor functionality to your needs.

PSoC Creator automatically configures clocks and routes the I/O to the selected pins and then generates APIs to give the application complete control over the hardware. Changing the PSoC device configuration is as simple as adding a new component, setting its parameters, and rebuilding the project.

At any stage of development you are free to change the hardware configuration and even the target processor. To retarget your application (hardware and software) to new devices, even from 8- to 32-bit families, just select the new device and rebuild.

You also have the ability to change the C compiler and evaluate an alternative. Components are designed for portability and are validated against all devices, from all families, and against all supported tool chains. Switching compilers is as easy as editing the from the project options and rebuilding the application with no errors from the generated APIs or boot code.

#### 7.1.4.2 Component Catalog

The component catalog is a repository of reusable design elements that select device functionality and customize your PSoC device. It is populated with an impressive selection of content; from simple primitives such as logic gates and device registers, through the digital timers, counters and PWMs, plus analog components such as ADC, DACs, and filters, and communication protocols, such as I<sup>2</sup>C, USB, and CAN. See Example Peripherals on page 40 for more details about available peripherals. All content is fully characterized and carefully documented in data sheets with code examples, AC/DC specifications, and user code ready APIs.

#### 7.1.4.3 Design Reuse

The symbol editor gives you the ability to develop reusable components that can significantly reduce future design time. Just draw a symbol and associate that symbol with your proven design. PSoC Creator allows for the placement of the new symbol anywhere in the component catalog along with the content provided by Cypress. You can then reuse your content as many times as you want, and in any number of projects, without ever having to revisit the details of the implementation.

#### 7.1.4.4 Software Development

Anchoring the tool is a modern, highly customizable user interface. It includes project management and integrated editors for C and assembler source code, as well the design entry tools.

Project build control leverages compiler technology from top commercial vendors such as ARM<sup>®</sup> Limited, Keil<sup>™</sup>, and CodeSourcery (GNU). Free versions of Keil C51 and GNU C Compiler (GCC) for ARM, with no restrictions on code size or end product distribution, are included with the tool distribution. Upgrading to more optimizing compilers is a snap with support for the professional Keil C51 product and ARM RealView<sup>™</sup> compiler.

#### 7.1.4.5 Nonintrusive Debugging

With JTAG (4-wire) and SWD (2-wire) debug connectivity available on all devices, the PSoC Creator debugger offers full control over the target device with minimum intrusion. Breakpoints and code execution commands are all readily available from toolbar buttons and an impressive lineup of windows—register, locals, watch, call stack, memory and peripherals—make for an unparalleled level of visibility into the system.

PSoC Creator contains all the tools necessary to complete a design, and then to maintain and extend that design for years to come. All steps of the design flow are carefully integrated and optimized for ease-of-use and to maximize productivity.

## 7.5 CAN

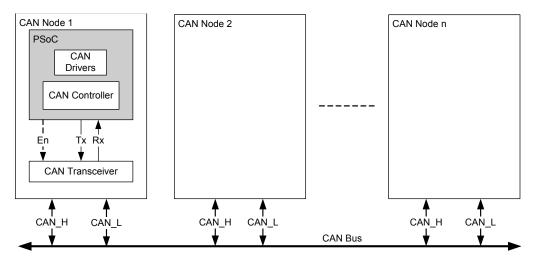

The CAN peripheral is a fully functional controller area network (CAN) supporting communication baud rates up to 1 Mbps. The CAN controller implements the CAN2.0A and CAN2.0B specifications as defined in the Bosch specification and conforms to the ISO-11898-1 standard. The CAN protocol was originally designed for automotive applications with a focus on a high level of fault detection. This ensures high communication reliability at a low cost. Because of its success in automotive applications, CAN is used as a standard communication protocol for motion oriented machine control networks (CANOpen) and factory automation applications (DeviceNet). The CAN controller features allow the efficient implementation of higher level protocols without affecting the performance of the microcontroller CPU. Full configuration support is provided in PSoC Creator.

#### Figure 7-14. CAN Bus System Implementation

#### 7.5.1 CAN Features

- CAN2.0A/B protocol implementation ISO 11898 compliant

Standard and extended frames with up to 8 bytes of data per frame

- Message filter capabilities

- □ Remote Transmission Request (RTR) support

- Programmable bit rate up to 1 Mbps

- Listen Only mode

- SW readable error counter and indicator

- Sleep mode: Wake the device from sleep with activity on the Rx pin

- Supports two or three wire interface to external transceiver (Tx, Rx, and Enable). The three-wire interface is compatible with the Philips PHY; the PHY is not included on-chip. The three wires can be routed to any I/O

- Enhanced interrupt controller

CAN receive and transmit buffers status

- CAN controller error status including BusOff

- Receive path

- □ 16 receive buffers each with its own message filter

- Enhanced hardware message filter implementation that covers the ID, IDE, and RTR

- DeviceNet addressing support

- Multiple receive buffers linkable to build a larger receive message array

- a Automatic transmission request (RTR) response handler

- Lost received message notification

- Transmit path

- Eight transmit buffers

- Programmable transmit priority

- Round robin

- Fixed priority

- Message transmissions abort capability

#### 7.5.2 Software Tools Support

- CAN Controller configuration integrated into PSoC Creator:

- CAN Configuration walkthrough with bit timing analyzer

- Receive filter setup

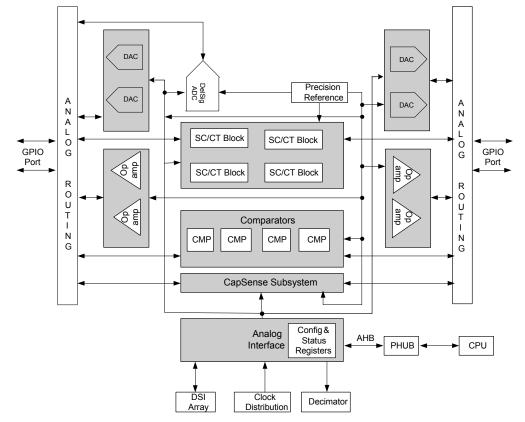

Figure 8-1. Analog Subsystem Block Diagram

The PSoC Creator software program provides a user friendly interface to configure the analog connections between the GPIO and various analog resources and connections from one analog resource to another. PSoC Creator also provides component libraries that allow you to configure the various analog blocks to perform application specific functions (PGA, transimpedance amplifier, voltage DAC, current DAC, and so on). The tool also generates API interface libraries that allow you to write firmware that allows the communication between the analog peripheral and CPU/Memory.

## 8.1 Analog Routing

The CY8C38 family of devices has a flexible analog routing architecture that provides the capability to connect GPIOs and different analog blocks, and also route signals between different analog blocks. One of the strong points of this flexible routing architecture is that it allows dynamic routing of input and output connections to the different analog blocks.

For information on how to make pin selections for optimal analog routing, refer to the application note, AN58304 - PSoC® 3 and PSoC® 5 - Pin Selection for Analog Designs.

#### 8.1.1 Features

- Flexible, configurable analog routing architecture

- 16 analog globals (AG) and two analog mux buses (AMUXBUS) to connect GPIOs and the analog blocks

- Each GPIO is connected to one analog global and one analog mux bus

- Eight analog local buses (abus) to route signals between the different analog blocks

- Multiplexers and switches for input and output selection of the analog blocks

#### 8.1.2 Functional Description

Analog globals (AGs) and analog mux buses (AMUXBUS) provide analog connectivity between GPIOs and the various analog blocks. There are 16 AGs in the CY8C38 family. The analog routing architecture is divided into four quadrants as shown in Figure 8-2. Each quadrant has four analog globals (AGL[0..3], AGL[4..7], AGR[0..3], AGR[4..7]). Each GPIO is connected to the corresponding AG through an analog switch. The analog mux bus is a shared routing resource that connects to every GPIO through an analog switch. There are two AMUXBUS routes in CY8C38, one in the left half (AMUXBUSL) and one in the right half (AMUXBUSR), as shown in Figure 8-2 on page 53.

#### Table 11-2. DC Specifications (continued)

| Parameter               | Description                                                                    | Conditions | Min | Тур  | Мах  | Units |

|-------------------------|--------------------------------------------------------------------------------|------------|-----|------|------|-------|

| ldd <sup>[24, 25]</sup> | Active Mode, VDD = 1.71 V - 5.                                                 | 5 V        |     |      |      |       |

|                         | Execute from CPU instruction<br>buffer, see Flash Program<br>Memory on page 21 |            |     |      |      |       |

|                         | CPU at 3 MHz                                                                   | T = -40 °C | -   | 1.3  | 2.9  | mA    |

|                         |                                                                                | T = 25 °C  | -   | 1.6  | 3.2  | mA    |

|                         |                                                                                | T = 85 °C  | -   | 4.8  | 7.5  | mA    |

|                         |                                                                                | T = 125 °C | -   | 4.9  | 7.7  | mA    |

|                         | CPU at 6 MHz                                                                   | T = -40 °C | -   | 2.1  | 3.7  | mA    |

|                         |                                                                                | T = 25 °C  | -   | 2.3  | 3.9  | mA    |

|                         |                                                                                | T = 85 °C  | -   | 5.6  | 8.5  | mA    |

|                         |                                                                                | T = 125 °C | -   | 5.8  | 8.7  | mA    |

|                         | CPU at 12 MHz                                                                  | T = -40 °C | -   | 3.5  | 5.2  | mA    |

|                         |                                                                                | T = 25 °C  | -   | 3.8  | 5.5  | mA    |

|                         |                                                                                | T = 85 °C  | -   | 7.1  | 9.8  | mA    |

|                         |                                                                                | T = 125 °C | -   | 9.0  | 10   | mA    |

|                         | CPU at 24 MHz                                                                  | T = -40 °C | -   | 6.3  | 8.1  | mA    |

|                         |                                                                                | T = 25 °C  | -   | 6.6  | 8.3  | mA    |

|                         |                                                                                | T = 85 °C  | -   | 10   | 13   | mA    |

|                         |                                                                                | T = 125 °C | -   | 12   | 14   | mA    |

|                         | CPU at 48 MHz                                                                  | T = -40 °C | -   | 11.5 | 13.5 | mA    |

|                         |                                                                                | T = 25 °C  | -   | 12   | 14   | mA    |

|                         |                                                                                | T = 85 °C  | -   | 15.5 | 18.5 | mA    |

|                         |                                                                                | T = 125 °C | -   | 16.5 | 19   | mA    |

|                         | CPU at 62 MHz                                                                  | T = -40 °C | -   | 16   | 18   | mA    |

|                         |                                                                                | T = 25 °C  | _   | 16   | 18   | mA    |

|                         |                                                                                | T = 85 °C  | _   | 19.5 | 23   | mA    |

|                         |                                                                                | T = 125 °C | _   | 20   | 24   | mA    |

Notes

24. The current consumption of additional peripherals that are implemented only in programmed logic blocks can be found in their respective data sheets, available in PSoC Creator, the integrated design environment. To compute total current, find CPU current at frequency of interest and add peripheral currents for your particular system from the device data sheet and component data sheets.

25. Total current for all power domains: digital (I<sub>DDD</sub>), analog (I<sub>DDA</sub>), and I/Os (I<sub>DDIO0, 1, 2, 3</sub>). All I/Os floating.

## Table 11-2. DC Specifications (continued)

| Parameter         | Description                                                       | Conditions                                             |            | Min | Тур | Max | Units |

|-------------------|-------------------------------------------------------------------|--------------------------------------------------------|------------|-----|-----|-----|-------|

|                   | Hibernate Mode <sup>[28]</sup>                                    |                                                        |            |     |     |     |       |

|                   |                                                                   | V <sub>DD</sub> = V <sub>DDIO</sub> = 4.5 V–5.5 V      | T = -40 °C | -   | 0.2 | 1.6 | μA    |

|                   |                                                                   |                                                        | T = 25 °C  | -   | 0.5 | 1.5 | μA    |

|                   |                                                                   |                                                        | T = 85 °C  | -   | 4.1 | 5.3 | μA    |

|                   |                                                                   |                                                        | T = 125 °C | -   | 6.3 | 10  | μA    |

|                   | Hibernate mode current<br>All regulators and oscillators off.     | V <sub>DD</sub> = V <sub>DDIO</sub> = 2.7 V–3.6 V      | T = -40 °C | -   | 0.2 | 1.5 | μA    |

|                   | SRAM retention<br>GPIO interrupts are active                      |                                                        | T = 25 °C  | -   | 0.2 | 1.5 | μA    |

|                   |                                                                   |                                                        | T = 85 °C  | -   | 3.2 | 4.2 | μA    |

|                   | SIO Pins in single ended input,<br>unregulated output mode        |                                                        | T = 125 °C | -   | 6   | 10  | μA    |

|                   |                                                                   | V <sub>CC</sub> = V <sub>DDIO</sub> =<br>1.71 V–1.95 V | T = -40 °C | -   | 0.2 | 1.5 | μA    |

|                   |                                                                   | 1.71 V–1.95 V                                          | T = 25 °C  | -   | 0.2 | 1.5 | μA    |

|                   |                                                                   |                                                        | T = 85 °C  | -   | 2.8 | 4.3 | μA    |

|                   |                                                                   |                                                        | T = 125 °C | -   | 5.4 | 10  | μA    |

| I <sub>DDAR</sub> | Analog current consumption while device is reset <sup>[29]</sup>  | V <sub>DDA</sub> <u>≤</u> 3.6 V                        |            | -   | 0.3 | 1   | mA    |

|                   | while device is reset <sup>[29]</sup>                             | V <sub>DDA</sub> > 3.6 V                               |            | -   | 1.4 | 3.3 | mA    |

| IDDDR             | Digital current consumption while device is reset <sup>[29]</sup> | V <sub>DDD</sub> <u>&lt;</u> 3.6 V                     |            | -   | 1.1 | 6   | mA    |

|                   | device is reset <sup>[29]</sup>                                   | V <sub>DDD</sub> > 3.6 V                               |            | -   | 0.7 | 6   | mA    |

| I <sub>IB</sub>   | Input bias current <sup>[29]</sup>                                |                                                        | T = 25 °C  | -   | 10  | -   | pА    |

Notes

28. If Vccd and Vcca are externally regulated, the voltage difference between Vccd and Vcca must be less than 50 mV.

29. Based on device characterization (not production tested). USBIO pins tied to ground (V<sub>SSD</sub>).

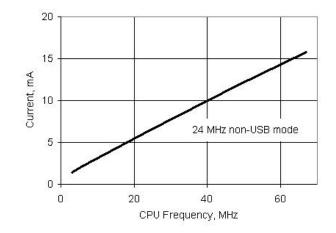

## Figure 11-1. Active Mode Current vs $F_{CPU}$ , $V_{DD}$ = 3.3 V, Temperature = 25 °C

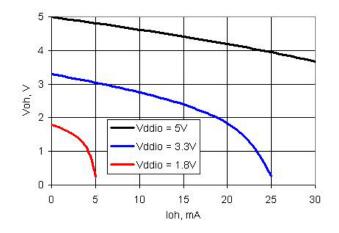

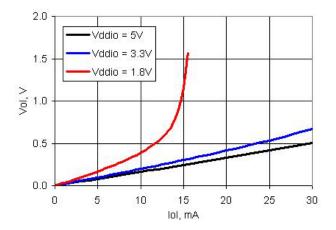

## Figure 11-6. GPIO Output High Voltage and Current

Figure 11-7. GPIO Output Low Voltage and Current

## 11.4.4 XRES

## Table 11-13. XRES DC Specifications

| Parameter | Description                                                   | Conditions                | Min                | Тур | Max                | Units |

|-----------|---------------------------------------------------------------|---------------------------|--------------------|-----|--------------------|-------|

| Vih       | Input voltage high threshold                                  | CMOS Input, PRT[x]CTL = 0 | $0.7 \times Vddio$ | -   | -                  | V     |

| Vil       | Input voltage low threshold                                   | CMOS Input, PRT[x]CTL = 0 | -                  | -   | $0.3 \times Vddio$ | V     |

| Rpullup   | Pull up resistor                                              |                           | 3.5                | 5.6 | 8.5                | kΩ    |

| Cin       | Input capacitance <sup>[30]</sup>                             |                           | -                  | 3   | -                  | pF    |

| Vh        | Input voltage hysteresis<br>(Schmitt-Trigger) <sup>[30]</sup> |                           | -                  | 100 | -                  | mV    |

| ldiode    | Current through protection diode to Vddio and Vssio           |                           | -                  | -   | 100                | μA    |

## Table 11-14. XRES AC Specifications

| Parameter | Description       | Conditions | Min | Тур | Мах | Units |

|-----------|-------------------|------------|-----|-----|-----|-------|

| Treset    | Reset pulse width |            | 1   | -   | -   | μs    |

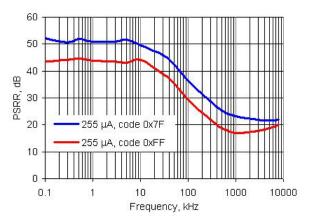

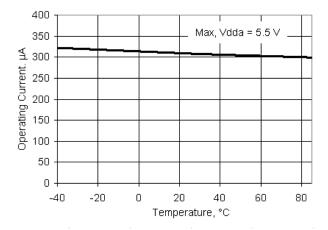

Figure 11-44. IDAC PSRR vs Frequency

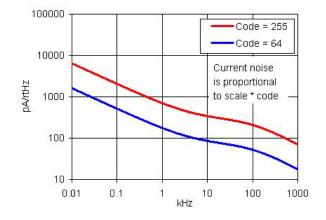

Figure 11-45. IDAC Current Noise, 255 µA Mode, Source Mode, High speed mode, Vdda = 5 V

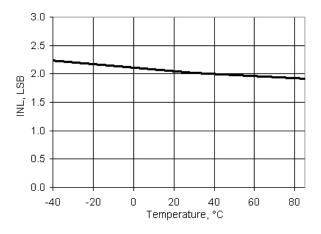

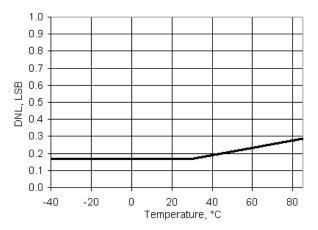

Figure 11-47. VDAC DNL vs Input Code, 1 V Mode

Figure 11-49. VDAC DNL vs Temperature, 1 V Mode

### 11.5.9 Transimpedance Amplifier

The TIA is created using a SC/CT Analog Block, see the TIA component data sheet in PSoC Creator for full AC/DC specifications, and APIs and example code.

Table 11-34. Transimpedance Amplifier (TIA) DC Specifications

| Parameter | Description                           | Conditions | Min | Тур | Max | Units |

|-----------|---------------------------------------|------------|-----|-----|-----|-------|

| Vioff     | Input offset voltage                  |            | -   | -   | 10  | mV    |

|           | Conversion resistance <sup>[46]</sup> | ·          |     |     |     |       |

|           | R = 20K                               | 40 pF load | -25 | -   | +35 | %     |

|           | R = 30K                               | 40 pF load | -25 | -   | +35 | %     |

|           | R = 40K                               | 40 pF load | -25 | -   | +35 | %     |

| Rconv     | R = 80K                               | 40 pF load | -25 | -   | +35 | %     |

|           | R = 120K                              | 40 pF load | -25 | -   | +35 | %     |

|           | R = 250K                              | 40 pF load | -25 | -   | +35 | %     |

|           | R= 500K                               | 40 pF load | -25 | -   | +35 | %     |

|           | R = 1M                                | 40 pF load | -25 | -   | +35 | %     |

|           | Quiescent current                     |            | _   | 1.1 | 2   | mA    |

#### Table 11-35. Transimpedance Amplifier (TIA) AC Specifications

| Parameter | Description             | Conditions           | Min  | Тур | Мах | Units |

|-----------|-------------------------|----------------------|------|-----|-----|-------|

| BW        | Input bandwidth (–3 dB) | R = 20K; –40 pF load | 1000 | -   | -   | kHz   |

|           |                         | R = 120K;            | 220  | -   | -   | kHz   |

|           |                         | R = 1M; –40 pF load  | 25   | -   | -   | kHz   |

<sup>46.</sup> Conversion resistance values are not calibrated. Calibrated values and details about calibration are provided in PSoC Creator component data sheets. External precision resistors can also be used.

## 11.7.2 EEPROM

#### Table 11-57. EEPROM DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Мах | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage |            | 1.71 | -   | 5.5 | V     |

#### Table 11-58. EEPROM AC Specifications

| Parameter          | Description                                                                 | Conditions                                                                  | Min | Тур | Max | Units |

|--------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-----|-----|-----|-------|

| T <sub>WRITE</sub> | Single row erase/write cycle time                                           |                                                                             | _   | 2   | 20  | ms    |

|                    | EEPROM data retention time, retention period measured from last erase cycle | Average ambient temp, T <sub>A</sub> ≤ 25 °C,<br>1M erase/program cycles    | 20  | -   | -   | years |

|                    |                                                                             | Average ambient temp, T <sub>A</sub> ≤ 55 °C,<br>100 K erase/program cycles | 20  | -   | -   |       |

|                    |                                                                             | Average ambient temp. T <sub>A</sub> ≤ 85 °C,<br>10 K erase/program cycles  | 10  | -   | -   |       |

## 11.7.3 Nonvolatile Latches (NVL)

## Table 11-59. NVL DC Specifications

| Parameter | Description               | Conditions | Min  | Тур | Мах | Units |

|-----------|---------------------------|------------|------|-----|-----|-------|

|           | Erase and program voltage | Vddd pin   | 1.71 | -   | 5.5 | V     |

#### Table 11-60. NVL AC Specifications

| Parameter | Description             | Conditions           | Min | Тур | Max | Units                       |

|-----------|-------------------------|----------------------|-----|-----|-----|-----------------------------|

|           | NVL endurance           | Programmed at 25°C   | 1K  | -   | -   | program/<br>erase<br>cycles |

|           |                         | Programmed at 0-70°C | 100 | -   | -   | program/<br>erase<br>cycles |

|           | NVL data retention time | Programmed at 55°C   | 20  | -   | -   | years                       |

|           |                         | Programmed at 0-70°C | 10  | -   | -   | years                       |

#### 11.7.4 SRAM

#### Table 11-61. SRAM DC Specifications

| Parameter | Description            | Conditions | Min | Тур | Мах | Units |

|-----------|------------------------|------------|-----|-----|-----|-------|

| Vsram     | SRAM retention voltage |            | 1.2 | -   | -   | V     |

## Table 11-62. SRAM AC Specifications

| Parameter | Description              | Conditions                                       | Min | Тур | Мах | Units |

|-----------|--------------------------|--------------------------------------------------|-----|-----|-----|-------|

| Fsram     | SRAM operating frequency | -40°C $\leq$ Ta $\leq$ 85°C and Tj $\leq$ 100°C  | DC  | -   | 67  | MHz   |

|           |                          | -40°C $\leq$ Ta $\leq$ 125°C and Tj $\leq$ 150°C | DC  | -   | 50  | MHz   |

## 14. Acronyms

## Table 14-1. Acronyms Used in this Document

| Acronym          | Description                                                                                             |

|------------------|---------------------------------------------------------------------------------------------------------|

| abus             | analog local bus                                                                                        |

| ADC              | analog-to-digital converter                                                                             |

| AG               | analog global                                                                                           |

| АНВ              | AMBA (advanced microcontroller bus archi-<br>tecture) high-performance bus, an ARM data<br>transfer bus |

| ALU              | arithmetic logic unit                                                                                   |

| AMUXBUS          | analog multiplexer bus                                                                                  |

| API              | application programming interface                                                                       |

| APSR             | application program status register                                                                     |

| ARM <sup>®</sup> | advanced RISC machine, a CPU architecture                                                               |

| ATM              | automatic thump mode                                                                                    |

| BW               | bandwidth                                                                                               |

| CAN              | Controller Area Network, a communications protocol                                                      |

| CMRR             | common-mode rejection ratio                                                                             |

| CPU              | central processing unit                                                                                 |

| CRC              | cyclic redundancy check, an error-checking protocol                                                     |

| DAC              | digital-to-analog converter, see also IDAC, VDAC                                                        |

| DFB              | digital filter block                                                                                    |

| DIO              | digital input/output, GPIO with only digital capabilities, no analog. See GPIO.                         |

| DMA              | direct memory access, see also TD                                                                       |

| DNL              | differential nonlinearity, see also INL                                                                 |

| DNU              | do not use                                                                                              |

| DR               | port write data registers                                                                               |

| DSI              | digital system interconnect                                                                             |

| DWT              | data watchpoint and trace                                                                               |

| ECC              | error correcting code                                                                                   |

| ECO              | external crystal oscillator                                                                             |

| EEPROM           | electrically erasable programmable read-only memory                                                     |

| EMI              | electromagnetic interference                                                                            |

| EMIF             | external memory interface                                                                               |

| EOC              | end of conversion                                                                                       |

| EOF              | end of frame                                                                                            |

| EPSR             | execution program status register                                                                       |

| ESD              | electrostatic discharge                                                                                 |

| ETM              | embedded trace macrocell                                                                                |

## Table 14-1. Acronyms Used in this Document (continued)

| Acronym                  | Description                                            |

|--------------------------|--------------------------------------------------------|

| FIR                      | finite impulse response, see also IIR                  |

| FPB                      | flash patch and breakpoint                             |

| FS                       | full-speed                                             |

| GPIO                     | general-purpose input/output, applies to a PSoC pin    |

| HVI                      | high-voltage interrupt, see also LVI, LVD              |

| IC                       | integrated circuit                                     |

| IDAC                     | current DAC, see also DAC, VDAC                        |

| IDE                      | integrated development environment                     |

| I <sup>2</sup> C, or IIC | Inter-Integrated Circuit, a communications protocol    |

| lir                      | infinite impulse response, see also FIR                |

| ILO                      | internal low-speed oscillator, see also IMO            |

| IMO                      | internal main oscillator, see also ILO                 |

| INL                      | integral nonlinearity, see also DNL                    |

| I/O                      | input/output, see also GPIO, DIO, SIO, USBIO           |

| IPOR                     | initial power-on reset                                 |

| IPSR                     | interrupt program status register                      |

| IRQ                      | interrupt request                                      |

| ITM                      | instrumentation trace macrocell                        |

| LCD                      | liquid crystal display                                 |

| LIN                      | Local Interconnect Network, a communications protocol. |

| LR                       | link register                                          |

| LUT                      | lookup table                                           |

| LVD                      | low-voltage detect, see also LVI                       |

| LVI                      | low-voltage interrupt, see also HVI                    |

| LVTTL                    | low-voltage transistor-transistor logic                |

| MAC                      | multiply-accumulate                                    |

| MCU                      | microcontroller unit                                   |

| MISO                     | master-in slave-out                                    |

| NC                       | no connect                                             |

| NMI                      | nonmaskable interrupt                                  |

| NRZ                      | non-return-to-zero                                     |

| NVIC                     | nested vectored interrupt controller                   |

| NVL                      | nonvolatile latch, see also WOL                        |

| opamp                    | operational amplifier                                  |

| PAL                      | programmable array logic, see also PLD                 |

| PC                       | program counter                                        |

| РСВ                      | printed circuit board                                  |

| PGA                      | programmable gain amplifier                            |

## **16. Document Conventions**

## 16.1 Units of Measure

## Table 16-1. Units of Measure

| Symbol | Unit of Measure        |

|--------|------------------------|

| °C     | degree Celsius         |

| dB     | decibels               |

| fF     | femtofarads            |

| Hz     | hertz                  |

| KB     | 1024 bytes             |

| kbps   | kilobits per second    |

| Khr    | kilohours              |

| kHz    | kilohertz              |

| kΩ     | kilohms                |

| ksps   | kilosamples per second |

| LSB    | least significant bit  |

| Mbps   | megabits per second    |

| MHz    | megahertz              |

| MΩ     | megaohms               |

| Msps   | megasamples per second |

| μA     | microamperes           |

| μF     | microfarads            |

| μH     | microhenrys            |

| μs     | microseconds           |

| μV     | microvolts             |

| μW     | microwatts             |

| mA     | milliamperes           |

| ms     | milliseconds           |

| mV     | millivolts             |

| nA     | nanoamperes            |

| ns     | nanoseconds            |

| nV     | nanovolts              |

| Ω      | ohms                   |

| pF     | picofarads             |

| ppm    | parts per million      |

| ps     | picoseconds            |

| S      | seconds                |

| sps    | samples per second     |

| sqrtHz | square root of hertz   |

| V      | volts                  |

# 17. Revision History (continued)

| Rev.<br>*H (cont.) 4 | ECN<br>4094193 | Submission<br>Date<br>08/30/2013 | Orig. of<br>Change<br>NFB /<br>ANMD | Description of Change           Updated Electrical Specifications:           Updated Device Level Specifications:           Updated Table 11-2.           Updated Table 11-3.           Updated Inputs and Outputs:           Updated GPIO:           Updated Table 11-7.           Removed figure "GPIO Output Rise and Fall Times, Fast Strong Mode,           V <sub>DDIO</sub> = 3.3 V, 25 pF Load" and figure "GPIO Output Rise and Fall Times, Slow Strong Mode, V <sub>DDIO</sub> = 3.3 V, 25 pF Load".           Updated Analog Peripherals:           Updated Delta-Sigma ADC:           Updated Table 11-17. |

|----------------------|----------------|----------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *H (cont.) 4         | 4094193        | 08/30/2013                       |                                     | Updated Device Level Specifications:<br>Updated Table 11-2.<br>Updated Table 11-3.<br>Updated Inputs and Outputs:<br>Updated GPIO:<br>Updated Table 11-7.<br>Removed figure "GPIO Output Rise and Fall Times, Fast Strong Mode,<br>V <sub>DDIO</sub> = 3.3 V, 25 pF Load" and figure "GPIO Output Rise and Fall Times, Slow<br>Strong Mode, V <sub>DDIO</sub> = 3.3 V, 25 pF Load".<br>Updated Analog Peripherals:<br>Updated Delta-Sigma ADC:                                                                                                                                                                         |

|                      |                |                                  |                                     | Updated Table 11-18.<br>Updated Voltage Reference:<br>Updated Table 11-24.<br>Updated IDAC:<br>Updated Table 11-28.<br>Updated Memory:<br>Updated Flash:<br>Updated Table 11-56.<br>Updated Clocking:<br>Updated Internal Main Oscillator:<br>Updated Internal Main Oscillator:<br>Updated Table 11-76.<br>Updated Packaging:<br>spec 51-85048 – Changed revision from *G to *H.<br>Updated in new template.<br>Completing Sunset Review.                                                                                                                                                                              |

| *1 4                 | 4174912        | 10/26/2013                       | NFB /<br>ANMD                       | Updated Pinouts:<br>Added Note 8 and referred the same note in 100 mA in description.<br>Updated Electrical Specifications:<br>Updated Absolute Maximum Ratings:<br>Updated Table 11-1.<br>Added Note 18 and referred the same note in Table 11-1.<br>Added Note 20 and referred the same note in Ivddio parameter in Table 11-1<br>Updated Device Level Specifications:<br>Updated Table 11-2.<br>Updated Analog Peripherals:<br>Updated Opamp:<br>Updated Table 11-15.<br>Updated Voltage Reference:<br>Updated Table 11-24.<br>Updated Packaging:                                                                   |

| *J 4                 | 4188568        | 11/14/2013                       | WKA                                 | Updated Table 13-1.<br>No content update.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |