Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | AVR                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 16MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 32                                                                      |

| Program Memory Size        | 16KB (8K x 16)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 512 x 8                                                                 |

| RAM Size                   | 1K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                             |

| Data Converters            | A/D 8x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 44-VFQFN Exposed Pad                                                    |

| Supplier Device Package    | 44-VQFN (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atmega16a-mur |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2 Pin Descriptions

# 2.2.1 VCC

Digital supply voltage.

# 2.2.2 GND

Ground.

# 2.2.3 Port A (PA7:PA0)

Port A serves as the analog inputs to the A/D Converter.

Port A also serves as an 8-bit bi-directional I/O port, if the A/D Converter is not used. Port pins can provide internal pull-up resistors (selected for each bit). The Port A output buffers have symmetrical drive characteristics with both high sink and source capability. When pins PA0 to PA7 are used as inputs and are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

# 2.2.4 Port B (PB7:PB0)

Port B is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port B output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tristated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16A as listed on page 57.

# 2.2.5 Port C (PC7:PC0)

Port C is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port C output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port C pins that are externally pulled low will source current if the pull-up resistors are activated. The Port C pins are tristated when a reset condition becomes active, even if the clock is not running. If the JTAG interface is enabled, the pull-up resistors on pins PC5(TDI), PC3(TMS) and PC2(TCK) will be activated even if a reset occurs.

Port C also serves the functions of the JTAG interface and other special features of the ATmega16A as listed on page 59.

# 2.2.6 Port D (PD7:PD0)

Port D is an 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). The Port D output buffers have symmetrical drive characteristics with both high sink and source capability. As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port D also serves the functions of various special features of the ATmega16A as listed on page 62.

# 2.2.7 **RESET**

Reset Input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 27-2 on page 282. Shorter pulses are not guaranteed to generate a reset.

# 2.2.8 XTAL1

Input to the inverting Oscillator amplifier and input to the internal clock operating circuit.

| Table 8-4. | Start-up Times for the Crystal Oscillator Clock Selection (Continued) |

|------------|-----------------------------------------------------------------------|

|------------|-----------------------------------------------------------------------|

| CKSEL0 | SUT1:0 | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | Recommended Usage                          |

|--------|--------|----------------------------------------------------|------------------------------------------------------------|--------------------------------------------|

| 1      | 01     | 16K CK                                             | _                                                          | Crystal Oscillator, BOD<br>enabled         |

| 1      | 10     | 16K CK                                             | 4.1ms                                                      | Crystal Oscillator, fast rising power      |

| 1      | 11     | 16K CK                                             | 65ms                                                       | Crystal Oscillator, slowly<br>rising power |

Notes: 1. These options should only be used when not operating close to the maximum frequency of the device, and only if frequency stability at start-up is not important for the application. These options are not suitable for crystals.

2. These options are intended for use with ceramic resonators and will ensure frequency stability at start-up. They can also be used with crystals when not operating close to the maximum frequency of the device, and if frequency stability at start-up is not important for the application.

# 8.5 Low-frequency Crystal Oscillator

To use a 32.768kHz watch crystal as the clock source for the device, the Low-frequency Crystal Oscillator must be selected by setting the CKSEL Fuses to "1001". The crystal should be connected as shown in Figure 8-2. By programming the CKOPT Fuse, the user can enable internal capacitors on XTAL1 and XTAL2, thereby removing the need for external capacitors. The internal capacitors have a nominal value of 36pF.

When this Oscillator is selected, start-up times are determined by the SUT Fuses as shown in Table 8-5.

| SUT1:0 | Start-up Time from<br>Power-down and<br>Power-save | Additional Delay<br>from Reset<br>(V <sub>CC</sub> = 5.0V) | Recommended Usage                |

|--------|----------------------------------------------------|------------------------------------------------------------|----------------------------------|

| 00     | 1K CK <sup>(1)</sup>                               | 4.1ms                                                      | Fast rising power or BOD enabled |

| 01     | 1K CK <sup>(1)</sup>                               | 65ms                                                       | Slowly rising power              |

| 10     | 32K CK                                             | 65ms                                                       | Stable frequency at start-up     |

| 11     |                                                    | Reserve                                                    | d                                |

Table 8-5.

Start-up Times for the Low-frequency Crystal Oscillator Clock Selection

Note: 1. These options should only be used if frequency stability at start-up is not important for the application.

# 8.6 External RC Oscillator

For timing insensitive applications, the external RC configuration shown in Figure 8-3 can be used. The frequency is roughly estimated by the equation f = 1/(3RC). C should be at least 22pF. By programming the CKOPT Fuse, the user can enable an internal 36pF capacitor between XTAL1 and GND, thereby removing the need for an external capacitor. For more information on Oscillator operation and details on how to choose R and C, refer to the External RC Oscillator application note.

# 9.10 Register Description

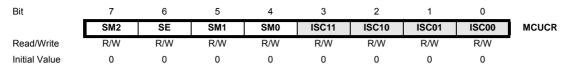

# 9.10.1 MCUCR – MCU Control Register

The MCU Control Register contains control bits for power management.

### • Bits 7, 5, 4 – SM2:0: Sleep Mode Select Bits 2, 1, and 0

These bits select between the six available sleep modes as shown in Table 9-2.

| Table 3-2. | Sleep Mode Se | HECI |                                 |

|------------|---------------|------|---------------------------------|

| SM2        | SM1           | SM0  | Sleep Mode                      |

| 0          | 0             | 0    | Idle                            |

| 0          | 0             | 1    | ADC Noise Reduction             |

| 0          | 1             | 0    | Power-down                      |

| 0          | 1             | 1    | Power-save                      |

| 1          | 0             | 0    | Reserved                        |

| 1          | 0             | 1    | Reserved                        |

| 1          | 1             | 0    | Standby <sup>(1)</sup>          |

| 1          | 1             | 1    | Extended Standby <sup>(1)</sup> |

#### Table 9-2. Sleep Mode Select

Note: 1. Standby mode and Extended Standby mode are only available with external crystals or resonators.

#### • Bit 6 – SE: Sleep Enable

The SE bit must be written to logic one to make the MCU enter the sleep mode when the SLEEP instruction is executed. To avoid the MCU entering the sleep mode unless it is the programmers purpose, it is recommended to write the Sleep Enable (SE) bit to one just before the execution of the SLEEP instruction and to clear it immediately after waking up.

```

Assembly Code Example

```

```

WDT_off:

; Reset WDT

WDR

; Write logical one to WDTOE and WDE

in r16, WDTCR

ori r16, (1<<WDE)|(1<<WDE)

out WDTCR, r16

; Turn off WDT

ldi r16, (0<<WDE)

out WDTCR, r16

ret

```

C Code Example void WDT\_off(void)

}

{

```

/* Reset WDT*/

_WDR();

/* Write logical one to WDTOE and WDE */

WDTCR |= (1<<WDTOE) | (1<<WDE);

/* Turn off WDT */

WDTCR = 0x00;</pre>

```

# 12.3.4 Alternate Functions of Port D

The Port D pins with alternate functions are shown in Table 12-12.

| Port Pin | Alternate Function                                  |

|----------|-----------------------------------------------------|

| PD7      | OC2 (Timer/Counter2 Output Compare Match Output)    |

| PD6      | ICP1 (Timer/Counter1 Input Capture Pin)             |

| PD5      | OC1A (Timer/Counter1 Output Compare A Match Output) |

| PD4      | OC1B (Timer/Counter1 Output Compare B Match Output) |

| PD3      | INT1 (External Interrupt 1 Input)                   |

| PD2      | INT0 (External Interrupt 0 Input)                   |

| PD1      | TXD (USART Output Pin)                              |

| PD0      | RXD (USART Input Pin)                               |

Table 12-12.

Port D Pins Alternate Functions

The alternate pin configuration is as follows:

# • OC2 - Port D, Bit 7

OC2, Timer/Counter2 Output Compare Match output: The PD7 pin can serve as an external output for the Timer/Counter2 Output Compare. The pin has to be configured as an output (DDD7 set (one)) to serve this function. The OC2 pin is also the output pin for the PWM mode timer function.

# • ICP1 – Port D, Bit 6

ICP1 – Input Capture Pin: The PD6 pin can act as an Input Capture pin for Timer/Counter1.

# • OC1A - Port D, Bit 5

OC1A, Output Compare Match A output: The PD5 pin can serve as an external output for the Timer/Counter1 Output Compare A. The pin has to be configured as an output (DDD5 set (one)) to serve this function. The OC1A pin is also the output pin for the PWM mode timer function.

# • OC1B - Port D, Bit 4

OC1B, Output Compare Match B output: The PD4 pin can serve as an external output for the Timer/Counter1 Output Compare B. The pin has to be configured as an output (DDD4 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

# • INT1 - Port D, Bit 3

INT1, External Interrupt Source 1: The PD3 pin can serve as an external interrupt source.

# • INT0 - Port D, Bit 2

INTO, External Interrupt Source 0: The PD2 pin can serve as an external interrupt source.

# • TXD - Port D, Bit 1

TXD, Transmit Data (Data output pin for the USART). When the USART Transmitter is enabled, this pin is configured as an output regardless of the value of DDD1.

maximum 8-bit value (TOP = 0xFF) and then restarts from the bottom (0x00). In normal operation the Timer/Counter Overflow Flag (TOV0) will be set in the same timer clock cycle as the TCNT0 becomes zero. The TOV0 Flag in this case behaves like a ninth bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt that automatically clears the TOV0 Flag, the timer resolution can be increased by software. There are no special cases to consider in the normal mode, a new counter value can be written anytime.

The output compare unit can be used to generate interrupts at some given time. Using the output compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time.

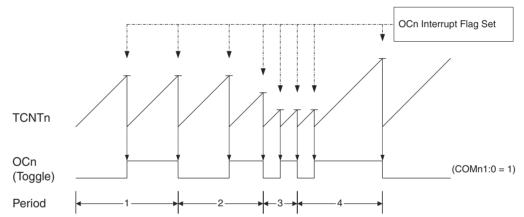

# 14.7.2 Clear Timer on Compare Match (CTC) Mode

In Clear Timer on Compare or CTC mode (WGM01:0 = 2), the OCR0 Register is used to manipulate the counter resolution. In CTC mode the counter is cleared to zero when the counter value (TCNT0) matches the OCR0. The OCR0 defines the top value for the counter, hence also its resolution. This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events.

The timing diagram for the CTC mode is shown in Figure 14-5. The counter value (TCNT0) increases until a compare match occurs between TCNT0 and OCR0, and then counter (TCNT0) is cleared.

### Figure 14-5. CTC Mode, Timing Diagram

An interrupt can be generated each time the counter value reaches the TOP value by using the OCF0 Flag. If the interrupt is enabled, the interrupt handler routine can be used for updating the TOP value. However, changing TOP to a value close to BOTTOM when the counter is running with none or a low prescaler value must be done with care since the CTC mode does not have the double buffering feature. If the new value written to OCR0 is lower than the current value of TCNT0, the counter will miss the compare match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the compare match can occur.

For generating a waveform output in CTC mode, the OC0 output can be set to toggle its logical level on each compare match by setting the Compare Output mode bits to toggle mode (COM01:0 = 1). The OC0 value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC0} = f_{clk\_l/O}/2$  when OCR0 is set to zero (0x00). The waveform frequency is defined by the following equation:

$$f_{OCn} = \frac{f_{\mathsf{clk\_l/O}}}{2 \cdot N \cdot (1 + OCRn)}$$

The N variable represents the prescale factor (1, 8, 64, 256, or 1024).

As for the Normal mode of operation, the TOV0 Flag is set in the same timer clock cycle that the counter counts from MAX to 0x00.

# Atmel

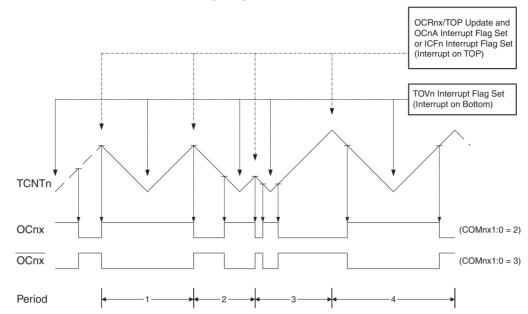

The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x Interrupt Flag will be set when a compare match occurs.

#### Figure 16-8. Phase Correct PWM Mode, Timing Diagram

The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches BOTTOM. When either OCR1A or ICR1 is used for defining the TOP value, the OC1A or ICF1 Flag is set accordingly at the same timer clock cycle as the OCR1x Registers are updated with the double buffer value (at TOP). The Interrupt Flags can be used to generate an interrupt each time the counter reaches the TOP or BOTTOM value.

When changing the TOP value the program must ensure that the new TOP value is higher or equal to the value of all of the Compare Registers. If the TOP value is lower than any of the Compare Registers, a compare match will never occur between the TCNT1 and the OCR1x. Note that when using fixed TOP values, the unused bits are masked to zero when any of the OCR1x Registers are written. As the third period shown in Figure 16-8 illustrates, changing the TOP actively while the Timer/Counter is running in the phase correct mode can result in an unsymmetrical output. The reason for this can be found in the time of update of the OCR1x Register. Since the OCR1x update occurs at TOP, the PWM period starts and ends at TOP. This implies that the length of the falling slope is determined by the previous TOP value, while the length of the rising slope is determined by the new TOP value. When these two values differ the two slopes of the period will differ in length. The difference in length gives the unsymmetrical result on the output.

It is recommended to use the phase and frequency correct mode instead of the phase correct mode when changing the TOP value while the Timer/Counter is running. When using a static TOP value there are practically no differences between the two modes of operation.

In phase correct PWM mode, the compare units allow generation of PWM waveforms on the OC1x pins. Setting the COM1x1:0 bits to 2 will produce a non-inverted PWM and an inverted PWM output can be generated by setting the COM1x1:0 to 3 (See Table 16-2 on page 105). The actual OC1x value will only be visible on the port pin if the data direction for the port pin is set as output (DDR\_OC1x). The PWM waveform is generated by setting (or clearing) the OC1x Register at the compare match between OCR1x and TCNT1 when the counter increments, and clearing (or setting) the OC1x Register at compare match between OCR1x and TCNT1 when

A frequency (with 50% duty cycle) waveform output in fast PWM mode can be achieved by setting OC2 to toggle its logical level on each compare match (COM21:0 = 1). The waveform generated will have a maximum frequency of  $f_{oc2} = f_{clk\_l/O}/2$  when OCR2 is set to zero. This feature is similar to the OC2 toggle in CTC mode, except the double buffer feature of the output compare unit is enabled in the fast PWM mode.

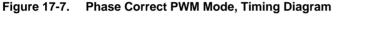

# 17.7.4 Phase Correct PWM Mode

The phase correct PWM mode (WGM21:0 = 1) provides a high resolution phase correct PWM waveform generation option. The phase correct PWM mode is based on a dual-slope operation. The counter counts repeatedly from BOTTOM to MAX and then from MAX to BOTTOM. In non-inverting Compare Output mode, the Output Compare (OC2) is cleared on the compare match between TCNT2 and OCR2 while upcounting, and set on the compare match while downcounting. In inverting Output Compare mode, the operation is inverted. The dual-slope operation has lower maximum operation frequency than single slope operation. However, due to the symmetric feature of the dual-slope PWM modes, these modes are preferred for motor control applications.

The PWM resolution for the phase correct PWM mode is fixed to 8 bits. In phase correct PWM mode the counter is incremented until the counter value matches MAX. When the counter reaches MAX, it changes the count direction. The TCNT2 value will be equal to MAX for one timer clock cycle. The timing diagram for the phase correct PWM mode is shown on Figure 17-7. The TCNT2 value is in the timing diagram shown as a histogram for illustrating the dual-slope operation. The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT2 slopes represent compare matches between OCR2 and TCNT2.

The Timer/Counter Overflow Flag (TOV2) is set each time the counter reaches BOTTOM. The Interrupt Flag can be used to generate an interrupt each time the counter reaches the BOTTOM value.

In phase correct PWM mode, the compare unit allows generation of PWM waveforms on the OC2 pin. Setting the COM21:0 bits to 2 will produce a non-inverted PWM. An inverted PWM output can be generated by setting the COM21:0 to 3 (see Table 17-5 on page 126). The actual OC2 value will only be visible on the port pin if the data direction for the port pin is set as output. The PWM waveform is generated by clearing (or setting) the OC2 Register at the compare match between OCR2 and TCNT2 when the counter increments, and setting (or

# 19.7.7 Flushing the Receive Buffer

The receiver buffer FIFO will be flushed when the Receiver is disabled, i.e., the buffer will be emptied of its contents. Unread data will be lost. If the buffer has to be flushed during normal operation, due to for instance an error condition, read the UDR I/O location until the RXC Flag is cleared. The following code example shows how to flush the receive buffer.

| Assembly Code Example <sup>(1)</sup> |                                            |

|--------------------------------------|--------------------------------------------|

| USART_Flush:                         |                                            |

| sbis                                 | UCSRA, RXC                                 |

| ret                                  |                                            |

| in                                   | r16, UDR                                   |

| rjmp                                 | USART_Flush                                |

| C Code Example <sup>(1)</sup>        |                                            |

| void USART_Flush( void               | )                                          |

| {                                    |                                            |

| <b>unsigned char</b> du              | ummy;                                      |

| while ( UCSRA &                      | (1< <rxc) )="" dummy="UDR;&lt;/td"></rxc)> |

| }                                    |                                            |

Note: 1. See "About Code Examples" on page 7.

# 19.8 Asynchronous Data Reception

The USART includes a clock recovery and a data recovery unit for handling asynchronous data reception. The clock recovery logic is used for synchronizing the internally generated baud rate clock to the incoming asynchronous serial frames at the RxD pin. The data recovery logic samples and low pass filters each incoming bit, thereby improving the noise immunity of the receiver. The asynchronous reception operational range depends on the accuracy of the internal baud rate clock, the rate of the incoming frames, and the frame size in number of bits.

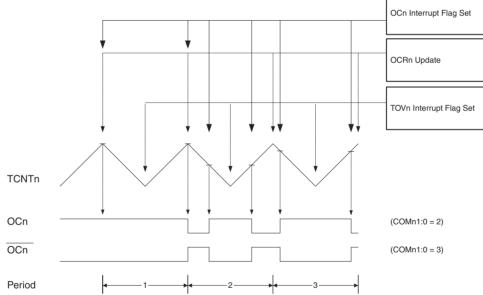

# 19.8.1 Asynchronous Clock Recovery

The clock recovery logic synchronizes internal clock to the incoming serial frames. Figure 19-5 illustrates the sampling process of the start bit of an incoming frame. The sample rate is 16 times the baud rate for Normal mode, and 8 times the baud rate for Double Speed mode. The horizontal arrows illustrate the synchronization variation due to the sampling process. Note the larger time variation when using the double speed mode (U2X = 1) of operation. Samples denoted zero are samples done when the RxD line is idle (i.e., no communication activity).

#### Figure 19-5. Start Bit Sampling

When the clock recovery logic detects a high (idle) to low (start) transition on the RxD line, the start bit detection sequence is initiated. Let sample 1 denote the first zero-sample as shown in the figure. The clock recovery logic then uses samples 8, 9, and 10 for Normal mode, and samples 4, 5, and 6 for Double Speed mode (indicated with sample numbers inside boxes on the figure), to decide if a valid start bit is received. If two or more of these three samples have logical high levels (the majority wins), the start bit is rejected as a noise spike and the

# • Bit 6 – TWEA: TWI Enable Acknowledge Bit

The TWEA bit controls the generation of the acknowledge pulse. If the TWEA bit is written to one, the ACK pulse is generated on the TWI bus if the following conditions are met:

- 1. The device's own Slave address has been received.

- 2. A general call has been received, while the TWGCE bit in the TWAR is set.

- 3. A data byte has been received in Master Receiver or Slave Receiver mode.

By writing the TWEA bit to zero, the device can be virtually disconnected from the Two-wire Serial Bus temporarily. Address recognition can then be resumed by writing the TWEA bit to one again.

# • Bit 5 – TWSTA: TWI START Condition Bit

The application writes the TWSTA bit to one when it desires to become a Master on the Two-wire Serial Bus. The TWI hardware checks if the bus is available, and generates a START condition on the bus if it is free. However, if the bus is not free, the TWI waits until a STOP condition is detected, and then generates a new START condition to claim the bus Master status. TWSTA must be cleared by software when the START condition has been transmitted.

# • Bit 4 – TWSTO: TWI STOP Condition Bit

Writing the TWSTO bit to one in Master mode will generate a STOP condition on the Two-wire Serial Bus. When the STOP condition is executed on the bus, the TWSTO bit is cleared automatically. In Slave mode, setting the TWSTO bit can be used to recover from an error condition. This will not generate a STOP condition, but the TWI returns to a well-defined unaddressed Slave mode and releases the SCL and SDA lines to a high impedance state.

# • Bit 3 – TWWC: TWI Write Collision Flag

The TWWC bit is set when attempting to write to the TWI Data Register – TWDR when TWINT is low. This flag is cleared by writing the TWDR Register when TWINT is high.

# • Bit 2 – TWEN: TWI Enable Bit

The TWEN bit enables TWI operation and activates the TWI interface. When TWEN is written to one, the TWI takes control over the I/O pins connected to the SCL and SDA pins, enabling the slew-rate limiters and spike filters. If this bit is written to zero, the TWI is switched off and all TWI transmissions are terminated, regardless of any ongoing operation.

# • Bit 1 - Res: Reserved Bit

This bit is a reserved bit and will always read as zero.

# • Bit 0 – TWIE: TWI Interrupt Enable

When this bit is written to one, and the I-bit in SREG is set, the TWI interrupt request will be activated for as long as the TWINT Flag is high.

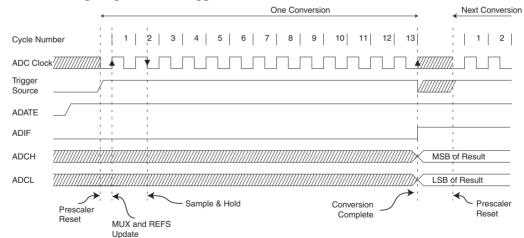

| Table 1. | Ana | alog Compara | ator Multiplexed | Input | (Continued) |

|----------|-----|--------------|------------------|-------|-------------|

|          |     |              |                  |       |             |

|          |     |              |                  |       |             |

| ACME | ADEN | MUX2:0 | Analog Comparator Negative Input |

|------|------|--------|----------------------------------|

| 1    | 0    | 100    | ADC4                             |

| 1    | 0    | 101    | ADC5                             |

| 1    | 0    | 110    | ADC6                             |

| 1    | 0    | 111    | ADC7                             |

# 21.2 Register Description

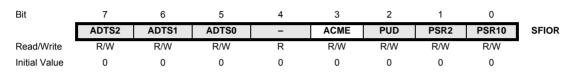

# 21.2.1 SFIOR – Special Function IO Register

# • Bit 3 – ACME: Analog Comparator Multiplexer Enable

When this bit is written logic one and the ADC is switched off (ADEN in ADCSRA is zero), the ADC multiplexer selects the negative input to the Analog Comparator. When this bit is written logic zero, AIN1 is applied to the negative input of the Analog Comparator. For a detailed description of this bit, see "Analog Comparator Multiplexed Input" on page 193.

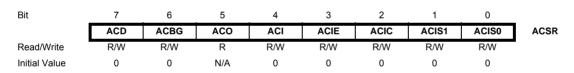

# 21.2.2 ACSR – Analog Comparator Control and Status Register

# • Bit 7 – ACD: Analog Comparator Disable

When this bit is written logic one, the power to the Analog Comparator is switched off. This bit can be set at any time to turn off the Analog Comparator. This will reduce power consumption in active and Idle mode. When changing the ACD bit, the Analog Comparator Interrupt must be disabled by clearing the ACIE bit in ACSR. Otherwise an interrupt can occur when the bit is changed.

# • Bit 6 – ACBG: Analog Comparator Bandgap Select

When this bit is set, a fixed bandgap reference voltage replaces the positive input to the Analog Comparator. When this bit is cleared, AIN0 is applied to the positive input of the Analog Comparator. See "Internal Voltage Reference" on page 39.

# • Bit 5 – ACO: Analog Comparator Output

The output of the Analog Comparator is synchronized and then directly connected to ACO. The synchronization introduces a delay of 1 - 2 clock cycles.

# • Bit 4 – ACI: Analog Comparator Interrupt Flag

This bit is set by hardware when a comparator output event triggers the interrupt mode defined by ACIS1 and ACIS0. The Analog Comparator Interrupt routine is executed if the ACIE bit is set and the I-bit in SREG is set. ACI is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ACI is cleared by writing a logic one to the flag.

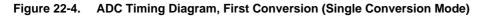

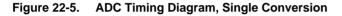

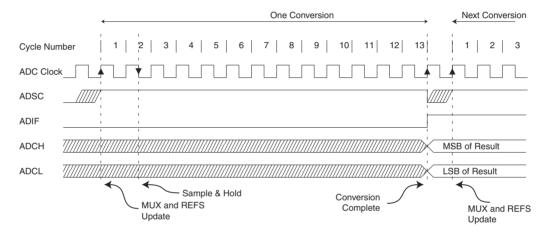

Figure 22-6. ADC Timing Diagram, Auto Triggered Conversion

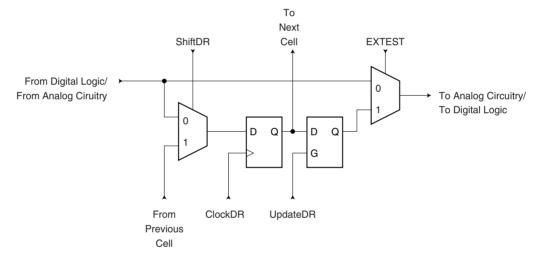

### Figure 24-9. General Boundary-scan Cell used for Signals for Comparator and ADC

### • Bit 2 – PGWRT: Page Write

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles executes Page Write, with the data stored in the temporary buffer. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGWRT bit will auto-clear upon completion of a page write, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire page write operation if the NRWW section is addressed.

### • Bit 1 – PGERS: Page Erase

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles executes Page Erase. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon completion of a page erase, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire page write operation if the NRWW section is addressed.

# • Bit 0 – SPMEN: Store Program Memory Enable

This bit enables the SPM instruction for the next four clock cycles. If written to one together with either RWWSRE, BLBSET, PGWRT' or PGERS, the following SPM instruction will have a special meaning, see description above. If only SPMEN is written, the following SPM instruction will store the value in R1:R0 in the temporary page buffer addressed by the Z-pointer. The LSB of the Z-pointer is ignored. The SPMEN bit will auto-clear upon completion of an SPM instruction, or if no SPM instruction is executed within four clock cycles. During page erase and page write, the SPMEN bit remains high until the operation is completed.

Writing any other combination than "10001", "01001", "00101", "00011" or "00001" in the lower five bits will have no effect.

# 25.7 Addressing the Flash during Self-Programming

| Bit      | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| ZH (R31) | Z15 | Z14 | Z13 | Z12 | Z11 | Z10 | Z9 | Z8 |

| ZL (R30) | Z7  | Z6  | Z5  | Z4  | Z3  | Z2  | Z1 | Z0 |

|          | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

The Z-pointer is used to address the SPM commands.

Since the Flash is organized in pages (see Table 26-5 on page 254), the Program Counter can be treated as having two different sections. One section, consisting of the least significant bits, is addressing the words within a page, while the most significant bits are addressing the pages. This is shown in Figure 25-3. Note that the Page Erase and Page Write operations are addressed independently. Therefore it is of major importance that the Boot Loader software addresses the same page in both the Page Erase and Page Write operation. Once a programming operation is initiated, the address is latched and the Z-pointer can be used for other operations.

The only SPM operation that does not use the Z-pointer is Setting the Boot Loader Lock bits. The content of the Z-pointer is ignored and will have no effect on the operation. The LPM instruction does also use the Z pointer to store the address. Since this instruction addresses the Flash byte by byte, also the LSB (bit Z0) of the Z-pointer is used.

# $T_A = -40^{\circ}C$ to 85°C, $V_{CC} = 2.7V$ to 5.5V (Unless Otherwise Noted) (Continued)

| Symbol            | Parameter                                                                                                                                                                                                                                                                                          | Condition                         | Min                                                    | Тур | Max | Units |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------|-----|-----|-------|

|                   | Active 1MHz, $V_{CC} = 3V$ 0.6Active 4MHz, $V_{CC} = 3V$ 1.9Active 4MHz, $V_{CC} = 3V$ 1.9Active 8MHz, $V_{CC} = 5V$ 7Idle 1MHz, $V_{CC} = 3V$ 0.2Idle 4MHz, $V_{CC} = 3V$ 0.6Idle 8MHz, $V_{CC} = 3V$ 0.6Idle 8MHz, $V_{CC} = 5V$ 2.7Power-down Mode <sup>(5)</sup> WDT enabled, $V_{CC} = 3V$ <8 | Active 1MHz, V <sub>CC</sub> = 3V |                                                        | 0.6 |     | mA    |

|                   |                                                                                                                                                                                                                                                                                                    | Active 4MHz, V <sub>CC</sub> = 3V |                                                        | 1.9 | 5   | mA    |

|                   |                                                                                                                                                                                                                                                                                                    | 15                                | mA                                                     |     |     |       |

|                   | Power Supply Current                                                                                                                                                                                                                                                                               | Idle 1MHz, V <sub>CC</sub> = 3V   | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$ | mA  |     |       |

| Power-c           |                                                                                                                                                                                                                                                                                                    | Idle 4MHz, V <sub>CC</sub> = 3V   |                                                        | 0.6 | 2   | mA    |

|                   |                                                                                                                                                                                                                                                                                                    | Idle 8MHz, V <sub>CC</sub> = 5V   |                                                        | 2.7 | 7   | mA    |

|                   | D                                                                                                                                                                                                                                                                                                  | WDT enabled, V <sub>CC</sub> = 3V |                                                        | <8  | 15  | μA    |

|                   | Power-down Mode                                                                                                                                                                                                                                                                                    | WDT disabled, $V_{CC}$ = 3V       |                                                        | < 1 | 4   | μA    |

| V <sub>ACIO</sub> | <b>u</b>                                                                                                                                                                                                                                                                                           | 00                                |                                                        |     | 40  | mV    |

| I <sub>ACLK</sub> |                                                                                                                                                                                                                                                                                                    |                                   | -50                                                    |     | 50  | nA    |

| t <sub>ACPD</sub> | <b>u</b>                                                                                                                                                                                                                                                                                           |                                   |                                                        |     |     | ns    |

Notes: 1. "Max" means the highest value where the pin is guaranteed to be read as low

2. "Min" means the lowest value where the pin is guaranteed to be read as high

- Although each I/O port can sink more than the test conditions (20mA at Vcc = 5V, 10mA at Vcc = 3V) under steady state conditions (non-transient), the following must be observed: PDIP Package:

- PDIP Package:

- 1] The sum of all IOL, for all ports, should not exceed 200mA.

- 2] The sum of all IOL, for port A0 A7, should not exceed 100mA.

- 3] The sum of all IOL, for ports B0 B7,C0 C7, D0 D7 and XTAL2, should not exceed 100mA.

- TQFP and QFN/MLF Package:

- 1] The sum of all IOL, for all ports, should not exceed 400mA.

- 2] The sum of all IOL, for ports A0 A7, should not exceed 100mA.

- 3] The sum of all IOL, for ports B0 B7, should not exceed 100mA.

- 4] The sum of all IOL, for ports C0 C7, should not exceed 100mA.

- 5] The sum of all IOL, for ports D0 D7, xtal2, should not exceed 100mA.

If IOL exceeds the test condition, VOL may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

- Although each I/O port can source more than the test conditions (20mA at Vcc = 5V, 10mA at Vcc = 3V) under steady state conditions (non-transient), the following must be observed: PDIP Package:

- 1] The sum of all IOH, for all ports, should not exceed 200mA.

- 2] The sum of all IOH, for port A0 A7, should not exceed 100mA.

- 3] The sum of all IOH, for ports B0 B7,C0 C7, D0 D7 and XTAL2, should not exceed 100mA.

- TQFP and QFN/MLF Package:

- 1] The sum of all IOH, for all ports, should not exceed 400mA.

- 2] The sum of all IOH, for ports A0 A7, should not exceed 100mA.

- 3] The sum of all IOH, for ports B0 B7, should not exceed 100mA.

- 4] The sum of all IOL, for ports C0 C7, should not exceed 100mA.

- 5] The sum of all IOL, for ports D0 D7, xtal2, should not exceed 100mA..

- 5. Minimum  $V_{CC}$  for Power-down is 2.5V.

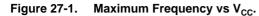

# 27.3 Speed Grades

# 27.4 Clock Characteristics

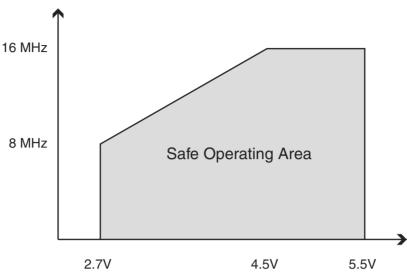

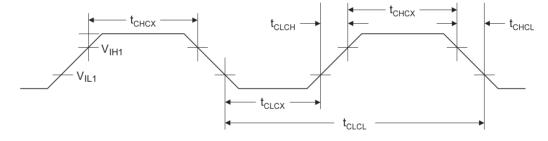

# 27.4.1 External Clock Drive Waveforms

# 27.4.2 External Clock Drive

#### Figure 27-3. External Clock Drive<sup>(1)</sup>

|                     |                      | V <sub>CC</sub> = 2.7 | V <sub>CC</sub> = 2.7V to 5.5V |      | V <sub>CC</sub> = 4.5V to 5.5V |       |  |

|---------------------|----------------------|-----------------------|--------------------------------|------|--------------------------------|-------|--|

| Symbol              | Parameter            | Min                   | Max                            | Min  | Max                            | Units |  |

| 1/t <sub>CLCL</sub> | Oscillator Frequency | 0                     | 8                              | 0    | 16                             | MHz   |  |

| t <sub>CLCL</sub>   | Clock Period         | 125                   |                                | 62.5 |                                | ns    |  |

| t <sub>CHCX</sub>   | High Time            | 50                    |                                | 25   |                                | ns    |  |

| t <sub>CLCX</sub>   | Low Time             | 50                    |                                | 25   |                                | ns    |  |

| Figure 27-3. | External Clock Drive <sup>(1)</sup> | (Continued) |

|--------------|-------------------------------------|-------------|

|--------------|-------------------------------------|-------------|

|                    |                                                         | V <sub>CC</sub> = 2.7V to 5.5V V <sub>CC</sub> = 4.5 |     | 5V to 5.5V |     |       |

|--------------------|---------------------------------------------------------|------------------------------------------------------|-----|------------|-----|-------|

| Symbol             | Parameter                                               | Min                                                  | Max | Min        | Max | Units |

| t <sub>CLCH</sub>  | Rise Time                                               |                                                      | 1.6 |            | 0.5 | μs    |

| t <sub>CHCL</sub>  | Fall Time                                               |                                                      | 1.6 |            | 0.5 | μs    |

| ∆t <sub>CLCL</sub> | Change in period from<br>one clock cycle to the<br>next |                                                      | 2   |            | 2   | %     |

Note: 1. Refer to "External Clock" on page 29 for details.

Table 27-1.

External RC Oscillator, Typical Frequencies (V<sub>CC</sub> = 5)

| <b>R [kΩ]</b> <sup>(1)</sup> | C [pF] | <b>f</b> <sup>(2)</sup> |

|------------------------------|--------|-------------------------|

| 33                           | 22     | 650kHz                  |

| 10                           | 22     | 2.0MHz                  |

Notes: 1. R should be in the range  $3k\Omega - 100k\Omega$ , and C should be at least 20pF.

2. The frequency will vary with package type and board layout.

# 27.5 System and Reset Characteristics

| Symbol            | Parameter                                                 | Condition    | Min                 | Тур  | Max                | Units |

|-------------------|-----------------------------------------------------------|--------------|---------------------|------|--------------------|-------|

|                   | Power-on Reset Threshold<br>Voltage (rising)              |              |                     | 1.4  | 2.3                | V     |

| V <sub>POT</sub>  | Power-on Reset Threshold Voltage (falling) <sup>(1)</sup> |              |                     | 1.3  | 2.3                | V     |

| V <sub>RST</sub>  | RESET Pin Threshold Voltage                               |              | 0.1 V <sub>CC</sub> |      | 0.9V <sub>CC</sub> | V     |

| t <sub>RST</sub>  | Minimum pulse width on RESET Pin                          |              |                     |      | 1.5                | μs    |

| N                 | Brown-out Reset Threshold Voltage <sup>(2)</sup>          | BODLEVEL = 1 | 2.5                 | 2.7  | 3.2                | V     |

| V <sub>BOT</sub>  |                                                           | BODLEVEL = 0 | 3.6                 | 4.0  | 4.5                |       |

|                   | Minimum low voltage period                                | BODLEVEL = 1 |                     | 2    |                    | μs    |

| t <sub>BOD</sub>  | for Brown-out Detection                                   | BODLEVEL = 0 |                     | 2    |                    | μs    |

| V <sub>HYST</sub> | Brown-out Detector<br>hysteresis                          |              |                     | 50   |                    | mV    |

| V <sub>BG</sub>   | Bandgap reference voltage                                 |              | 1.15                | 1.23 | 1.4                | V     |

| t <sub>BG</sub>   | Bandgap reference start-up time                           |              |                     | 40   | 70                 | μs    |

| I <sub>BG</sub>   | Bandgap reference current consumption                     |              |                     | 10   |                    | μA    |

Table 27-2.

Reset, Brown-out and Internal Voltage ReferenceCharacteristics

Notes: 1. The Power-on Reset will not work unless the supply voltage has been below V<sub>POT</sub> (falling).

2.  $V_{BOT}$  may be below nominal minimum operating voltage for some devices. For devices where this is the case, the device is tested down to  $V_{CC} = V_{BOT}$  during the production test. This guarantees that a Brown-out Reset will occur before  $V_{CC}$  drops to a voltage where correct operation of the microcontroller is no longer guaranteed. The test is performed using BODLEVEL = 1 and BODLEVEL = 0 for ATmega16A.

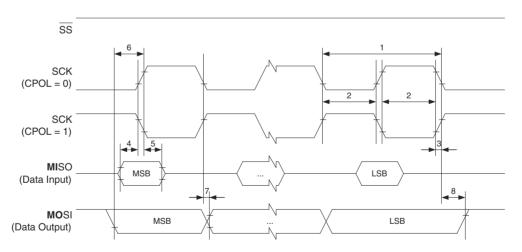

|    | Description                       | Mode   | Min                  | Тур                    | Max |    |

|----|-----------------------------------|--------|----------------------|------------------------|-----|----|

| 1  | SCK period                        | Master |                      | See Table 18-5         |     |    |

| 2  | SCK high/low                      | Master |                      | 50% duty cycle         |     |    |

| 3  | Rise/Fall time                    | Master |                      | 3.6                    |     |    |

| 4  | Setup                             | Master |                      | 10                     |     |    |

| 5  | Hold                              | Master |                      | 10                     |     |    |

| 6  | Out to SCK                        | Master |                      | 0.5 • t <sub>SCK</sub> |     | ns |

| 7  | SCK to out                        | Master |                      | 10                     |     |    |

| 8  | SCK to out high                   | Master |                      | 10                     |     |    |

| 9  | $\overline{\text{SS}}$ low to out | Slave  |                      | 15                     |     |    |

| 10 | SCK period                        | Slave  | 4 • t <sub>SCK</sub> |                        |     |    |

| 11 | SCK high/low                      | Slave  | 2 • t <sub>SCK</sub> |                        |     |    |

| 12 | Rise/Fall time                    | Slave  |                      |                        | 1.6 | μs |

| 13 | Setup                             | Slave  | 10                   |                        |     |    |

| 14 | Hold                              | Slave  | 10                   |                        |     |    |

| 15 | SCK to out                        | Slave  |                      | 15                     |     | 20 |

| 16 | SCK to $\overline{SS}$ high       | Slave  | 20                   |                        |     | ns |

| 17 | SS high to tri-state              | Slave  |                      | 10                     |     |    |

| 18 | $\overline{SS}$ low to SCK        | Slave  | 2 • t <sub>SCK</sub> |                        |     |    |

Table 27-5.SPI Timing Parameters

Figure 27-6. SPI Interface Timing Requirements (Master Mode)

# Atmel

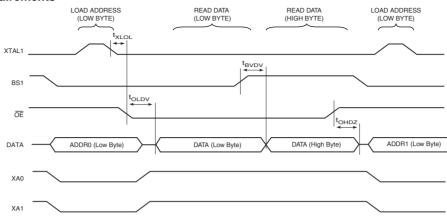

Figure 27-10. Parallel Programming Timing, Reading Sequence (within the Same Page) with Timing Requirements<sup>(1)</sup>

Note: 1. The timing requirements shown in Figure 27-8 (i.e.,  $t_{DVXH}$ ,  $t_{XHXL}$ , and  $t_{XLDX}$ ) also apply to reading operation.

|                      | 7-7. Parallel Programming Characteristics, $v_{CC} = 5 V \pm 10\%$ |      |     |      |       |  |

|----------------------|--------------------------------------------------------------------|------|-----|------|-------|--|

| Symbol               | Parameter                                                          | Min  | Тур | Max  | Units |  |

| V <sub>PP</sub>      | Programming Enable Voltage                                         | 11.5 |     | 12.5 | V     |  |

| I <sub>PP</sub>      | Programming Enable Current                                         |      |     | 250  | μA    |  |

| t <sub>DVXH</sub>    | Data and Control Valid before XTAL1 High                           | 67   |     |      | ns    |  |

| t <sub>XLXH</sub>    | XTAL1 Low to XTAL1 High                                            | 200  |     |      | ns    |  |

| t <sub>XHXL</sub>    | XTAL1 Pulse Width High                                             | 150  |     |      | ns    |  |

| t <sub>XLDX</sub>    | Data and Control Hold after XTAL1 Low                              | 67   |     |      | ns    |  |

| t <sub>XLWL</sub>    | XTAL1 Low to WR Low                                                | 0    |     |      | ns    |  |

| t <sub>XLPH</sub>    | XTAL1 Low to PAGEL high                                            | 0    |     |      | ns    |  |

| t <sub>PLXH</sub>    | PAGEL low to XTAL1 high                                            | 150  |     |      | ns    |  |

| t <sub>BVPH</sub>    | BS1 Valid before PAGEL High                                        | 67   |     |      | ns    |  |

| t <sub>PHPL</sub>    | PAGEL Pulse Width High                                             | 150  |     |      | ns    |  |

| t <sub>PLBX</sub>    | BS1 Hold after PAGEL Low                                           | 67   |     |      | ns    |  |

| t <sub>WLBX</sub>    | BS2/1 Hold after WR Low                                            | 67   |     |      | ns    |  |

| t <sub>PLWL</sub>    | PAGEL Low to WR Low                                                | 67   |     |      | ns    |  |

| t <sub>BVWL</sub>    | BS1 Valid to WR Low                                                | 67   |     |      | ns    |  |

| t <sub>WLWH</sub>    | WR Pulse Width Low                                                 | 150  |     |      | ns    |  |

| t <sub>WLRL</sub>    | WR Low to RDY/BSY Low                                              | 0    |     | 1    | μS    |  |

| t <sub>WLRH</sub>    | WR Low to RDY/BSY High <sup>(1)</sup>                              | 3.7  |     | 4.5  | ms    |  |

| t <sub>WLRH_CE</sub> | WR Low to RDY/BSY High for Chip Erase <sup>(2)</sup>               | 7.5  |     | 9    | ms    |  |

| t <sub>XLOL</sub>    | XTAL1 Low to OE Low                                                | 0    |     |      | ns    |  |

| t <sub>BVDV</sub>    | BS1 Valid to DATA valid                                            | 0    |     | 250  | ns    |  |

| t <sub>OLDV</sub>    | OE Low to DATA Valid                                               |      |     | 250  | ns    |  |

| t <sub>OHDZ</sub>    | OE High to DATA Tri-stated                                         |      |     | 250  | ns    |  |

Table 27-7. Parallel Programming Characteristics,  $V_{CC} = 5 V \pm 10\%$

Notes: 1. t<sub>WLRH</sub> is valid for the Write Flash, Write EEPROM, Write Fuse bits and Write Lock bits commands.

2.  $t_{WLRH CE}$  is valid for the Chip Erase command.

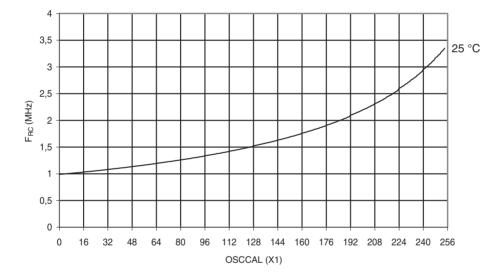

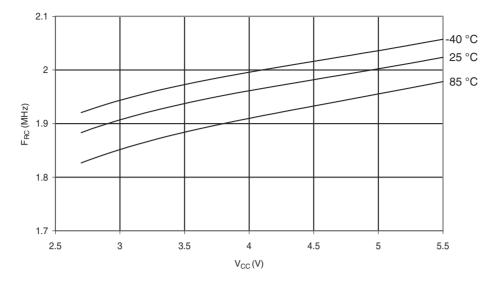

Figure 28-45. Calibrated 2MHz RC Oscillator Frequency vs. Osccal Value