Welcome to **E-XFL.COM**

**Understanding Embedded - DSP (Digital Signal Processors)**

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

# Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                                |

|-------------------------|--------------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                       |

| Туре                    | SC3850 Single Core                                                             |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | 0°C ~ 105°C (TJ)                                                               |

| Mounting Type           | Surface Mount                                                                  |

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=msc8151svt1000b                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

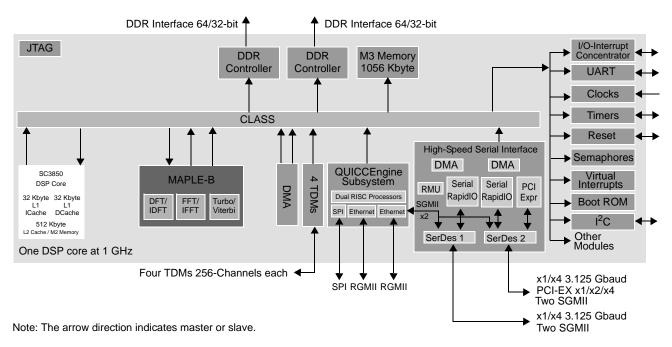

Figure 1. MSC8151 Block Diagram

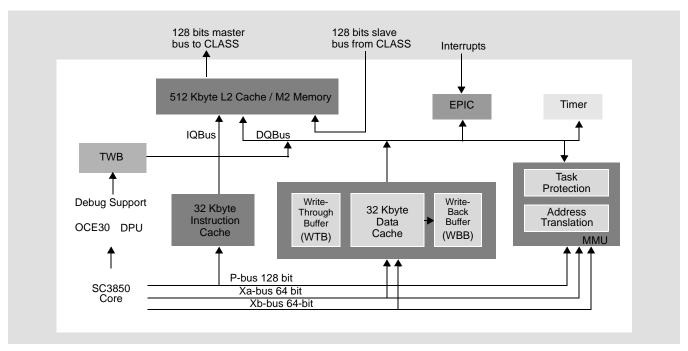

Figure 2. StarCore SC3850 DSP Subsystem Block Diagram

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|----------------------------|------------------------|--------------------|--|

| В9          | M2A13                      | 0                      | GVDD2              |  |

| B10         | VSS                        | Ground                 | N/A                |  |

| B11         | GVDD2                      | Power                  | N/A                |  |

| B12         | M2CS1                      | 0                      | GVDD2              |  |

| B13         | VSS                        | Ground                 | N/A                |  |

| B14         | GVDD2                      | Power                  | N/A                |  |

| B15         | M2DQ35                     | I/O                    | GVDD2              |  |

| B16         | VSS                        | Ground                 | N/A                |  |

| B17         | GVDD2                      | Power                  | N/A                |  |

| B18         | M2DQ51                     | I/O                    | GVDD2              |  |

| B19         | VSS                        | Ground                 | N/A                |  |

| B20         | GVDD2                      | Power                  | N/A                |  |

| B21         | Reserved                   | NC                     | _                  |  |

| B22         | Reserved                   | NC                     | _                  |  |

| B23         | SR1_TXD0                   | 0                      | SXPVDD1            |  |

| B24         | SR1_TXD0                   | 0                      | SXPVDD1            |  |

| B25         | SXCVDD1                    | Power                  | N/A                |  |

| B26         | SXCVSS1                    | Ground                 | N/A                |  |

| B27         | SR1_RXD0                   | I                      | SXCVDD1            |  |

| B28         | SR1_RXD0                   | l                      | SXCVDD1            |  |

| C1          | M2DQ28                     | I/O                    | GVDD2              |  |

| C2          | M2DM3                      | 0                      | GVDD2              |  |

| C3          | M2DQ26                     | I/O                    | GVDD2              |  |

| C4          | M2ECC4                     | I/O                    | GVDD2              |  |

| C5          | M2DM8                      | 0                      | GVDD2              |  |

| C6          | M2ECC2                     | 1/0                    | GVDD2              |  |

| C7          | M2CKE1                     | 0                      | GVDD2              |  |

| C8          | M2CK0                      | 0                      | GVDD2              |  |

| C9          | M2CK0                      | 0                      | GVDD2              |  |

| C10         | M2BA1                      | 0                      | GVDD2              |  |

| C11         | M2A1                       | 0                      | GVDD2              |  |

| C12         | M2WE                       | 0                      | GVDD2              |  |

| C13         | M2DQ37                     | 1/0                    | GVDD2<br>GVDD2     |  |

| C14         | M2DM4                      | 0                      | GVDD2<br>GVDD2     |  |

| C15         | M2DQ36                     | 1/0                    | GVDD2<br>GVDD2     |  |

| C16         | M2DQ36 M2DQ32              | 1/O                    | GVDD2<br>GVDD2     |  |

| C17         | M2DQ32<br>M2DQ55           | 1/0                    | GVDD2<br>GVDD2     |  |

| C18         |                            | 0                      | GVDD2<br>GVDD2     |  |

|             | M2DM6                      |                        |                    |  |

| C19         | M2DQ53<br>M2DQ52           | 1/0                    | GVDD2              |  |

| C20         |                            | I/O                    | GVDD2              |  |

| C21         | Reserved CPA IMP CAL BY    | NC .                   | - CVCVDD4          |  |

| C22         | SR1_IMP_CAL_RX             | Consumed               | SXCVDD1            |  |

| C23         | SXPVSS1                    | Ground                 | N/A                |  |

| C24         | SXPVDD1                    | Power                  | N/A                |  |

| C25         | SR1_REF_CLK                | I                      | SXCVDD1            |  |

Table 1. Signal List by Ball Number (continued)

| Ball Number | Signal Name <sup>1,2</sup>                        | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|---------------------------------------------------|------------------------|--------------------|--|

| E17         | M2DQ56                                            | I/O                    | GVDD2              |  |

| E18         | M2DQ57                                            | I/O                    | GVDD2              |  |

| E19         | M2DQS7                                            | I/O                    | GVDD2              |  |

| E20         | Reserved                                          | NC                     | _                  |  |

| E21         | Reserved                                          | NC                     | _                  |  |

| E22         | Reserved                                          | NC                     | _                  |  |

| E23         | SXPVDD1                                           | Power                  | N/A                |  |

| E24         | SXPVSS1                                           | Ground                 | N/A                |  |

| E25         | SR1_PLL_AGND <sup>9</sup>                         | Ground                 | SXCVSS1            |  |

| E26         | SR1_PLL_AVDD <sup>9</sup>                         | Power                  | SXCVDD1            |  |

| E27         | SXCVSS1                                           | Ground                 | N/A                |  |

| E28         | SXCVDD1                                           | Power                  | N/A                |  |

| F1          | VSS                                               | Ground                 | N/A                |  |

| F2          | GVDD2                                             | Power                  | N/A                |  |

| F3          | M2DQ16                                            | I/O                    | GVDD2              |  |

| F4          | VSS                                               | Ground                 | N/A                |  |

| F5          | GVDD2                                             | Power                  | N/A                |  |

| F6          | M2DQ17                                            | I/O                    | GVDD2              |  |

| F7          | VSS                                               | Ground                 | N/A                |  |

| F8          | GVDD2                                             | Power                  | N/A                |  |

| F9          | M2BA2                                             | 0                      | GVDD2              |  |

| F10         | VSS                                               | Ground                 | N/A                |  |

| F11         | GVDD2                                             | Power                  | N/A                |  |

| F12         | M2A4                                              | 0                      | GVDD2              |  |

| F13         | VSS                                               | Ground                 | N/A                |  |

| F14         | GVDD2                                             | Power                  | N/A                |  |

| F15         | M2DQ42                                            | 1/0                    | GVDD2              |  |

| F16         | VSS                                               | Ground                 | N/A                |  |

| F17         | GVDD2                                             | Power                  | N/A                |  |

| F18         | M2DQ58                                            | I/O                    | GVDD2              |  |

| F19         | M2DQS7                                            | I/O                    | GVDD2              |  |

| F20         | GVDD2                                             | Power                  | N/A                |  |

| F21         | SXPVDD1                                           | Power                  | N/A                |  |

| F22         | SXPVSS1                                           | Ground                 | N/A                |  |

| F23         | SR1_TXD2/SG1_TX <sup>4</sup>                      | O                      | SXPVDD1            |  |

| F23         | SR1_TXD2/SG1_TX<br>  SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |  |

| F24<br>F25  | SXCVDD1                                           | Power                  | N/A                |  |

|             |                                                   |                        |                    |  |

| F26         | SXCVSS1  SR1_RXD2/SG1_RX <sup>4</sup>             | Ground I               | N/A<br>SXCVDD1     |  |

| F27         | SR1_RXD2/SG1_RX <sup>4</sup>                      |                        | †                  |  |

| F28         |                                                   |                        | SXCVDD1            |  |

| G1          | M2DQS2                                            | 1/0                    | GVDD2              |  |

| G2          | M2DQS2                                            | 1/0                    | GVDD2              |  |

| G3          | M2DQ19                                            | 1/0                    | GVDD2              |  |

| G4          | M2DM2                                             | 0                      | GVDD2              |  |

| G5          | M2DQ21                                            | I/O                    | GVDD2              |  |

28

#### 2.5.1.4 DDR Reference Current Draw

Table 9 lists the current draw characteristics for MV<sub>REF</sub>.

**Note:** Values when used at recommended operating conditions (see Table 3).

Table 9. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter / Condition                            | Symbol              | Min | Max | Unit       |

|--------------------------------------------------|---------------------|-----|-----|------------|

| Current draw for MV <sub>REFn</sub> • DDR2 SDRAM | I <sub>MVREFn</sub> | _   | 300 | μΑ         |

| DDR3 SDRAM                                       |                     |     | 250 | μ <b>A</b> |

# 2.5.2 High-Speed Serial Interface (HSSI) DC Electrical Characteristics

The MSC8151 features an HSSI that includes two 4-channel SerDes ports used for high-speed serial interface applications (PCI Express, Serial RapidIO interfaces, and SGMII). This section and its subsections describe the common portion of the SerDes DC, including the DC requirements for the SerDes reference clocks and the SerDes data lane transmitter (Tx) and receiver (Rx) reference circuits. The data lane circuit specifications are specific for each supported interface, and they have individual subsections by protocol. The selection of individual data channel functionality is done via the Reset Configuration Word High Register (RCWHR) SerDes Protocol selection fields (S1P and S2P). Specific AC electrical characteristics are defined in Section 2.6.2, "HSSI AC Timing Specifications."

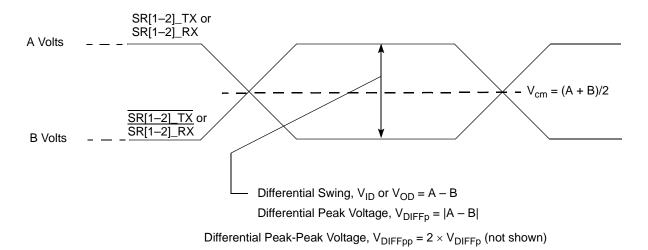

## 2.5.2.1 Signal Term Definitions

The SerDes interface uses differential signalling to transfer data across the serial link. This section defines terms used in the description and specification of differential signals. Figure 4 shows how the signals are defined. For illustration purposes only, one SerDes lane is used in the description. Figure 4 shows the waveform for either a transmitter output ( $SR[1-2]_TX$  and  $\overline{SR[1-2]_TX}$ ) or a receiver input ( $SR[1-2]_RX$  and  $\overline{SR[1-2]_RX}$ ). Each signal swings between A volts and B volts where A > B.

Figure 4. Differential Voltage Definitions for Transmitter or Receiver

Using this waveform, the definitions are listed in Table 10. To simplify the illustration, the definitions assume that the SerDes transmitter and receiver operate in a fully symmetrical differential signalling environment.

**Table 10. Differential Signal Definitions**

| Term                                                                         | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Single-Ended Swing                                                           | The transmitter output signals and the receiver input signals SR[1–2]_TX, SR[1–2]_TX, SR[1–2]_RX and SR[1–2]_RX each have a peak-to-peak swing of A – B volts. This is also referred to as each signal wire's single-ended swing.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Differential Output Voltage, V <sub>OD</sub> (or Differential Output Swing): | The differential output voltage (or swing) of the transmitter, $V_{OD}$ , is defined as the difference of the two complimentary output voltages: $V_{SR[1-2]\_TX} - V_{\overline{SR[1-2]\_TX}}$ . The $V_{OD}$ value can be either positive or negative.                                                                                                                                                                                                                                                                                                                                                                                                           |

| Differential Input Voltage, V <sub>ID</sub> (or<br>Differential Input Swing) | The differential input voltage (or swing) of the receiver, $V_{ID}$ , is defined as the difference of the two complimentary input voltages: $V_{SR[1-2]\_RX} - V_{\overline{SR[1-2]\_RX}}$ . The $V_{ID}$ value can be either positive or negative.                                                                                                                                                                                                                                                                                                                                                                                                                |

| Differential Peak Voltage, V <sub>DIFFp</sub>                                | The peak value of the differential transmitter output signal or the differential receiver input signal is defined as the differential peak voltage, $V_{\text{DIFFp}} =  A - B $ volts.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Differential Peak-to-Peak, V <sub>DIFFp-p</sub>                              | Since the differential output signal of the transmitter and the differential input signal of the receiver each range from A – B to –(A – B) volts, the peak-to-peak value of the differential transmitter output signal or the differential receiver input signal is defined as differential peak-to-peak voltage, $V_{DIFFp-p} = 2 \times V_{DIFFp} = 2 \times  (A-B)  \text{ volts, which is twice the differential swing in amplitude, or twice of the differential peak. For example, the output differential peak-peak voltage can also be calculated as V_{TX-DIFFp-p} = 2 \times  V_{OD} .$                                                                 |

| Differential Waveform                                                        | The differential waveform is constructed by subtracting the inverting signal (\$\overline{SR}[1-2]_TX\$, for example) from the non-inverting signal (\$\overline{SR}[1-2]_TX\$, for example) within a differential pair. There is only one signal trace curve in a differential waveform. The voltage represented in the differential waveform is not referenced to ground. Refer to Figure 16 as an example for differential waveform.                                                                                                                                                                                                                            |

| Common Mode Voltage, V <sub>cm</sub>                                         | The common mode voltage is equal to half of the sum of the voltages between each conductor of a balanced interchange circuit and ground. In this example, for SerDes output, $V_{\text{cm\_out}} = (V_{\text{SR}[1-2]\_TX} + V_{\overline{\text{SR}[1-2]\_TX}}) \div 2 = (A+B) \div 2,  which is the arithmetic mean of the two complimentary output voltages within a differential pair. In a system, the common mode voltage may often differ from one component's output to the other's input. It may be different between the receiver input and driver output circuits within the same component. It is also referred to as the DC offset on some occasions.$ |

To illustrate these definitions using real values, consider the example of a current mode logic (CML) transmitter that has a common mode voltage of 2.25 V and outputs, TD and TD. If these outputs have a swing from 2.0 V to 2.5 V, the peak-to-peak voltage swing of each signal (TD or TD) is 500 mV p-p, which is referred to as the single-ended swing for each signal. Because the differential signaling environment is fully symmetrical in this example, the transmitter output differential swing (V<sub>OD</sub>) has the same amplitude as each signal single-ended swing. The differential output signal ranges between 500 mV and -500 mV. In other words, V<sub>OD</sub> is 500 mV in one phase and -500 mV in the other phase. The peak differential voltage (V<sub>DIFFp</sub>) is 500 mV. The peak-to-peak differential voltage ( $V_{DIFFp-p}$ ) is 1000 mV p-p.

MSC8151 Single-Core Digital Signal Processor Data Sheet, Rev. 6 Freescale Semiconductor 29

#### rical Characteristics

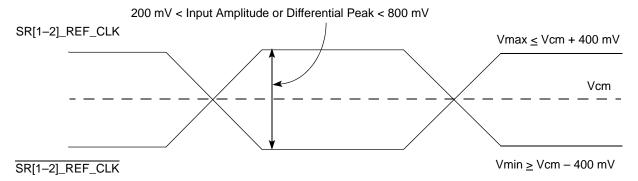

For an external AC-coupled connection, there is no common mode voltage requirement for the clock driver. Because the external AC-coupling capacitor blocks the DC-level, the clock driver and the SerDes reference clock receiver operate in different command mode voltages. The SerDes reference clock receiver in this connection scheme has its common mode voltage set to GND<sub>SXC</sub>. Each signal wire of the differential inputs is allowed to swing below and above the command mode voltage GND<sub>SXC</sub>. Figure 8 shows the SerDes reference clock input requirement for AC-coupled connection scheme.

Figure 8. Differential Reference Clock Input DC Requirements (External AC-Coupled)

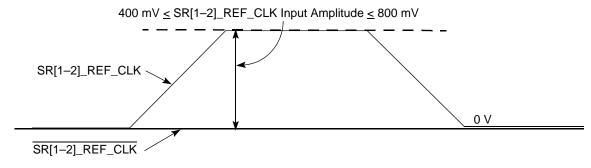

- Single-Ended Mode

- The reference clock can also be single-ended. The SR[1-2]\_REF\_CLK input amplitude (single-ended swing) must be between 400 mV and 800 mV peak-peak (from V<sub>MIN</sub> to V<sub>MAX</sub>) with SR[1-2]\_REF\_CLK either left unconnected or tied to ground.

- The SR[1–2]\_REF\_CLK input average voltage must be between 200 and 400 mV. Figure 9 shows the SerDes reference clock input requirement for single-ended signalling mode.

- To meet the input amplitude requirement, the reference clock inputs may need to be DC- or AC-coupled externally. For the best noise performance, the reference of the clock could be DC- or AC-coupled into the unused phase (SR[1–2]\_REF\_CLK) through the same source impedance as the clock input (SR[1–2]\_REF\_CLK) in use.

Figure 9. Single-Ended Reference Clock Input DC Requirements

# 2.5.3.2 DC-Level Requirements for PCI Express Configurations

The DC-level requirements for PCI Express implementations have separate requirements for the Tx and Rx lines. The MSC8151 supports a 2.5 Gbps PCI Express interface defined by the *PCI Express Base Specification, Revision 1.0a*. The transmitter specifications are defined in Table 11 and the receiver specifications are defined in Table 12.

**Note:** Specifications are valid at the recommended operating conditions listed in Table 3.

Table 11. PCI Express (2.5 Gbps) Differential Transmitter (Tx) Output DC Specifications

| Parameter                                         | Symbol                   | Min | Typical | Max  | Units | Notes |

|---------------------------------------------------|--------------------------|-----|---------|------|-------|-------|

| Differential peak-to-peak output voltage          | V <sub>TX-DIFFp-p</sub>  | 800 | 1000    | 1200 | mV    | 1     |

| De-emphasized differential output voltage (ratio) | V <sub>TX-DE-RATIO</sub> | 3.0 | 3.5     | 4.0  | dB    | 2     |

| DC differential Tx impedance                      | Z <sub>TX-DIFF-DC</sub>  | 80  | 100     | 120  | Ω     | 3     |

| Transmitter DC impedance                          | Z <sub>TX-DC</sub>       | 40  | 50      | 60   | Ω     | 4     |

Notes:

- .  $V_{TX-DIFFp-p} = 2 \times |V_{TX-D+} V_{TX-D-}|$  Measured at the package pins with a test load of 50  $\Omega$  to GND on each pin.

- 2. Ratio of the V<sub>TX-DIFFp-p</sub> of the second and following bits after a transition divided by the V<sub>TX-DIFFp-p</sub> of the first bit after a transition. Measured at the package pins with a test load of 50 Ω to GND on each pin.

- 3. Tx DC differential mode low impedance

- 4. Required Tx D+ as well as D- DC Impedance during all states

Table 12. PCI Express (2.5 Gbps) Differential Receiver (Rx) Input DC Specifications

| Parameter                               | Symbol                           | Min | Typical | Max  | Units | Notes |

|-----------------------------------------|----------------------------------|-----|---------|------|-------|-------|

| Differential input peak-to-peak voltage | V <sub>RX-DIFFp-p</sub>          | 120 | 1000    | 1200 | mV    | 1     |

| DC differential Input Impedance         | Z <sub>RX-DIFF-DC</sub>          | 80  | 100     | 120  | Ω     | 2     |

| DC input impedance                      | Z <sub>RX-DC</sub>               | 40  | 50      | 60   | Ω     | 3     |

| Powered down DC input impedance         | Z <sub>RX-HIGH-IMP-DC</sub>      | 50  | _       | _    | ΚΩ    | 4     |

| Electrical idle detect threshold        | V <sub>RX-IDLE-DET-DIFFp-p</sub> | 65  | _       | 175  | mV    | 5     |

Notes:

- 1.  $V_{RX-DIFFp-p} = 2 \times |V_{RX-D+} V_{RX-D-}|$  Measured at the package pins with a test load of 50  $\Omega$  to GND on each pin.

- 2. Rx DC differential mode impedance. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM), there is a 5 ms transition time before the receiver termination values must be met on all unconfigured lanes of a port.

- 3. Required Rx D+ as well as D- DC Impedance (50 ±20% tolerance). Measured at the package pins with a test load of 50 Ω to GND on each pin. Impedance during all LTSSM states. When transitioning from a fundamental reset to detect (the initial state of the LTSSM), there is a 5 ms transition time before the receiver termination values must be met on all unconfigured lanes of a port.

- 4. Required Rx D+ as well as D- DC Impedance when the receiver terminations do not have power. The Rx DC common mode impedance that exists when no power is present or fundamental reset is asserted. This helps ensure that the receiver detect circuit does not falsely assume a receiver is powered on when it is not. This term must be measured at 300 mV above the Rx ground.

- 5.  $V_{RX-IDLE-DET-DIFFp-p} = 2 \times |V_{RX-D+} V_{RX-D-}|$ . Measured at the package pins of the receiver

# 2.5.3.3 DC-Level Requirements for Serial RapidIO Configurations

This sections provided various DC-level requirements for Serial RapidIO Configurations.

**Note:** Specifications are valid at the recommended operating conditions listed in Table 3.

**Table 13. Serial RapidIO Transmitter DC Specifications**

| Parameter                                                                         | Symbol       | Min   | Typical | Max  | Units | Notes |

|-----------------------------------------------------------------------------------|--------------|-------|---------|------|-------|-------|

| Output voltage                                                                    | Vo           | -0.40 | _       | 2.30 | V     | 1     |

| Long run differential output voltage                                              | $V_{DIFFPP}$ | 800   | _       | 1600 | mVp-p | _     |

| Short run differential output voltage                                             | $V_{DIFFPP}$ | 500   | _       | 1000 | mVp-p | _     |

| Note: Voltage relative to COMMON of either signal comprising a differential pair. |              |       |         |      |       |       |

#### **Table 14. Serial RapidIO Receiver DC Specifications**

| Parameter                      | Symbol                        | Min | Typical | Max  | Units | Notes |  |  |

|--------------------------------|-------------------------------|-----|---------|------|-------|-------|--|--|

| Differential input voltage     | V <sub>IN</sub>               | 200 | _       | 1600 | mVp-p | 1     |  |  |

| Notes: 1. Measured at receiver | Notes: 1 Measured at receiver |     |         |      |       |       |  |  |

## 2.5.3.4 DC-Level Requirements for SGMII Configurations

**Note:** Specifications are valid at the recommended operating conditions listed in Table 3

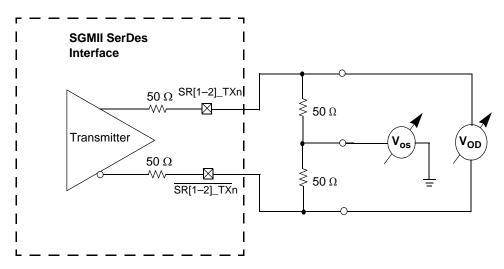

Table 15 describes the SGMII SerDes transmitter AC-coupled DC electrical characteristics. Transmitter DC characteristics are measured at the transmitter outputs  $(SR[1-2]_TX[n])$  and  $\overline{SR[1-2]_TX[n]}$  as shown in Figure 10.

Table 15. SGMII DC Transmitter Electrical Characteristics

| Parameter                               | Symbol          | Min                                       | Тур | Max                                       | Unit | Notes  |

|-----------------------------------------|-----------------|-------------------------------------------|-----|-------------------------------------------|------|--------|

| Output high voltage                     | V <sub>OH</sub> | _                                         | _   | $XV_{DD\_SRDS-Typ}/2 +  V_{OD} _{-max}/2$ | mV   | 1      |

| Output low voltage                      | V <sub>OL</sub> | $XV_{DD\_SRDS-Typ}/2 -  V_{OD} _{-max}/2$ | _   | _                                         | mV   | 1      |

| Output differential                     | V <sub>OD</sub> | 323                                       | 500 | 725                                       | mV   | 2,3,4  |

| voltage (XV <sub>DD-Typ</sub> at 1.0 V) |                 | 296                                       | 459 | 665                                       |      | 2,3,5  |

| 1.0 V)                                  |                 | 269                                       | 417 | 604                                       |      | 2,3,6  |

|                                         |                 | 243                                       | 376 | 545                                       |      | 2,3,7  |

|                                         |                 | 215                                       | 333 | 483                                       |      | 2,3,8  |

|                                         |                 | 189                                       | 292 | 424                                       |      | 2,3,9  |

|                                         |                 | 162                                       | 250 | 362                                       |      | 2,3,10 |

| Output impedance (single-ended)         | R <sub>O</sub>  | 40                                        | 50  | 60                                        | Ω    | _      |

Notes:

- 1. This does not align to DC-coupled SGMII.  $XV_{DD SRDS2-Tvp} = 1.1 \text{ V}$ .

- 2. The |V<sub>OD</sub>| value shown in the table assumes full multitude by setting srd\_smit\_lvl as 000 and the following transmit equalization setting in the XMITEQAB (for lanes A and B) or XMITEQEF (for lanes E and F) bit field of Control Register:

- The MSB (bit 0) of the above bit field is set to zero (selecting the full V<sub>DD-DIFF-p-p</sub> amplitude which is power up default);

- The LSB (bit [1-3]) of the above bit field is set based on the equalization settings listed in notes 4 through 10.

- 3. The  $|V_{OD}|$  value shown in the Typ column is based on the condition of  $XV_{DD\_SRDS2-Typ} = 1.0 \text{ V}$ , no common mode offset variation ( $V_{OS} = 500 \text{mV}$ ), SerDes transmitter is terminated with 100- $\Omega$  differential load between

- 4. Equalization setting: 1.0x: 0000.

- 5. Equalization setting: 1.09x: 1000.

- 6. Equalization setting: 1.2x: 0100.

- 7. Equalization setting: 1.33x: 1100.

- 8. Equalization setting: 1.5x: 0010.

- 9. Equalization setting: 1.71x: 1010.

- 10. Equalization setting: 2.0x: 0110.

- 11.  $|V_{OD}| = |V_{SR[1-2]}|_{TX_D} V_{\overline{SR[1-2]}}|_{TX_D}|_{TX_D}$  is also referred to as output differential peak voltage.  $V_{TX-DIFF_{D-D}} = 2^*|V_{OD}|$

Figure 10. SGMII Transmitter DC Measurement Circuit

Table 16 describes the SGMII SerDes receiver AC-coupled DC electrical characteristics.

Table 16. SGMII DC Receiver Electrical Characteristics<sup>5</sup>

| Parameter              |                                                                                    | Symbol               | Min  | Тур | Max  | Unit | Notes |

|------------------------|------------------------------------------------------------------------------------|----------------------|------|-----|------|------|-------|

| DC Input voltage range |                                                                                    | _                    |      | N/A |      | _    | 1     |

| Input<br>differential  | $ \begin{array}{llllllllllllllllllllllllllllllllllll$                              |                      | 1200 | mV  | 2, 4 |      |       |

| voltage                | SRDSnCR4[EICE{12:10}] = 0b100 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b100 for SGMII2 |                      | 175  | _   |      |      |       |

| Loss of signal         | signal SRDSnCR4[EICF{4:2}] = 0b001 for SGMII2                                      |                      | 30   | _   | 100  | mV   | 3, 4  |

|                        | SRDSnCR4[EICE{12:10}] = 0b100 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b100 for SGMII2 |                      | 65   | _   | 175  |      |       |

| Receiver diffe         | erential input impedance                                                           | Z <sub>RX_DIFF</sub> | 80   | _   | 120  | W    | _     |

Notes: 1. Input must be externally AC-coupled.

- 2. V<sub>RX\_DIFFp-p</sub> is also referred to as peak-to-peak input differential voltage.

- 3. The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in the PCI Express interface. Refer to the PCI Express Differential Receiver (RX) Input Specifications section of the PCI Express Specification document. for details.

- 4. The values for SGMII1 and SGMII2 are selected in the SRDS control registers.

- 5. The supply voltage is 1.0 V.

Table 24. SR[1–2]\_REF\_CLK and SR[1–2]\_REF\_CLK Input Clock Requirements (continued)

| Parameter | Symbol | Min | Typical | Max | Units | Notes |

|-----------|--------|-----|---------|-----|-------|-------|

|-----------|--------|-----|---------|-----|-------|-------|

Notes:

- 1. Caution: Only 100 and 125 have been tested. Other values will not work correctly with the rest of the system.

- 2. Limits from PCI Express CEM Rev 1.0a

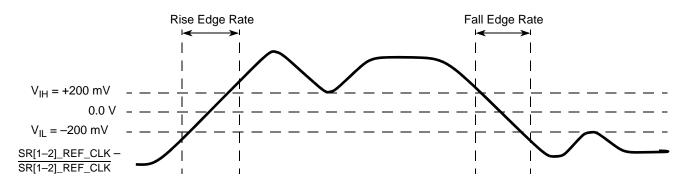

- 3. Measured from -200 mV to +200 mV on the differential waveform (derived from SR[1-2]\_REF\_CLK minus SR[1-2]\_REF\_CLK). The signal must be monotonic through the measurement region for rise and fall time. The 400 mV measurement window is centered on the differential zero crossing. See Figure 16.

- 4. Measurement taken from differential waveform

- 5. Measurement taken from single-ended waveform

- 6. Matching applies to rising edge for SR[1–2]\_REF\_CLK and falling edge rate for \$\overline{SR[1-2]\_REF\_CLK}\$. It is measured using a 200 mV window centered on the median cross point where \$SR[1–2]\_REF\_CLK rising meets \$SR[1–2]\_REF\_CLK falling. The median cross point is used to calculate the voltage thresholds that the oscilloscope uses for the edge rate calculations. The rise edge rate of \$SR[1-2]\_REF\_CLK should be compared to the fall edge rate of \$\overline{SR[1-2]\_REF\_CLK}\$; the maximum allowed difference should not exceed 20% of the slowest edge rate. See Figure 17.

Figure 16. Differential Measurement Points for Rise and Fall Time

Figure 17. Single-Ended Measurement Points for Rise and Fall Time Matching

## 2.6.2.3 Serial RapidIO AC Timing Specifications

**Note:** Specifications are valid at the recommended operating conditions listed in Table 3.

Table 27 defines the transmitter AC specifications for the Serial RapidIO interface. The AC timing specifications do not include REF\_CLK jitter.

Table 27. Serial RapidIO Transmitter AC Timing Specifications

| Characteristic             | Symbol         | Min          | Typical | Max          | Unit   |

|----------------------------|----------------|--------------|---------|--------------|--------|

| Deterministic Jitter       | J <sub>D</sub> | _            | _       | 0.17         | UI p-p |

| Total Jitter               | J <sub>T</sub> | _            |         | 0.35         | UI p-p |

| Unit Interval: 1.25 GBaud  | UI             | 800 – 100ppm | 800     | 800 + 100ppm | ps     |

| Unit Interval: 2.5 GBaud   | UI             | 400 – 100ppm | 400     | 400 + 100ppm | ps     |

| Unit Interval: 3.125 GBaud | UI             | 320 – 100ppm | 320     | 320 + 100ppm | ps     |

Table 28 defines the Receiver AC specifications for the Serial RapidIO interface. The AC timing specifications do not include REF\_CLK jitter.

Table 28. Serial RapidIO Receiver AC Timing Specifications

| Characteristic                                     | Symbol         | Min          | Typical | Max               | Unit   | Notes |

|----------------------------------------------------|----------------|--------------|---------|-------------------|--------|-------|

| Deterministic Jitter Tolerance                     | J <sub>D</sub> | 0.37         | _       | _                 | UI p-p | 1     |

| Combined Deterministic and Random Jitter Tolerance | $J_{DR}$       | 0.55         | _       | _                 | UI p-p | 1     |

| Total Jitter Tolerance                             | J <sub>T</sub> | 0.65         | _       | _                 | UI p-p | 1, 2  |

| Bit Error Rate                                     | BER            | _            | _       | 10 <sup>-12</sup> | _      | _     |

| Unit Interval: 1.25 GBaud                          | UI             | 800 – 100ppm | 800     | 800 + 100ppm      | ps     | _     |

| Unit Interval: 2.5 GBaud                           | UI             | 400 – 100ppm | 400     | 400 + 100ppm      | ps     | _     |

| Unit Interval: 3.125 GBaud                         | UI             | 320 – 100ppm | 320     | 320 + 100ppm      | ps     | _     |

Notes: 1. Measured at receiver.

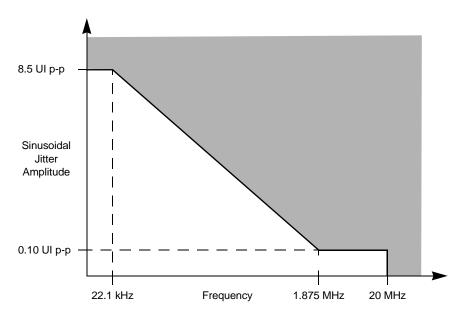

2. Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 18. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

Figure 18. Single Frequency Sinusoidal Jitter Limits

MSC8151 Single-Core Digital Signal Processor Data Sheet, Rev. 6

# 2.6.3 TDM Timing

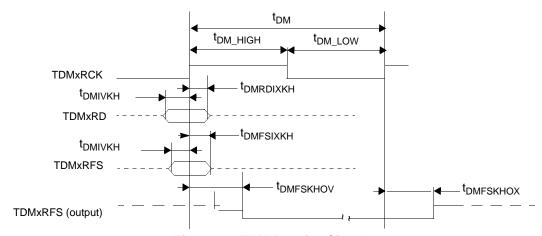

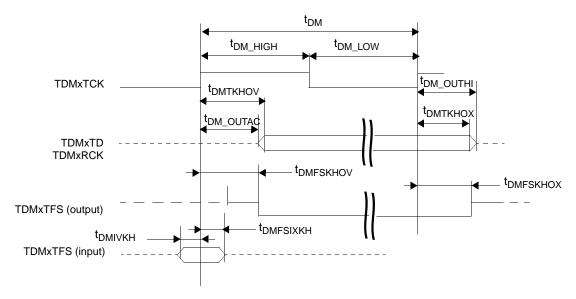

Table 31 provides the input and output AC timing specifications for the TDM interface.

Table 31. TDM AC Timing Specifications for 62.5 MHz<sup>1</sup>

| Parameter                                    | Symbol <sup>2</sup>   | Min  | Max  | Unit |

|----------------------------------------------|-----------------------|------|------|------|

| TDMxRCK/TDMxTCK                              | t <sub>DM</sub>       | 16.0 | _    | ns   |

| TDMxRCK/TDMxTCK high pulse width             | t <sub>DM_HIGH</sub>  | 7.0  | _    | ns   |

| TDMxRCK/TDMxTCK low pulse width              | t <sub>DM_LOW</sub>   | 7.0  | _    | ns   |

| TDM all input setup time                     | t <sub>DMIVKH</sub>   | 3.6  | _    | ns   |

| TDMxRD hold time                             | t <sub>DMRDIXKH</sub> | 1.9  | _    | ns   |

| TDMxTFS/TDMxRFS input hold time              | t <sub>DMFSIXKH</sub> | 1.9  | _    | ns   |

| TDMxTCK High to TDMxTD output active         | t <sub>DM_OUTAC</sub> | 2.5  | _    | ns   |

| TDMxTCK High to TDMxTD output valid          | t <sub>DMTKHOV</sub>  | _    | 9.8  | ns   |

| TDMxTD hold time                             | t <sub>DMTKHOX</sub>  | 2.5  | _    | ns   |

| TDMxTCK High to TDMxTD output high impedance | t <sub>DM_OUTHI</sub> | _    | 9.8  | ns   |

| TDMxTFS/TDMxRFS output valid                 | t <sub>DMFSKHOV</sub> | _    | 9.25 | ns   |

| TDMxTFS/TDMxRFS output hold time             | t <sub>DMFSKHOX</sub> | 2.0  | _    | ns   |

Notes:

- 1. The symbols used for timing specifications follow the pattern t<sub>(first two letters of functional block)</sub>(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)</sub>(reference)(state)(signal)(state) for outputs. For example, t<sub>HIKHOX</sub> symbolizes the output internal timing (HI) for the time t<sub>serial</sub> memory clock reference (K) goes from the high state (H) until outputs (O) are invalid (X).

- 2. Output values are based on 30 pF capacitive load.

- Inputs are referenced to the sampling that the TDM is programmed to use. Outputs are referenced to the programming edge

they are programmed to use. Use of the rising edge or falling edge as a reference is programmable. T<sub>DMxTCK</sub> and T<sub>DMxRCK</sub> are

shown using the rising edge.

- 4. All values are based on a maximum TDM interface frequency of 62.5 MHz.

Figure 20 shows the TDM receive signal timing.

Figure 20. TDM Receive Signals

47

Figure 21 shows the TDM transmit signal timing.

Figure 21. TDM Transmit Signals

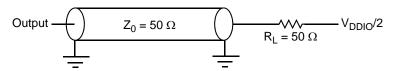

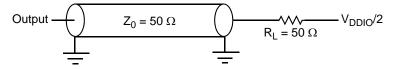

Figure 22 provides the AC test load for the TDM/SI.

Figure 22. TDM AC Test Load

# 2.6.4 Timers AC Timing Specifications

Table 32 lists the timer input AC timing specifications.

**Table 32. Timers Input AC Timing Specifications**

| Characteristics                                                                                                           |                                                                                                                                  | Symbol | Minimum            | Unit | Notes |      |

|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|------|-------|------|

| Timers inputs—minimum pulse width                                                                                         |                                                                                                                                  |        | T <sub>TIWID</sub> | 8    | ns    | 1, 2 |

| Notes: 1. The maximum allowed frequency of timer outputs is 125 MHz. Configure the timer modules appropriately.           |                                                                                                                                  |        |                    |      |       |      |

| 2. Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by any |                                                                                                                                  |        |                    |      |       |      |

|                                                                                                                           | external synchronous logic. Timer inputs are required to be valid for at least t <sub>TIWID</sub> ns to ensure proper operation. |        |                    |      |       |      |

**Note:** For recommended operating conditions, see Table 3.

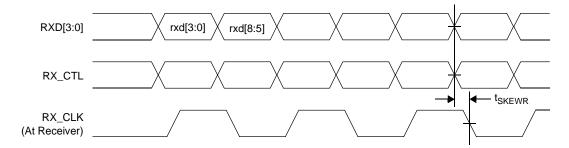

Figure 23 shows the AC test load for the timers.

Figure 23. Timer AC Test Load

MSC8151 Single-Core Digital Signal Processor Data Sheet, Rev. 6

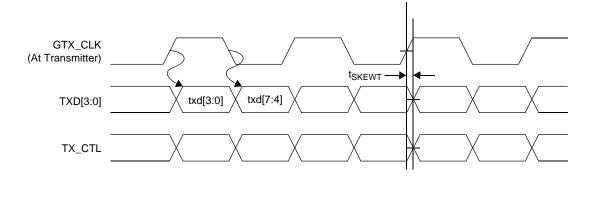

## 2.6.5.2 RGMII AC Timing Specifications

Table 34 presents the RGMII AC timing specifications for applications requiring an on-board delayed clock.

Table 34. RGMII at 1 Gbps<sup>2</sup> with On-Board Delay<sup>3</sup> AC Timing Specifications

| Parameter/Condition                                     | Symbol             | Min | Тур | Max | Unit |

|---------------------------------------------------------|--------------------|-----|-----|-----|------|

| Data to clock output skew (at transmitter) <sup>4</sup> | t <sub>SKEWT</sub> | 0.5 | _   | 0.5 | ns   |

| Data to clock input skew (at receiver) <sup>4</sup>     | t <sub>SKEWR</sub> | 1   | _   | 2.6 | ns   |

**Notes:** 1. At recommended operating conditions with  $V_{DDIO}$  of 2.5 V  $\pm$  5%.

2. RGMII at 100 Mbps support is guaranteed by design.

3. Program GCR4 as 0x000000000.

4. This implies that PC board design requires clocks to be routed such that an additional trace delay of greater than 1.5 ns and less than 2.0 ns is added to the associated clock signal.

Table 35 presents the RGMII AC timing specification for applications required non-delayed clock on board.

Table 35. RGMII at 1 Gbps<sup>2</sup> with No On-Board Delay<sup>3</sup> AC Timing Specifications

| Parameter/Condition                                     | Symbol             | Min  | Тур | Max  | Unit |

|---------------------------------------------------------|--------------------|------|-----|------|------|

| Data to clock output skew (at transmitter) <sup>4</sup> | t <sub>SKEWT</sub> | -2.6 | _   | -1.0 | ns   |

| Data to clock input skew (at receiver) <sup>4</sup>     | t <sub>SKEWR</sub> | -0.5 | _   | 0.5  | ns   |

**Notes:** 1. At recommended operating conditions with  $V_{DDIO}$  of 2.5 V  $\pm$  5%.

2. RGMII at 100 Mbps support is guaranteed by design.

3. GCR4 should be programmed as 0x000CC330.

4. This implies that PC board design requires clocks to be routed with no additional trace delay

Figure 25 shows the RGMII AC timing and multiplexing diagrams.

Figure 25. RGMII AC Timing and Multiplexing

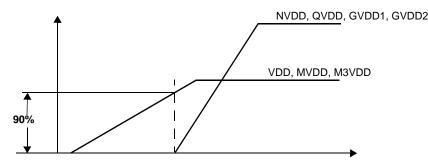

#### ware Design Considerations

2. After the above rails rise to 90% of their nominal voltage, the following I/O power rails may rise in any sequence (see Figure 34): QVDD, NVDD, GVDD1, and GVDD2.

Figure 34. Supply Ramp-Up Sequence

**Notes:** 1. If the M3 memory is not used, M3VDD can be tied to GND.

- 2. If the MAPLE-B is not used, MVDD can be tied to GND.

- 3. If the HSSI port1 is not used, SXCVDD1 and SXPVDD1 must be connected to the designated power supplies.

- **4.** If the HSSI port2 is not used, SXCVDD2 and SXPVDD2 must be connected to the designated power supplies.

- **5.** If the DDR port 1 interface is not used, it is recommended that GVDD1 be left unconnected.

- 6. If the DDR port 2 interface is not used, it is recommended that GVDD2 be left unconnected.

#### 3.1.4 Reset Guidelines

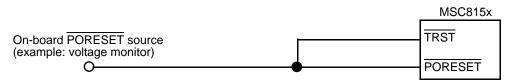

When a debugger is not used, implement the connection scheme shown in Figure 35.

Figure 35. Reset Connection in Functional Application

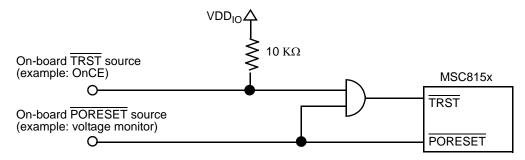

When a debugger is used, implement the connection scheme shown in Figure 36.

Figure 36. Reset Connection in Debugger Application

# 3.2 PLL Power Supply Design Considerations

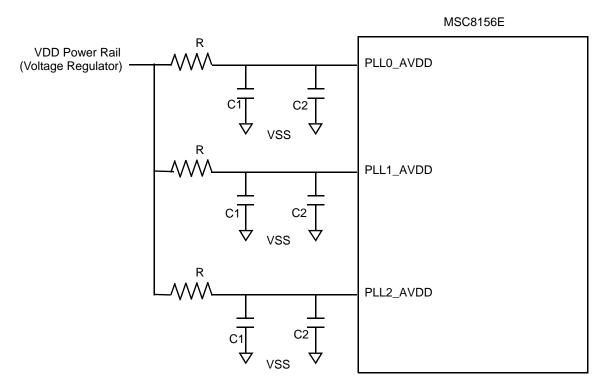

Each global PLL power supply must have an external RC filter for the PLLn\_AVDD input (see Figure 37) in which the following components are defined as listed:

- $R = 5 \Omega \pm 5\%$

- C1 = 10  $\mu$ F ± 10%, 0603, X5R, with ESL  $\leq$  0.5 nH, low ESL Surface Mount Capacitor.

- C2 = 1.0  $\mu$ F ± 10%, 0402, X5R, with ESL  $\leq$  0.5 nH, low ESL Surface Mount Capacitor.

**Note:** A higher capacitance value for C2 may be used to improve the filter as long as the other C2 parameters do not change.

All three PLLs can connect to a single supply voltage source (such as a voltage regulator) as long as the external RC filter is applied to each PLL separately. For optimal noise filtering, place the circuit as close as possible to its PLLn AVDD inputs.

Figure 37. PLL Supplies

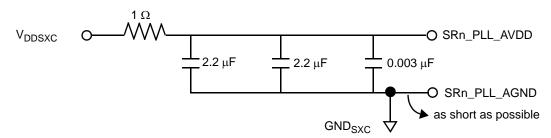

Each SerDes PLL power supply must be filtered using a circuit similar to the one shown in Figure 38, to ensure stability of the internal clock. For maximum effectiveness, the filter circuit should be placed as closely as possible to the SRn\_PLL\_AVDD ball to ensure it filters out as much noise as possible. The ground connection should be near the SRn\_PLL\_AVDD ball. The 0.003  $\mu$ F capacitor is closest to the ball, followed by the two 2.2  $\mu$ F capacitors, and finally the 1  $\Omega$  resistor to the board supply plane. The capacitors are connected from SRn\_PLL\_AVDD to the ground plane. Use ceramic chip capacitors with the highest possible self-resonant frequency. All trances should be kept short, wide, and direct.

Figure 38. SerDes PLL Supplies

MSC8151 Single-Core Digital Signal Processor Data Sheet, Rev. 6

# 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

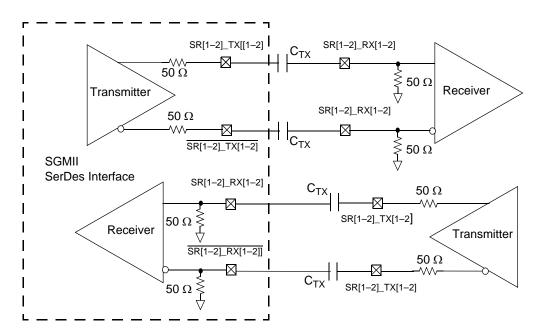

# 3.4 SGMII AC-Coupled Serial Link Connection Example

Figure 39 shows an example of a 4-wire AC-coupled serial link connection. For additional layout suggestions, see *AN3556 MSC815x High Speed Serial Interface Hardware Design Considerations*, available on the Freescale website or from your local sales office or representative.

Figure 39. 4-Wire AC-Coupled SGMII Serial Link Connection Example

#### 3.5.1.4 DDR2 Unused MAPAR Pin Connections

When the MAPAR signals are not used, refer to Table 43 to determine the correct pin connections.

Table 43. Connectivity of MAPAR Pins for DDR2

| Signal Name |                                                                                                                                                                                                                                                                                                                                 | Signal Name | Pin connection |  |  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------|--|--|

| MAPAR_OUT   |                                                                                                                                                                                                                                                                                                                                 |             | NC             |  |  |

| MAPAR_IN    |                                                                                                                                                                                                                                                                                                                                 |             | NC             |  |  |

| Notes:      | <ol> <li>For the signals listed in this table, the initial M stands for M1 or M2 depending on which DDR controller is used for DDR2.</li> <li>For MSC8151 Revision 1 silicon, these pins were connected to GND. For newer revisions of the MSC8151, connecting these pins to GND increases device power consumption.</li> </ol> |             |                |  |  |

## 3.5.2 HSSI-Related Pins

#### 3.5.2.1 HSSI Port Is Not Used

The signal names in Table 44 and Table 45 are generic names for a RapidIO interface. For actual pin names refer to Table 1.

Table 44. Connectivity of Serial RapidIO Interface Related Pins When the RapidIO Interface Is Not Used

| Signal Name                                                                                                   | Pin Connection |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| SR_IMP_CAL_RX                                                                                                 | NC             |  |  |  |  |

| SR_IMP_CAL_TX                                                                                                 | NC             |  |  |  |  |

| SR[1-2]_REF_CLK                                                                                               | SXCVSS         |  |  |  |  |

| SR[1-2]_REF_CLK                                                                                               | SXCVSS         |  |  |  |  |

| SR[1-2]_RXD[3-0]                                                                                              | SXCVSS         |  |  |  |  |

| SR[1-2]_RXD[3-0]                                                                                              | SXCVSS         |  |  |  |  |

| SR[1-2]_TXD[3-0]                                                                                              | NC             |  |  |  |  |

| SR[1-2]_TXD[3-0]                                                                                              | NC             |  |  |  |  |

| SR[1-2]_PLL_AVDD                                                                                              | In use         |  |  |  |  |

| SR[1-2]_PLL_AGND                                                                                              | In use         |  |  |  |  |

| SXPVSS                                                                                                        | In use         |  |  |  |  |

| SXCVSS                                                                                                        | In use         |  |  |  |  |

| SXPVDD                                                                                                        | In use         |  |  |  |  |

| SXCVDD In use                                                                                                 |                |  |  |  |  |

| Note: All lanes in the HSSI SerDes should be powered down. Refer to the MSC8151 Reference Manual for details. |                |  |  |  |  |

# 3.5.2.2 HSSI Specific Lane Is Not Used

Table 45. Connectivity of HSSI Related Pins When Specific Lane Is Not Used

| Signal Name     | Pin Connection |

|-----------------|----------------|

| SR_IMP_CAL_RX   | In use         |

| SR_IMP_CAL_TX   | In use         |

| SR[1-2]_REF_CLK | In use         |

| SR[1-2]_REF_CLK | In use         |

Table 45. Connectivity of HSSI Related Pins When Specific Lane Is Not Used (continued)

| Signal Name                                                                        | Pin Connection |  |  |  |

|------------------------------------------------------------------------------------|----------------|--|--|--|

| SR[1-2]_RXD <i>n</i>                                                               | SXCVSS         |  |  |  |

| SR[1-2]_RXD <b>n</b>                                                               | SXCVSS         |  |  |  |

| SR[1-2]_TXD <i>n</i>                                                               | NC             |  |  |  |

| SR[1-2]_TXD <b>n</b>                                                               | NC             |  |  |  |

| SR[1-2]_PLL_AVDD                                                                   | in use         |  |  |  |

| SR[1-2]_PLL_AGND                                                                   | in use         |  |  |  |

| SXPVSS                                                                             | in use         |  |  |  |

| SXCVSS                                                                             | in use         |  |  |  |

| SXPVDD                                                                             | in use         |  |  |  |

| SXCVDD                                                                             | in use         |  |  |  |

| <b>Note:</b> The $n$ indicates the lane number $\{0,1,2,3\}$ for all unused lanes. |                |  |  |  |

#### 3.5.3 RGMII Ethernet Related Pins

**Note:** Table 46 and Table 47 assume that the alternate function of the specified pin is not used. If the alternate function is used, connect the pin as required to support that function.

Table 46. Connectivity of RGMII Related Pins When the RGMII Interface Is Not Used

| Signal Name                                                              | Pin Connection |  |

|--------------------------------------------------------------------------|----------------|--|

| GE1_RX_CTL                                                               | GND            |  |

| GE2_TX_CTL                                                               | NC             |  |

| Note: Assuming GE1 and GE2 are disabled in the reset configuration word. |                |  |

GE\_MDC and GE\_MDIO pins should be connected as required by the specified protocol. If neither GE1 nor GE2 is used, Table 47 lists the recommended management pin connections.

Table 47. Connectivity of GE Management Pins When GE1 and GE2 Are Not Used

| Signal Name | Pin Connection |

|-------------|----------------|

| GE_MDC      | NC             |

| GE_MDIO     | NC             |

#### 3.5.4 TDM Interface Related Pins

Table 48 lists the board connections of the TDM pins when an entire specific TDM is not used. For multiplexing options that select a subset of a TDM interface, use the connections described in Table 48 for those signals that are not selected. Table 48 assumes that the alternate function of the specified pin is not used. If the alternate function is used, connect that pin as required to support the selected function.

Table 48. Connectivity of TDM Related Pins When TDM Interface Is Not Used

| Signal Name       | Pin Connection |  |

|-------------------|----------------|--|

| TDM <b>n</b> RCLK | GND            |  |

| TDM <b>n</b> RDAT | GND            |  |

| TDM <b>n</b> RSYN | GND            |  |

MSC8151 Single-Core Digital Signal Processor Data Sheet, Rev. 6

# 3.6 Guide to Selecting Connections for Remote Power Supply Sensing

To assure consistency of input power levels, some applications use a practice of connecting the remote sense signal input of an on-board power supply to one of power supply pins of the IC device. The advantage of using this connection is the ability to compensate for the slow components of the IR drop caused by resistive supply current path from on-board power supply to the pins layer on the package. However, because of specific device requirements, not every ball connection can be selected as the remote sense pin. Some of these pins must be connected to the appropriate power supply or ground to ensure correct device functionality. Some connections supply critical power to a specific high usage area of the IC die; using such a connection as a non-supply pin could impact necessary supply current during high current events. The following balls can be used as the board supply remote sense output without degrading the power and ground supply quality:

*VDD*: W10, T19*VSS*: J18, Y10*M3VDD*: None

Do not use any other connections for remote sensing. Use of any other connections for this purpose can result in application and device failure.

# 4 Ordering Information

Consult a Freescale Semiconductor sales office or authorized distributor to determine product availability and place an order.

| Qual Status                        | Cores         | Encryption                 | Temeprature<br>Range                  | Package Type                                           | Core<br>Frequency | Die<br>Revision |

|------------------------------------|---------------|----------------------------|---------------------------------------|--------------------------------------------------------|-------------------|-----------------|

| PC = Prototype<br>MSC = Production | 8151 = 1 Core | [blank] =<br>Non-encrypted | S = 0° to 105°C<br>T = -40°C to 105°C | VT = FC-PBGA Lead Free<br>AG = FC-PBGA C4/C5 Lead Free | 1000 = 1Ghz       | B = Rev 2.1     |