Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                         |

|----------------------------|-----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                                         |

| Core Size                  | 32-Bit Single-Core                                                                      |

| Speed                      | 50MHz                                                                                   |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, SPI, UART/USART                                        |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, LVD, POR, PS2, PWM, WDT                  |

| Number of I/O              | 51                                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                                        |

| Program Memory Type        | FLASH                                                                                   |

| EEPROM Size                | -                                                                                       |

| RAM Size                   | 16K x 8                                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                             |

| Data Converters            | A/D 8x12b                                                                               |

| Oscillator Type            | Internal                                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                       |

| Mounting Type              | Surface Mount                                                                           |

| Package / Case             | 64-LQFP                                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/nuc100re3dn |

# 2.2 NuMicro® NUC120 Features - USB Line

- ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core

- Runs up to 50 MHz

- One 24-bit system timer

- Supports low power sleep mode

- Single-cycle 32-bit hardware multiplier

- NVIC for the 32 interrupt inputs, each with 4-levels of priority

- Serial Wire Debug supports with 2 watchpoints/4 breakpoints

- Built-in LDO for wide operating voltage ranges from 2.5 V to 5.5 V

- Flash Memory

- 32/64/128 Kbytes Flash for program code

- 4 KB flash for ISP loader

- Supports In-System-Program (ISP) and In-Application-Program (IAP) application code update

- 512 byte page erase for flash

- Configurable Data Flash address and size for 128 KB system, fixed 4 KB Data Flash for the 32 KB and 64 KB system

- Supports 2-wired ICP update through SWD/ICE interface

- Supports fast parallel programming mode by external programmer

- SRAM Memory

- 4/8/16 Kbytes embedded SRAM

- Supports PDMA mode

- PDMA (Peripheral DMA)

- Supports 9 channels PDMA for automatic data transfer between SRAM and peripherals

- Supports CRC calculation with four common polynomials, CRC-CCITT, CRC-8, CRC-16 and CRC-32

- Clock Control

- Flexible selection for different applications

- Built-in 22.1184 MHz high speed oscillator for system operation

- ♦ Trimmed to ±1 % at +25  $^{\circ}$ C and  $V_{DD} = 5 \text{ V}$

- $\bullet$  Trimmed to ±3 % at -40  $^{\circ}$ C ~ +85  $^{\circ}$ C and V<sub>DD</sub> = 2.5 V ~ 5.5 V

- Built-in 10 kHz low speed oscillator for Watchdog Timer and Wake-up operation

- Supports one PLL, up to 50 MHz, for high performance system operation

- External 4~24 MHz high speed crystal input for USB and precise timing operation

- External 32.768 kHz low speed crystal input for RTC function and low power system operation

- GPIO

- Four I/O modes:

- Quasi-bidirectional

- Push-pull output

- Open-drain output

- ◆ Input only with high impendence

- TTL/Schmitt trigger input selectable

- I/O pin configured as interrupt source with edge/level setting

- Timer

- Supports 4 sets of 32-bit timers with 24-bit up-timer and one 8-bit prescale counter

- Independent clock source for each timer

- Provides one-shot, periodic, toggle and continuous counting operation modes

- Supports event counting function

- Supports input capture function

## Watchdog Timer

- Multiple clock sources

- 8 selectable time-out period from 1.6 ms ~ 26.0 sec (depending on clock source)

- Wake-up from Power-down or Idle mode

- Interrupt or reset selectable on watchdog time-out

## Window Watchdog Timer

6-bit down counter with 11-bit prescale for wide range window selected

### RTC

- Supports software compensation by setting frequency compensate register (FCR)

- Supports RTC counter (second, minute, hour) and calendar counter (day, month, year)

- Supports Alarm registers (second, minute, hour, day, month, year)

- Selectable 12-hour or 24-hour mode

- Automatic leap year recognition

- Supports periodic time tick interrupt with 8 period options 1/128, 1/64, 1/32, 1/16, 1/8, 1/4, 1/2 and 1 second

- Supports wake-up function

### PWM/Capture

- Up to four built-in 16-bit PWM generators providing eight PWM outputs or four complementary paired PWM outputs

- Each PWM generator equipped with one clock source selector, one clock divider, one

8-bit prescaler and one Dead-Zone generator for complementary paired PWM

- Up to eight 16-bit digital capture timers (shared with PWM timers) providing eight rising/falling capture inputs

- Supports Capture interrupt

### UART

- Up to three UART controllers

- UART ports with flow control (TXD, RXD, CTS and RTS)

- UART0 with 64-byte FIFO is for high speed

- UART1/2(optional) with 16-byte FIFO for standard device

- Supports IrDA (SIR) and LIN function

- Supports RS-485 9-bit mode and direction control

- Programmable baud-rate generator up to 1/16 system clock

- Supports PDMA mode

## SPI

- Up to four sets of SPI controllers

- The maximum SPI clock rate of Master can up to 36 MHz (chip working at 5V)

- The maximum SPI clock rate of Slave can up to 18 MHz (chip working at 5V)

- Supports SPI Master/Slave mode

- Full duplex synchronous serial data transfer

- Variable length of transfer data from 8 to 32 bits

- MSB or LSB first data transfer

- Rx and Tx on both rising or falling edge of serial clock independently

- Two slave/device select lines in Master mode, and one slave/device select line in Slave mode

- Supports Byte Suspend mode in 32-bit transmission

- Supports PDMA mode

- Supports three wire, no slave select signal, bi-direction interface

I<sup>2</sup>C

- Up to two sets of I<sup>2</sup>C device

- Master/Slave mode

- Bidirectional data transfer between masters and slaves

- Multi-master bus (no central master)

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus

- Serial clock synchronization allowing devices with different bit rates to communicate via one serial bus

- Serial clock synchronization used as a handshake mechanism to suspend and resume serial transfer

- Programmable clocks allowing for versatile rate control

- Supports multiple address recognition (four slave address with mask option)

- Supports wake-up function

# I<sup>2</sup>S

- Interface with external audio CODEC

- Operate as either Master or Slave mode

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Supports mono and stereo audio data

- Supports I<sup>2</sup>S and MSB justified data format

- Provides two 8 word FIFO data buffers, one for transmitting and the other for receiving

- Generates interrupt requests when buffer levels cross a programmable boundary

- Supports two DMA requests, one for transmitting and the other for receiving

### PS/2 Device

- Host communication inhibit and request to send detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- Software override bus

- EBI (External bus interface)

- Accessible space: 64 KB in 8-bit mode or 128 KB in 16-bit mode

- Supports 8-/16-bit data width

- Supports byte write in 16-bit data width mode

- USB 2.0 Full-Speed Device

- One set of USB 2.0 FS Device 12 Mbps

- On-chip USB Transceiver

- Provides 1 interrupt source with 4 interrupt events

- Supports Control, Bulk In/Out, Interrupt and Isochronous transfers

- Auto suspend function when no bus signaling for 3 ms

- Provides 6 programmable endpoints

- Includes 512 Bytes internal SRAM as USB buffer

- Provides remote wake-up capability

## ADC

- 12-bit SAR ADC with 760 kSPS

- Up to 8-ch single-end input or 4-ch differential input

- Single scan/single cycle scan/continuous scan

- Each channel with individual result register

- Scan on enabled channels

- Threshold voltage detection

- Conversion started by software programming or external input

- Supports PDMA mode

- Analog Comparator

| SPS  | Samples per Second                         |  |  |  |

|------|--------------------------------------------|--|--|--|

| TDES | riple Data Encryption Standard             |  |  |  |

| TMR  | mer Controller                             |  |  |  |

| UART | niversal Asynchronous Receiver/Transmitter |  |  |  |

| UCID | Jnique Customer ID                         |  |  |  |

| USB  | Universal Serial Bus                       |  |  |  |

| WDT  | Watchdog Timer                             |  |  |  |

| WWDT | Window Watchdog Timer                      |  |  |  |

Table 3-1 List of Abbreviations

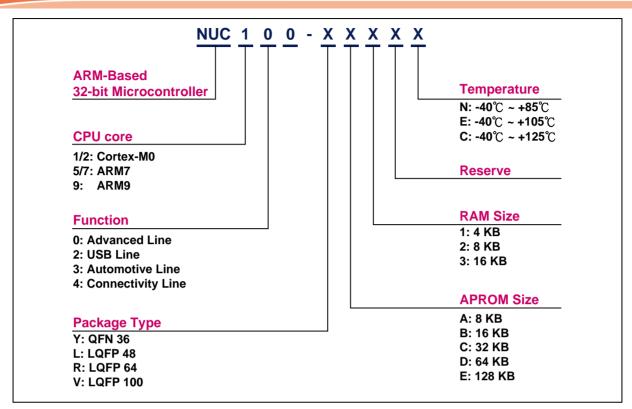

Figure 4-1 NuMicro® NUC100 Series Selection Code

| Pin No.         |                |                |          |          |                                                       |  |  |  |  |

|-----------------|----------------|----------------|----------|----------|-------------------------------------------------------|--|--|--|--|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name | Pin Type | Description                                           |  |  |  |  |

|                 |                |                | T2EX     | ı        | Timer2 external capture input pin.                    |  |  |  |  |

|                 |                |                | nWRL     | 0        | EBI low byte write enable output pin                  |  |  |  |  |

|                 |                |                | PB.3     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

|                 |                |                | CTS0     | ı        | Clear to Send input pin for UART0.                    |  |  |  |  |

| 35              | 20             | 16             | ТЗЕХ     | 1        | Timer3 external capture input pin.                    |  |  |  |  |

|                 |                |                | SC2CD    | ı        | SmartCard2 card detect pin.                           |  |  |  |  |

|                 |                |                | nWRH     | 0        | EBI high byte write enable output pin                 |  |  |  |  |

| 36              | 21             |                | PD.6     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 37              | 22             |                | PD.7     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

|                 |                |                | PD.14    | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 38              | 23             |                | RXD2     | ı        | Data receiver input pin for UART2.                    |  |  |  |  |

| 00              | 0.4            |                | PD.15    | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 39              | 24             |                | TXD2     | 0        | Data transmitter output pin for UART2.                |  |  |  |  |

| 40              |                |                | PC.5     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 40              |                |                | MOSI01   | I/O      | 2 <sup>nd</sup> SPI0 MOSI (Master Out, Slave In) pin. |  |  |  |  |

| 41              |                |                | PC.4     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 41              |                |                | MISO01   | I/O      | 2 <sup>nd</sup> SPI0 MISO (Master In, Slave Out) pin. |  |  |  |  |

|                 |                | 17             | PC.3     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 42              | 25             |                | MOSI00   | 1/0      | 1 <sup>st</sup> SPI0 MOSI (Master Out, Slave In) pin. |  |  |  |  |

|                 |                |                | I2SDO    | 0        | I <sup>2</sup> S data output.                         |  |  |  |  |

|                 |                |                | PC.2     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 43              | 26             | 18             | MISO00   | 1/0      | 1 <sup>st</sup> SPI0 MISO (Master In, Slave Out) pin. |  |  |  |  |

|                 |                |                | I2SDI    | I        | I <sup>2</sup> S data input.                          |  |  |  |  |

|                 |                | 19             | PC.1     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 44              | 27             |                | SPICLK0  | 1/0      | SPI0 serial clock pin.                                |  |  |  |  |

|                 |                |                | I2SBCLK  | I/O      | I <sup>2</sup> S bit clock pin.                       |  |  |  |  |

|                 | 28             | 20             | PC.0     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 45              |                |                | SPISS00  | 1/0      | 1 <sup>st</sup> SPI0 slave select pin.                |  |  |  |  |

|                 |                |                | I2SLRCLK | I/O      | I <sup>2</sup> S left right channel clock.            |  |  |  |  |

| 46              |                |                | PE.6     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 47              | 29             | 21             | PE.5     | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 41              | 20             |                | PWM5     | I/O      | PWM5 output/Capture input.                            |  |  |  |  |

| Pin No.         |                |                |          |                                      |                                                       |                                  |  |  |  |

|-----------------|----------------|----------------|----------|--------------------------------------|-------------------------------------------------------|----------------------------------|--|--|--|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name | Pin Type                             | Description                                           |                                  |  |  |  |

|                 |                |                | T1EX     | I Timer1 external capture input pin. |                                                       |                                  |  |  |  |

|                 |                |                | PB.11    | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 48              | 30             | 22             | TM3      | I/O                                  | Timer3 event counter input / toggle output.           |                                  |  |  |  |

|                 |                |                | PWM4     | 1/0                                  | PWM4 output/Capture input.                            |                                  |  |  |  |

|                 | 31             | 23             | PB.10    | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 49              | 31             | 23             | TM2      | 1/0                                  | Timer2 event counter input / toggle output.           |                                  |  |  |  |

|                 |                |                | SPISS01  | 1/0                                  | 2 <sup>nd</sup> SPI0 slave select pin.                |                                  |  |  |  |

|                 | 32             | 24             | PB.9     | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 50              | 32             | 24             | TM1      | 1/0                                  | Timer1 event counter input / toggle output.           |                                  |  |  |  |

|                 |                |                | SPISS11  | 1/0                                  | 2 <sup>nd</sup> SPI1 slave select pin.                |                                  |  |  |  |

| 51              |                |                | PE.4     | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 52              |                |                | PE.3     | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 53              |                |                | PE.2     | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 54              |                |                | PE.1     | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 34              |                |                | PWM7     | I/O                                  | PWM7 output/Capture input.                            |                                  |  |  |  |

|                 |                |                | PE.0     | I/O                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 55              |                |                | PWM6     | I/O                                  | PWM6 output/Capture input.                            |                                  |  |  |  |

| 5.0             |                |                | PC.13    | I/O                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 56              |                |                | MOSI11   | 1/0                                  | 2 <sup>nd</sup> SPI1 MOSI (Master Out, Slave In) pin. |                                  |  |  |  |

| 57              |                |                | PC.12    | I/O                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 57              |                |                | MISO11   | I/O                                  | 2 <sup>nd</sup> SPI1 MISO (Master In, Slave Out) pin. |                                  |  |  |  |

| 58              | 33             | 22             |          | PC.11                                | 1/0                                                   | General purpose digital I/O pin. |  |  |  |

| 56              | 33             |                | MOSI10   | 1/0                                  | 1 <sup>st</sup> SPI1 MOSI (Master Out, Slave In) pin. |                                  |  |  |  |

| 59              | 34             |                | PC.10    | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 59              | 34             |                | MISO10   | 1/0                                  | 1 <sup>st</sup> SPI1 MISO (Master In, Slave Out) pin. |                                  |  |  |  |

|                 | 35             |                | PC.9     | 1/0                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 60              |                |                | SPICLK1  | 1/0                                  | SPI1 serial clock pin.                                |                                  |  |  |  |

|                 | 36             |                | PC.8     | I/O                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 61              |                |                | SPISS10  | 1/0                                  | 1 <sup>st</sup> SPI1 slave select pin.                |                                  |  |  |  |

|                 |                |                | MCLK     | 0                                    | EBI external clock output pin                         |                                  |  |  |  |

| 00              | 07             | 0.5            | PA.15    | I/O                                  | General purpose digital I/O pin.                      |                                  |  |  |  |

| 62              | 37             | 25             | PWM3     | 1/0                                  | PWM output/Capture input.                             |                                  |  |  |  |

| Pin No.         |                |                |           |          |                                                       |  |  |  |  |

|-----------------|----------------|----------------|-----------|----------|-------------------------------------------------------|--|--|--|--|

| LQFP<br>100-pin | LQFP<br>64-pin | LQFP<br>48-pin | Pin Name  | Pin Type | Description                                           |  |  |  |  |

|                 |                |                | SC0DAT    | 0        | SmartCard0 data pin.                                  |  |  |  |  |

|                 |                |                | AD10      | I/O      | EBI Address/Data bus bit10                            |  |  |  |  |

|                 |                |                | PA.4      | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

|                 |                | 36             | ADC4      | Al       | ADC4 analog input.                                    |  |  |  |  |

| 75              | 48             |                | SC1PWR    | 0        | SmartCard1 power pin.                                 |  |  |  |  |

|                 |                |                | AD9       | I/O      | EBI Address/Data bus bit9                             |  |  |  |  |

|                 |                |                | PA.5      | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 70              | 40             | 37             | ADC5      | Al       | ADC5 analog input.                                    |  |  |  |  |

| 76              | 49             |                | SC1RST    | 0        | SmartCard1 reset pin.                                 |  |  |  |  |

|                 |                |                | AD8       | I/O      | EBI Address/Data bus bit8                             |  |  |  |  |

|                 |                |                | PA.6      | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 77              | 50             | 38             | ADC6      | Al       | ADC6 analog input.                                    |  |  |  |  |

| 77              | 50             |                | SC1CLK    | I/O      | SmartCard1 clock pin.                                 |  |  |  |  |

|                 |                |                | AD7       | I/O      | EBI Address/Data bus bit7                             |  |  |  |  |

|                 |                |                | PA.7      | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

|                 |                | 20             | ADC7      | Al       | ADC7 analog input.                                    |  |  |  |  |

| 78              | 51             | 39             | SC1DAT    | 0        | SmartCard1 data pin.                                  |  |  |  |  |

|                 |                |                | SPISS21   | I/O      | 2 <sup>nd</sup> SPI2 slave select pin.                |  |  |  |  |

|                 |                |                | AD6       | I/O      | EBI Address/Data bus bit6                             |  |  |  |  |

| 79              |                |                | $V_{REF}$ | AP       | Voltage reference input for ADC.                      |  |  |  |  |

| 80              | 52             | 40             | $AV_{DD}$ | AP       | Power supply for internal analog circuit.             |  |  |  |  |

| 81              |                |                | PD.0      | 1/0      | General purpose digital I/O pin.                      |  |  |  |  |

| 01              |                |                | SPISS20   | 1/0      | 1 <sup>st</sup> SPI2 slave select pin.                |  |  |  |  |

| 82              |                |                | PD.1      | 1/0      | General purpose digital I/O pin.                      |  |  |  |  |

| 02              |                |                | SPICLK2   | 1/0      | SPI2 serial clock pin.                                |  |  |  |  |

| 83              |                |                | PD.2      | 1/0      | General purpose digital I/O pin.                      |  |  |  |  |

| 83              |                |                | MISO20    | 1/0      | 1 <sup>st</sup> SPI2 MISO (Master In, Slave Out) pin. |  |  |  |  |

| 94              |                |                | PD.3      | 1/0      | General purpose digital I/O pin.                      |  |  |  |  |

| 84              |                |                | MOSI20    | I/O      | 1 <sup>st</sup> SPI2 MOSI (Master Out, Slave In) pin. |  |  |  |  |

| 85              |                |                | PD.4      | 1/0      | General purpose digital I/O pin.                      |  |  |  |  |

| 00              |                |                | MISO21    | I/O      | 2 <sup>nd</sup> SPI2 MISO (Master In, Slave Out) pin. |  |  |  |  |

| 96              |                |                | PD.5      | I/O      | General purpose digital I/O pin.                      |  |  |  |  |

| 86              |                |                | MOSI21    | I/O      | 2 <sup>nd</sup> SPI2 MOSI (Master Out, Slave In) pin. |  |  |  |  |

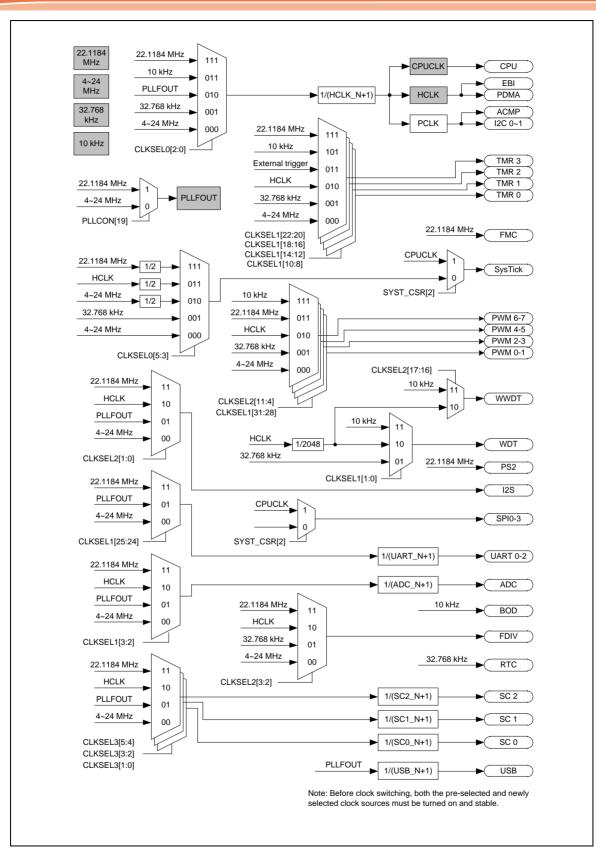

Figure 6-10 Clock Generator Global View Diagram

# 6.3.3 System Clock and SysTick Clock

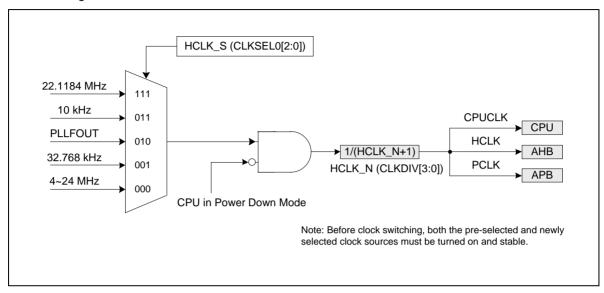

The system clock has 5 clock sources which were generated from clock generator block. The clock source switch depends on the register HCLK\_S (CLKSEL0[2:0]). The block diagram is shown in Figure 6-12.

Figure 6-12 System Clock Block Diagram

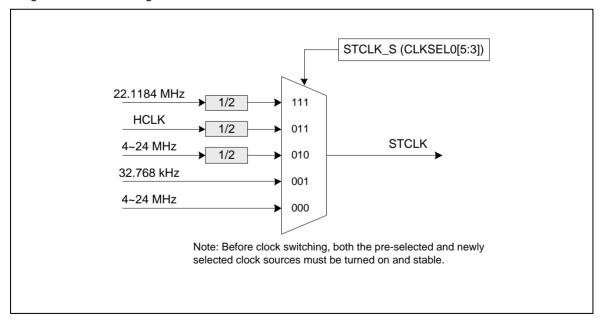

The clock source of SysTick in Cortex®-M0 core can use CPU clock or external clock (SYST\_CSR[2]). If using external clock, the SysTick clock (STCLK) has 5 clock sources. The clock source switch depends on the setting of the register STCLK\_S (CLKSEL0[5:3]). The block diagram is shown in Figure 6-13.

Figure 6-13 SysTick Clock Control Block Diagram

# 6.6 General Purpose I/O (GPIO)

### 6.6.1 Overview

The NuMicro® NUC100 series has up to 84 General Purpose I/O pins to be shared with other function pins depending on the chip configuration. These 84 pins are arranged in 6 ports named as GPIOA, GPIOB, GPIOC, GPIOD, GPIOE and GPIOF. The GPIOA/B/C/D/E port has the maximum of 16 pins and GPIOF port has the maximum of 4 pins. Each of the 84 pins is independent and has the corresponding register bits to control the pin mode function and data.

The I/O type of each of I/O pins can be configured by software individually as input, output, opendrain or Quasi-bidirectional mode. After reset, the I/O mode of all pins are depending on Config0[10] setting. In Quasi-bidirectional mode, I/O pin has a very weak individual pull-up resistor which is about 110~300 K $\Omega$  for V<sub>DD</sub> is from 5.0 V to 2.5 V.

### 6.6.2 Features

- Four I/O modes:

- Quasi-bidirectional

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable by GPx\_TYPE[15:0] in GPx\_MFP[31:16]

- I/O pin configured as interrupt source with edge/level setting

- Configurable default I/O mode of all pins after reset by Config0[10] setting

- If Config[10] is 0, all GPIO pins in input tri-state mode after chip reset

- If Config[10] is 1, all GPIO pins in Quasi-bidirectional mode after chip reset

- I/O pin internal pull-up resistor enabled only in Quasi-bidirectional I/O mode

- Enabling the pin interrupt function will also enable the pin wake-up function.

So the maximum capture frequency will be 1/900ns = 1000 kHz

#### 6.9.2 **Features**

nuvoton

#### 6.9.2.1 PWM Function:

- Up to 2 PWM groups (PWMA/PWMB) to support 8 PWM channels or 4 complementary PWM paired channels

- Each PWM group has two PWM generators with each PWM generator supporting one 8-bit prescaler, two clock divider, two PWM-timers, one Dead-zone generator and two PWM outputs.

- Up to 16-bit resolution

- PWM Interrupt request synchronized with PWM period

- One-shot or Auto-reload mode PWM

- Edge-aligned type or Center-aligned type option

#### 6.9.2.2 Capture Function:

- Timing control logic shared with PWM Generators

- Supports 8 Capture input channels shared with 8 PWM output channels

- Each channel supports one rising latch register (CRLR), one falling latch register (CFLR) and Capture interrupt flag (CAPIFx)

SIR Protocol encoder/decoder. The IrDA SIR Protocol encoder/decoder is half-duplex only. So it cannot transmit and receive data at the same time. The IrDA SIR physical layer specifies a minimum 10ms transfer delay between transmission and reception, and this delay feature must be implemented by software.

The alternate function of UART controllers is LIN (Local Interconnect Network) function. The LIN mode is selected by setting the UA\_FUN\_SEL[1:0] to '01'. In LIN mode, 1 start bit and 8 data bits format with 1 stop bit are required in accordance with the LIN standard.

For NuMicro® NUC100 series, another alternate function of UART controllers is RS-485 9-bit mode, and direction control provided by /RTS pin or can program GPIO (PB.2 for UART0\_nRTS and PB.6 for UART1\_nRTS) to implement the function by software. The RS-485 mode is selected by setting the UA\_FUN\_SEL register to select RS-485 function. The RS-485 transceiver control is implemented using the /RTS control signal from an asynchronous serial port to enable the RS-485 transceiver. In RS-485 mode, many characteristics of the receiving and transmitting are same as UART.

### 6.14.2 Features

- Full duplex, asynchronous communications

- Separates receive / transmit 64/16/16 bytes (UART0/UART1/UART2) entry FIFO for data payloads

- Supports hardware auto flow control/flow control function (CTS, RTS) and programmable RTS flow control trigger level (UART0 and UART1 support)

- Programmable receiver buffer trigger level

- Supports programmable baud-rate generator for each channel individually

- Supports CTS wake-up function (UART0 and UART1 support)

- Supports 7-bit receiver buffer time-out detection function

- UART0/UART1 can through DMA channels to receive/transmit data

- Programmable transmitting data delay time between the last stop and the next start bit by setting UA\_TOR [DLY] register

- Supports break error, frame error, parity error and receive / transmit buffer overflow detect function

- Fully programmable serial-interface characteristics

- Programmable data bit length, 5-, 6-, 7-, 8-bit character

- Programmable parity bit, even, odd, no parity or stick parity bit generation and detection

- Programmable stop bit length, 1, 1.5, or 2 stop bit generation

- IrDA SIR function mode

- Supports 3-/16-bit duration for normal mode

- LIN function mode

- Supports LIN master/slave mode

- Supports programmable break generation function for transmitter

- Supports break detect function for receiver

- RS-485 function mode.

# 6.16 PS/2 Device Controller (PS2D)

## 6.16.1 Overview

The PS/2 device controller provides a basic timing control for PS/2 communication. All communication between the device and the host is managed through the CLK and DATA pins. Unlike PS/2 keyboard or mouse device controller, the receive/transmit code needs to be translated as meaningful code by firmware. The device controller generates the CLK signal after receiving a "Request to Send" state, but host has ultimate control over communication. Data of DATA line sent from the host to the device is read on the rising edge and sent from the device to the host is change after rising edge. A 16 bytes FIFO is used to reduce CPU intervention. Software can select 1 to 16 bytes for a continuous transmission.

### 6.16.2 Features

- Host communication inhibit and Request to Send state detection

- Reception frame error detection

- Programmable 1 to 16 bytes transmit buffer to reduce CPU intervention

- Double buffer for data reception

- Software override bus

# 6.17 I<sup>2</sup>C Serial Interface Controller (I<sup>2</sup>C)

## 6.17.1 Overview

I<sup>2</sup>C is a two-wire, bidirectional serial bus that provides a simple and efficient method of data exchange between devices. The I<sup>2</sup>C standard is a true multi-master bus including collision detection and arbitration that prevents data corruption if two or more masters attempt to control the bus simultaneously.

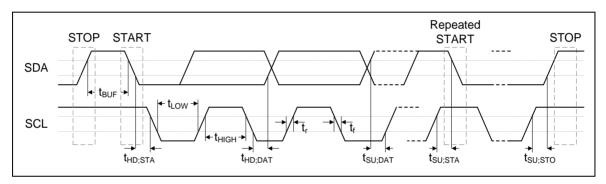

Data is transferred between a Master and a Slave. Data bits transfer on the SCL and SDA lines are synchronously on a byte-by-byte basis. Each data byte is 8-bit long. There is one SCL clock pulse for each data bit with the MSB being transmitted first, and an acknowledge bit follows each transferred byte. Each bit is sampled during the high period of SCL; therefore, the SDA line may be changed only during the low period of SCL and must be held stable during the high period of SCL. A transition on the SDA line while SCL is high is interpreted as a command (START or STOP). Please refer to Figure 6-17 for more detailed I<sup>2</sup>C BUS Timing.

Figure 6-17 I<sup>2</sup>C Bus Timing

The device's on-chip I<sup>2</sup>C logic provides a serial interface that meets the I<sup>2</sup>C bus standard mode specification. The I<sup>2</sup>C port handles byte transfers autonomously. To enable this port, the bit ENS1 in I2CON should be set to '1'. The I<sup>2</sup>C hardware interfaces to the I<sup>2</sup>C bus via two pins: SDA and SCL. Pull-up resistor is needed for I<sup>2</sup>C operation as the SDA and SCL are open drain pins. When I/O pins are used as I<sup>2</sup>C ports, user must set the pins function to I<sup>2</sup>C in advance.

# 6.19 I<sup>2</sup>S Controller (I<sup>2</sup>S)

# 6.19.1 Overview

The I<sup>2</sup>S controller consists of I<sup>2</sup>S protocol to interface with external audio CODEC. Two 8-word deep FIFO for read path and write path respectively and is capable of handling 8-, 16-, 24- and 32-bit word sizes. PDMA controller handles the data movement between FIFO and memory.

### 6.19.2 Features

- Operated as either Master or Slave

- Capable of handling 8-, 16-, 24- and 32-bit word sizes

- Supports Mono and stereo audio data

- Supports I<sup>2</sup>S and MSB justified data format

- Provides two 8-word FIFO data buffers, one for transmitting and the other for receiving

- Generates interrupt requests when buffer levels cross a programmable boundary

- Two PDMA requests, one for transmitting and the other for receiving

# 8.2 DC Electrical Characteristics

( $V_{DD}$ - $V_{SS}$ =5.5 V,  $T_A$  = 25°C,  $F_{OSC}$  = 50 MHz unless otherwise specified.)

| DADAMETER                        | CVM                                 | SPECIFICATION |          |      |      | TEST COMPLETIONS                                                                          |               |            |        |

|----------------------------------|-------------------------------------|---------------|----------|------|------|-------------------------------------------------------------------------------------------|---------------|------------|--------|

| PARAMETER                        | SYM.                                | MIN.          | TYP.     | MAX. | UNIT | TEST CONDITIONS                                                                           |               |            | 5      |

| Operation Voltage                | V <sub>DD</sub>                     | 2.5           |          | 5.5  | V    | V <sub>DD</sub> = 2.                                                                      | 5V ~ 5.5V     | ' up to 50 | MHz    |

| Power Ground                     | V <sub>SS</sub><br>AV <sub>SS</sub> | -0.3          |          |      | V    |                                                                                           |               |            |        |

| LDO Output Voltage               | V <sub>LDO</sub>                    | 1.62          | 1.8      | 1.98 | V    | V <sub>DD</sub> > 2.                                                                      | 5V            |            |        |

| Analog Operating Voltage         | AV <sub>DD</sub>                    |               | $V_{DD}$ |      | V    | When system used analog function, please refer to chap for corresponding analog opvoltage |               | apter 8.4  |        |

|                                  | I <sub>DD1</sub>                    |               | 34       |      | mA   | $V_{DD}$                                                                                  | XTAL          | PLL        | All IP |

| Operating Current                | וטטז                                |               | 34       |      | IIIA | 5.5V                                                                                      | 12 MHz        | V          | V      |

| Normal Run Mode                  | I <sub>DD2</sub>                    |               | 15       |      | mA   | 5.5V                                                                                      | 12 MHz        | V          | Х      |

| at 50 MHz                        | I <sub>DD3</sub>                    |               | 32       |      | mA   | 3.3V                                                                                      | 12 MHz        | V          | V      |

|                                  | I <sub>DD4</sub>                    |               | 14       |      | mA   | 3.3V                                                                                      | 12 MHz        | V          | Х      |

|                                  | 1                                   |               | 8.5      |      | mA   | $V_{DD}$                                                                                  | XTAL          | PLL        | All IP |

| Operating Current                | I <sub>DD5</sub>                    |               | 0.5      |      | IIIA | 5.5V                                                                                      | 12 MHz        | Х          | V      |

| Normal Run Mode                  | I <sub>DD6</sub>                    |               | 3.6      |      | mA   | 5.5V                                                                                      | 12 MHz        | Х          | Х      |

| at 12 MHz                        | I <sub>DD7</sub>                    |               | 7.5      |      | mA   | 3.3V                                                                                      | 12 MHz        | Х          | V      |

|                                  | I <sub>DD8</sub>                    |               | 2.6      |      | mA   | 3.3V                                                                                      | 12 MHz        | Х          | Х      |

|                                  | I <sub>DD9</sub>                    |               | 3.6      |      | mA   | $V_{DD}$                                                                                  | XTAL          | PLL        | All IP |

| Operating Current                |                                     |               |          |      |      | 5.5V                                                                                      | 4 MHz         | Х          | V      |

| Normal Run Mode                  | I <sub>DD10</sub>                   |               | 2        |      | mA   | 5.5V                                                                                      | 4 MHz         | Х          | Х      |

| at 4 MHz                         | I <sub>DD11</sub>                   |               | 2.8      |      | mA   | 3.3V                                                                                      | 4 MHz         | Х          | V      |

|                                  | I <sub>DD12</sub>                   |               | 1.2      |      | mA   | 3.3V                                                                                      | 4 MHz         | Х          | Х      |

|                                  |                                     |               | 141      |      |      | $V_{DD}$                                                                                  | XTAL          | PLL        | All IP |

| Operating Current                | I <sub>DD13</sub>                   |               |          |      | μА   | 5.5V                                                                                      | 32.768<br>kHz | Х          | V      |

| Normal Run Mode<br>at 32.768 kHz | I <sub>DD14</sub>                   |               | 129      |      | μА   | 5.5V                                                                                      | 32.768<br>kHz | Х          | Х      |

|                                  | I <sub>DD15</sub>                   |               | 138      |      | μА   | 3.3V                                                                                      | 32.768<br>kHz | Х          | V      |

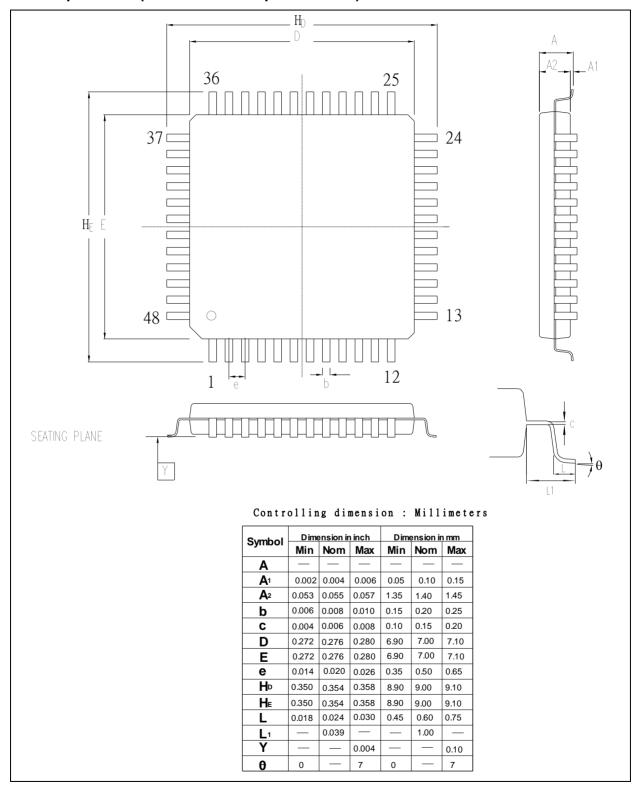

# 9.3 48-pin LQFP (7x7x1.4 mm footprint 2.0 mm)

# **10 REVISION HISTORY**

| Date       | Revision | Description                                                                                                                                                                                                                |  |  |

|------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2014.05.13 | 1.00     | Preliminary version.                                                                                                                                                                                                       |  |  |

|            |          | Reorganized the chapter sequence.                                                                                                                                                                                          |  |  |

| 2015.08.31 | 1.01     | <ol> <li>Added a note in all clock source block diagrams of all peripheral sections<br/>that "Before clock switching, both the pre-selected and newly selected<br/>clock sources must be turned on and stable."</li> </ol> |  |  |

|            |          | <ol> <li>Revised package size of 64-pin LQFP (10x10x1.4 mm footprint 2.0 mm)<br/>in section 9.2.</li> </ol>                                                                                                                |  |  |

|            |          | Updated section 4.1 NuMicro® NUC100/120xxxDN Selection Guide.                                                                                                                                                              |  |  |

| 2017.03.02 | 1.02     | <ol><li>Updated Low Voltage Reset Specification in section 8.4.3.</li></ol>                                                                                                                                                |  |  |

|            |          | Updated Comparator Specification in section 8.4.7.                                                                                                                                                                         |  |  |

# **Important Notice**

Nuvoton Products are neither intended nor warranted for usage in systems or equipment, any malfunction or failure of which may cause loss of human life, bodily injury or severe property damage. Such applications are deemed, "Insecure Usage".

Insecure usage includes, but is not limited to: equipment for surgical implementation, atomic energy control instruments, airplane or spaceship instruments, the control or operation of dynamic, brake or safety systems designed for vehicular use, traffic signal instruments, all types of safety devices, and other applications intended to support or sustain life.

All Insecure Usage shall be made at customer's risk, and in the event that third parties lay claims to Nuvoton as a result of customer's Insecure Usage, customer shall indemnify the damages and liabilities thus incurred by Nuvoton.

Please note that all data and specifications are subject to change without notice.

All the trademarks of products and companies mentioned in this datasheet belong to their respective owners.