Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 4                                                                        |

| Program Memory Size        | 384B (256 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 16 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 2x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f220-i-mc |

|                            |                                                                          |

### 4.0 MEMORY ORGANIZATION

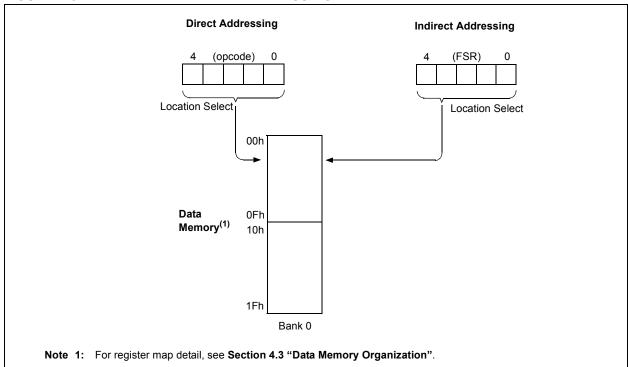

The PIC10F220/222 memories are organized into program memory and data memory. Data memory banks are accessed using the File Select Register (FSR).

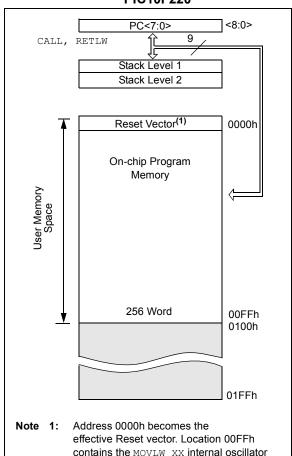

### 4.1 Program Memory Organization for the PIC10F220

The PIC10F220 devices have a 9-bit Program Counter (PC) capable of addressing a 512 x 12 program memory space.

Only the first 256 x 12 (0000h-00FFh) for the PIC10F220 are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wrap-around within the first 256 x 12 space (PIC10F220). The effective Reset vector is at 0000h, (see Figure 4-1). Location 00FFh (PIC10F220) contains the internal clock oscillator calibration value. This value should never be overwritten.

# FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC10F220

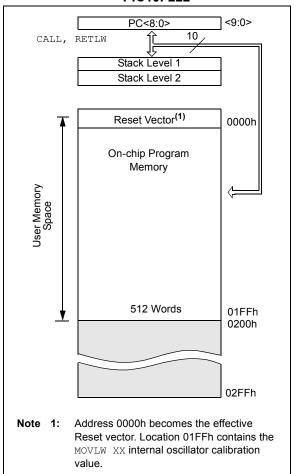

### 4.2 Program Memory Organization for the PIC10F222

The PIC10F222 devices have a 10-bit Program Counter (PC) capable of addressing a 1024 x 12 program memory space.

Only the first 512 x 12 (0000h-01FFh) for the Mem-High are physically implemented (see Figure 4-2). Accessing a location above these boundaries will cause a wrap-around within the first 512 x 12 space (PIC10F222). The effective Reset vector is at 0000h, (see Figure 4-2). Location 01FFh (PIC10F222) contains the internal clock oscillator calibration value. This value should never be overwritten.

FIGURE 4-2: PROGRAM MEMORY MAP

AND STACK FOR THE

PIC10F222

calibration value.

## 4.9 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

### 4.9.1 INDIRECT ADDRESSING

- · Register file 09 contains the value 10h

- · Register file 0A contains the value 0Ah

- · Load the value 09 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 0A)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using Indirect addressing is shown in Example 4-1.

# EXAMPLE 4-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT   | MOVLW MOVWF CLRF INCF BTFSC | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4 | ;initialize pointer ;to RAM ;clear INDF ;register ;inc pointer ;all done? |

|--------|-----------------------------|---------------------------------------|---------------------------------------------------------------------------|

|        | GOTO                        | NEXT                                  | ;NO, clear next                                                           |

| CONTIN | IUE                         |                                       |                                                                           |

|        | :                           |                                       | ;YES, continue                                                            |

|        | :                           |                                       |                                                                           |

|        |                             |                                       |                                                                           |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**Note:** Do not use banking. FSR <7:5> are unimplemented and read as '1's.

### FIGURE 4-6: DIRECT/INDIRECT ADDRESSING

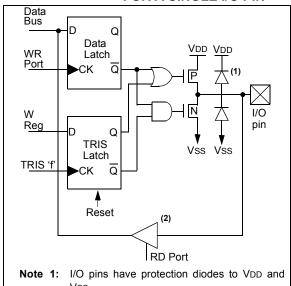

#### 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all

#### 5.1 **GPIO**

GPIO is an 8-bit I/O register. Only the low-order 4 bits are used (GP<3:0>). Bits 7 through 4 are unimplemented and read as '0's. Please note that GP3 is an input only pin. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not individually pin selectable. If GP3/ MCLR is configured as MCLR, a weak pull-up can be enabled via the Configuration Word. Configuring GP3 as MCLR disables the wake-up on change function for this pin.

#### 5.2 **TRIS Registers**

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input only, and the GP2/T0CKI/ FOSC4 pin, which may be controlled by various registers. See Table 5-1.

A read of the ports reads the pins, not the Note: output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

#### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3, which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

FIGURE 5-1: **EQUIVALENT CIRCUIT** FOR A SINGLE I/O PIN

Vss

2: See Table 3-1 for buffer type.

**TABLE 5-1:** ORDER OF PRECEDENCE FOR PIN FUNCTIONS

| Priority | GP0       | GP1       | GP2       | GP3  |

|----------|-----------|-----------|-----------|------|

| 1        | AN0       | AN1       | FOSC4     | MCLR |

| 2        | TRIS GPIO | TRIS GPIO | T0CKI     | _    |

| 3        | _         | -         | TRIS GPIO | _    |

**TABLE 5-2:** REQUIREMENTS TO MAKE PINS AVAILABLE IN DIGITAL MODE

| Bit   | GP0 | GP1 | GP2 | GP3 |

|-------|-----|-----|-----|-----|

| FOSC4 | _   | _   | 0   | _   |

| T0CS  | _   | _   | 0   | _   |

| ANS1  | _   | 0   | _   | _   |

| ANS0  | 0   | _   | _   | _   |

| MCLRE | _   | _   | _   | 0   |

— = Condition of bit will have no effect on the setting of the pin to Digital mode.

# PIC10F220/222

NOTES:

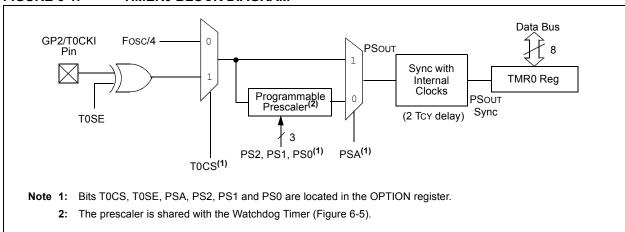

## 6.0 TMR0 MODULE AND TMR0 REGISTER

The Timer0 module has the following features:

- 8-bit timer/counter register, TMR0

- · Readable and writable

- 8-bit software programmable prescaler

- · Internal or external clock select:

- Edge select for external clock

Figure 6-1 is a simplified block diagram of the Timer0 module.

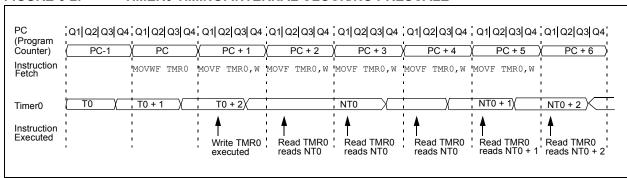

Timer mode is selected by clearing the TOCS bit (OPTION<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without prescaler). If TMR0 register is written, the increment is inhibited for the following two cycles (Figure 6-2 and Figure 6-3). The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the TOCS bit (OPTION<5>). In this mode, Timer0 will increment either on every rising or falling edge of pin TOCKI. The TOSE bit (OPTION<4>) determines the source edge. Clearing the TOSE bit selects the rising edge. Restrictions on the external clock input are discussed in detail in Section 6.1 "Using Timer0 With An External Clock".

The prescaler may be used by either the Timer0 module or the Watchdog Timer, but not both. The prescaler assignment is controlled in software by the control bit PSA (OPTION<3>). Clearing the PSA bit will assign the prescaler to Timer0. The prescaler is not readable or writable. When the prescaler is assigned to the Timer0 module, prescale values of 1:2, 1:4, 1:256 are selectable. **Section 6.2 "Prescaler"** details the operation of the prescaler.

A summary of registers associated with the Timer0 module is found in Table 6-1.

FIGURE 6-1: TIMERO BLOCK DIAGRAM

#### FIGURE 6-2: TIMER0 TIMING: INTERNAL CLOCK/NO PRESCALE

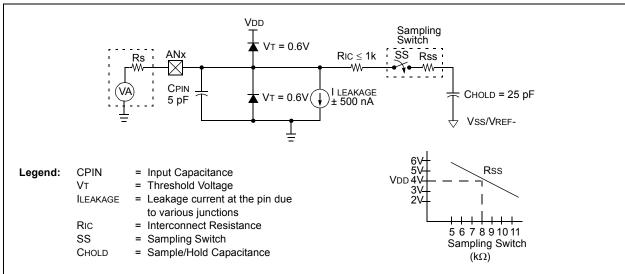

### 7.9 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 7-1. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-1. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### **EQUATION 7-1: ACQUISITION TIME EXAMPLE**

Assumptions:  $Temperature = 50^{\circ}C \text{ and external impedance of } 10 \text{ k}\Omega 5.0 \text{V VDD}$  Tacq = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF  $= 2 \mu s + TC + [(Temperature - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$ Solving for Tc:  $Tc = CHOLD (RIC + RSS + RS) \ln(1/512)$   $= -25pF (l k\Omega + 7 k\Omega + 10 k\Omega) \ln(0.00196)$   $= 2.81 \mu s$ Therefore:  $Tacq = 2 \mu s + 2.81 \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

Note 1: The charge holding capacitor (CHOLD) is not discharged after each conversion.

2: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

### FIGURE 7-1: ANALOG INPUT MODULE

$= 6.06 \mu s$

### PIC10F220/222

TABLE 9-2: INSTRUCTION SET SUMMARY

| Mnem   | onic, | Description                  |                  | 12-Bit Opcode |      |      | Status   | Notes |

|--------|-------|------------------------------|------------------|---------------|------|------|----------|-------|

| Opera  |       | Description                  | Cycles           | MSb           |      | LSb  | Affected | Notes |

| ADDWF  | f, d  | Add W and f                  | 1                | 0001          | 11df | ffff | C,DC,Z   | 1,2,4 |

| ANDWF  | f, d  | AND W with f                 | 1                | 0001          | 01df | ffff | Z        | 2,4   |

| CLRF   | f     | Clear f                      | 1                | 0000          | 011f | ffff | Z        | 4     |

| CLRW   | _     | Clear W                      | 1                | 0000          | 0100 | 0000 | Z        |       |

| COMF   | f, d  | Complement f                 | 1                | 0010          | 01df | ffff | Z        |       |

| DECF   | f, d  | Decrement f                  | 1                | 0000          | 11df | ffff | Z        | 2,4   |

| DECFSZ | f, d  | Decrement f, Skip if 0       | 1 <sup>(2)</sup> | 0010          | 11df | ffff | None     | 2,4   |

| INCF   | f, d  | Increment f                  | 1                | 0010          | 10df | ffff | Z        | 2,4   |

| INCFSZ | f, d  | Increment f, Skip if 0       | 1 <sup>(2)</sup> | 0011          | 11df | ffff | None     | 2,4   |

| IORWF  | f, d  | Inclusive OR W with f        | 1                | 0001          | 00df | ffff | Z        | 2,4   |

| MOVF   | f, d  | Move f                       | 1                | 0010          | 00df | ffff | Z        | 2,4   |

| MOVWF  | f     | Move W to f                  | 1                | 0000          | 001f | ffff | None     | 1,4   |

| NOP    | -     | No Operation                 | 1                | 0000          | 0000 | 0000 | None     |       |

| RLF    | f, d  | Rotate left f through Carry  | 1                | 0011          | 01df | ffff | С        | 2,4   |

| RRF    | f, d  | Rotate right f through Carry | 1                | 0011          | 00df | ffff | С        | 2,4   |

| SUBWF  | f, d  | Subtract W from f            | 1                | 0000          | 10df | ffff | C,DC,Z   | 1,2,4 |

| SWAPF  | f, d  | Swap f                       | 1                | 0011          | 10df | ffff | None     | 2,4   |

| XORWF  | f, d  | Exclusive OR W with f        | 1                | 0001          | 10df | ffff | Z        | 2,4   |

|        |       | BIT-ORIENTED FILE REGISTE    | R OPERA          | ATIONS        |      |      |          |       |

| BCF    | f, b  | Bit Clear f                  | 1                | 0100          | bbbf | ffff | None     | 2,4   |

| BSF    | f, b  | Bit Set f                    | 1                | 0101          | bbbf | ffff | None     | 2,4   |

| BTFSC  | f, b  | Bit Test f, Skip if Clear    | 1 <sup>(2)</sup> | 0110          | bbbf | ffff | None     |       |

| BTFSS  | f, b  | Bit Test f, Skip if Set      | 1 <sup>(2)</sup> | 0111          | bbbf | ffff | None     |       |

|        |       | LITERAL AND CONTROL O        | PERATION         | ONS           |      |      |          |       |

| ANDLW  | k     | AND literal with W           | 1                | 1110          | kkkk | kkkk | Ζ        |       |

| CALL   | k     | Call subroutine              | 2                | 1001          | kkkk | kkkk | None     | 1     |

| CLRWDT | k     | Clear Watchdog Timer         | 1                | 0000          | 0000 | 0100 | TO, PD   |       |

| GOTO   | k     | Unconditional branch         | 2                | 101k          | kkkk | kkkk | None     |       |

| IORLW  | k     | Inclusive OR Literal with W  | 1                | 1101          | kkkk | kkkk | Z        |       |

| MOVLW  | k     | Move Literal to W            | 1                | 1100          | kkkk | kkkk | None     |       |

| OPTION | _     | Load OPTION register         |                  | 0000          | 0000 | 0010 | None     |       |

| RETLW  | k     | Return, place Literal in W   | 2                | 1000          | kkkk | kkkk | None     |       |

| SLEEP  | _     | Go into standby mode         | 1                | 0000          | 0000 | 0011 | TO, PD   |       |

| TRIS   | f     | Load TRIS register           | 1                | 0000          | 0000 | Offf | None     | 3     |

| XORLW  | k     | Exclusive OR Literal to W    | 1                | 1111          | kkkk | kkkk | Z        |       |

- **Note 1:** The 9th bit of the program counter will be forced to a '0' by any instruction that writes to the PC except for GOTO. See **Section 4.7 "Program Counter"**.

- 2: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

- 3: The instruction TRIS f, where f = 6 causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

- **4:** If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

### 10.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings(†)

| Ambient temperature under bias                                                                                   | 40°C to +125°C            |

|------------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                              | 65°C to +150°C            |

| Voltage on VDD with respect to Vss                                                                               | 0 to +6.5V                |

| Voltage on MCLR with respect to Vss                                                                              | 0 to +13.5V               |

| Voltage on all other pins with respect to Vss                                                                    |                           |

| Total power dissipation <sup>(1)</sup>                                                                           | 800 mW                    |

| Max. current out of Vss pin                                                                                      | 80 mA                     |

| Max. current into VDD pin                                                                                        | 80 mA                     |

| Input clamp current, lik (Vi < 0 or Vi > VDD)                                                                    | ±20 mA                    |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                                                   | ±20 mA                    |

| Max. output current sunk by any I/O pin                                                                          | 25 mA                     |

| Max. output current sourced by any I/O pin                                                                       | 25 mA                     |

| Max. output current sourced by I/O port                                                                          | 75 mA                     |

| Max. output current sunk by I/O port                                                                             | 75 mA                     |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $- \sum IOH$ } + $\sum {(VDD IOL)}$ | ) – Voн) x Ioн} + ∑(Vol x |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### 10.1 DC Characteristics: PIC10F220/222 (Industrial)

| IDC CHARACTERISTICS |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40 \times C \le TA \le +85 ^{\circ}C$ (industrial) |       |                              |                          |                          |                                                                                                              |

|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|--------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|

| Param<br>No.        | Sym  | Characteristic                                                                                                                           | Min   | Typ <sup>(1)</sup>           | Max                      | Units                    | Conditions                                                                                                   |

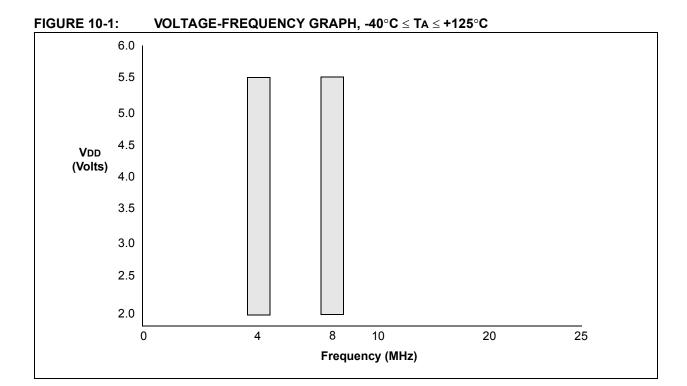

| D001                | Vdd  | Supply Voltage                                                                                                                           | 2.0   |                              | 5.5                      | V                        | See Figure 10-1                                                                                              |

| D002                | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                                                                                | 1.5*  | _                            | -                        | V                        | Device in Sleep mode                                                                                         |

| D003                | VPOR | VDD Start Voltage<br>to ensure Power-on Reset                                                                                            | _     | Vss                          | _                        | V                        |                                                                                                              |

| D004                | SVDD | VDD Rise Rate<br>to ensure Power-on Reset                                                                                                | 0.05* | _                            | _                        | V/ms                     |                                                                                                              |

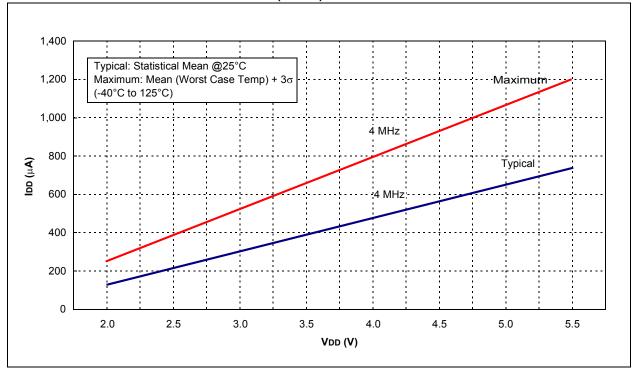

|                     | IDD  | Supply Current <sup>(3)</sup>                                                                                                            |       |                              |                          |                          |                                                                                                              |

| D010                |      |                                                                                                                                          |       | 175<br>0.625<br>250<br>0.800 | 275<br>1.1<br>400<br>1.5 | μΑ<br>mA<br>μΑ<br>mA     | VDD = 2.0V, Fosc = 4 MHz<br>VDD = 5.0V, Fosc = 4 MHz<br>VDD = 2.0V, Fosc = 8 MHz<br>VDD = 5.0V, Fosc = 8 MHz |

|                     | IPD  | Power-down Current <sup>(4)</sup>                                                                                                        |       |                              |                          |                          |                                                                                                              |

| D020                |      |                                                                                                                                          |       | 0.1<br>1                     | 1.2<br>2.4               | μ <b>Α</b><br>μ <b>Α</b> | VDD = 2.0V<br>VDD = 5.0V                                                                                     |

|                     | IWDT | WDT Current <sup>(4)</sup>                                                                                                               |       |                              |                          |                          |                                                                                                              |

| D022                |      |                                                                                                                                          |       | 1.0<br>7                     | 3<br>16                  | μ <b>Α</b><br>μ <b>Α</b> | VDD = 2.0V<br>VDD = 5.0V                                                                                     |

- \* These parameters are characterized but not tested.

- Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

- 2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

- 3: The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

- a) The test conditions for all IDD measurements in active operation mode are:

All I/O pins tri-stated, pulled to Vss, T0CKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

- b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

- **4:** Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss. The peripheral current is the sum of the base IPD and the additional current consumed when the peripheral is enabled.

# PIC10F220/222

TABLE 10-1: PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min | Тур  | Max  | Units |

|-------------|------------------|-----|------|------|-------|

| GP0/GP1     |                  |     |      |      |       |

| 2.0         | -40              | 73K | 105K | 186K | Ω     |

|             | 25               | 73K | 113K | 187K | Ω     |

|             | 85               | 82K | 123K | 190K | Ω     |

|             | 125              | 86K | 132k | 190K | Ω     |

| 5.5         | -40              | 15K | 21K  | 33K  | Ω     |

|             | 25               | 15K | 22K  | 34K  | Ω     |

|             | 85               | 19K | 26k  | 35K  | Ω     |

|             | 125              | 23K | 29K  | 35K  | Ω     |

| GP3         | <u> </u>         |     |      |      |       |

| 2.0         | -40              | 63K | 81K  | 96K  | Ω     |

|             | 25               | 77K | 93K  | 116K | Ω     |

|             | 85               | 82K | 96k  | 116K | Ω     |

|             | 125              | 86K | 100K | 119K | Ω     |

| 5.5         | -40              | 16K | 20k  | 22K  | Ω     |

|             | 25               | 16K | 21K  | 23K  | Ω     |

|             | 85               | 24K | 25k  | 28K  | Ω     |

|             | 125              | 26K | 27K  | 29K  | Ω     |

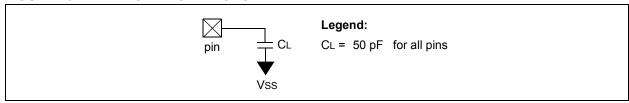

### 10.4 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created following one of the following formats:

- 1. TppS2ppS

- 2. TppS

| Т           |        |

|-------------|--------|

| F Frequency | T Time |

Lowercase subscripts (pp) and their meanings:

| рр  |                    |     |                |

|-----|--------------------|-----|----------------|

| 2   | to                 | mc  | MCLR           |

| ck  | CLKOUT             | osc | Oscillator     |

| су  | Cycle time         | os  | OSC1           |

| drt | Device Reset Timer | t0  | T0CKI          |

| io  | I/O port           | wdt | Watchdog Timer |

Uppercase letters and their meanings:

| S |                          |   |                |

|---|--------------------------|---|----------------|

| F | Fall                     | Р | Period         |

| Н | High                     | R | Rise           |

| 1 | Invalid (high-impedance) | V | Valid          |

| L | Low                      | Z | High-impedance |

### FIGURE 10-2: LOAD CONDITIONS

### TABLE 10-2: CALIBRATED INTERNAL RC FREQUENCIES - PIC10F220/222

| AC CHARACTERISTICS |                                          |                     | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (industrial), $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ (extended)  Operating Voltage VDD range is described in  Section 10.1 "DC Characteristics: PIC10F220/222 (Industrial)". |      |      |      |     |                                                                                                                                                                                       |

|--------------------|------------------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym                                      | Characteristic      | Freq. Tolerance Min Typ† Max Units Conditions                                                                                                                                                                                                                                                                                                    |      |      |      |     | Conditions                                                                                                                                                                            |

| F10                | Fosc                                     | Internal Calibrated | ± 1%                                                                                                                                                                                                                                                                                                                                             | 3.96 | 4.00 | 4.04 | MHz | VDD=3.5V @ 25°C                                                                                                                                                                       |

|                    | INTOSC<br>Frequency <sup>(1, 2, 3)</sup> |                     | ± 2%                                                                                                                                                                                                                                                                                                                                             | 3.92 | 4.00 | 4.08 |     | $2.5V \le VDD \le 5.5V$<br>$0^{\circ}C \le TA \le +85^{\circ}C$ (industrial)                                                                                                          |

|                    |                                          |                     | ± 5%                                                                                                                                                                                                                                                                                                                                             | 3.80 | 4.00 | 4.20 | MHz | $ \begin{array}{l} 2.0V \leq VDD \leq 5.5V \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ (industrial)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \text{ (extended)} \end{array} $ |

- † Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible.  $0.1~\mu F$  and  $0.01~\mu F$  values in parallel are recommended.

- **2:** Under stable VDD conditions.

- 3: Frequency values in this table are doubled when the 8 MHz INTOSC option is selected.

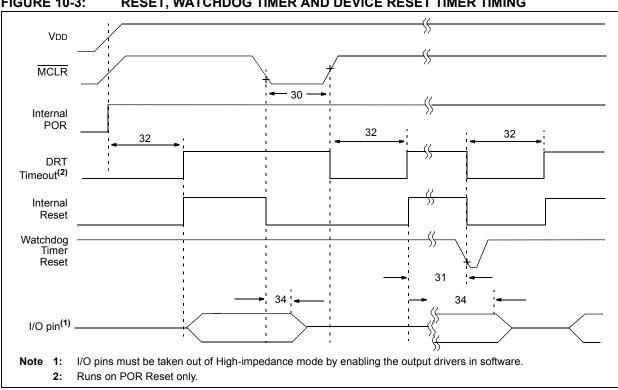

RESET, WATCHDOG TIMER AND DEVICE RESET TIMER TIMING FIGURE 10-3:

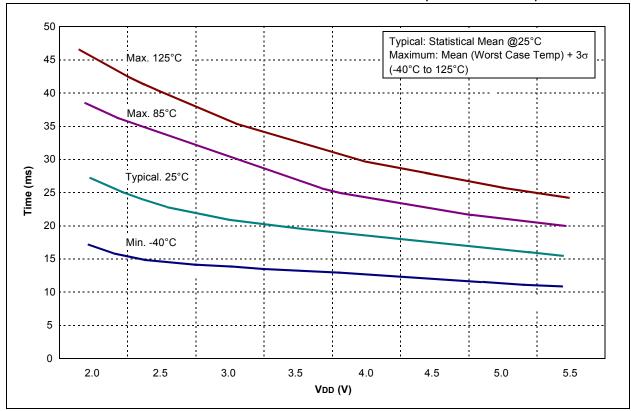

**TABLE 10-3:** RESET, WATCHDOG TIMER AND DEVICE RESET TIMER - PIC10F220/222

| AC CHARACTERISTICS |       |                                                      | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)  Operating Voltage VDD range is described in Section 10.1 "DC Characteristics: PIC10F220/222 (Industrial)" |                    |              |                          |                                                  |

|--------------------|-------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--------------------------|--------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                       | Min                                                                                                                                                                                                                                                                                                 | Typ <sup>(1)</sup> | Max          | Units                    | Conditions                                       |

| 30                 | Тмс   | MCLR Pulse Width (low)                               | 2*<br>5*                                                                                                                                                                                                                                                                                            |                    |              | μ <b>S</b><br>μ <b>S</b> | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |

| 31                 | TWDT  | Watchdog Timer Time-out Period (no prescaler)        | 10<br>10                                                                                                                                                                                                                                                                                            | 18<br>18           | 29<br>31     | ms<br>ms                 | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 32                 | TDRT* | Device Reset Timer Period (standard)                 | 0.600<br>0.600                                                                                                                                                                                                                                                                                      | 1.125<br>1.125     | 1.85<br>1.95 | ms<br>ms                 | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 34                 | Tıoz  | I/O High-impedance from $\overline{\text{MCLR}}$ low |                                                                                                                                                                                                                                                                                                     | _                  | 2*           | μS                       |                                                  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

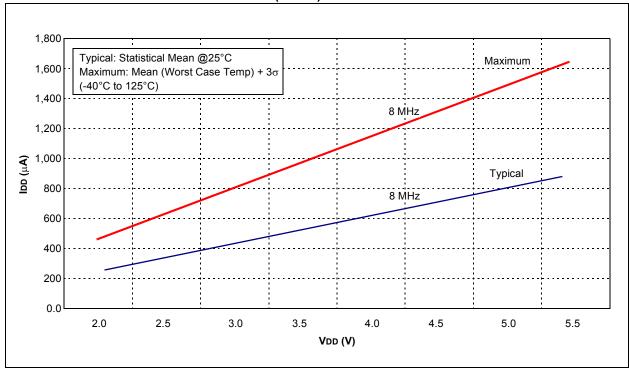

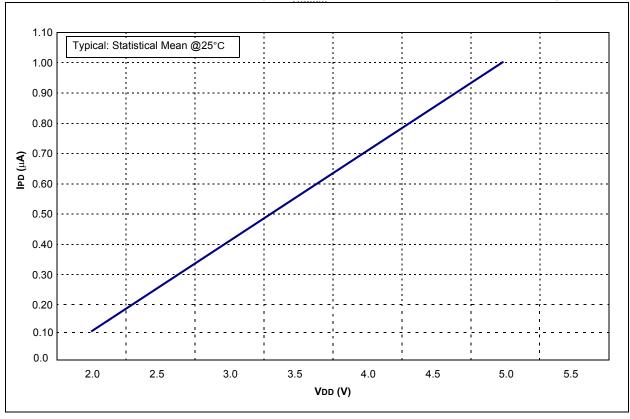

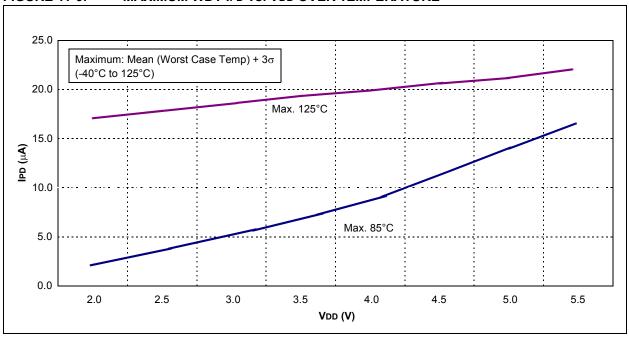

### 11.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES.

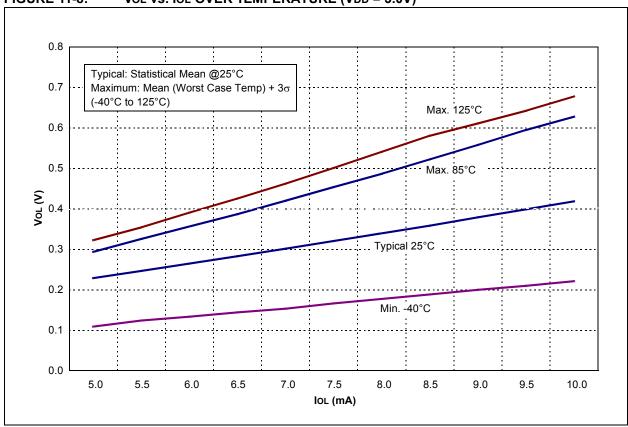

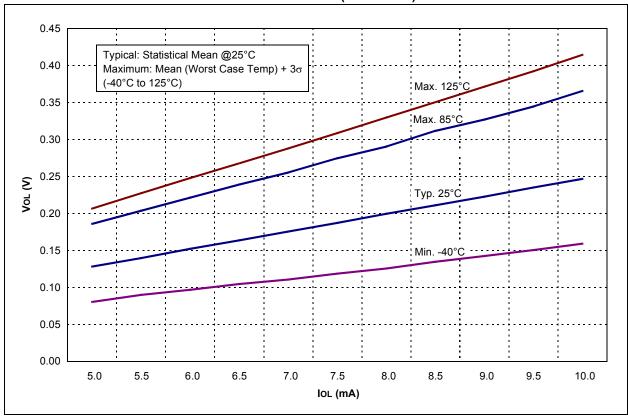

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

FIGURE 11-1: IDD vs. VDD OVER Fosc (4 MHz)

<sup>&</sup>quot;Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

FIGURE 11-2: IDD vs. VDD OVER Fosc (8 MHz)

FIGURE 11-3: TYPICAL IPD vs. VDD (SLEEP MODE, ALL PERIPHERALS DISABLED)

FIGURE 11-6: MAXIMUM WDT IPD vs. VDD OVER TEMPERATURE

FIGURE 11-7: WDT TIME-OUT vs. VDD OVER TEMPERATURE (NO PRESCALER)

FIGURE 11-8: Vol vs. Iol OVER TEMPERATURE (VDD = 3.0V)

FIGURE 11-9: Vol vs. Iol OVER TEMPERATURE (VDD = 5.0V)

### 12.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- · Integrated Development Environment

- MPLAB® X IDE Software

- · Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>TM</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- · Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- · Third-party development tools

### 12.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

#### Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

Project-Based Workspaces:

- · Multiple projects

- · Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- · Built-in support for Bugzilla issue tracker

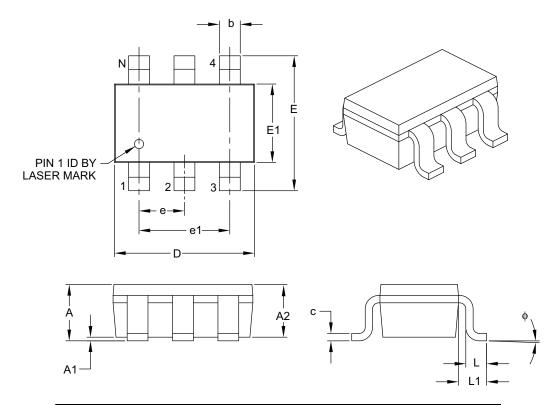

### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          | MILLIMETERS | 3    |  |

|--------------------------|------------------|----------|-------------|------|--|

|                          | Dimension Limits | MIN      | NOM         | MAX  |  |

| Number of Pins           | N                | 6        |             |      |  |

| Pitch                    | е                | 0.95 BSC |             |      |  |

| Outside Lead Pitch       | e1               | 1.90 BSC |             |      |  |

| Overall Height           | Α                | 0.90     | _           | 1.45 |  |

| Molded Package Thickness | A2               | 0.89     | _           | 1.30 |  |

| Standoff                 | A1               | 0.00     | _           | 0.15 |  |

| Overall Width            | E                | 2.20     | _           | 3.20 |  |

| Molded Package Width     | E1               | 1.30     | _           | 1.80 |  |

| Overall Length           | D                | 2.70     | _           | 3.10 |  |

| Foot Length              | L                | 0.10     | _           | 0.60 |  |

| Footprint                | L1               | 0.35     | _           | 0.80 |  |

| Foot Angle               | ф                | 0°       | _           | 30°  |  |

| Lead Thickness           | С                | 0.08     | _           | 0.26 |  |

| Lead Width               | b                | 0.20     | _           | 0.51 |  |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

### **INDEX**

| A                                        |        | M                                                                     |        |

|------------------------------------------|--------|-----------------------------------------------------------------------|--------|

| A/D                                      |        | Memory Organization                                                   | 13     |

| Specifications                           | 60     | Data Memory                                                           |        |

| ADC                                      |        | Program Memory (PIC10F220)                                            |        |

| Internal Sampling Switch (Rss) IMPEDANCE | 32     | Program Memory (PIC10F222)                                            |        |

| Source Impedance                         |        | Microchip Internet Web Site                                           |        |

| ALU                                      |        | MPLAB ASM30 Assembler, Linker, Librarian                              |        |

| Assembler                                |        | MPLAB ICD 2 In-Circuit Debugger                                       |        |

| MPASM Assembler                          | 62     | MPLAB ICE 2000 High-Performance Universal                             | 00     |

| WI ASIVI ASSETTIBLET                     | 02     | In-Circuit Emulator                                                   | 63     |

| В                                        |        | MPLAB Integrated Development Environment Software                     |        |

| Block Diagram                            |        |                                                                       |        |

| On-Chip Reset Circuit                    | 36     | MPLAB PM3 Device Programmer MPLAB REAL ICE In-Circuit Emulator System |        |

| Timer0                                   |        | · · · · · · · · · · · · · · · · · · ·                                 |        |

| TMR0/WDT Prescaler                       |        | MPLINK Object Linker/MPLIB Object Librarian                           | 62     |

|                                          |        | 0                                                                     |        |

| Watchdog Timer                           | 39     | _                                                                     | 4-     |

| Block Diagrams                           | 00     | OPTION Register                                                       |        |

| Analog Input Model                       |        | OSCCAL Register                                                       |        |

| Brown-Out Protection Circuit             | 40     | Oscillator Configurations                                             | 32     |

| C                                        |        | Oscillator Types                                                      | _      |

|                                          |        | HS                                                                    |        |

| C Compilers                              |        | LP                                                                    | 34     |

| MPLAB C18                                |        | P                                                                     |        |

| MPLAB C30                                |        | •                                                                     | _      |

| Carry                                    |        | PIC10F220/222 Device Varieties                                        |        |

| Clocking Scheme                          |        | PICSTART Plus Development Programmer                                  | 64     |

| Code Protection                          | ,      | POR                                                                   |        |

| Configuration Bits                       |        | Device Reset Timer (DRT)                                              |        |

| Customer Change Notification Service     |        | PD                                                                    |        |

| Customer Notification Service            |        | Power-on Reset (POR)                                                  |        |

| Customer Support                         | 75     | TO                                                                    | 39     |

| D                                        |        | Power-down Mode                                                       | 40     |

| _                                        |        | Prescaler                                                             | 27     |

| DC and AC Characteristics                | 65     | Program Counter                                                       | 19     |

| Development Support                      | 61     | •                                                                     |        |

| Digit Carry                              | 9      | Q                                                                     |        |

| E                                        |        | Q cycles                                                              | 1′     |

| _                                        |        | D                                                                     |        |

| Errata                                   | 3      | R                                                                     |        |

| F                                        |        | Reader Response                                                       | 76     |

|                                          |        | Read-Modify-Write                                                     | 23     |

| Family of Devices                        |        | Register File Map                                                     |        |

| PIC10F22X                                | 5      | PIC10F220                                                             | 14     |

| FSR                                      | 20     | PIC10F222                                                             | 14     |

| G                                        |        | Registers                                                             |        |

| •                                        |        | Special Function                                                      | 14     |

| GPIO                                     | 21     | Reset                                                                 | 33     |

| 1                                        |        | Reset on Brown-Out                                                    | 40     |

| 1                                        |        |                                                                       |        |

| I/O Interfacing                          | 21     | <b>S</b>                                                              |        |

| I/O Ports                                |        | Sleep 3                                                               | 33, 40 |

| I/O Programming Considerations           | 23     | Software Simulator (MPLAB SIM)                                        |        |

| ID Locations                             | 33, 41 | Special Features of the CPU                                           | 33     |

| INDF                                     | 20     | Special Function Registers                                            |        |

| Indirect Data Addressing                 | 20     | Stack                                                                 |        |

| Instruction Cycle                        | 11     | STATUS Register                                                       |        |

| Instruction Flow/Pipelining              | 11     | _                                                                     | -, -   |

| Instruction Set Summary                  |        | T                                                                     |        |

| Internal Sampling Switch (RSS) IMPEDANCE |        | Timer0                                                                |        |

| Internet Address                         |        | Timer0                                                                | 25     |

|                                          | -      | Timer0 (TMR0) Module                                                  |        |

| L                                        |        | TMR0 with External Clock                                              |        |

| Loading of PC                            | 19     | Timing Parameter Symbology and Load Conditions                        |        |

| •                                        | -      | TRIS Registers                                                        |        |

|                                          |        | Trao registers                                                        | 2      |