Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

|                            |                                                                           |

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 4                                                                         |

| Program Memory Size        | 384B (256 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 2x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f220t-e-ot |

#### **Table of Contents**

| 1.0   | General Description                         | 5  |

|-------|---------------------------------------------|----|

| 2.0   | Device Varieties                            | 7  |

| 3.0   | Architectural Overview                      | 9  |

| 4.0   | Memory Organization                         | 13 |

| 5.0   | I/O Port                                    |    |

| 6.0   | TMR0 Module and TMR0 Register               | 25 |

| 7.0   | Analog-to-Digital (A/D) converter           | 29 |

| 8.0   | Special Features Of The CPU                 | 33 |

| 9.0   | Instruction Set Summary                     | 43 |

| 10.0  | Electrical Characteristics                  | 51 |

| 11.0  | Development Support                         | 61 |

| 12.0  | DC and AC Characteristics Graphs and Charts | 69 |

| 13.0  | Packaging Information                       | 73 |

|       |                                             |    |

| The N | /licrochip Web Site                         | 83 |

| Custo | omer Change Notification Service            | 83 |

| Custo | omer Support                                | 83 |

| Produ | uct Identification System                   | 85 |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include \_literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

| Address | Name               | Bit 7                                  | Bit 6       | Bit 5     | Bit 4     | Bit 3                | Bit 2      | Bit 1          | Bit 0 | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

|---------|--------------------|----------------------------------------|-------------|-----------|-----------|----------------------|------------|----------------|-------|----------------------------------------------|--------|

| 00h     | INDF               | Uses con                               | tents of FS | SR to add | ress data | memory               | (not a phy | ysical registe | r)    | xxxx xxxx                                    | 20     |

| 01h     | TMR0               | 8-Bit Rea                              | I-Time Clo  | ck/Count  | er        |                      |            |                |       | xxxx xxxx                                    | 25     |

| 02h     | PCL <sup>(1)</sup> | Low Orde                               | r 8 Bits of | PC        |           |                      |            |                |       | 1111 1111                                    | 19     |

| 03h     | STATUS             | GPWUF                                  | _           | _         | TO        | PD                   | Z          | DC             | С     | 01 1xxx <sup>(3)</sup>                       | 15     |

| 04h     | FSR                | Indirect D                             | ata Memo    | ry Addres | s Pointer |                      | •          | •              | •     | 111x xxxx                                    | 20     |

| 05h     | OSCCAL             | CAL6                                   | CAL5        | CAL4      | CAL3      | CAL2                 | CAL1       | CAL0           | FOSC4 | 1111 1110                                    | 18     |

| 06h     | GPIO               | _                                      | _           | _         | _         | GP3                  | GP2        | GP1            | GP0   | xxxx                                         | 21     |

| 07h     | ADCON0             | ANS1                                   | ANS0        | _         | _         | CHS1                 | CHS0       | GO/DONE        | ADON  | 11 1100                                      | 30     |

| 08h     | ADRES              | Result of Analog-to-Digital Conversion |             |           |           |                      |            |                |       | xxxx xxxx                                    | 31     |

| N/A     | TRISGPIO           | _                                      | _           | _         | _         | I/O Control Register |            |                |       |                                              | 23     |

| N/A     | OPTION             | GPWU                                   | GPPU        | T0CS      | T0SE      | PSA                  | PS2        | PS1            | PS0   | 1111 1111                                    | 17     |

**Legend:** - = unimplemented, read as '0', x = unknown, u = unchanged, q = value depends on condition.

- Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.7 "Program Counter" for an explanation of how to access these bits.

- 2: Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

- 3: See Table 8-1 for other Reset specific values.

#### 4.4 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect Status bits, see Instruction Set Summary.

#### 4.5 OPTION Register

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

The OPTION register is not memory mapped and is therefore only addressable by executing the  $\mathtt{OPTION}$  instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<7:0> bits.

Note: If TRIS bit is set to '0', the wake-up on change and pull-up functions are disabled for that pin (i.e., note that TRIS overrides Option control of GPPU and GPWU).

**Note:** If the TOCS bit is set to '1', it will override the TRIS function on the TOCKI pin.

#### **REGISTER 4-2: OPTION REGISTER**

| W-1   | W-1  | W-1  | W-1  | W-1 | W-1 | W-1 | W-1   |

|-------|------|------|------|-----|-----|-----|-------|

| GPWU  | GPPU | T0CS | T0SE | PSA | PS2 | PS1 | PS0   |

| bit 7 |      |      |      |     |     |     | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7 **GPWU:** Enable Wake-up On Pin Change bit (GP0, GP1, GP3)

1 = Disabled

0 = Enabled

bit 6 **GPPU:** Enable Weak Pull-ups bit (GP0, GP1, GP3)

1 = Disabled 0 = Enabled

bit 5 TOCS: Timer0 Clock Source Select bit

1 = Transition on T0CKI pin (overrides TRIS on the T0CKI pin)

0 = Transition on internal instruction cycle clock, Fosc/4

bit 4 **T0SE**: Timer0 Source Edge Select bit

1 = Increment on high-to-low transition on the TOCKI pin 0 = Increment on low-to-high transition on the TOCKI pin

bit 3 **PSA:** Prescaler Assignment bit

1 = Prescaler assigned to the WDT

0 = Prescaler assigned to Timer0

bit 2-0 **PS<2:0>:** Prescaler Rate Select bits

| Bit Value                                     | Timer0 Rate WDT Rate                                        |                                                           |  |  |  |  |

|-----------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| 000<br>001<br>010<br>011<br>100<br>101<br>110 | 1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128<br>1:256 | 1:1<br>1:2<br>1:4<br>1:8<br>1:16<br>1:32<br>1:64<br>1:128 |  |  |  |  |

#### 4.6 OSCCAL Register

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal precision 4/8 MHz oscillator. It contains seven bits for calibration.

Note: Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part so it can be reprogrammed correctly later.

After you move in the calibration constant, do not change the value. See **Section 8.2.2 "Internal 4/8 MHz Oscillator"**.

#### REGISTER 4-3: OSCCAL – OSCILLATOR CALIBRATION REGISTER (ADDRESS: 05h)

| R/W-1 | R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| CAL6  | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | FOSC4 |

| bit 7 |       |       |       |       |       |       | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-1 CAL<6:0>: Oscillator Calibration bits

0111111 = Maximum frequency

Ť

•

0000001

0000000 = Center frequency

1111111

•

.

1000000 = Minimum frequency

bit 0 FOSC4: INTOSC/4 Output Enable bit<sup>(1)</sup>

1 = INTOSC/4 output onto GP2 0 = GP2/T0CKI applied to GP2

Note 1: Overrides GP2/T0CKI control registers when enabled.

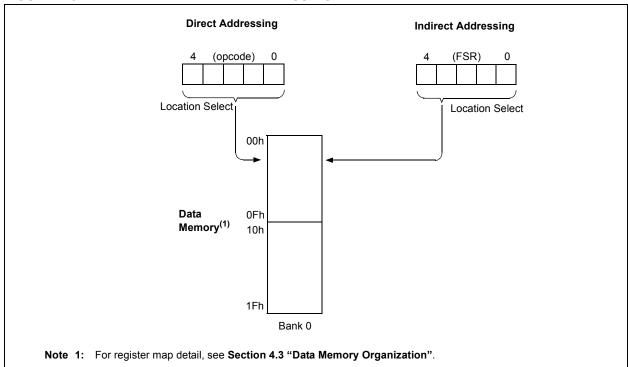

# 4.9 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### 4.9.1 INDIRECT ADDRESSING

- · Register file 09 contains the value 10h

- · Register file 0A contains the value 0Ah

- · Load the value 09 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 0A)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using Indirect addressing is shown in Example 4-1.

# EXAMPLE 4-1: HOW TO CLEAR RAM USING INDIRECT ADDRESSING

| NEXT   | MOVLW MOVWF CLRF INCF BTFSC | 0x10<br>FSR<br>INDF<br>FSR,F<br>FSR,4 | ;initialize pointer ;to RAM ;clear INDF ;register ;inc pointer ;all done? |

|--------|-----------------------------|---------------------------------------|---------------------------------------------------------------------------|

|        | GOTO                        | NEXT                                  | ;NO, clear next                                                           |

| CONTIN | IUE                         |                                       |                                                                           |

|        | :                           |                                       | ;YES, continue                                                            |

|        | :                           |                                       |                                                                           |

|        |                             |                                       |                                                                           |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**Note:** Do not use banking. FSR <7:5> are unimplemented and read as '1's.

#### FIGURE 4-6: DIRECT/INDIRECT ADDRESSING

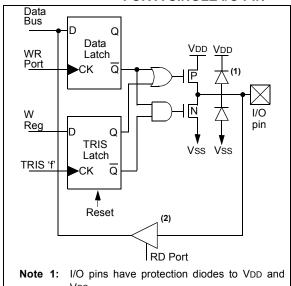

#### 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all

#### 5.1 **GPIO**

GPIO is an 8-bit I/O register. Only the low-order 4 bits are used (GP<3:0>). Bits 7 through 4 are unimplemented and read as '0's. Please note that GP3 is an input only pin. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not individually pin selectable. If GP3/ MCLR is configured as MCLR, a weak pull-up can be enabled via the Configuration Word. Configuring GP3 as MCLR disables the wake-up on change function for this pin.

#### 5.2 **TRIS Registers**

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input only, and the GP2/T0CKI/ FOSC4 pin, which may be controlled by various registers. See Table 5-1.

A read of the ports reads the pins, not the Note: output data latches. That is, if an output driver on a pin is enabled and driven high, but the external system is holding it low, a read of the port will indicate that the pin is

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

#### 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3, which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

FIGURE 5-1: **EQUIVALENT CIRCUIT** FOR A SINGLE I/O PIN

Vss

2: See Table 3-1 for buffer type.

**TABLE 5-1:** ORDER OF PRECEDENCE FOR PIN FUNCTIONS

| Priority | GP0       | GP1       | GP2       | GP3  |

|----------|-----------|-----------|-----------|------|

| 1        | AN0       | AN1       | FOSC4     | MCLR |

| 2        | TRIS GPIO | TRIS GPIO | T0CKI     | _    |

| 3        | _         | -         | TRIS GPIO | _    |

**TABLE 5-2:** REQUIREMENTS TO MAKE PINS AVAILABLE IN DIGITAL MODE

| Bit   | GP0 | GP1 | GP2 | GP3 |

|-------|-----|-----|-----|-----|

| FOSC4 | _   | _   | 0   | _   |

| T0CS  | _   | _   | 0   | _   |

| ANS1  | _   | 0   | _   | _   |

| ANS0  | 0   | _   | _   | _   |

| MCLRE | _   | _   | _   | 0   |

— = Condition of bit will have no effect on the setting of the pin to Digital mode.

TABLE 5-3: SUMMARY OF PORT REGISTERS

| Address | Name     | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2    | Bit 1   | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other Resets |

|---------|----------|-------|-------|-------|-------|--------|----------|---------|-------|-------------------------------|------------------------------|

| N/A     | TRISGPIO | _     | _     | -     | -     | I/O Co | ntrol Re | gisters |       | 1111                          | 1111                         |

| N/A     | OPTION   | GPWU  | GPPU  | T0CS  | T0SE  | PSA    | PS2      | PS1     | PS0   | 1111 1111                     | 1111 1111                    |

| 03h     | STATUS   | GPWUF | _     | _     | TO    | PD     | Z        | DC      | С     | 0001 1xxx                     | q00q quuu(1)                 |

| 06h     | GPIO     | _     | _     | _     | _     | GP3    | GP2      | GP1     | GP0   | xxxx                          | uuuu                         |

**Legend:** Shaded cells not used by PORT registers, read as '0', -= unimplemented, read as '0', x = unknown, u = unchanged, q = depends on condition.

Note 1: If Reset was due to wake-up on pin change, then bit 7 = 1. All other Resets will cause bit 7 = 0.

#### 5.4 I/O Programming Considerations

#### 5.4.1 BIDIRECTIONAL I/O PORTS

Some instructions operate internally as read followed by write operations. The BCF and BSF instructions, for example, read the entire port into the CPU, execute the bit operation and re-write the result. Caution must be used when these instructions are applied to a port where one or more pins are used as input/outputs. For example, a BSF operation on bit 2 of GPIO will cause all eight bits of GPIO to be read into the CPU, bit 2 to be set and the GPIO value to be written to the output latches. If another bit of GPIO is used as a bidirectional I/O pin (say bit 0) and it is defined as an input at this time, the input signal present on the pin itself would be read into the CPU and rewritten to the data latch of this particular pin, overwriting the previous content. As long as the pin stays in the Input mode, no problem occurs. However, if bit 0 is switched into Output mode later on, the content of the data latch may now be unknown.

Example 5-1 shows the effect of two sequential Read-Modify-Write instructions (e.g., BCF, BSF, etc.) on an I/O port.

A pin actively outputting a high or a low should not be driven from external devices at the same time in order to change the level on this pin ("wired-or", "wired-and"). The resulting high output currents may damage the chip.

## EXAMPLE 5-1: I/O PORT READ-MODIFY-WRITE INSTRUCTIONS

```

;Initial GPIO Settings

GPIO<3:2> Inputs

;GPIO<1:0> Outputs

GPIO latch

GPIO pins

BCF

GPIO,

1 ;---- pp01

---- pp11

GPIO,

BCF

0 ;---- pp10

---- pp11

007h;

W.TVOM

---- pp11

TRIS

GPIO

;---- pp10

The user may have expected the pin values to

Note:

be ---- pp00. The second BCF caused GP1

to be latched as the pin value (High).

```

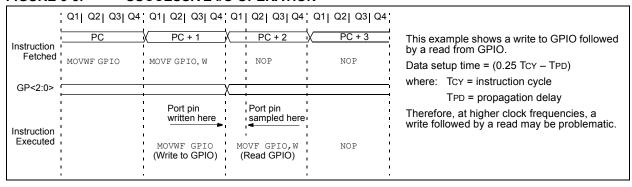

## 5.4.2 SUCCESSIVE OPERATIONS ON I/O PORTS

The actual write to an I/O port happens at the end of an instruction cycle, whereas for reading, the data must be valid at the beginning of the instruction cycle (Figure 5-5). Therefore, care must be exercised if a write followed by a read operation is carried out on the same I/O port. The sequence of instructions should allow the pin voltage to stabilize (load dependent) before the next instruction causes that file to be read into the CPU. Otherwise, the previous state of that pin may be read into the CPU rather than the new state. When in doubt, it is better to separate these instructions with a  ${\tt NOP}$  or another instruction not accessing this I/O port.

FIGURE 5-5: SUCCESSIVE I/O OPERATION

#### 8.2 Oscillator Configurations

#### 8.2.1 OSCILLATOR TYPES

The PIC10F220/222 devices are offered with internal oscillator mode only.

· INTOSC: Internal 4/8 MHz Oscillator

#### 8.2.2 INTERNAL 4/8 MHz OSCILLATOR

The internal oscillator provides a 4/8 MHz (nominal) system clock (see **Section 10.0** "**Electrical Characteristics**" for information on variation over voltage and temperature).

In addition, a calibration instruction is programmed into the last address of memory, which contains the calibration value for the internal oscillator. This location is always uncode protected, regardless of the code-protect settings. This value is programmed as a  $\texttt{MOVLW}\ XX$  instruction where XX is the calibration value and is placed at the Reset vector. This will load the W register with the calibration value upon Reset and the PC will then roll over to the users program at address 0x000. The user then has the option of writing the value to the OSCCAL Register (05h) or ignoring it.

OSCCAL, when written to with the calibration value, will "trim" the internal oscillator to remove process variation from the oscillator frequency.

Note:

Erasing the device will also erase the preprogrammed internal calibration value for the internal oscillator. The calibration value must be read prior to erasing the part so it can be reprogrammed correctly later.

#### 8.3 Reset

The device differentiates between various kinds of Reset:

- · Power-on Reset (POR)

- MCLR Reset during normal operation

- · MCLR Reset during Sleep

- · WDT Time-out Reset during normal operation

- WDT Time-out Reset during Sleep

- · Wake-up from Sleep on pin change

Some registers are not reset in any way, they are unknown on POR and unchanged in any other Reset. Most other registers are reset to "Reset state" on Power-on Reset (POR), MCLR, WDT or Wake-up on pin change Reset during normal operation. They are not affected by a WDT Reset during Sleep or MCLR Reset during Sleep, since these Resets are viewed as resumption of normal operation. The exceptions to this are  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  and GPWUF bits. They are set or cleared differently in different Reset situations. These bits are used in software to determine the nature of Reset. See Table 8-1 for a full description of Reset states of all registers.

TABLE 8-1: RESET CONDITIONS FOR REGISTERS – PIC10F220/222

| Register | Address | Power-on Reset           | MCLR Reset, WDT Time-out, Wake-up On Pin Change, |

|----------|---------|--------------------------|--------------------------------------------------|

| W        | _       | qqqq qqqu <sup>(1)</sup> | qqqq qqqu <sup>(1)</sup>                         |

| INDF     | 00h     | XXXX XXXX                | uuuu uuuu                                        |

| TMR0     | 01h     | XXXX XXXX                | uuuu uuuu                                        |

| PC       | 02h     | 1111 1111                | 1111 1111                                        |

| STATUS   | 03h     | 01 1xxx                  | q00q quuu                                        |

| FSR      | 04h     | 111x xxxx                | 111u uuuu                                        |

| OSCCAL   | 05h     | 1111 1110                | uuuu uuuu                                        |

| GPIO     | 06h     | xxxx                     | uuuu                                             |

| ADCON0   | 07h     | 11 1100                  | 11 1100                                          |

| ADRES    | 08h     | XXXX XXXX                | uuuu uuuu                                        |

| OPTION   | _       | 1111 1111                | 1111 1111                                        |

| TRIS     | _       | 1111                     | 1111                                             |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0', q = value depends on condition.

Note 1: Bits <7:2> of W register contain oscillator calibration values due to MOVLW XX instruction at top of memory.

TABLE 8-2: RESET CONDITION FOR SPECIAL REGISTERS

|                                    | STATUS Addr: 03h | PCL Addr: 02h |  |

|------------------------------------|------------------|---------------|--|

| Power-on Reset                     | 01 1xxx          | 1111 1111     |  |

| MCLR Reset during normal operation | 0u uuuu          | 1111 1111     |  |

| MCLR Reset during Sleep            | 01 Ouuu          | 1111 1111     |  |

| WDT Reset during Sleep             | 00 Ouuu          | 1111 1111     |  |

| WDT Reset normal operation         | 0 <b></b> 0 uuuu | 1111 1111     |  |

| Wake-up from Sleep on pin change   | 11 Ouuu          | 1111 1111     |  |

**Legend:** u = unchanged, x = unknown, - = unimplemented bit, read as '0'.

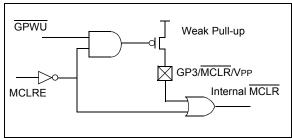

#### 8.3.1 MCLR ENABLE

This Configuration bit, when unprogrammed (left in the '1' state), enables the external MCLR function. When programmed, the MCLR function is tied to the internal VDD and the pin is assigned to be a I/O. See Figure 8-1.

FIGURE 8-1: MCLR SELECT

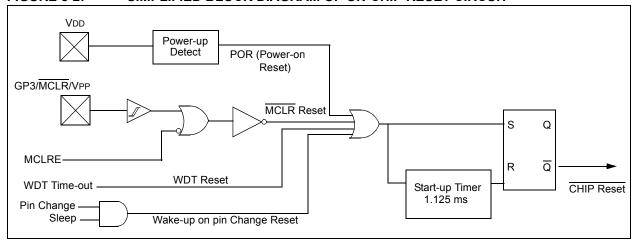

#### 8.4 Power-on Reset (POR)

The PIC10F220/222 devices incorporate an on-chip Power-on Reset (POR) circuitry, which provides an internal chip Reset for most power-up situations.

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the internal POR, program the GP3/MCLR/VPP pin as MCLR and tie through a resistor to VDD, or program the pin as GP3. An internal weak pull-up resistor is implemented using a transistor (refer to Table 10-1 for the pull-up resistor ranges). This will eliminate external RC components usually needed to create a Power-on Reset.

When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature,...) must be met to ensure operation. If these conditions are not met, the devices must be held in Reset until the operating parameters are met.

A simplified block diagram of the on-chip Power-on Reset circuit is shown in Figure 8-2.

The Power-on Reset circuit and the Device Reset Timer (see Section 8.5 "Device Reset Timer (DRT)") circuit are closely related. On power-up, the Reset latch is set and the DRT is reset. The DRT timer begins counting once it detects MCLR to be high. After the time-out period, which is typically 1.125 ms, it will reset the Reset latch and thus end the on-chip Reset signal.

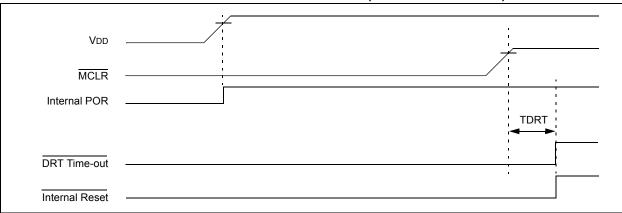

A power-up example where  $\overline{MCLR}$  is held low is shown in Figure 8-3. VDD is allowed to rise and stabilize before bringing  $\overline{MCLR}$  high. The chip will actually come out of Reset TDRT msec after  $\overline{MCLR}$  goes high.

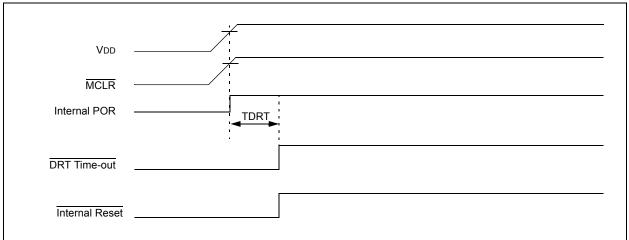

In Figure 8-4, the on-chip Power-on Reset feature is being used (MCLR and VDD are tied together or the pin is programmed to be GP3). The VDD is stable before the Start-up timer times out and there is no problem in getting a proper Reset. However, Figure 8-5 depicts a problem situation where VDD rises too slowly. The time between when the DRT senses that MCLR is high and when MCLR and VDD actually reach their full value, is too long. In this situation, when the start-up timer times out, VDD has not reached the VDD (min) value and the chip may not function correctly. For such situations, we recommend that external RC circuits be used to achieve longer POR delay times (Figure 8-4).

Note: When the devices start normal operation (exit the Reset condition), device operating parameters (voltage, frequency, temperature, etc.) must be met to ensure proper operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information on design considerations related to the use of PIC10F220/222 devices with their short device Reset timer, refer to Application Notes AN522, "Power-Up Considerations" (DS00522) and AN607, "Power-up Trouble Shooting" (DS00607).

FIGURE 8-2: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

FIGURE 8-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

FIGURE 8-4: TIME-OUT SEQUENCE ON POWER-UP (MCLR TIED TO VDD): FAST VDD RISE TIME

| IORWF            | Inclusive OR W with f                                                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] IORWF f,d                                                                                                                                              |

| Operands:        | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                              |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                               |

| Status Affected: | Z                                                                                                                                                              |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f' |

| MOVWF            | Move W to f                                    |

|------------------|------------------------------------------------|

| Syntax:          | [ label ] MOVWF f                              |

| Operands:        | $0 \leq f \leq 31$                             |

| Operation:       | $(W) \rightarrow (f)$                          |

| Status Affected: | None                                           |

| Description:     | Move data from the W register to register 'f'. |

|                  |                                                |

|                  |                                                |

| MOVF             | Move f                                                                                                                                                                                                                                         |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVF f,d                                                                                                                                                                                                                               |  |  |  |  |

| Operands:        | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                                                                                                              |  |  |  |  |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                                                                                              |  |  |  |  |

| Description:     | The contents of register 'f' are moved to destination 'd'. If 'd' is '0', destination is the W register. If 'd' is '1', the destination is file register 'f'. 'd' = 1 is useful as a test of a file register, since status flag Z is affected. |  |  |  |  |

| NOP              | No Operation  |  |  |  |

|------------------|---------------|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |

| Operands:        | None          |  |  |  |

| Operation:       | No operation  |  |  |  |

| Status Affected: | None          |  |  |  |

| Description:     | No operation. |  |  |  |

|                  |               |  |  |  |

|                  |               |  |  |  |

|                  |               |  |  |  |

|                  |               |  |  |  |

| MOVLW            | Move Literal to W                                                                                  |  |  |

|------------------|----------------------------------------------------------------------------------------------------|--|--|

| Syntax:          | [label] MOVLW k                                                                                    |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                |  |  |

| Status Affected: | None                                                                                               |  |  |

| Description:     | The eight-bit literal 'k' is loaded into the W register. The "don't cares" will assembled as '0's. |  |  |

| OPTION           | Load OPTION Register                                              |  |  |

|------------------|-------------------------------------------------------------------|--|--|

| Syntax:          | [ label ] OPTION                                                  |  |  |

| Operands:        | None                                                              |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                          |  |  |

| Status Affected: | None                                                              |  |  |

| Description:     | The content of the W register is loaded into the OPTION register. |  |  |

#### 10.0 ELECTRICAL CHARACTERISTICS

## Absolute Maximum Ratings(†)

| Ambient temperature under bias                                                                                   | 40°C to +125°C            |

|------------------------------------------------------------------------------------------------------------------|---------------------------|

| Storage temperature                                                                                              | 65°C to +150°C            |

| Voltage on VDD with respect to Vss                                                                               | 0 to +6.5V                |

| Voltage on MCLR with respect to Vss                                                                              | 0 to +13.5V               |

| Voltage on all other pins with respect to Vss                                                                    |                           |

| Total power dissipation <sup>(1)</sup>                                                                           | 800 mW                    |

| Max. current out of Vss pin                                                                                      | 80 mA                     |

| Max. current into VDD pin                                                                                        | 80 mA                     |

| Input clamp current, lik (Vi < 0 or Vi > VDD)                                                                    | ±20 mA                    |

| Output clamp current, lok (Vo < 0 or Vo > VDD)                                                                   | ±20 mA                    |

| Max. output current sunk by any I/O pin                                                                          | 25 mA                     |

| Max. output current sourced by any I/O pin                                                                       | 25 mA                     |

| Max. output current sourced by I/O port                                                                          | 75 mA                     |

| Max. output current sunk by I/O port                                                                             | 75 mA                     |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $- \sum IOH$ } + $\sum {(VDD IOL)}$ | ) – Voн) x Ioн} + ∑(Vol x |

<sup>†</sup>NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

## 10.3 DC Characteristics: PIC10F220/222 (Industrial, Extended)

| DC CHA       | RACTI | ERISTICS                                | Standard Operating Conditions (unless otherwise specified)  Operating temperature $-40^{\circ}\text{C} \leq \text{Ta} \leq +85^{\circ}\text{C}$ (industrial) $-40^{\circ}\text{C} \leq \text{Ta} \leq +125^{\circ}\text{C}$ (extended)  Operating voltage VDD range as described in DC specification |      |          |       |                                                                                                           |

|--------------|-------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-----------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym   | Characteristic                          | Min                                                                                                                                                                                                                                                                                                  | Тур† | Max      | Units | Conditions                                                                                                |

|              | VIL   | Input Low Voltage                       |                                                                                                                                                                                                                                                                                                      |      |          |       |                                                                                                           |

|              |       | I/O ports:                              |                                                                                                                                                                                                                                                                                                      |      |          |       |                                                                                                           |

| D030         |       | with TTL buffer                         | Vss                                                                                                                                                                                                                                                                                                  | _    | 0.8      | V     | For all 4.5 ≤ VDD ≤ 5.5V                                                                                  |

| D030A        |       |                                         | Vss                                                                                                                                                                                                                                                                                                  | _    | 0.15 VDD | V     | Otherwise                                                                                                 |

| D031         |       | with Schmitt Trigger<br>buffer          | Vss                                                                                                                                                                                                                                                                                                  | _    | 0.2 VDD  | V     |                                                                                                           |

| D032         |       | MCLR, TOCKI                             | Vss                                                                                                                                                                                                                                                                                                  | _    | 0.2 VDD  | V     |                                                                                                           |

|              | VIH   | Input High Voltage                      |                                                                                                                                                                                                                                                                                                      |      |          |       |                                                                                                           |

|              |       | I/O ports:                              |                                                                                                                                                                                                                                                                                                      | _    |          |       |                                                                                                           |

| D040         |       | with TTL buffer                         | 2.0                                                                                                                                                                                                                                                                                                  | _    | VDD      | V     | $4.5 \le VDD \le 5.5V$                                                                                    |

| D040A        |       |                                         | 0.25 VDD + 0.8                                                                                                                                                                                                                                                                                       | _    | VDD      | V     | Otherwise                                                                                                 |

| D041         |       | with Schmitt Trigger<br>buffer          | 0.8VDD                                                                                                                                                                                                                                                                                               | _    | VDD      | V     | For entire VDD range                                                                                      |

| D042         |       | MCLR, TOCKI                             | 0.8VDD                                                                                                                                                                                                                                                                                               | _    | VDD      | V     |                                                                                                           |

| D070         | IPUR  | GPIO weak pull-up current               | 50                                                                                                                                                                                                                                                                                                   | 250  | 400      | μА    | VDD = 5V, VPIN = VSS                                                                                      |

|              | lıL   | Input Leakage Current <sup>(1)</sup>    |                                                                                                                                                                                                                                                                                                      |      |          |       |                                                                                                           |

| D060         |       | I/O ports                               | _                                                                                                                                                                                                                                                                                                    | ±0.1 | ± 1      | μА    | $\label{eq:VDD}  \mbox{Vss} \leq \mbox{VPIN} \leq \mbox{VDD}, \mbox{ Pin at high-imped-} \\ \mbox{ance} $ |

| D061         |       | GP3/MCLR <sup>(2)</sup>                 | _                                                                                                                                                                                                                                                                                                    | ±0.7 | ± 5      | μА    | Vss ≤ VPIN ≤ VDD                                                                                          |

|              |       | Output Low Voltage                      |                                                                                                                                                                                                                                                                                                      |      |          |       |                                                                                                           |

| D080         |       | I/O ports                               | _                                                                                                                                                                                                                                                                                                    | _    | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V, -40°C to +85°C                                                                  |

| D080A        |       |                                         | _                                                                                                                                                                                                                                                                                                    | _    | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V, -40°C to +125°C                                                                 |

|              |       | Output High Voltage                     | •                                                                                                                                                                                                                                                                                                    |      |          | •     |                                                                                                           |

| D090         |       | I/O ports <sup>(2)</sup>                | VDD - 0.7                                                                                                                                                                                                                                                                                            | _    | _        | V     | IOH = -3.0 mA, VDD = 4.5V, -40°C to +85°C                                                                 |

| D090A        |       |                                         | VDD - 0.7                                                                                                                                                                                                                                                                                            | _    | _        | V     | IOH = -2.5 mA, VDD = 4.5V, -40°C to +125°C                                                                |

|              |       | Capacitive Loading Specs on Output Pins |                                                                                                                                                                                                                                                                                                      |      |          |       |                                                                                                           |

| D101         |       | All I/O pins                            | _                                                                                                                                                                                                                                                                                                    | _    | 50*      | pF    |                                                                                                           |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>\*</sup> These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as coming out of the pin.

<sup>2:</sup> This specification applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

NOTES:

#### 12.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoq® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

#### 12.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

TABLE 13-1: 8-LEAD 2x3 DFN (MC) TOP MARKING

| Part Number    | Marking |

|----------------|---------|

| PIC10F220-I/MC | BJ0     |

| PIC10F220-E/MC | BK0     |

| PIC10F222-I/MC | BL0     |

| PIC10F222-E/MC | BM0     |

TABLE 13-2: 6-LEAD SOT-23 (OT)

PACKAGE TOP MARKING

| Part Number    | Marking |

|----------------|---------|

| PIC10F220-I/OT | 20NN    |

| PIC10F220-E/OT | A0NN    |

| PIC10F222-I/OT | 22NN    |

| PIC10F222-E/OT | A2NN    |

**Note:** NN represents the alphanumeric traceability code.

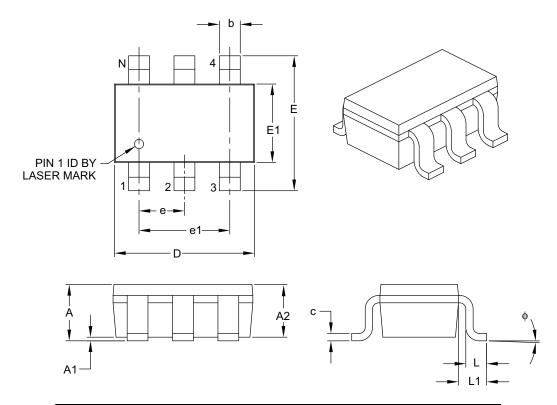

### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |

|--------------------------|------------------|-------------|----------|------|

|                          | Dimension Limits |             | NOM      | MAX  |

| Number of Pins           | N                |             | 6        |      |

| Pitch                    | е                |             | 0.95 BSC |      |

| Outside Lead Pitch       | e1               |             | 1.90 BSC |      |

| Overall Height           | Α                | 0.90        | _        | 1.45 |

| Molded Package Thickness | A2               | 0.89        | _        | 1.30 |

| Standoff                 | A1               | 0.00        | _        | 0.15 |

| Overall Width            | E                | 2.20        | _        | 3.20 |

| Molded Package Width     | E1               | 1.30        | _        | 1.80 |

| Overall Length           | D                | 2.70        | _        | 3.10 |

| Foot Length              | L                | 0.10        | _        | 0.60 |

| Footprint                | L1               | 0.35        | _        | 0.80 |

| Foot Angle               | ф                | 0°          | _        | 30°  |

| Lead Thickness           | С                | 0.08        | -        | 0.26 |

| Lead Width               | b                | 0.20        | _        | 0.51 |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

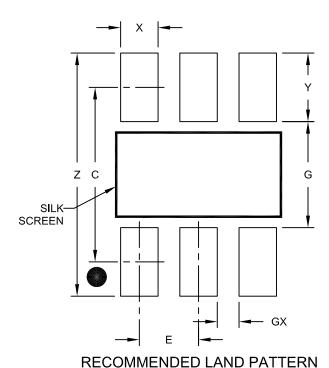

#### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

MILLIMETERS Units **Dimension Limits** MIN MOM MAX Contact Pitch 0.95 BSC Ε Contact Pad Spacing С 2.80 Contact Pad Width (X6) Х 0.60 Contact Pad Length (X6) Υ 1.10 Distance Between Pads G 1.70 0.35 Distance Between Pads GΧ Overall Width 3.90

#### Notes

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2028A

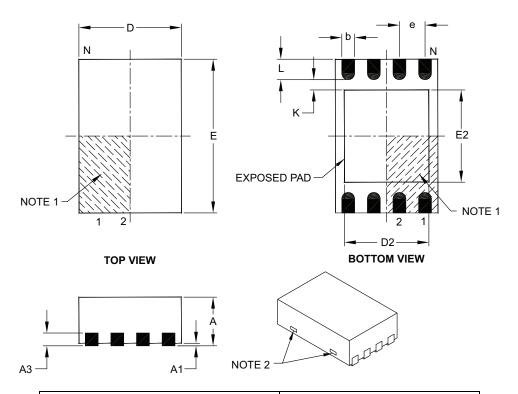

### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    |          | MILLIMETERS |      |  |

|------------------------|----------|----------|-------------|------|--|

| Dimension              | n Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | Ν        | 8        |             |      |  |

| Pitch                  | е        | 0.50 BSC |             |      |  |

| Overall Height         | Α        | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1       | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | А3       | 0.20 REF |             |      |  |

| Overall Length         | D        | 2.00 BSC |             |      |  |

| Overall Width          | Е        | 3.00 BSC |             |      |  |

| Exposed Pad Length     | D2       | 1.30     | _           | 1.55 |  |

| Exposed Pad Width      | E2       | 1.50     | _           | 1.75 |  |

| Contact Width          | b        | 0.20     | 0.25        | 0.30 |  |

| Contact Length         | L        | 0.30     | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | K        | 0.20     | _           | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference} \textbf{REF: Reference Dimension, usually without tolerance, for information purposes only.}$

Microchip Technology Drawing C04-123C