# E·XFL

#### Details

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 4                                                                         |

| Program Memory Size        | 384B (256 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 16 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 2x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f220t-i-ot |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

### 4.5 **OPTION Register**

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

The OPTION register is not memory mapped and is therefore only addressable by executing the <code>OPTION</code> instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<br/><7:0> bits.

| Note: | If TRIS bit is set to '0', the wake-up on    |

|-------|----------------------------------------------|

|       | change and pull-up functions are disabled    |

|       | for that pin (i.e., note that TRIS overrides |

|       | Option control of GPPU and GPWU).            |

| Note: | If the T0CS bit is set to '1', it will override |

|-------|-------------------------------------------------|

|       | the TRIS function on the T0CKI pin.             |

#### REGISTER 4-2: OPTION REGISTER

| W-1           | W-1                                                                                                                                                   | W-1                                                                                                                                                | W-1                                               | W-1              | W-1  | W-1             | W-1   |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|------------------|------|-----------------|-------|

| GPWU          | GPPU                                                                                                                                                  | TOCS                                                                                                                                               | T0SE                                              | PSA              | PS2  | PS1             | PS0   |

| bit 7         |                                                                                                                                                       |                                                                                                                                                    |                                                   | •<br>•           |      |                 | bit 0 |

|               |                                                                                                                                                       |                                                                                                                                                    |                                                   |                  |      |                 |       |

| Legend:       |                                                                                                                                                       |                                                                                                                                                    |                                                   |                  |      |                 |       |

| R = Readable  |                                                                                                                                                       | W = Writable bit                                                                                                                                   |                                                   | U = Unimpler     |      |                 |       |

| -n = Value at | POR                                                                                                                                                   | '1' = Bit is set                                                                                                                                   |                                                   | '0' = Bit is cle | ared | x = Bit is unkr | nown  |

| bit 7         | GPWII: Enab                                                                                                                                           | le Wake-un Or                                                                                                                                      | Pin Change                                        | bit (GP0, GP1,   | GP3) |                 |       |

| on 7          | 1 = Disabled<br>0 = Enabled                                                                                                                           |                                                                                                                                                    |                                                   |                  |      |                 |       |

| bit 6         | GPPU: Enabl                                                                                                                                           | e Weak Pull-up                                                                                                                                     | os bit (GP0, G                                    | GP1, GP3)        |      |                 |       |

|               | 1 = Disabled<br>0 = Enabled                                                                                                                           |                                                                                                                                                    |                                                   |                  |      |                 |       |

| bit 5         | TOCS: Timer(                                                                                                                                          | Clock Source                                                                                                                                       | Select bit                                        |                  |      |                 |       |

|               | <ul> <li>1 = Transition on T0CKI pin (overrides TRIS on the T0CKI pin)</li> <li>0 = Transition on internal instruction cycle clock, Fosc/4</li> </ul> |                                                                                                                                                    |                                                   |                  |      |                 |       |

| bit 4         | T0SE: Timer0                                                                                                                                          | ) Source Edge                                                                                                                                      | Select bit                                        |                  |      |                 |       |

|               | <ul> <li>1 = Increment on high-to-low transition on the T0CKI pin</li> <li>0 = Increment on low-to-high transition on the T0CKI pin</li> </ul>        |                                                                                                                                                    |                                                   |                  |      |                 |       |

| bit 3         | PSA: Prescal                                                                                                                                          | er Assignment                                                                                                                                      | bit                                               |                  |      |                 |       |

|               | <ul> <li>1 = Prescaler assigned to the WDT</li> <li>0 = Prescaler assigned to Timer0</li> </ul>                                                       |                                                                                                                                                    |                                                   |                  |      |                 |       |

| bit 2-0       | <b>PS&lt;2:0&gt;:</b> Pre                                                                                                                             | escaler Rate Se                                                                                                                                    | elect bits                                        |                  |      |                 |       |

|               | Bit                                                                                                                                                   | Value Timer0                                                                                                                                       | Rate WDT F                                        | Rate             |      |                 |       |

|               | 0<br>0<br>1<br>1                                                                                                                                      | 000         1:2           001         1:4           010         1:8           011         1:1           .000         1:3           .01         1:6 | 1 : 2<br>1 : 4<br>6 1 : 8<br>2 1 : 16<br>4 1 : 32 | 2                |      |                 |       |

|               |                                                                                                                                                       | .10 1:1<br>.11 1:2                                                                                                                                 |                                                   |                  |      |                 |       |

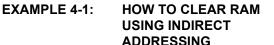

#### 4.9 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### 4.9.1 INDIRECT ADDRESSING

- · Register file 09 contains the value 10h

- · Register file 0A contains the value 0Ah

- · Load the value 09 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 0A)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using Indirect addressing is shown in Example 4-1.

#### FIGURE 4-6: DIRECT/INDIRECT ADDRESSING

|      |                                |                              | DILLOUINO                                                                  |  |  |  |

|------|--------------------------------|------------------------------|----------------------------------------------------------------------------|--|--|--|

| NEXT | MOVLW<br>MOVWF<br>CLRF<br>INCF | 0x10<br>FSR<br>INDF<br>FSR,F | ;initialize pointer<br>;to RAM<br>;clear INDF<br>;register<br>;inc pointer |  |  |  |

|      | BTFSC<br>GOTO                  | FSR <b>,</b> 4<br>NEXT       | ;all done?<br>;NO, clear next                                              |  |  |  |

| CONT | CONTINUE                       |                              |                                                                            |  |  |  |

|      | :                              |                              | ;YES, continue                                                             |  |  |  |

|      | :                              |                              |                                                                            |  |  |  |

|      |                                |                              |                                                                            |  |  |  |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**Note:** Do not use banking. FSR <7:5> are unimplemented and read as '1's.

| R-X                                 | R-X    | R-X              | R-X                                | R-X             | R-X    | R-X    | R-X    |

|-------------------------------------|--------|------------------|------------------------------------|-----------------|--------|--------|--------|

| ADRES7                              | ADRES6 | ADRES5           | ADRES4                             | ADRES3          | ADRES2 | ADRES1 | ADRES0 |

| bit 7                               | •      | •                |                                    |                 |        | •      | bit 0  |

|                                     |        |                  |                                    |                 |        |        |        |

| Legend:                             |        |                  |                                    |                 |        |        |        |

| R = Readable bit W = Writable bit U |        |                  | U = Unimplemented bit, read as '0' |                 |        |        |        |

| -n = Value at POR '1' = Bit is set  |        | '0' = Bit is cle | ared                               | x = Bit is unkr | nown   |        |        |

#### REGISTER 7-2: ADRES: ANALOG CONVERSION RESULT REGISTER

bit 7-0 ADRES<7:0>

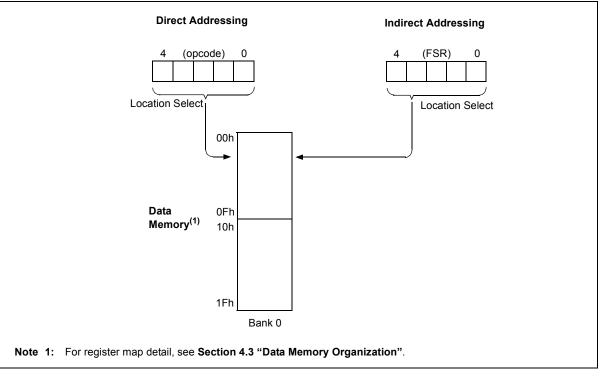

#### FIGURE 8-2: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

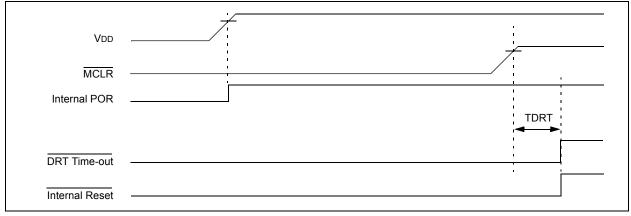

#### FIGURE 8-3: TIME-OUT SEQUENCE ON POWER-UP (MCLR PULLED LOW)

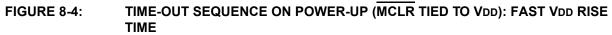

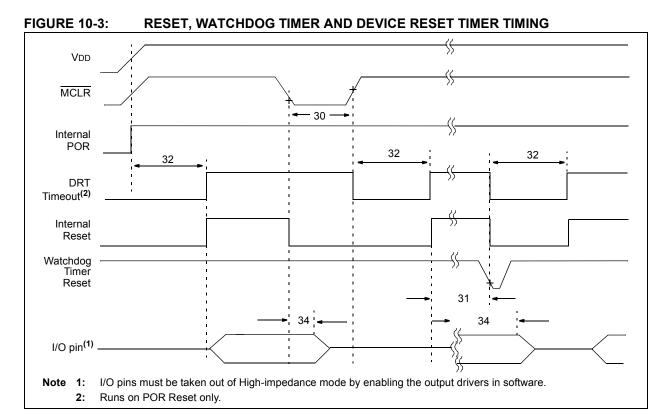

#### 8.5 Device Reset Timer (DRT)

On the PIC10F220/222 devices, the DRT runs any time the device is powered up.

The DRT operates on an internal oscillator. The processor is kept in Reset as long as the DRT is active. The DRT delay allows VDD to rise above VDD min. and for the oscillator to stabilize.

The on-chip DRT keeps the devices in a Reset condition for approximately 1.125 ms after MCLR has reached a logic high (VIH MCLR) level. Programming GP3/MCLR/VPP as MCLR and using an external RC network connected to the MCLR input is not required in most cases. This allows savings in cost-sensitive and/ or space restricted applications, as well as allowing the use of the GP3/MCLR/VPP pin as a general purpose input.

The Device Reset Time delays will vary from chip-tochip due to VDD, temperature and process variation. See AC parameters for details.

Reset sources are POR, MCLR, WDT time-out and wake-up on pin change. See Section 8.9.2 "Wake-up from Sleep", Notes 1, 2 and 3.

# TABLE 8-3:DRT (DEVICE RESET TIMER<br/>PERIOD)

| POR Reset          | Subsequent Resets |

|--------------------|-------------------|

| 1.125 ms (typical) | 10 μs (typical)   |

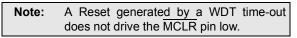

### 8.6 Watchdog Timer (WDT)

The Watchdog Timer (WDT) is a free running on-chip RC oscillator, which does not require any external components. This RC oscillator is separate from the internal 4/8 MHz oscillator. This means that the WDT will run even if the main processor clock has been stopped, for example, by execution of a SLEEP instruction. During normal operation or Sleep, a WDT Reset or wake-up Reset, generates a device Reset.

The  $\overline{\text{TO}}$  bit (STATUS<4>) will be cleared upon a Watchdog Timer Reset.

The WDT can be permanently disabled by programming the configuration WDTE as a '0' (see **Section 8.1 "Configuration Bits"**). Refer to the PIC10F220/222 Programming Specification to determine how to access the Configuration Word.

#### 8.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms, (with no prescaler). If a longer time-out period is desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT (under software control) by writing to the OPTION register. Thus, a time-out period of a nominal 2.3 seconds can be realized. These periods vary with temperature, VDD and part-to-part process variations (see DC specs).

Under worst-case conditions (VDD = Min., Temperature = Max., max. WDT prescaler), it may take several seconds before a WDT time-out occurs.

#### 8.6.2 WDT PROGRAMMING CONSIDERATIONS

The CLRWDT instruction clears the WDT and the postscaler, if assigned to the WDT, and prevents it from timing out and generating a device Reset.

The SLEEP instruction resets the WDT and the postscaler, if assigned to the WDT. This gives the maximum Sleep time before a WDT wake-up Reset.

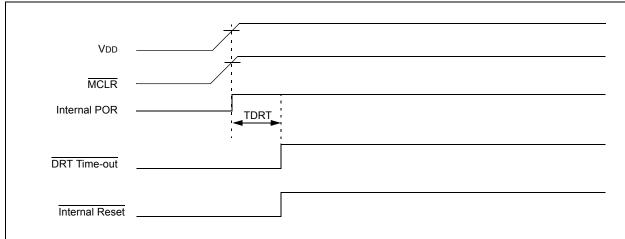

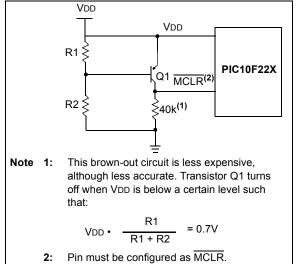

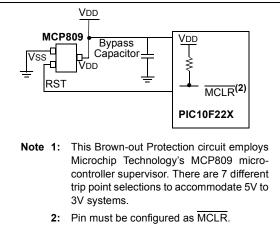

#### 8.8 Reset on Brown-out

A Brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a Brown-out.

To reset PIC10F220/222 devices when a Brown-out occurs, external Brown-out protection circuits may be built, as shown in Figure 8-7 and Figure 8-8.

FIGURE 8-7: BROWN-OUT PROTECTION CIRCUIT 1

#### FIGURE 8-8:

BROWN-OUT PROTECTION CIRCUIT 2

#### FIGURE 8-9: BROWN-OUT PROTECTION CIRCUIT 3

### 8.9 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

#### 8.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the TO bit (STATUS<4>) is set, the PD bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

For lowest current consumption while powered down, the T0CKI input should be at VDD or VSs and the GP3/ MCLR/VPP pin must be at a logic high level if MCLR is enabled.

| TABLE 9-2: IN | ISTRUCTION SET | SUMMARY |

|---------------|----------------|---------|

|---------------|----------------|---------|

| Mnemonic, |           | Description                                       | Cycles           | 12-1      | Bit Opcode |           | Status     |          |

|-----------|-----------|---------------------------------------------------|------------------|-----------|------------|-----------|------------|----------|

| Oper      |           | Description                                       | Cycles           | MSb       | MSb L      |           | Affected   | Notes    |

| ADDWF     | f, d      | Add W and f                                       | 1                | 0001      | 11df       | ffff      | C,DC,Z     | 1,2,4    |

| ANDWF     | f, d      | AND W with f                                      | 1                | 0001      | 01df       | ffff      | Z          | 2,4      |

| CLRF      | f         | Clear f                                           | 1                | 0000      | 011f       | ffff      | Z          | 4        |

| CLRW      | -         | Clear W                                           | 1                | 0000      | 0100       | 0000      | Z          |          |

| COMF      | f, d      | Complement f                                      | 1                | 0010      | 01df       | ffff      | Z          |          |

| DECF      | f, d      | Decrement f                                       | 1                | 0000      | 11df       | ffff      | Z          | 2,4      |

| DECFSZ    | f, d      | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010      | 11df       | ffff      | None       | 2,4      |

| INCF      | f, d      | Increment f                                       | 1                | 0010      | 10df       | ffff      | Z          | 2,4      |

| INCFSZ    | f, d      | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011      | 11df       | ffff      | None       | 2,4      |

| IORWF     | f, d      | Inclusive OR W with f                             | 1                | 0001      | 00df       | ffff      | Z          | 2,4      |

| MOVF      | f, d      | Move f                                            | 1                | 0010      | 00df       | ffff      | Z          | 2,4      |

| MOVWF     | f         | Move W to f                                       | 1                | 0000      | 001f       | ffff      | None       | 1,4      |

| NOP       | _         | No Operation                                      | 1                | 0000      | 0000       | 0000      | None       |          |

| RLF       | f, d      | Rotate left f through Carry                       | 1                | 0011      | 01df       | ffff      | С          | 2,4      |

| RRF       | f, d      | Rotate right f through Carry                      | 1                | 0011      | 00df       | ffff      | С          | 2,4      |

| SUBWF     | f, d      | Subtract W from f                                 | 1                | 0000      | 10df       | ffff      | C,DC,Z     | 1,2,4    |

| SWAPF     | f, d      | Swap f                                            | 1                | 0011      | 10df       | ffff      | None       | 2,4      |

| XORWF     | f, d      | Exclusive OR W with f                             | 1                | 0001      | 10df       | ffff      | Z          | 2,4      |

|           |           | BIT-ORIENTED FILE REGISTE                         |                  | ATIONS    | ;          |           |            |          |

| BCF       | f, b      | Bit Clear f                                       | 1                | 0100      | bbbf       | ffff      | None       | 2,4      |

| BSF       | f, b      | Bit Set f                                         | 1                | 0101      | bbbf       | ffff      | None       | 2,4      |

| BTFSC     | f, b      | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110      | bbbf       | ffff      | None       |          |

| BTFSS     | f, b      | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111      | bbbf       | ffff      | None       |          |

|           |           | LITERAL AND CONTROL                               | OPERATIO         | ONS       |            |           |            |          |

| ANDLW     | k         | AND literal with W                                | 1                | 1110      | kkkk       | kkkk      | Z          |          |

| CALL      | k         | Call subroutine                                   | 2                | 1001      | kkkk       | kkkk      | None       | 1        |

| CLRWDT    | k         | Clear Watchdog Timer                              | 1                | 0000      | 0000       | 0100      | TO, PD     |          |

| GOTO      | k         | Unconditional branch                              | 2                | 101k      | kkkk       | kkkk      | None       |          |

| IORLW     | k         | Inclusive OR Literal with W                       | 1                | 1101      | kkkk       | kkkk      | Z          |          |

| MOVLW     | k         | Move Literal to W                                 | 1                | 1100      | kkkk       | kkkk      | None       |          |

| OPTION    | -         | Load OPTION register                              | 1                | 0000      | 0000       | 0010      | None       |          |

| RETLW     | k         | Return, place Literal in W                        | 2                | 1000      | kkkk       | kkkk      | None       |          |

| SLEEP     | -         | Go into standby mode                              | 1                | 0000      | 0000       | 0011      | TO, PD     |          |

| TRIS      | f         | Load TRIS register                                | 1                | 0000      | 0000       | Offf      | None       | 3        |

| XORLW     | k         | Exclusive OR Literal to W                         | 1                | 1111      | kkkk       | kkkk      | Z          |          |

| Note 1:   | The 9th I | bit of the program counter will be forced to a '0 | ' by any ii      | nstructio | on that v  | vrites to | the PC exc | cept for |

GOTO. See Section 4.7 "Program Counter".

2: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6 causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

| DECF             | Decrement f                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECF f,d                                                                                                                         |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                        |

| Operation:       | $(f) - 1 \rightarrow (dest)$                                                                                                                      |

| Status Affected: | Z                                                                                                                                                 |

| Description:     | Decrement register 'f'. If 'd' is '0',<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |

Decrement f, Skip if 0

[label] DECFSZ f,d

(f)  $-1 \rightarrow d$ ; skip if result = 0

The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register

If the result is '0', the next instruction, which is already fetched, is discarded and a NOP is executed

instead making it a two-cycle

$\begin{array}{l} 0 \leq f \leq 31 \\ d \, \in \, [0,1] \end{array}$

None

'f'.

instruction.

DECFSZ

Operands:

Operation:

Description:

Status Affected:

Syntax:

| Syntax:          | [ <i>label</i> ] INCF f,d                                                                                                                                                  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                 |

| Operation:       | (f) + 1 $\rightarrow$ (dest)                                                                                                                                               |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                     |

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                 |

| Operation:       | (f) + 1 $\rightarrow$ (dest), skip if result = 0                                                                                                                           |

| Status Affected: | None                                                                                                                                                                       |

| Description:     | The contents of register 'f' are incremented. If 'd' is '0', the result                                                                                                    |

|                  | is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '0', then the next                                        |

Increment f

INCF

| GOTO             | Unconditional Branch                                                                                                                                                                        |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                     |

| Operands:        | $0 \leq k \leq 511$                                                                                                                                                                         |

| Operation:       | k → PC<8:0>;<br>STATUS<6:5> → PC<10:9>                                                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                        |

| Description:     | GOTO is an unconditional branch.<br>The 9-bit immediate value is<br>loaded into PC bits <8:0>. The<br>upper bits of PC are loaded from<br>STATUS<6:5>. GOTO is a two-<br>cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |  |

| Operation:       | (W) .OR. (k) $\rightarrow$ (W)                                                                                            |  |

| Status Affected: | Z                                                                                                                         |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the W<br>register. |  |

cycle instruction.

| RETLW                                                                                                    | Return with Literal in W                                                | SLEEP            | Enter SLEEP Mode                                                                                      |

|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------|

| Syntax:                                                                                                  | [ <i>label</i> ] RETLW k                                                | Syntax:          | [label] SLEEP                                                                                         |

| Operands:                                                                                                | $0 \leq k \leq 255$                                                     | Operands:        | None                                                                                                  |

| Operation:                                                                                               | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                            | Operation:       | 00h $\rightarrow$ WDT;<br>0 $\rightarrow$ WDT prescaler;                                              |

| Status Affected:                                                                                         | None                                                                    |                  | $1 \rightarrow \overline{\underline{TO}};$                                                            |

| Description:                                                                                             | The W register is loaded with the<br>eight-bit literal 'k'. The program | Status Affected: | $0 \rightarrow PD$<br>TO, PD, RBWUF                                                                   |

| counter is loaded from the top of<br>the stack (the return address). This<br>is a two-cycle instruction. | the stack (the return address). This                                    | Description:     | Time-out Status bit $(\overline{TO})$ is set. The Power-down Status bit $(\overline{PD})$ is cleared. |

|                                                                                                          |                                                                         |                  | RBWUF is unaffected.                                                                                  |

|                                                                                                          |                                                                         |                  | The WDT and its prescaler are<br>cleared.                                                             |

|                                                                                                          |                                                                         |                  | The processor is put into Sleep mode with the oscillator stopped.                                     |

| RLF              | Rotate Left f t                                                  | hrough Carry                                                                                                                           |

|------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ]                                                        | RLF f,d                                                                                                                                |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$ |                                                                                                                                        |

| Operation:       | See description                                                  | n below                                                                                                                                |

| Status Affected: | С                                                                |                                                                                                                                        |

| Description:     | rotated one bit<br>the Carry Flag.<br>result is placed           | f register 'f' are<br>to the left through<br>. If 'd' is '0', the<br>l in the W register. If<br>sult is stored back in<br>register 'f' |

| SUBWF            | Subtract W from f                                                                                                                                                                               |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SUBWF f,d                                                                                                                                                                      |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                      |  |  |  |

| Operation:       | $(f) - (W) \rightarrow (dest)$                                                                                                                                                                  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                                        |  |  |  |

| Description:     | Subtract (2's complement method)<br>the W register from register 'f'. If 'd'<br>is '0', the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |

details.

See section on Sleep for more

| RRF              | Rotate Right f through Carry                                                                                                                                                                                          |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                              |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                                                                            |  |

| Operation:       | See description below                                                                                                                                                                                                 |  |

| Status Affected: | С                                                                                                                                                                                                                     |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry Flag. If 'd' is '0', the<br>result is placed in the W register. If<br>'d' is '1', the result is placed back<br>in register 'f'. |  |

| SWAPF            | Swap Nibbles in f                                                                                                                                                              |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] SWAPF f,d                                                                                                                                                     |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                               |  |  |  |

| Operation:       | $(f<3:0>) \rightarrow (dest<7:4>);$<br>$(f<7:4>) \rightarrow (dest<3:0>)$                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                                           |  |  |  |

| Description:     | The upper and lower nibbles of<br>register 'f' are exchanged. If 'd' is<br>'0', the result is placed in W<br>register. If 'd' is '1', the result is<br>placed in register 'f'. |  |  |  |

| TRIS             | Load TRIS Register                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] TRIS f                                                                                           |

| Operands:        | f = 6                                                                                                             |

| Operation:       | (W) $\rightarrow$ TRIS register f                                                                                 |

| Status Affected: | None                                                                                                              |

| Description:     | TRIS register 'f' (f = 6 or 7) is<br>loaded with the contents of the W<br>register                                |

| XORLW            | Exclusive OR literal with W                                                                                       |

| Syntax:          | [ <i>label</i> ] XORLW k                                                                                          |

| Operands:        | $0 \le k \le 255$                                                                                                 |

| Operation:       | (W) .XOR. $k \rightarrow (W)$                                                                                     |

| Status Affected: | Z                                                                                                                 |

| Description:     | The contents of the W register are XOR'ed with the eight-bit literal 'k'. The result is placed in the W register. |

| XORWF            | Exclusive OR W with f                                                                                             |

| Syntax:          | [ <i>label</i> ] XORWF f,d                                                                                        |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                        |

| Operation:       | (W) .XOR. (f) $\rightarrow$ (dest)                                                                                |

Status Affected: Z

Description: Exclusive OR the contents of the W register with register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'.

#### RESET, WATCHDOG TIMER AND DEVICE RESET TIMER - PIC10F220/222 TABLE 10-3:

| АС СНА       | ARACTE           | RISTICS                                       | Operati<br>Operati | ng Temp<br>ng Volta | perature<br>ge VDD i | ≥ 40°C-<br>≥ 40°C-<br>range is | s (unless otherwise specified)<br>$TA \le +85^{\circ}C$ (industrial)<br>$TA \le +125^{\circ}C$ (extended)<br>described in Section 10.1 "DC<br>2 (Industrial)" |

|--------------|------------------|-----------------------------------------------|--------------------|---------------------|----------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Sym              | Characteristic                                | Min                | Typ <sup>(1)</sup>  | Max                  | Units                          | Conditions                                                                                                                                                    |

| 30           | Тмс <sub>L</sub> | MCLR Pulse Width (low)                        | 2*<br>5*           | _                   |                      | μS<br>μS                       | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V                                                                                                                        |

| 31           | Twdt             | Watchdog Timer Time-out Period (no prescaler) | 10<br>10           | 18<br>18            | 29<br>31             | ms<br>ms                       | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended)                                                                                                              |

| 32           | Tdrt*            | Device Reset Timer Period<br>(standard)       | 0.600<br>0.600     | 1.125<br>1.125      | 1.85<br>1.95         | ms<br>ms                       | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended)                                                                                                              |

| 34           | Tioz             | I/O High-impedance from MCLR low              | —                  | _                   | 2*                   | μS                             |                                                                                                                                                               |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 10-5: A/D CONVERTER CHARACTERISTICS

|              | -            | rating Conditions (unless operature $-40^{\circ}C \le TA \le +12$ |      | se stated)                |                  |       |                          |

|--------------|--------------|-------------------------------------------------------------------|------|---------------------------|------------------|-------|--------------------------|

| Param<br>No. | Sym          | Characteristic                                                    | Min  | Тур†                      | Мах              | Units | Conditions               |

| A01          | Nr           | Resolution                                                        |      | —                         | 8 bits           | bit   |                          |

| A03          | EIL          | Integral Error                                                    | _    | —                         | ±1.5             | LSb   |                          |

| A04          | Edl          | Differential Error                                                | _    | —                         | -1 < EDL ≤ + 1.5 | LSb   |                          |

| A05          | EFS          | Full-scale Range                                                  | 2.0* | —                         | 5.5*             | V     |                          |

| A06          | EOFF         | Offset Error                                                      | _    | —                         | ±1.5             | LSb   |                          |

| A07          | Egn          | Gain Error                                                        | _    | —                         | ±1.5             | LSb   |                          |

| A10          | —            | Monotonicity                                                      | _    | guaranteed <sup>(1)</sup> | —                | _     | $Vss \leq Vain \leq Vdd$ |

| A25          | VAIN         | Analog Input Voltage                                              | Vss  | —                         | Vdd              | V     |                          |

| A30          | Zain         | Recommended<br>Impedence of Analog<br>Voltage Source              | —    | _                         | 10               | kΩ    |                          |

| A31*         | $\Delta IAD$ | A/D Conversion Current <sup>(2)</sup>                             | _    | 120                       | 150              | μA    | 2.0V                     |

|              |              |                                                                   | _    | 200                       | 250              | μΑ    | 5.0V                     |

\* These parameters are characterized but not tested.

† Data in the "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only are not tested.

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

2: This is the additional current consumed by the A/D module when it is enabled; this current adds to base IDD.

#### TABLE 10-6: A/D CONVERSION REQUIREMENTS

#### Standard Operating Conditions (unless otherwise stated) $-40^\circ C \le TA \le +125^\circ C$ Operating temperature Param Sym Characteristic Min Typ† Max Units Conditions No. Set GO/DONE bit to new data in A/D AD131 Conversion Time TCNV 13 TCY (not including Result register Acquisition Time) Acquisition Time<sup>(1)</sup> AD132\* TACQ 3.5 μS VDD = 5Vμs 5 VDD = 2.5V

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The **Section 7.9 "A/D Acquisition Requirements"** for information on how to compute minimum acquisition times based on operating conditions.

#### 12.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 12.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 12.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 12.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 12.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 12.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 12.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 12.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 12.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

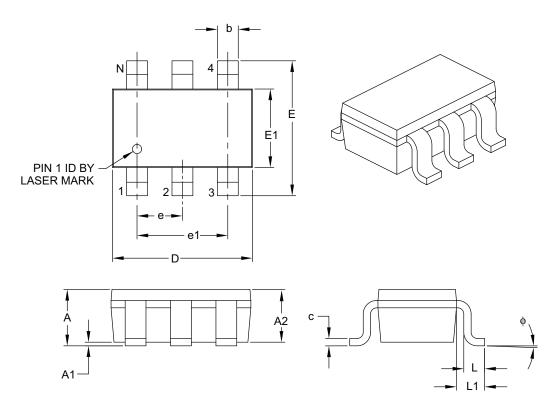

### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units     |      | MILLIMETERS |      |  |

|--------------------------|-----------|------|-------------|------|--|

| Dimensio                 | on Limits | MIN  | NOM         | MAX  |  |

| Number of Pins           | Ν         |      | 6           |      |  |

| Pitch                    | е         |      | 0.95 BSC    |      |  |

| Outside Lead Pitch       | e1        |      | 1.90 BSC    |      |  |

| Overall Height           | Α         | 0.90 | -           | 1.45 |  |

| Molded Package Thickness | A2        | 0.89 | -           | 1.30 |  |

| Standoff                 | A1        | 0.00 | -           | 0.15 |  |

| Overall Width            | Е         | 2.20 | -           | 3.20 |  |

| Molded Package Width     | E1        | 1.30 | -           | 1.80 |  |

| Overall Length           | D         | 2.70 | -           | 3.10 |  |

| Foot Length              | L         | 0.10 | -           | 0.60 |  |

| Footprint                | L1        | 0.35 | -           | 0.80 |  |

| Foot Angle               | φ         | 0°   | -           | 30°  |  |

| Lead Thickness           | С         | 0.08 | -           | 0.26 |  |

| Lead Width               | b         | 0.20 | -           | 0.51 |  |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

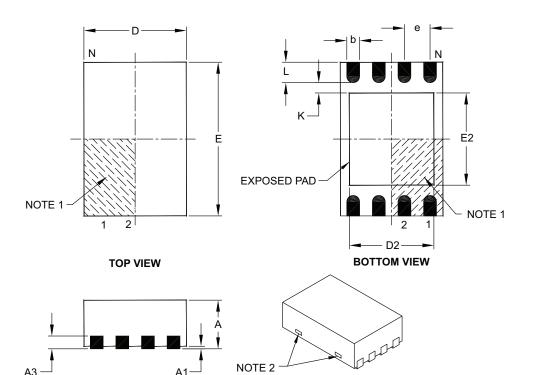

#### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          | MILLIMETERS |      |  |

|------------------------|------------------|----------|-------------|------|--|

|                        | Dimension Limits | MIN      | NOM         | MAX  |  |

| Number of Pins         | N                | 8        |             |      |  |

| Pitch                  | e                |          | 0.50 BSC    |      |  |

| Overall Height         | A                | 0.80     | 0.90        | 1.00 |  |

| Standoff               | A1               | 0.00     | 0.02        | 0.05 |  |

| Contact Thickness      | A3               | 0.20 REF |             |      |  |

| Overall Length         | D                | 2.00 BSC |             |      |  |

| Overall Width          | E                |          | 3.00 BSC    |      |  |

| Exposed Pad Length     | D2               | 1.30     | -           | 1.55 |  |

| Exposed Pad Width      | E2               | 1.50     | -           | 1.75 |  |

| Contact Width          | b                | 0.20     | 0.25        | 0.30 |  |

| Contact Length         | L                | 0.30     | 0.40        | 0.50 |  |

| Contact-to-Exposed Pad | К                | 0.20     | -           | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C

## INDEX

|   | ۰. |

|---|----|

| , | ۰. |

| A/D                                      |    |

|------------------------------------------|----|

| Specifications                           | 60 |

| ADC                                      |    |

| Internal Sampling Switch (Rss) IMPEDANCE | 32 |

| Source Impedance                         | 32 |

| ALU                                      | 9  |

| Assembler                                |    |

| MPASM Assembler                          | 62 |

|                                          |    |

## В

| Block Diagram                |     |

|------------------------------|-----|

| •                            | ~~~ |

| On-Chip Reset Circuit        |     |

| Timer0                       |     |

| TMR0/WDT Prescaler           |     |

| Watchdog Timer               |     |

| Block Diagrams               |     |

| Analog Input Model           |     |

| Brown-Out Protection Circuit | 40  |

### С

| C Compilers                          |    |

|--------------------------------------|----|

| MPLAB C18                            |    |

| MPLAB C30                            |    |

| Carry                                | 9  |

| Clocking Scheme                      |    |

| Code Protection                      |    |

| Configuration Bits                   |    |

| Customer Change Notification Service |    |

| Customer Notification Service        | 75 |

| Customer Support                     | 75 |

|                                      |    |

### D

| DC and AC Characteristics | 65 |

|---------------------------|----|

| Development Support       | 61 |

| Digit Carry               | 9  |

## Е

# F

| Family of Devices |  |

|-------------------|--|

| PIC10F22X         |  |

| FSR               |  |

|                   |  |

### G

| GPIO                                     | 21       |

|------------------------------------------|----------|

| I                                        |          |

| I/O Interfacing                          | 21       |

| I/O Ports                                | 21       |

| I/O Programming Considerations           | 23       |

| ID Locations                             | . 33, 41 |

| INDF                                     | 20       |

| Indirect Data Addressing                 | 20       |

| Instruction Cycle                        | 11       |

| Instruction Flow/Pipelining              |          |

| Instruction Set Summary                  | 44       |

| Internal Sampling Switch (RSS) IMPEDANCE | 32       |

| Internet Address                         | 75       |

| L                                        |          |

| Loading of PC 19 |

|------------------|

|------------------|

## Μ

| Memory Organization       13         Data Memory       14         Program Memory (PIC10F220)       13         Program Memory (PIC10F222)       13         Microchip Internet Web Site       75         MPLAB ASM30 Assembler, Linker, Librarian       62         MPLAB ICD 2 In-Circuit Debugger       63         MPLAB ICE 2000 High-Performance Universal       1         In-Circuit Emulator       63         MPLAB Integrated Development Environment Software       61         MPLAB REAL ICE In-Circuit Emulator System       63         MPLINK Object Linker/MPLIB Object Librarian       62 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| OPTION Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| PIC10F220/222 Device Varieties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Power-on Reset (POR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Power-down Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Q cycles 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Reader Response       76         Read-Modify-Write       23         Register File Map       PIC10F220         PIC040F2020       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PIC10F22214<br>Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |