#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 4                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 23 x 8                                                                   |

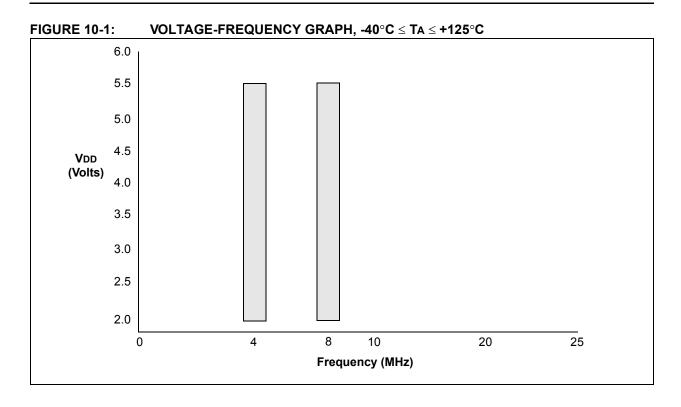

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 2x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f222-e-mc |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

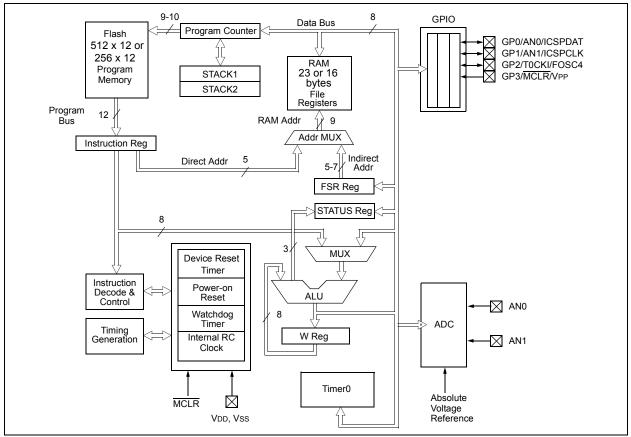

# 3.0 ARCHITECTURAL OVERVIEW

The high performance of the PIC10F220/222 devices can be attributed to a number of architectural features commonly found in RISC microprocessors. To begin with, the PIC10F220/222 devices use a Harvard architecture in which program and data are accessed on separate buses. This improves bandwidth over traditional von Neumann architectures where program and data are fetched on the same bus. Separating program and data memory further allows instructions to be sized differently than the 8-bit wide data word. Instruction opcodes are 12 bits wide, making it possible to have all single-word instructions. A 12-bit wide program memory access bus fetches a 12-bit instruction in a single cycle. A two-stage pipeline overlaps fetch and execution of instructions. Consequently, all instructions (33) execute in a single cycle (1 µs @ 4 MHz or 500 ns @ 8 MHz) except for program branches.

The table below lists program memory (Flash) and data memory (RAM) for the PIC10F220/222 devices.

| Device    | Memory   |        |  |  |  |  |

|-----------|----------|--------|--|--|--|--|

| Device    | Program  | Data   |  |  |  |  |

| PIC10F220 | 256 x 12 | 16 x 8 |  |  |  |  |

| PIC10F222 | 512 x 12 | 23 x 8 |  |  |  |  |

The PIC10F220/222 devices can directly or indirectly address its register files and data memory. All Special Function Registers (SFR), including the PC, are mapped in the data memory. The PIC10F220/222 devices have a highly orthogonal (symmetrical) instruction set that makes it possible to carry out any operation, on any register, using any addressing mode. This symmetrical nature and lack of "special optimal situations" make programming with the PIC10F220/222 devices simple, yet efficient. In addition, the learning curve is reduced significantly.

The PIC10F220/222 devices contain an 8-bit ALU and working register. The ALU is a general purpose arithmetic unit. It performs arithmetic and Boolean functions between data in the working register and any register file.

The ALU is 8-bits wide and capable of addition, subtraction, shift and logical operations. Unless otherwise mentioned, arithmetic operations are two's complement in nature. In two-operand instructions, one operand is typically the W (working) register. The other operand is either a file register or an immediate constant. In single operand instructions, the operand is either the W register or a file register.

The W register is an 8-bit working register used for ALU operations. It is not an addressable register.

Depending on the instruction executed, the ALU may affect the values of the Carry (C), Digit Carry (DC) and Zero (Z) bits in the STATUS register. The C and DC bits operate as a borrow and digit borrow out bit, respectively, in subtraction. See the SUBWF and ADDWF instructions for examples.

A simplified block diagram is shown in Figure 3-1 with the corresponding device pins described in Table 3-1.

### FIGURE 3-1: BLOCK DIAGRAM

# TABLE 3-1: PINOUT DESCRIPTION

| Name            | Function | Input<br>Type | Output<br>Type | Description                                                                                                                                                                                                     |

|-----------------|----------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GP0/AN0/ICSPDAT | GP0      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                               |

|                 | AN0      | AN            |                | Analog Input                                                                                                                                                                                                    |

|                 | ICSPDAT  | ST            | CMOS           | In-Circuit programming data                                                                                                                                                                                     |

| GP1/AN1/ICSPCLK | GP1      | TTL           | CMOS           | Bidirectional I/O pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                               |

|                 | AN1      | AN            |                | Analog Input                                                                                                                                                                                                    |

|                 | ICSPCLK  | ST            | _              | In-Circuit programming clock                                                                                                                                                                                    |

| GP2/T0CKI/FOSC4 | GP2      | TTL           | CMOS           | Bidirectional I/O pin                                                                                                                                                                                           |

|                 | TOCKI    | ST            |                | Clock input to TMR0                                                                                                                                                                                             |

|                 | FOSC4    | -             | CMOS           | Oscillator/4 output                                                                                                                                                                                             |

| GP3/MCLR/Vpp    | GP3      | TTL           | —              | Input pin. Can be software programmed for internal weak pull-up and wake-up from Sleep on pin change.                                                                                                           |

|                 | MCLR     | ST            | —              | Master Clear (Reset). When configured as MCLR, this pin is an active-low Reset to the device. Voltage on MCLR/VPP must not exceed VDD during normal device operation or the device will enter Programming mode. |

|                 | VPP      | HV            | _              | Programming voltage input                                                                                                                                                                                       |

| Vdd             | Vdd      | Р             | _              | Positive supply for logic and I/O pins                                                                                                                                                                          |

| Vss             | Vss      | Р             | _              | Ground reference for logic and I/O pins                                                                                                                                                                         |

**Legend:** I = Input, O = Output, I/O = Input/Output, P = Power, — = Not used, TTL = TTL input, ST = Schmitt Trigger input, AN = Analog Input

NOTES:

# 4.5 **OPTION Register**

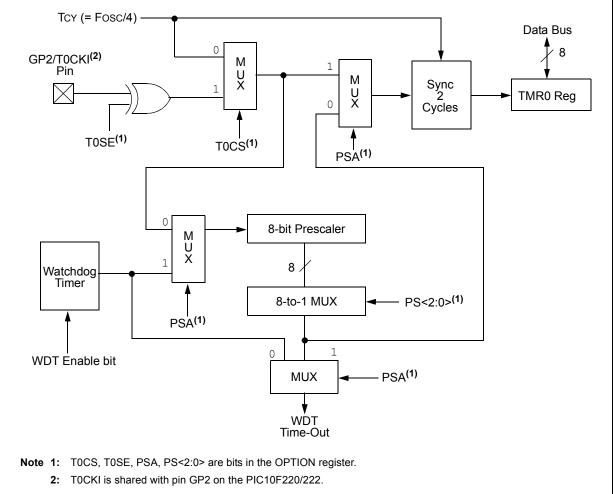

The OPTION register is a 8-bit wide, write-only register, which contains various control bits to configure the Timer0/WDT prescaler and Timer0.

The OPTION register is not memory mapped and is therefore only addressable by executing the <code>OPTION</code> instruction, the contents of the W register will be transferred to the OPTION register. A Reset sets the OPTION<br/><7:0> bits.

| Note: | If TRIS bit is set to '0', the wake-up on    |

|-------|----------------------------------------------|

|       | change and pull-up functions are disabled    |

|       | for that pin (i.e., note that TRIS overrides |

|       | Option control of GPPU and GPWU).            |

| Note: | If the T0CS bit is set to '1', it will override |

|-------|-------------------------------------------------|

|       | the TRIS function on the T0CKI pin.             |

# REGISTER 4-2: OPTION REGISTER

| W-1           | W-1                         | W-1                                                                                                                                                | W-1                                               | W-1                              | W-1                                      | W-1             | W-1   |

|---------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------|------------------------------------------|-----------------|-------|

| GPWU          | GPPU                        | TOCS                                                                                                                                               | T0SE                                              | PSA                              | PS2                                      | PS1             | PS0   |

| bit 7         |                             |                                                                                                                                                    |                                                   | •<br>•                           |                                          |                 | bit 0 |

|               |                             |                                                                                                                                                    |                                                   |                                  |                                          |                 |       |

| Legend:       |                             |                                                                                                                                                    |                                                   |                                  |                                          |                 |       |

| R = Readable  |                             | W = Writable                                                                                                                                       |                                                   | U = Unimpler                     |                                          |                 |       |

| -n = Value at | POR                         | '1' = Bit is set                                                                                                                                   |                                                   | '0' = Bit is cle                 | ared                                     | x = Bit is unkr | nown  |

| bit 7         | GPWII: Enab                 | le Wake-un Or                                                                                                                                      | Pin Change                                        | bit (GP0, GP1,                   | GP3)                                     |                 |       |

| on 7          | 1 = Disabled<br>0 = Enabled |                                                                                                                                                    |                                                   |                                  |                                          |                 |       |

| bit 6         | GPPU: Enabl                 | e Weak Pull-up                                                                                                                                     | os bit (GP0, G                                    | GP1, GP3)                        |                                          |                 |       |

|               | 1 = Disabled<br>0 = Enabled |                                                                                                                                                    |                                                   |                                  |                                          |                 |       |

| bit 5         | TOCS: Timer(                | Clock Source                                                                                                                                       | Select bit                                        |                                  |                                          |                 |       |

|               |                             | n on T0CKI pin<br>n on internal ins                                                                                                                |                                                   | RIS on the T0Cl<br>clock, Fosc/4 | <i pin)<="" td=""><td></td><td></td></i> |                 |       |

| bit 4         | T0SE: Timer0                | ) Source Edge                                                                                                                                      | Select bit                                        |                                  |                                          |                 |       |

|               |                             | •                                                                                                                                                  |                                                   | the T0CKI pin<br>the T0CKI pin   |                                          |                 |       |

| bit 3         | PSA: Prescal                | er Assignment                                                                                                                                      | bit                                               |                                  |                                          |                 |       |

|               |                             | assigned to th assigned to Ti                                                                                                                      |                                                   |                                  |                                          |                 |       |

| bit 2-0       | <b>PS&lt;2:0&gt;:</b> Pre   | escaler Rate Se                                                                                                                                    | elect bits                                        |                                  |                                          |                 |       |

|               | Bit                         | Value Timer0                                                                                                                                       | Rate WDT F                                        | Rate                             |                                          |                 |       |

|               | 0<br>0<br>1<br>1            | 000         1:2           001         1:4           010         1:8           011         1:1           .000         1:3           .01         1:6 | 1 : 2<br>1 : 4<br>6 1 : 8<br>2 1 : 16<br>4 1 : 32 | 2                                |                                          |                 |       |

|               |                             | .10 <b>1:1</b><br>.11 <b>1:2</b>                                                                                                                   |                                                   |                                  |                                          |                 |       |

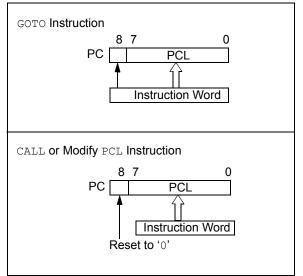

## 4.7 Program Counter

As a program instruction is executed, the Program Counter (PC) will contain the address of the next program instruction to be executed. The PC value is increased by one every instruction cycle, unless an instruction changes the PC.

For a GOTO instruction, bits 8:0 of the PC are provided by the GOTO instruction word. The PC Latch (PCL) is mapped to PC<7:0>.

For a CALL instruction or any instruction where the PCL is the destination, bits 7:0 of the PC again are provided by the instruction word. However, PC<8> does not come from the instruction word, but is always cleared (Figure 4-5).

Instructions where the PCL is the destination or Modify PCL instructions, include MOVWF PC, ADDWF PC and BSF PC, 5.

| Note: | Because PC<8> is cleared in the CALL       |  |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | instruction or any Modify PCL instruction, |  |  |  |  |  |  |  |  |  |

|       | all subroutine calls or computed jumps are |  |  |  |  |  |  |  |  |  |

|       | limited to the first 256 locations of any  |  |  |  |  |  |  |  |  |  |

|       | program memory page (512 words long).      |  |  |  |  |  |  |  |  |  |

### FIGURE 4-5: LOADING OF PC BRANCH INSTRUCTIONS

### 4.7.1 EFFECTS OF RESET

The PC is set upon a Reset, which means that the PC addresses the last location in program memory (i.e., the oscillator calibration instruction). After executing MOVLW XX, the PC will roll over to location 0000h and begin executing user code.

# 4.8 Stack

The PIC10F220 device has a 2-deep, 8-bit wide hardware PUSH/POP stack.

The PIC10F222 device has a 2-deep, 9-bit wide hardware PUSH/POP stack.

A CALL instruction will PUSH the current value of stack 1 into stack 2 and then PUSH the current PC value, incremented by one, into stack level 1. If more than two sequential CALL's are executed, only the most recent two return addresses are stored.

A RETLW instruction will POP the contents of stack level 1 into the PC and then copy stack level 2 contents into level 1. If more than two sequential RETLW's are executed, the stack will be filled with the address previously stored in level 2.

- **Note 1:** The W register will be loaded with the literal value specified in the instruction. This is particularly useful for the implementation of data look-up tables within the program memory.

- **2:** There are no Status bits to indicate stack overflows or stack underflow conditions.

- 3: There are no instructions mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL and RETLW instructions.

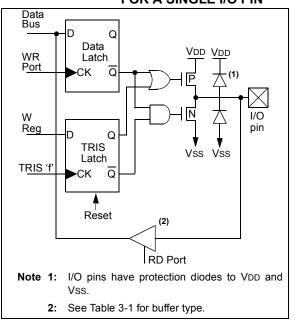

# 5.0 I/O PORT

As with any other register, the I/O register(s) can be written and read under program control. However, read instructions (e.g., MOVF GPIO, W) always read the I/O pins independent of the pin's Input/Output modes. On Reset, all I/O ports are defined as input (inputs are at high-impedance) since the I/O control registers are all set.

## 5.1 GPIO

GPIO is an 8-bit I/O register. Only the low-order 4 bits are used (GP<3:0>). Bits 7 through 4 are unimplemented and read as '0's. Please note that GP3 is an input only pin. Pins GP0, GP1 and GP3 can be configured with weak pull-ups and also for wake-up on change. The wake-up on change and weak pull-up functions are not individually pin selectable. If GP3/ MCLR is configured as MCLR, a weak pull-up can be enabled via the Configuration Word. Configuring GP3 as MCLR disables the wake-up on change function for this pin.

# 5.2 TRIS Registers

The Output Driver Control register is loaded with the contents of the W register by executing the TRIS f instruction. A '1' from a TRIS register bit puts the corresponding output driver in a High-Impedance mode. A '0' puts the contents of the output data latch on the selected pins, enabling the output buffer. The exceptions are GP3, which is input only, and the GP2/T0CKI/FOSC4 pin, which may be controlled by various registers. See Table 5-1.

| Note: | A read of the ports reads the pins, not the    |

|-------|------------------------------------------------|

|       | output data latches. That is, if an output     |

|       | driver on a pin is enabled and driven high,    |

|       | but the external system is holding it low, a   |

|       | read of the port will indicate that the pin is |

|       | low.                                           |

The TRIS registers are "write-only" and are set (output drivers disabled) upon Reset.

# 5.3 I/O Interfacing

The equivalent circuit for an I/O port pin is shown in Figure 5-1. All port pins, except GP3, which is input only, may be used for both input and output operations. For input operations, these ports are non-latching. Any input must be present until read by an input instruction (e.g., MOVF GPIO, W). The outputs are latched and remain unchanged until the output latch is rewritten. To use a port pin as output, the corresponding direction control bit in TRIS must be cleared (= 0). For use as an input, the corresponding TRIS bit must be set. Any I/O pin (except GP3) can be programmed individually as input or output.

FIGURE 5-1:

EQUIVALENT CIRCUIT FOR A SINGLE I/O PIN

| TABLE 5-1: 0 | ORDER OF PRECEDENCE FOR PIN FUNCTIONS |

|--------------|---------------------------------------|

|--------------|---------------------------------------|

| Priority | GP0       | GP1       | GP2       | GP3  |

|----------|-----------|-----------|-----------|------|

| 1        | AN0       | AN1       | FOSC4     | MCLR |

| 2        | TRIS GPIO | TRIS GPIO | TOCKI     | —    |

| 3        | —         | —         | TRIS GPIO | —    |

#### TABLE 5-2: REQUIREMENTS TO MAKE PINS AVAILABLE IN DIGITAL MODE

| GP0 | GP1     | GP2                                                           | GP3                                                                                                                         |

|-----|---------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| —   | —       | 0                                                             | _                                                                                                                           |

| —   | —       | 0                                                             | _                                                                                                                           |

| —   | 0       | —                                                             | _                                                                                                                           |

| 0   | —       | —                                                             | —                                                                                                                           |

| —   | —       | —                                                             | 0                                                                                                                           |

|     | GP0<br> | GP0         GP1                    0           0            0 | GP0         GP1         GP2             0             0            0            0             0             0             0 |

**Legend:** — = Condition of bit will have no effect on the setting of the pin to Digital mode.

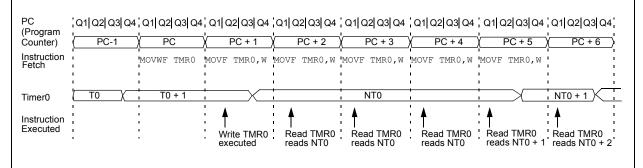

## FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                    | Bit 7    | Bit 6                                  | Bit 5 | Bit 4 | Bit 3                | Bit 2 | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|----------|----------------------------------------|-------|-------|----------------------|-------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0                    | Timer0 – | Timer0 – 8-Bit Real-Time Clock/Counter |       |       |                      |       |       |       | XXXX XXXX                     | uuuu uuuu                       |

| N/A     | OPTION                  | GPWU     | GPPU                                   | TOCS  | T0SE  | PSA                  | PS2   | PS1   | PS0   | 1111 1111                     | 1111 1111                       |

| N/A     | TRISGPIO <sup>(1)</sup> | —        | _                                      |       |       | I/O Control Register |       |       |       | 1111                          | 1111                            |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged.

Note 1: The TRIS of the TOCKI pin is overridden when TOCS = 1

#### 6.1 Using Timer0 With An External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 2Tt0H) and low for at least 2Tosc (and a small RC delay of 2Tt0H). Refer to the electrical specification of the desired device.

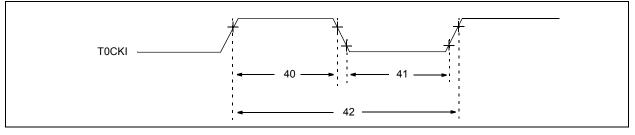

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 4Tt0H) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.2.1 SWITCHING PRESCALER ASSIGNMENT

The prescaler assignment is fully under software control (i.e., it can be changed "on-the-fly" during program execution). To avoid an unintended device Reset, the following instruction sequence (Example 6-1) must be executed when changing the prescaler assignment from Timer0 to the WDT.

# EXAMPLE 6-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

|        |             | · /                      |

|--------|-------------|--------------------------|

| CLRWDT |             | ;Clear WDT               |

| CLRF   | TMR0        | ;Clear TMR0 & Prescaler  |

| MOVLW  | '00xx1111'b | ;These 3 lines (5, 6, 7) |

| OPTION |             | ;are required only if    |

|        |             | ;desired                 |

| CLRWDT |             | ;PS<2:0> are 000 or 001  |

| MOVLW  | '00xx1xxx'b | ;Set Postscaler to       |

| OPTION |             | ;desired WDT rate        |

|        |             |                          |

To change prescaler from the WDT to the Timer0 module, use the sequence shown in Example 6-2. This sequence must be used even if the WDT is disabled. A CLRWDT instruction should be executed before switching the prescaler.

| EXAMPLE 6-2: | CHANGING PRESCALER |

|--------------|--------------------|

|              | (WDT→TIMER0)       |

|        |             | · · · · · · · · · · · · · · · · · · · |

|--------|-------------|---------------------------------------|

| CLRWDT |             | ;Clear WDT and                        |

|        |             | ;prescaler                            |

| MOVLW  | 'xxxx0xxxx' | ;Select TMR0, new                     |

|        |             | ;prescale value and                   |

|        |             | ;clock source                         |

| OPTION |             |                                       |

|        |             |                                       |

# 10.3 DC Characteristics: PIC10F220/222 (Industrial, Extended)

| DC CHA       | RACTI | ERISTICS                             | Standard Operating Conditions (unless otherwise specified)         Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)         Operating voltage VDD range as described in DC specification |      |           |    |                                                       |  |  |  |

|--------------|-------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------|----|-------------------------------------------------------|--|--|--|

| Param<br>No. | Sym   | Characteristic                       |                                                                                                                                                                                                                                                                      |      | Max Units |    | Conditions                                            |  |  |  |

|              | VIL   | Input Low Voltage                    |                                                                                                                                                                                                                                                                      |      |           |    | I                                                     |  |  |  |

|              |       | I/O ports:                           |                                                                                                                                                                                                                                                                      |      |           |    |                                                       |  |  |  |

| D030         |       | with TTL buffer                      | Vss                                                                                                                                                                                                                                                                  | _    | 0.8       | V  | For all $4.5 \le VDD \le 5.5V$                        |  |  |  |

| D030A        |       |                                      | Vss                                                                                                                                                                                                                                                                  | _    | 0.15 VDD  | V  | Otherwise                                             |  |  |  |

| D031         |       | with Schmitt Trigger<br>buffer       | Vss                                                                                                                                                                                                                                                                  | —    | 0.2 Vdd   | V  |                                                       |  |  |  |

| D032         |       | MCLR, TOCKI                          | Vss                                                                                                                                                                                                                                                                  | —    | 0.2 VDD   | V  |                                                       |  |  |  |

|              | Vih   | Input High Voltage                   | •                                                                                                                                                                                                                                                                    |      |           |    |                                                       |  |  |  |

|              |       | I/O ports:                           |                                                                                                                                                                                                                                                                      | —    |           |    |                                                       |  |  |  |

| D040         |       | with TTL buffer                      | 2.0                                                                                                                                                                                                                                                                  | —    | Vdd       | V  | $4.5 \leq V \text{DD} \leq 5.5 V$                     |  |  |  |

| D040A        |       |                                      | 0.25 VDD + 0.8                                                                                                                                                                                                                                                       | —    | Vdd       | V  | Otherwise                                             |  |  |  |

| D041         |       | with Schmitt Trigger<br>buffer       | 0.8Vdd                                                                                                                                                                                                                                                               | —    | Vdd       | V  | For entire VDD range                                  |  |  |  |

| D042         |       | MCLR, TOCKI                          | 0.8VDD                                                                                                                                                                                                                                                               | —    | Vdd       | V  |                                                       |  |  |  |

| D070         | IPUR  | GPIO weak pull-up current            | 50                                                                                                                                                                                                                                                                   | 250  | 400       | μA | VDD = 5V, VPIN = VSS                                  |  |  |  |

|              | lı∟   | Input Leakage Current <sup>(1)</sup> |                                                                                                                                                                                                                                                                      |      |           |    |                                                       |  |  |  |

| D060         |       | I/O ports                            | —                                                                                                                                                                                                                                                                    | ±0.1 | ± 1       | μA | $Vss \leq V PIN \leq V DD, \ Pin \ at high-impedance$ |  |  |  |

| D061         |       | GP3/MCLR <sup>(2)</sup>              | —                                                                                                                                                                                                                                                                    | ±0.7 | ± 5       | μA | $Vss \leq V \text{PIN} \leq V \text{DD}$              |  |  |  |

|              |       | Output Low Voltage                   |                                                                                                                                                                                                                                                                      |      |           |    |                                                       |  |  |  |

| D080         |       | I/O ports                            | —                                                                                                                                                                                                                                                                    |      | 0.6       | V  | IOL = 8.5 mA, VDD = 4.5V, -40°C to<br>+85°C           |  |  |  |

| D080A        |       |                                      | _                                                                                                                                                                                                                                                                    | —    | 0.6       | V  | Io∟ = 7.0 mA, VDD = 4.5V, -40°C to<br>+125°C          |  |  |  |

|              |       | Output High Voltage                  |                                                                                                                                                                                                                                                                      |      |           |    |                                                       |  |  |  |

| D090         |       | I/O ports <sup>(2)</sup>             | VDD - 0.7                                                                                                                                                                                                                                                            | _    | _         | V  | IOH = -3.0 mA, VDD = 4.5V, -40°С to<br>+85°С          |  |  |  |

| D090A        |       |                                      | Vdd - 0.7                                                                                                                                                                                                                                                            | —    | —         | V  | ІОН = -2.5 mA, VDD = 4.5V, -40°С to<br>+125°С         |  |  |  |

|              |       | Capacitive Loading Specs on          | Output Pins                                                                                                                                                                                                                                                          |      | •         | •  | •                                                     |  |  |  |

| D101         |       | All I/O pins                         | _                                                                                                                                                                                                                                                                    | _    | 50*       | pF |                                                       |  |  |  |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

\* These parameters are for design guidance only and are not tested.

**Note 1:** Negative current is defined as coming out of the pin.

2: This specification applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

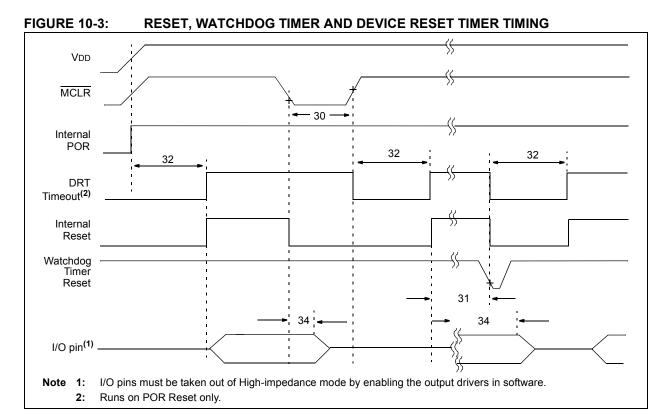

#### RESET, WATCHDOG TIMER AND DEVICE RESET TIMER - PIC10F220/222 TABLE 10-3:

| АС СНА       | ARACTE           | RISTICS                                       | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)Operating Voltage VDD range is described in Section 10.1 "DCCharacteristics: PIC10F220/222 (Industrial)" |                    |              |          |                                                  |  |  |

|--------------|------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|----------|--------------------------------------------------|--|--|

| Param<br>No. | Sym              | Characteristic                                | Min                                                                                                                                                                                                                                                                                            | Typ <sup>(1)</sup> | Max          | Units    | Conditions                                       |  |  |

| 30           | Тмс <sub>L</sub> | MCLR Pulse Width (low)                        | 2*<br>5*                                                                                                                                                                                                                                                                                       | _                  |              | μS<br>μS | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |  |  |

| 31           | Twdt             | Watchdog Timer Time-out Period (no prescaler) | 10<br>10                                                                                                                                                                                                                                                                                       | 18<br>18           | 29<br>31     | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |  |

| 32           | Tdrt*            | Device Reset Timer Period<br>(standard)       | 0.600<br>0.600                                                                                                                                                                                                                                                                                 | 1.125<br>1.125     | 1.85<br>1.95 | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |  |

| 34           | Tioz             | I/O High-impedance from MCLR low              | _                                                                                                                                                                                                                                                                                              | _                  | 2*           | μS       |                                                  |  |  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### FIGURE 10-4: **TIMER0 CLOCK TIMINGS**

#### TIMER0 CLOCK REQUIREMENTS **TABLE 10-4**:

| АС СНА       | RACT              | ERISTICS                     | $\begin{array}{l} \mbox{Standard Operating Conditions (unless otherwise specified)} \\ \mbox{Operating Temperature } -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ (industrial)} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ (extended)} \end{array}$ |                   |                    |     |       |                                                                |  |  |

|--------------|-------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------|-----|-------|----------------------------------------------------------------|--|--|

| Param<br>No. | Sym               | Characteristic               |                                                                                                                                                                                                                                                             | Min               | Typ <sup>(1)</sup> | Max | Units | Conditions                                                     |  |  |

| 40           | Tt0H              | 0H TOCKI High Pulse<br>Width | No Prescaler                                                                                                                                                                                                                                                | 0.5 Tcy + 20*     | _                  |     | ns    |                                                                |  |  |

|              |                   |                              | With Prescaler                                                                                                                                                                                                                                              | 10*               | —                  | -   | ns    |                                                                |  |  |

| 41           | 11 TtOL           | T0CKI Low Pulse Width        | No Prescaler                                                                                                                                                                                                                                                | 0.5 TCY + 20*     | —                  | _   | ns    |                                                                |  |  |

|              |                   |                              | With Prescaler                                                                                                                                                                                                                                              | 10*               | —                  | _   | ns    |                                                                |  |  |

| 42           | Tt0P T0CKI Period |                              |                                                                                                                                                                                                                                                             | 20 or Tcy + 40* N | —                  |     | ns    | Whichever is greater.<br>N = Prescale Value<br>(1, 2, 4,, 256) |  |  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 10-5: A/D CONVERTER CHARACTERISTICS

|              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                                      |      |                           |                  |       |                          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------|---------------------------|------------------|-------|--------------------------|--|--|--|--|

| Param<br>No. | Sym                                                                                                                  | Characteristic                                       | Min  | Тур†                      | Мах              | Units | Conditions               |  |  |  |  |

| A01          | Nr                                                                                                                   | Resolution                                           |      | —                         | 8 bits           | bit   |                          |  |  |  |  |

| A03          | EIL                                                                                                                  | Integral Error                                       | _    | —                         | ±1.5             | LSb   |                          |  |  |  |  |

| A04          | Edl                                                                                                                  | Differential Error                                   | _    | —                         | -1 < EDL ≤ + 1.5 | LSb   |                          |  |  |  |  |

| A05          | EFS                                                                                                                  | Full-scale Range                                     | 2.0* | —                         | 5.5*             | V     |                          |  |  |  |  |

| A06          | EOFF                                                                                                                 | Offset Error                                         | _    | —                         | ±1.5             | LSb   |                          |  |  |  |  |

| A07          | Egn                                                                                                                  | Gain Error                                           | _    | —                         | ±1.5             | LSb   |                          |  |  |  |  |

| A10          | —                                                                                                                    | Monotonicity                                         | _    | guaranteed <sup>(1)</sup> | —                | _     | $Vss \leq Vain \leq Vdd$ |  |  |  |  |

| A25          | VAIN                                                                                                                 | Analog Input Voltage                                 | Vss  | —                         | Vdd              | V     |                          |  |  |  |  |

| A30          | Zain                                                                                                                 | Recommended<br>Impedence of Analog<br>Voltage Source | —    | _                         | 10               | kΩ    |                          |  |  |  |  |

| A31*         | $\Delta IAD$                                                                                                         | A/D Conversion Current <sup>(2)</sup>                | _    | 120                       | 150              | μA    | 2.0V                     |  |  |  |  |

|              |                                                                                                                      |                                                      | _    | 200                       | 250              | μΑ    | 5.0V                     |  |  |  |  |

\* These parameters are characterized but not tested.

† Data in the "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only are not tested.

**Note 1:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

2: This is the additional current consumed by the A/D module when it is enabled; this current adds to base IDD.

### TABLE 10-6: A/D CONVERSION REQUIREMENTS

#### Standard Operating Conditions (unless otherwise stated) $-40^\circ C \le TA \le +125^\circ C$ Operating temperature Param Sym Characteristic Min Typ† Max Units Conditions No. Set GO/DONE bit to new data in A/D AD131 Conversion Time TCNV 13 TCY (not including Result register Acquisition Time) Acquisition Time<sup>(1)</sup> AD132\* TACQ 3.5 μS VDD = 5Vμs 5 VDD = 2.5V

\* These parameters are characterized but not tested.

† Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The **Section 7.9 "A/D Acquisition Requirements"** for information on how to compute minimum acquisition times based on operating conditions.

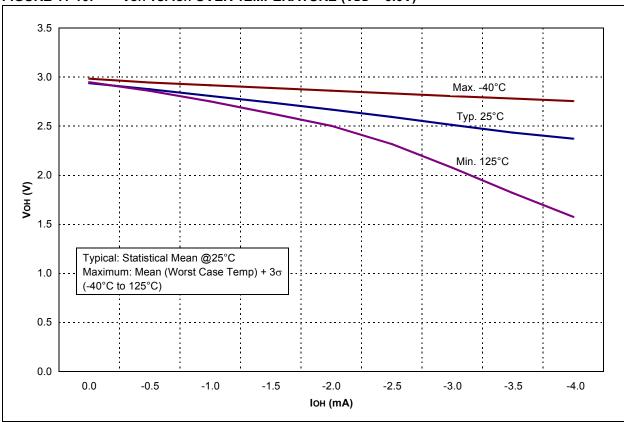

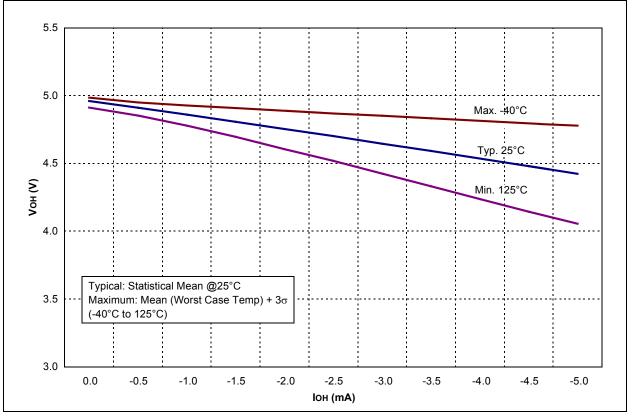

FIGURE 11-10: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

## 12.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 12.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# **13.0 PACKAGING INFORMATION**

# 13.1 Package Marking Information

8-Lead PDIP

#### 8-Lead DFN\*

Example

| Legend: | XXX<br>Y<br>YY<br>WW<br>NNN<br>@3<br>* | Product-specific information<br>Year code (last digit of calendar year)<br>Year code (last 2 digits of calendar year)<br>Week code (week of January 1 is week '01')<br>Alphanumeric traceability code<br>Pb-free JEDEC <sup>®</sup> designator for Matte Tin (Sn)<br>This package is Pb-free. The Pb-free JEDEC designator (e3)<br>can be found on the outer packaging for this package. |

|---------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | be carried                             | nt the full Microchip part number cannot be marked on one line, it will<br>d over to the next line, thus limiting the number of available<br>of or customer-specific information.                                                                                                                                                                                                        |

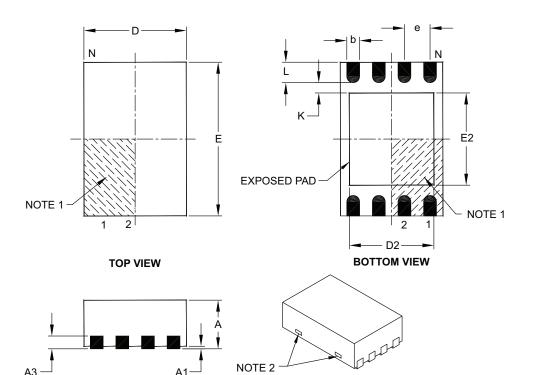

## 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units            |          | MILLIMETERS |      |  |  |

|------------------------|------------------|----------|-------------|------|--|--|

|                        | Dimension Limits | MIN      | NOM         | MAX  |  |  |

| Number of Pins         | N                | 8        |             |      |  |  |

| Pitch                  | e                |          | 0.50 BSC    |      |  |  |

| Overall Height         | A                | 0.80     | 0.90        | 1.00 |  |  |

| Standoff               | A1               | 0.00     | 0.02        | 0.05 |  |  |

| Contact Thickness      | A3               | 0.20 REF |             |      |  |  |

| Overall Length         | D                | 2.00 BSC |             |      |  |  |

| Overall Width          | E                | 3.00 BSC |             |      |  |  |

| Exposed Pad Length     | D2               | 1.30     | -           | 1.55 |  |  |

| Exposed Pad Width      | E2               | 1.50     | -           | 1.75 |  |  |

| Contact Width          | b                | 0.20     | 0.25        | 0.30 |  |  |

| Contact Length         | L                | 0.30     | 0.40        | 0.50 |  |  |

| Contact-to-Exposed Pad | К                | 0.20     | -           | _    |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C

NOTES:

# **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

**China - Hangzhou** Tel: 86-571-2819-3187 Fax: 86-571-2819-3189

China - Hong Kong SAR Tel: 852-2943-5100

Fax: 852-2401-3431 China - Nanjing

Tel: 86-25-8473-2460 Fax: 86-25-8473-2470 **China - Qingdao** Tel: 86-532-8502-7355

Fax: 86-532-8502-7205 China - Shanghai Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

**Malaysia - Penang** Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

**Taiwan - Kaohsiung** Tel: 886-7-213-7828 Fax: 886-7-330-9305

Taiwan - Taipei Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820