Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 8MHz                                                                     |

| Connectivity               | -                                                                        |

| Peripherals                | POR, WDT                                                                 |

| Number of I/O              | 4                                                                        |

| Program Memory Size        | 768B (512 x 12)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 23 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 2x8b                                                                 |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VFDFN Exposed Pad                                                      |

| Supplier Device Package    | 8-DFN (2x3)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f222-i-mc |

NOTES:

TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

| Address | Name               | Bit 7                                  | Bit 6                  | Bit 5     | Bit 4     | Bit 3                | Bit 2      | Bit 1          | Bit 0 | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

|---------|--------------------|----------------------------------------|------------------------|-----------|-----------|----------------------|------------|----------------|-------|----------------------------------------------|--------|

| 00h     | INDF               | Uses con                               | tents of FS            | SR to add | ress data | memory               | (not a phy | ysical registe | r)    | xxxx xxxx                                    | 20     |

| 01h     | TMR0               | 8-Bit Rea                              | I-Time Clo             | ck/Count  | er        |                      |            |                |       | xxxx xxxx                                    | 25     |

| 02h     | PCL <sup>(1)</sup> | Low Orde                               | Low Order 8 Bits of PC |           |           |                      |            |                |       | 1111 1111                                    | 19     |

| 03h     | STATUS             | GPWUF                                  | _                      | _         | TO        | PD                   | Z          | DC             | С     | 01 1xxx <sup>(3)</sup>                       | 15     |

| 04h     | FSR                | Indirect D                             | ata Memo               | ry Addres | s Pointer |                      | •          | •              | •     | 111x xxxx                                    | 20     |

| 05h     | OSCCAL             | CAL6                                   | CAL5                   | CAL4      | CAL3      | CAL2                 | CAL1       | CAL0           | FOSC4 | 1111 1110                                    | 18     |

| 06h     | GPIO               | _                                      | _                      | _         | _         | GP3                  | GP2        | GP1            | GP0   | xxxx                                         | 21     |

| 07h     | ADCON0             | ANS1                                   | ANS0                   | _         | _         | CHS1                 | CHS0       | GO/DONE        | ADON  | 11 1100                                      | 30     |

| 08h     | ADRES              | Result of Analog-to-Digital Conversion |                        |           |           |                      |            |                |       | xxxx xxxx                                    | 31     |

| N/A     | TRISGPIO           | _                                      | _                      | _         | _         | I/O Control Register |            |                |       | 1111                                         | 23     |

| N/A     | OPTION             | GPWU                                   | GPPU                   | T0CS      | T0SE      | PSA                  | PS2        | PS1            | PS0   | 1111 1111                                    | 17     |

**Legend:** - = unimplemented, read as '0', x = unknown, u = unchanged, q = value depends on condition.

- Note 1: The upper byte of the Program Counter is not directly accessible. See Section 4.7 "Program Counter" for an explanation of how to access these bits.

- 2: Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

- 3: See Table 8-1 for other Reset specific values.

### 4.4 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect Status bits, see Instruction Set Summary.

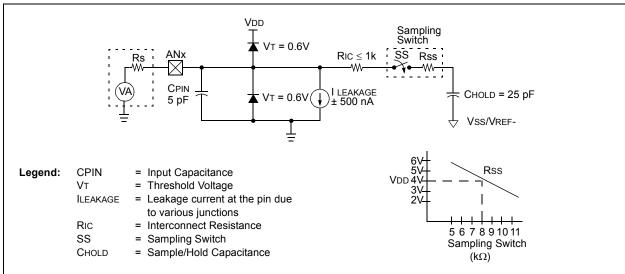

### 7.9 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 7-1. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-1. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### **EQUATION 7-1: ACQUISITION TIME EXAMPLE**

Assumptions:  $Temperature = 50^{\circ}C \text{ and external impedance of } 10 \text{ k}\Omega 5.0 \text{V VDD}$  Tacq = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF  $= 2 \mu s + TC + [(Temperature - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$ Solving for Tc:  $Tc = CHOLD (RIC + RSS + RS) \ln(1/512)$   $= -25pF (l k\Omega + 7 k\Omega + 10 k\Omega) \ln(0.00196)$   $= 2.81 \mu s$ Therefore:  $Tacq = 2 \mu s + 2.81 \mu s + [(50^{\circ}C - 25^{\circ}C)(0.05 \mu s/^{\circ}C)]$

Note 1: The charge holding capacitor (CHOLD) is not discharged after each conversion.

2: The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

### FIGURE 7-1: ANALOG INPUT MODULE

$= 6.06 \mu s$

# 8.0 SPECIAL FEATURES OF THE CPU

What sets a microcontroller apart from other processors are special circuits that deal with the needs of real-time applications. The PIC10F220/222 microcontrollers have a host of such features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving operating modes and offer code protection. These features are:

- Reset:

- Power-on Reset (POR)

- Device Reset Timer (DRT)

- Watchdog Timer (WDT)

- Wake-up from Sleep on pin change

- Sleep

- · Code Protection

- · ID Locations

- In-Circuit Serial Programming™

- · Clock Out

The PIC10F220/222 devices have a Watchdog Timer, which can be shut off only through Configuration bit WDTE. It runs off of its own RC oscillator for added reliability. When using DRT, there is an 1.125 ms (typical) delay only on VDD power-up. With this timer on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low current Power-Down mode. The user can wake-up from Sleep through a change on input pins or through a Watchdog Timer time-out.

### 8.1 Configuration Bits

The PIC10F220/222 Configuration Words consist of 12 bits. Configuration bits can be programmed to select various device configurations. One bit is the Watchdog Timer enable bit, one bit is the MCLR enable bit and one bit is for code protection (see Register 8-1).

### **REGISTER 8-1:** CONFIG: CONFIGURATION WORD<sup>(1)</sup>

| _      | - |  | _ | _ | _ | _ | MCLRE | CP | WDTE | MCPU | IOSCFS |

|--------|---|--|---|---|---|---|-------|----|------|------|--------|

| bit 11 |   |  |   |   |   |   |       |    |      |      | bit 0  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

- bit 11-5 Unimplemented: Read as '0'

- bit 4 MCLRE: GP3/MCLR Pin Function Select bit

- 1 =  $GP3/\overline{MCLR}$  pin function is  $\overline{MCLR}$

- 0 = GP3/MCLR pin function is digital I/O, MCLR internally tied to VDD

- bit 3 **CP:** Code Protection bit

- 1 = Code protection off

- 0 = Code protection on

- bit 2 WDTE: Watchdog Timer Enable bit

- 1 = WDT enabled

- 0 = WDT disabled

- bit 1 MCPU: Master Clear Pull-up Enable bit (2)

- 1 = Pull-up disabled

- 0 = Pull-up enabled

- bit 0 IOSCFS: Internal Oscillator Frequency Select bit

- 1 = 8 MHz

- 0 = 4 MHz

- **Note 1:** Refer to the "*PIC10F220/222 Memory Programming Specification*" (DS41266), to determine how to access the Configuration Word. The Configuration Word is not user addressable during device operation.

- 2: MCLRE must be a '1' to enable this selection.

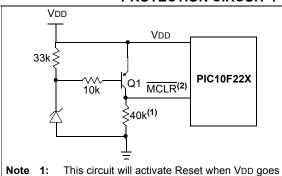

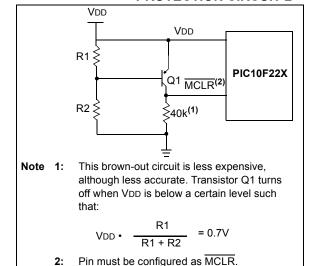

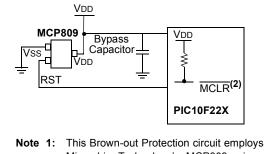

#### 8.8 Reset on Brown-out

A Brown-out is a condition where device power (VDD) dips below its minimum value, but not to zero, and then recovers. The device should be reset in the event of a Brown-out.

To reset PIC10F220/222 devices when a Brown-out occurs, external Brown-out protection circuits may be built, as shown in Figure 8-7 and Figure 8-8.

# FIGURE 8-7: BROWN-OUT PROTECTION CIRCUIT 1

# FIGURE 8-8: BROWN-OUT PROTECTION CIRCUIT 2

Pin must be configured as MCLR.

2:

below Vz + 0.7V (where  $Vz = Zener \ voltage$ ).

# FIGURE 8-9: BROWN-OUT PROTECTION CIRCUIT 3

- Note 1: This Brown-out Protection circuit employs Microchip Technology's MCP809 microcontroller supervisor. There are 7 different trip point selections to accommodate 5V to 3V systems.

- 2: Pin must be configured as MCLR.

### 8.9 Power-down Mode (Sleep)

A device may be powered down (Sleep) and later powered up (wake-up from Sleep).

#### 8.9.1 SLEEP

The Power-Down mode is entered by executing a SLEEP instruction.

If enabled, the Watchdog Timer will be cleared but keeps running, the  $\overline{\text{TO}}$  bit (STATUS<4>) is set, the  $\overline{\text{PD}}$  bit (STATUS<3>) is cleared and the oscillator driver is turned off. The I/O ports maintain the status they had before the SLEEP instruction was executed (driving high, driving low or high-impedance).

**Note:** A Reset generated by a WDT time-out does not drive the MCLR pin low.

For lowest current consumption while powered down, the T0CKI input should be at VDD or Vss and the GP3/MCLR/VPP pin must be at a logic high level if MCLR is enabled.

#### 8.9.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- An external Reset input on GP3/MCLR/VPP pin, when configured as  $\overline{\text{MCLR}}$ .

- 2. A Watchdog Timer Time-out Reset (if WDT was enabled).

- 3. A change on input pin GP0, GP1 or GP3 when wake-up on change is enabled.

These events cause a device Reset. The TO. PD GPWUF bits can be used to determine the cause of a device Reset. The TO bit is cleared if a WDT time-out occurred (and caused wake-up). The PD bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in Sleep at pins GP0, GP1 or GP3 (since the last file or bit operation on GP port).

Caution: Right before entering Sleep, read the input pins. When in Sleep, wake up occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before re-entering Sleep, a wake-up will occur immediately even if no pins change while in Sleep mode.

Note: The WDT is cleared when the device wakes from Sleep, regardless of the wakeup source.

#### 8.10 **Program Verification/Code Protection**

If the Code Protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (Reset Vector) can be read, regardless of the code protection bit setting.

#### 8.11 **ID Locations**

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '1's.

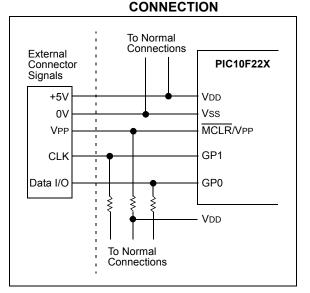

#### In-Circuit Serial Programming™ 8.12

The PIC10F220/222 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1 becomes the programming clock and GP0 becomes the programming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 16 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC10F220/222 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 8-10.

**FIGURE 8-10: TYPICAL IN-CIRCUIT**

SERIAL **PROGRAMMING™**

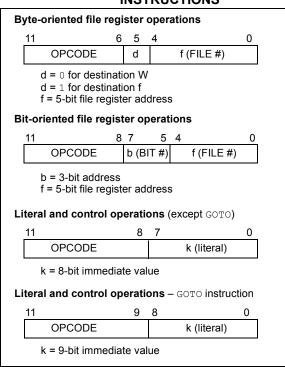

#### 9.0 INSTRUCTION SET SUMMARY

The PIC16 instruction set is highly orthogonal and is comprised of three basic categories.

- · Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

Each PIC16 instruction is a 12-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands** which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 9-1, while the various opcode fields are summarized in Table 9-1.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator which selects the number of the bit affected by the operation, while 'f' represents the number of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8 or 9-bit constant or literal value.

TABLE 9-1: OPCODE FIELD DESCRIPTIONS

| Field         | Description                                                                                                                                                        |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f             | Register file address (0x00 to 0x7F)                                                                                                                               |

| W             | Working register (accumulator)                                                                                                                                     |

| b             | Bit address within an 8-bit file register                                                                                                                          |

| k             | Literal field, constant data or label                                                                                                                              |

| х             | Don't care location (= 0 or 1) The assembler will generate code with x = 0. It is the recommended form of use for compatibility with all Microchip software tools. |

| d             | Destination select; d = 0 (store result in W) d = 1 (store result in file register 'f') Default is d = 1                                                           |

| label         | Label name                                                                                                                                                         |

| TOS           | Top-of-Stack                                                                                                                                                       |

| PC            | Program Counter                                                                                                                                                    |

| WDT           | Watchdog Timer counter                                                                                                                                             |

| TO            | Time-out bit                                                                                                                                                       |

| PD            | Power-down bit                                                                                                                                                     |

| dest          | Destination, either the W register or the specified register file location                                                                                         |

| [ ]           | Options                                                                                                                                                            |

| ( )           | Contents                                                                                                                                                           |

| $\rightarrow$ | Assigned to                                                                                                                                                        |

| < >           | Register bit field                                                                                                                                                 |

| €             | In the set of                                                                                                                                                      |

| italics       | User defined term (font is courier)                                                                                                                                |

All instructions are executed within a single instruction cycle, unless a conditional test is true or the program counter is changed as a result of an instruction. In this case, the execution takes two instruction cycles. One instruction cycle consists of four oscillator periods. Thus, for an oscillator frequency of 4 MHz, the normal instruction execution time is 1  $\mu$ s. If a conditional test is true or the program counter is changed as a result of an instruction, the instruction execution time is 2  $\mu$ s.

Figure 9-1 shows the three general formats that the instructions can have. All examples in the figure use the following format to represent a hexadecimal number:

'0xhhh'

where 'h' signifies a hexadecimal digit.

# FIGURE 9-1: GENERAL FORMAT FOR INSTRUCTIONS

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                         |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] BTFSS f,b                                                                                                                                                               |

| Operands:        | $0 \le f \le 31$<br>$0 \le b < 7$                                                                                                                                               |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '1', then the next instruction is skipped.                                                                                                        |

|                  | If bit 'b' is '1', then the next instruction fetched during the current instruction execution, is discarded and a NOP is executed instead, making this a two-cycle instruction. |

| CLRW             | Clear W                                         |

|------------------|-------------------------------------------------|

| Syntax:          | [label] CLRW                                    |

| Operands:        | None                                            |

| Operation:       | $00h \rightarrow (W);$ $1 \rightarrow Z$        |

| Status Affected: | Z                                               |

| Description:     | The W register is cleared. Zero bit (Z) is set. |

|                  |                                                 |

|                  |                                                 |

| CALL             | Subroutine Call                                                                                                                                                                                                               |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                                                |

| Operands:        | $0 \leq k \leq 255$                                                                                                                                                                                                           |

| Operation:       | (PC) + 1 $\rightarrow$ Top of Stack;<br>k $\rightarrow$ PC<7:0>;<br>(Status<6:5>) $\rightarrow$ PC<10:9>;<br>0 $\rightarrow$ PC<8>                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | Subroutine call. First, return address (PC + 1) is pushed onto the stack. The eight-bit immediate address is loaded into PC bits <7:0>. The upper bits PC<10:9> are loaded from STATUS<6:5>, PC<8> is cleared. CALL is a two- |

| CLRWDT           | Clear Watchdog Timer                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CLRWDT k                                                                                                                                                                                    |

| Operands:        | None                                                                                                                                                                                                |

| Operation:       | 00h → WDT;<br>0 → WDT prescaler (if assigned);<br>1 → $\overline{TO}$ ;<br>1 → $\overline{PD}$                                                                                                      |

| Status Affected: | TO, PD                                                                                                                                                                                              |

| Description:     | The CLRWDT instruction resets the WDT. It also resets the prescaler, if the prescaler is assigned to the WDT and not Timer0. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set. |

| CLRF             | Clear f                                                        |

|------------------|----------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                 |

| Operands:        | $0 \leq f \leq 31$                                             |

| Operation:       | $00h \rightarrow (f);$ $1 \rightarrow Z$                       |

| Status Affected: | Z                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |

cycle instruction.

| COMF             | Complement f                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                                              |

| Operands:        | $0 \le f \le 31$<br>$d \in [0,1]$                                                                                                                               |

| Operation:       | $(\bar{f}) \to (dest)$                                                                                                                                          |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |

## 10.3 DC Characteristics: PIC10F220/222 (Industrial, Extended)

| DC CHA       | RACTI | ERISTICS                             | $\begin{tabular}{lll} Standard Operating Conditions (unless otherwise specified) \\ Operating temperature & -40 ^{\circ}C \leq TA \leq +85 ^{\circ}C \mbox{ (industrial)} \\ & -40 ^{\circ}C \leq TA \leq +125 ^{\circ}C \mbox{ (extended)} \\ Operating voltage VDD range as described in DC specification \\ \end{tabular}$ |      |          |       |                                                                                                           |  |

|--------------|-------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|-----------------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Sym   | Characteristic                       | Min                                                                                                                                                                                                                                                                                                                           | Тур† | Max      | Units | Conditions                                                                                                |  |

|              | VIL   | Input Low Voltage                    |                                                                                                                                                                                                                                                                                                                               |      |          |       |                                                                                                           |  |

|              |       | I/O ports:                           |                                                                                                                                                                                                                                                                                                                               |      |          |       |                                                                                                           |  |

| D030         |       | with TTL buffer                      | Vss                                                                                                                                                                                                                                                                                                                           | _    | 0.8      | V     | For all 4.5 ≤ VDD ≤ 5.5V                                                                                  |  |

| D030A        |       |                                      | Vss                                                                                                                                                                                                                                                                                                                           | _    | 0.15 VDD | V     | Otherwise                                                                                                 |  |

| D031         |       | with Schmitt Trigger<br>buffer       | Vss                                                                                                                                                                                                                                                                                                                           | _    | 0.2 VDD  | V     |                                                                                                           |  |

| D032         |       | MCLR, TOCKI                          | Vss                                                                                                                                                                                                                                                                                                                           | _    | 0.2 VDD  | V     |                                                                                                           |  |

|              | VIH   | Input High Voltage                   |                                                                                                                                                                                                                                                                                                                               |      |          |       |                                                                                                           |  |

|              |       | I/O ports:                           |                                                                                                                                                                                                                                                                                                                               | _    |          |       |                                                                                                           |  |

| D040         |       | with TTL buffer                      | 2.0                                                                                                                                                                                                                                                                                                                           | _    | VDD      | V     | $4.5 \le VDD \le 5.5V$                                                                                    |  |

| D040A        |       |                                      | 0.25 VDD + 0.8                                                                                                                                                                                                                                                                                                                | _    | VDD      | V     | Otherwise                                                                                                 |  |

| D041         |       | with Schmitt Trigger<br>buffer       | 0.8VDD                                                                                                                                                                                                                                                                                                                        | _    | VDD      | V     | For entire VDD range                                                                                      |  |

| D042         |       | MCLR, TOCKI                          | 0.8VDD                                                                                                                                                                                                                                                                                                                        | _    | VDD      | V     |                                                                                                           |  |

| D070         | IPUR  | GPIO weak pull-up current            | 50                                                                                                                                                                                                                                                                                                                            | 250  | 400      | μА    | VDD = 5V, VPIN = VSS                                                                                      |  |

|              | lıL   | Input Leakage Current <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                               |      |          |       |                                                                                                           |  |

| D060         |       | I/O ports                            | _                                                                                                                                                                                                                                                                                                                             | ±0.1 | ± 1      | μА    | $\label{eq:VDD}  \mbox{Vss} \leq \mbox{VPIN} \leq \mbox{VDD}, \mbox{ Pin at high-imped-} \\ \mbox{ance} $ |  |

| D061         |       | GP3/MCLR <sup>(2)</sup>              | _                                                                                                                                                                                                                                                                                                                             | ±0.7 | ± 5      | μА    | Vss ≤ VPIN ≤ VDD                                                                                          |  |

|              |       | Output Low Voltage                   |                                                                                                                                                                                                                                                                                                                               |      |          |       |                                                                                                           |  |

| D080         |       | I/O ports                            | _                                                                                                                                                                                                                                                                                                                             | _    | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V, -40°C to +85°C                                                                  |  |

| D080A        |       |                                      | _                                                                                                                                                                                                                                                                                                                             | _    | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V, -40°C to +125°C                                                                 |  |

|              |       | Output High Voltage                  | •                                                                                                                                                                                                                                                                                                                             |      |          | •     |                                                                                                           |  |

| D090         |       | I/O ports <sup>(2)</sup>             | VDD - 0.7                                                                                                                                                                                                                                                                                                                     | _    | _        | V     | IOH = -3.0 mA, VDD = 4.5V, -40°C to +85°C                                                                 |  |

| D090A        |       |                                      | VDD - 0.7                                                                                                                                                                                                                                                                                                                     | _    | _        | V     | IOH = -2.5 mA, VDD = 4.5V, -40°C to<br>+125°C                                                             |  |

|              |       | Capacitive Loading Specs on          | Output Pins                                                                                                                                                                                                                                                                                                                   |      |          |       |                                                                                                           |  |

| D101         |       | All I/O pins                         | _                                                                                                                                                                                                                                                                                                                             | _    | 50*      | pF    |                                                                                                           |  |

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

<sup>\*</sup> These parameters are for design guidance only and are not tested.

Note 1: Negative current is defined as coming out of the pin.

<sup>2:</sup> This specification applies when GP3/MCLR is configured as an input with pull-up disabled. The leakage current of the MCLR circuit is higher than the standard I/O logic.

TABLE 10-1: PULL-UP RESISTOR RANGES

| VDD (Volts) | Temperature (°C) | Min | Тур  | Max  | Units |

|-------------|------------------|-----|------|------|-------|

| GP0/GP1     |                  |     |      |      |       |

| 2.0         | -40              | 73K | 105K | 186K | Ω     |

|             | 25               | 73K | 113K | 187K | Ω     |

|             | 85               | 82K | 123K | 190K | Ω     |

|             | 125              | 86K | 132k | 190K | Ω     |

| 5.5         | -40              | 15K | 21K  | 33K  | Ω     |

|             | 25               | 15K | 22K  | 34K  | Ω     |

|             | 85               | 19K | 26k  | 35K  | Ω     |

|             | 125              | 23K | 29K  | 35K  | Ω     |

| GP3         | <u> </u>         |     |      |      |       |

| 2.0         | -40              | 63K | 81K  | 96K  | Ω     |

|             | 25               | 77K | 93K  | 116K | Ω     |

|             | 85               | 82K | 96k  | 116K | Ω     |

|             | 125              | 86K | 100K | 119K | Ω     |

| 5.5         | -40              | 16K | 20k  | 22K  | Ω     |

|             | 25               | 16K | 21K  | 23K  | Ω     |

|             | 85               | 24K | 25k  | 28K  | Ω     |

|             | 125              | 26K | 27K  | 29K  | Ω     |

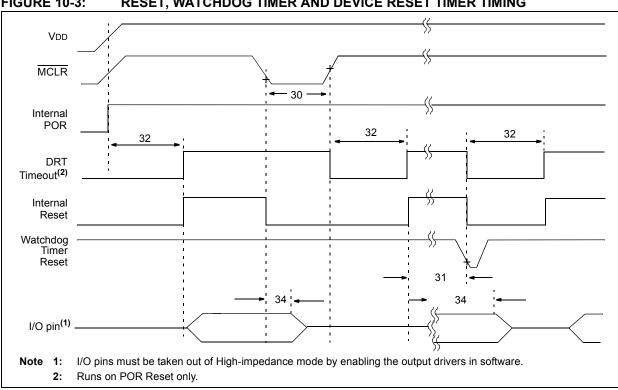

RESET, WATCHDOG TIMER AND DEVICE RESET TIMER TIMING FIGURE 10-3:

**TABLE 10-3:** RESET, WATCHDOG TIMER AND DEVICE RESET TIMER - PIC10F220/222

| AC CHARACTERISTICS |       |                                                      | Standard Operating Conditions (unless otherwise specified)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ (industrial) $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ (extended)  Operating Voltage VDD range is described in Section 10.1 "DC Characteristics: PIC10F220/222 (Industrial)" |                    |              |                          |                                                  |  |

|--------------------|-------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--------------------------|--------------------------------------------------|--|

| Param<br>No.       | Sym   | Characteristic                                       | Min                                                                                                                                                                                                                                                                                                                                           | Typ <sup>(1)</sup> | Max          | Units                    | Conditions                                       |  |

| 30                 | Тмс   | MCLR Pulse Width (low)                               | 2*<br>5*                                                                                                                                                                                                                                                                                                                                      |                    |              | μ <b>S</b><br>μ <b>S</b> | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |  |

| 31                 | TWDT  | Watchdog Timer Time-out Period (no prescaler)        | 10<br>10                                                                                                                                                                                                                                                                                                                                      | 18<br>18           | 29<br>31     | ms<br>ms                 | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |

| 32                 | TDRT* | Device Reset Timer Period (standard)                 | 0.600<br>0.600                                                                                                                                                                                                                                                                                                                                | 1.125<br>1.125     | 1.85<br>1.95 | ms<br>ms                 | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |

| 34                 | Tıoz  | I/O High-impedance from $\overline{\text{MCLR}}$ low | _                                                                                                                                                                                                                                                                                                                                             | _                  | 2*           | μS                       |                                                  |  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 10-5: A/D CONVERTER CHARACTERISTICS

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$

| Param<br>No. | Sym  | Characteristic                                       | Min  | Typ†                      | Max              | Units | Conditions               |

|--------------|------|------------------------------------------------------|------|---------------------------|------------------|-------|--------------------------|

| A01          | NR   | Resolution                                           |      | _                         | 8 bits           | bit   |                          |

| A03          | EIL  | Integral Error                                       | _    | _                         | ±1.5             | LSb   |                          |

| A04          | EDL  | Differential Error                                   | _    | _                         | -1 < EDL ≤ + 1.5 | LSb   |                          |

| A05          | EFS  | Full-scale Range                                     | 2.0* | _                         | 5.5*             | V     |                          |

| A06          | Eoff | Offset Error                                         | _    | _                         | ±1.5             | LSb   |                          |

| A07          | Egn  | Gain Error                                           | _    | _                         | ±1.5             | LSb   |                          |

| A10          | _    | Monotonicity                                         | _    | guaranteed <sup>(1)</sup> | _                | _     | $Vss \leq Vain \leq Vdd$ |

| A25          | VAIN | Analog Input Voltage                                 | Vss  | _                         | VDD              | V     |                          |

| A30          | ZAIN | Recommended<br>Impedence of Analog<br>Voltage Source | _    | _                         | 10               | kΩ    |                          |

| A31*         | ΔIAD | A/D Conversion Current <sup>(2)</sup>                |      | 120                       | 150              | μΑ    | 2.0V                     |

|              |      |                                                      | _    | 200                       | 250              | μΑ    | 5.0V                     |

- \* These parameters are characterized but not tested.

- † Data in the "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only are not tested.

- **Note 1:** The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

- 2: This is the additional current consumed by the A/D module when it is enabled; this current adds to base IDD.

### TABLE 10-6: A/D CONVERSION REQUIREMENTS

Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}\text{C} \le \text{Ta} \le +125^{\circ}\text{C}$

| Param<br>No. | Sym  | Characteristic                                         | Min | Тур†     | Max | Units    | Conditions                                         |

|--------------|------|--------------------------------------------------------|-----|----------|-----|----------|----------------------------------------------------|

| AD131        |      | Conversion Time<br>(not including<br>Acquisition Time) |     | 13       | _   | Tcy      | Set GO/DONE bit to new data in A/D Result register |

| AD132*       | TACQ | Acquisition Time <sup>(1)</sup>                        |     | 3.5<br>5 |     | μS<br>μS | V <sub>DD</sub> = 5V<br>V <sub>DD</sub> = 2.5V     |

- \* These parameters are characterized but not tested.

- † Data in 'Typ' column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** The **Section 7.9 "A/D Acquisition Requirements"** for information on how to compute minimum acquisition times based on operating conditions.

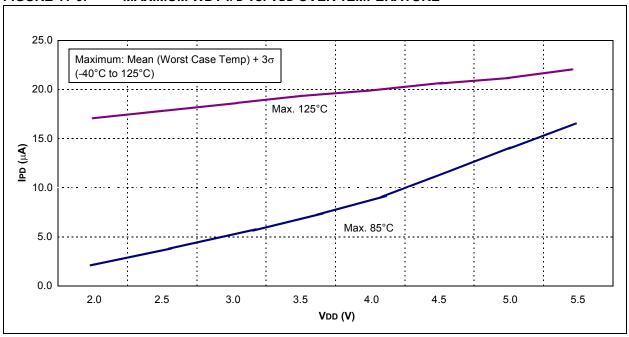

FIGURE 11-6: MAXIMUM WDT IPD vs. VDD OVER TEMPERATURE

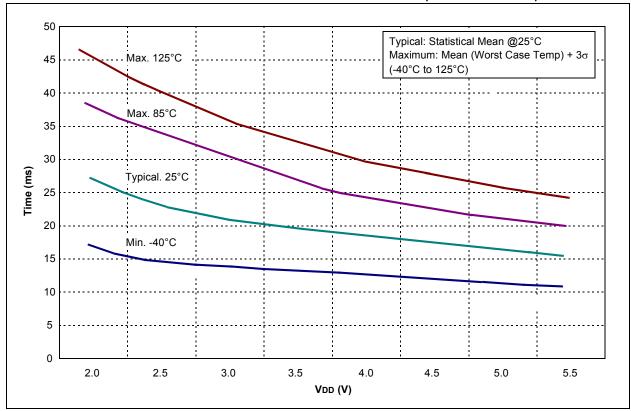

FIGURE 11-7: WDT TIME-OUT vs. VDD OVER TEMPERATURE (NO PRESCALER)

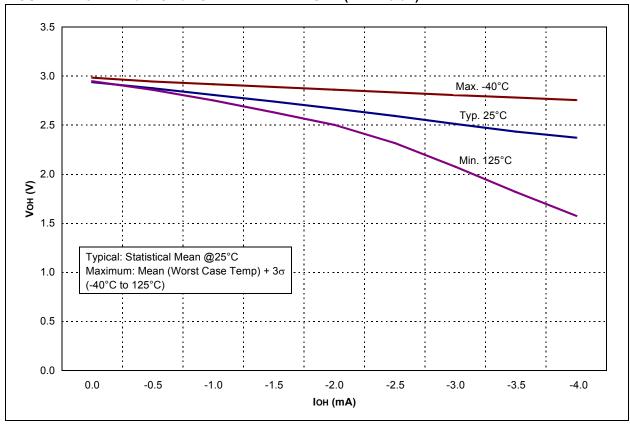

FIGURE 11-10: VOH vs. IOH OVER TEMPERATURE (VDD = 3.0V)

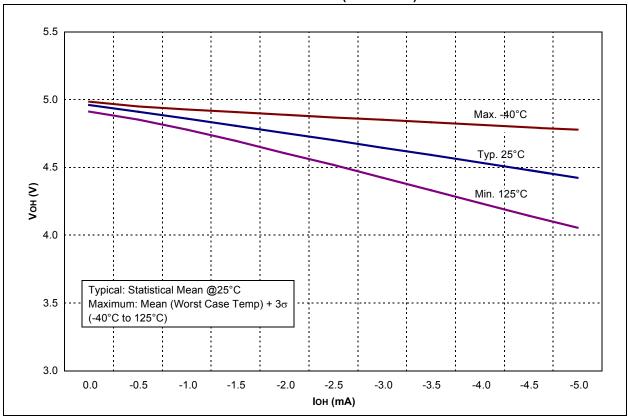

FIGURE 11-11: VOH vs. IOH OVER TEMPERATURE (VDD = 5.0V)

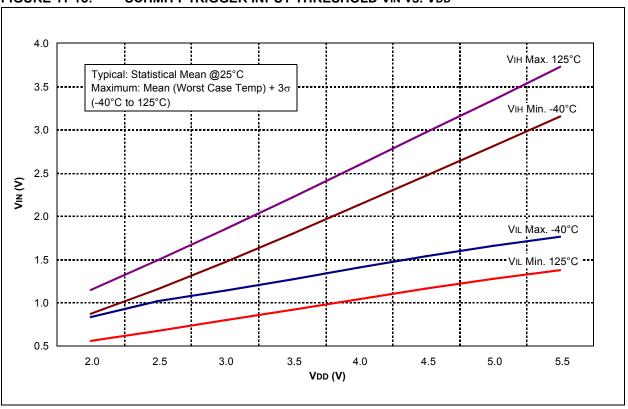

FIGURE 11-12: TTL INPUT THRESHOLD VIN vs. VDD

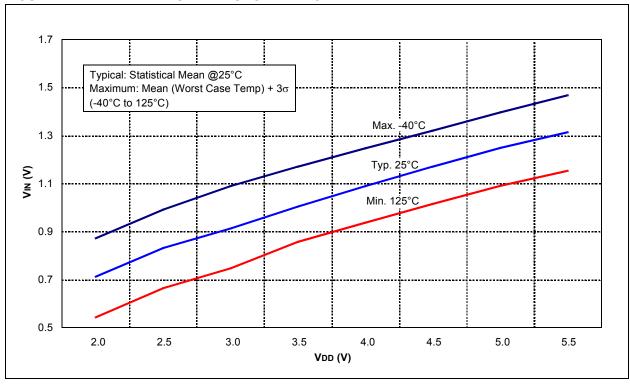

FIGURE 11-13: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD

### 13.0 PACKAGING INFORMATION

### 13.1 Package Marking Information

8-Lead PDIP

8-Lead DFN\*

Example

Example

Legend: XX...X Product-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

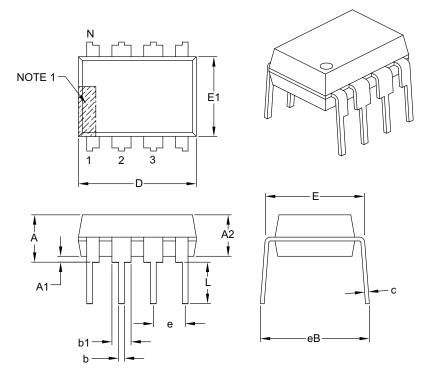

## 8-Lead Plastic Dual In-Line (P) - 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units            | INCHES |          |      |  |  |

|----------------------------|------------------|--------|----------|------|--|--|

|                            | Dimension Limits | MIN    | NOM      | MAX  |  |  |

| Number of Pins             | Number of Pins N |        | 8        |      |  |  |

| Pitch                      | е                |        | .100 BSC |      |  |  |

| Top to Seating Plane       | А                | _      | _        | .210 |  |  |

| Molded Package Thickness   | A2               | .115   | .130     | .195 |  |  |

| Base to Seating Plane      | A1               | .015   | _        | -    |  |  |

| Shoulder to Shoulder Width | E                | .290   | .310     | .325 |  |  |

| Molded Package Width       | E1               | .240   | .250     | .280 |  |  |

| Overall Length             | D                | .348   | .365     | .400 |  |  |

| Tip to Seating Plane       | L                | .115   | .130     | .150 |  |  |

| Lead Thickness             | С                | .008   | .010     | .015 |  |  |

| Upper Lead Width           | b1               | .040   | .060     | .070 |  |  |

| Lower Lead Width           | b                | .014   | .018     | .022 |  |  |

| Overall Row Spacing §      | eB               | _      | -        | .430 |  |  |

### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

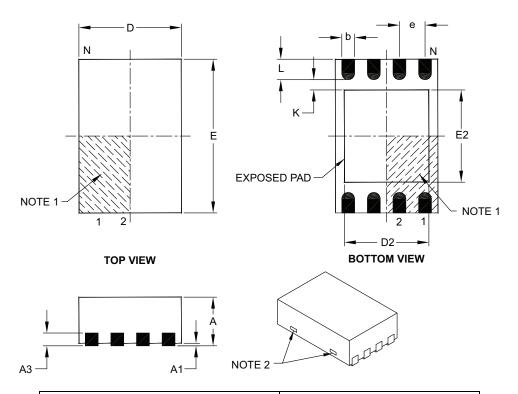

## 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | MILLIMETERS |      |      |  |

|------------------------|----------|-------------|------|------|--|

| Dimension              | n Limits | MIN         | NOM  | MAX  |  |

| Number of Pins         | N        |             | 8    |      |  |

| Pitch                  | е        | 0.50 BSC    |      |      |  |

| Overall Height         | Α        | 0.80        | 0.90 | 1.00 |  |

| Standoff               | A1       | 0.00        | 0.02 | 0.05 |  |

| Contact Thickness      | А3       | 0.20 REF    |      |      |  |

| Overall Length         | D        | 2.00 BSC    |      |      |  |

| Overall Width          | Е        | 3.00 BSC    |      |      |  |

| Exposed Pad Length     | D2       | 1.30        | _    | 1.55 |  |

| Exposed Pad Width      | E2       | 1.50        | _    | 1.75 |  |

| Contact Width          | b        | 0.20        | 0.25 | 0.30 |  |

| Contact Length         | L        | 0.30        | 0.40 | 0.50 |  |

| Contact-to-Exposed Pad | K        | 0.20        | _    | _    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

$\label{eq:REF:Reference} \textbf{REF: Reference Dimension, usually without tolerance, for information purposes only.}$

Microchip Technology Drawing C04-123C

## W

| Wake-up from Sleep         | 41     |

|----------------------------|--------|

| Watchdog Timer (WDT)       | 33, 38 |

| Period                     | 38     |

| Programming Considerations | 38     |

| WWW Address                |        |

| WWW, On-Line Support       | 3      |

| Z                          |        |

| Zero bit                   | ç      |

### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

### **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- · Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support