Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                  |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | -                                                                       |

| Peripherals                | POR, WDT                                                                |

| Number of I/O              | 4                                                                       |

| Program Memory Size        | 768B (512 x 12)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 23 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 2x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f222-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 6-Pin, 8-Bit Flash Microcontrollers

#### **Device Included In This Data Sheet:**

- PIC10F220

- PIC10F222

#### High-Performance RISC CPU:

- Only 33 Single-Word Instructions to Learn

- All Single-Cycle Instructions Except for Program Branches which are Two-Cycle

- 12-bit Wide Instructions

- 2-Level Deep Hardware Stack

- Direct, Indirect and Relative Addressing modes for Data and Instructions

- · 8-bit Wide Data Path

- 8 Special Function Hardware Registers

- · Operating Speed:

- 500 ns instruction cycle with 8 MHz internal clock

- 1  $\mu s$  instruction cycle with 4 MHz internal clock

#### **Special Microcontroller Features:**

- 4 or 8 MHz Precision Internal Oscillator:

- Factory calibrated to ±1%

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

- · In-Circuit Debugging (ICD) Support

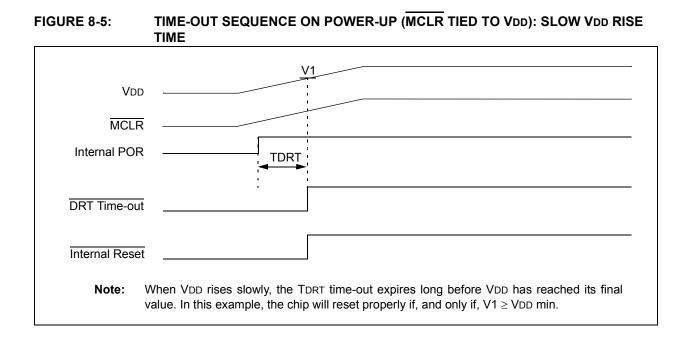

- Power-On Reset (POR)

- Short Device Reset Timer, DRT (1.125 ms typical)

- Watchdog Timer (WDT) with Dedicated On-Chip RC Oscillator for Reliable Operation

- Programmable Code Protection

- Multiplexed MCLR Input Pin

- Internal Weak Pull-Ups on I/O Pins

- · Power-Saving Sleep mode

- Wake-up from Sleep on Pin Change

#### Low-Power Features/CMOS Technology:

- Operating Current:

- < 175 μA @ 2V, 4 MHz

- Standby Current:

- 100 nA @ 2V, typical

- Low-Power, High-Speed Flash Technology:

- 100,000 Flash endurance

- > 40-year retention

- · Fully Static Design

- Wide Operating Voltage Range: 2.0V to 5.5V

- Wide Temperature Range:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

#### **Peripheral Features:**

- 4 I/O Pins:

- 3 I/O pins with individual direction control

- 1 input only pin

- High current sink/source for direct LED drive

- Wake-on-change

- Weak pull-ups

- 8-bit Real-Time Clock/Counter (TMR0) with 8-bit Programmable Prescaler

- Analog-to-Digital (A/D) Converter:

- 8-bit resolution

- 2 external input channels

- 1 internal input channel dedicated

| Device    | Program Memory | Data Memory  | I/O | Timers | 8-Bit A/D (ch)  |  |

|-----------|----------------|--------------|-----|--------|-----------------|--|

| Device    | Flash (words)  | SRAM (bytes) | 1/0 | 8-bit  | o-Bit A/D (Cit) |  |

| PIC10F220 | 256            | 16           | 4   | 1      | 2               |  |

| PIC10F222 | 512            | 23           | 4   | 1      | 2               |  |

NOTES:

### 2.0 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC10F220/222 Product Identification System at the back of this data sheet to specify the correct part number.

#### 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

#### 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

#### 4.0 MEMORY ORGANIZATION

The PIC10F220/222 memories are organized into program memory and data memory. Data memory banks are accessed using the File Select Register (FSR).

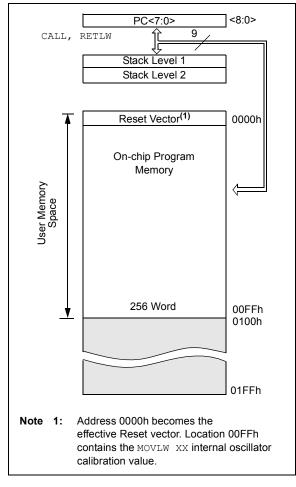

# 4.1 Program Memory Organization for the PIC10F220

The PIC10F220 devices have a 9-bit Program Counter (PC) capable of addressing a 512 x 12 program memory space.

Only the first 256 x 12 (0000h-00FFh) for the PIC10F220 are physically implemented (see Figure 4-1). Accessing a location above these boundaries will cause a wrap-around within the first 256 x 12 space (PIC10F220). The effective Reset vector is at 0000h, (see Figure 4-1). Location 00FFh (PIC10F220) contains the internal clock oscillator calibration value. This value should never be overwritten.

#### FIGURE 4-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC10F220

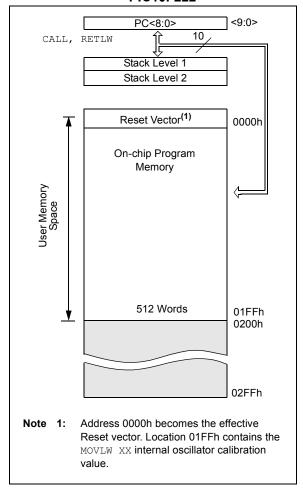

# 4.2 Program Memory Organization for the PIC10F222

The PIC10F222 devices have a 10-bit Program Counter (PC) capable of addressing a 1024 x 12 program memory space.

Only the first 512 x 12 (0000h-01FFh) for the Mem-High are physically implemented (see Figure 4-2). Accessing a location above these boundaries will cause a wrap-around within the first 512 x 12 space (PIC10F222). The effective Reset vector is at 0000h, (see Figure 4-2). Location 01FFh (PIC10F222) contains the internal clock oscillator calibration value. This value should never be overwritten.

# FIGURE 4-2:

#### PROGRAM MEMORY MAP AND STACK FOR THE PIC10F222

| Address | Name               | Bit 7                                  | Bit 6        | Bit 5     | Bit 4     | Bit 3     | Bit 2 | Bit 1   | Bit 0 | Value on<br>Power-On<br>Reset <sup>(2)</sup> | Page # |

|---------|--------------------|----------------------------------------|--------------|-----------|-----------|-----------|-------|---------|-------|----------------------------------------------|--------|

| 00h     | INDF               | Uses con                               | XXXX XXXX    | 20        |           |           |       |         |       |                                              |        |

| 01h     | TMR0               | 8-Bit Rea                              | I-Time Clo   | ck/Count  | er        |           |       |         |       | XXXX XXXX                                    | 25     |

| 02h     | PCL <sup>(1)</sup> | Low Orde                               | er 8 Bits of | PC        |           |           |       |         |       | 1111 1111                                    | 19     |

| 03h     | STATUS             | GPWUF                                  | —            | _         | TO        | PD        | Z     | DC      | С     | 01 1xxx <sup>(3)</sup>                       | 15     |

| 04h     | FSR                | Indirect D                             | ata Memo     | ry Addres | s Pointer |           |       |         |       | 111x xxxx                                    | 20     |

| 05h     | OSCCAL             | CAL6                                   | CAL5         | CAL4      | CAL3      | CAL2      | CAL1  | CAL0    | FOSC4 | 1111 1110                                    | 18     |

| 06h     | GPIO               | —                                      |              | —         |           | GP3       | GP2   | GP1     | GP0   | xxxx                                         | 21     |

| 07h     | ADCON0             | ANS1                                   | ANS0         | _         | _         | CHS1      | CHS0  | GO/DONE | ADON  | 11 1100                                      | 30     |

| 08h     | ADRES              | Result of Analog-to-Digital Conversion |              |           |           |           |       |         |       | XXXX XXXX                                    | 31     |

| N/A     | TRISGPIO           | —                                      | —            | —         | —         | I/O Conti | 1111  | 23      |       |                                              |        |

| N/A     | OPTION             | GPWU                                   | GPPU         | TOCS      | T0SE      | PSA       | PS2   | PS1     | PS0   | 1111 1111                                    | 17     |

TABLE 4-1: SPECIAL FUNCTION REGISTER (SFR) SUMMARY

Legend: -= unimplemented, read as '0', x = unknown, u = unchanged, g = value depends on condition.

**Note 1:** The upper byte of the Program Counter is not directly accessible. See **Section 4.7 "Program Counter"** for an explanation of how to access these bits.

2: Other (non Power-up) Resets include external Reset through MCLR, Watchdog Timer and wake-up on pin change Reset.

3: See Table 8-1 for other Reset specific values.

#### 4.4 STATUS Register

This register contains the arithmetic status of the ALU, the Reset status and the page preselect bit.

The STATUS register can be the destination for any instruction, as with any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS will clear the upper three bits and set the Z bit. This leaves the STATUS register as 000u uluu (where u = unchanged).

Therefore, it is recommended that only BCF, BSF and MOVWF instructions be used to alter the STATUS register. These instructions do not affect the Z, DC or C bits from the STATUS register. For other instructions, which do affect Status bits, see Instruction Set Summary.

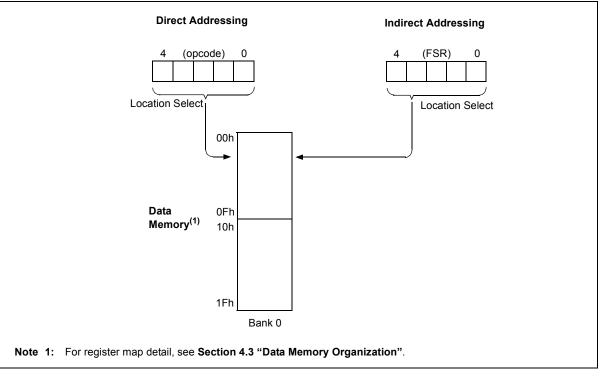

#### 4.9 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### 4.9.1 INDIRECT ADDRESSING

- · Register file 09 contains the value 10h

- · Register file 0A contains the value 0Ah

- · Load the value 09 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 0A)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

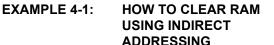

A simple program to clear RAM locations 10h-1Fh using Indirect addressing is shown in Example 4-1.

#### FIGURE 4-6: DIRECT/INDIRECT ADDRESSING

|      |                                |                              | DILLOUINO                                                                  |

|------|--------------------------------|------------------------------|----------------------------------------------------------------------------|

| NEXT | MOVLW<br>MOVWF<br>CLRF<br>INCF | 0x10<br>FSR<br>INDF<br>FSR,F | ;initialize pointer<br>;to RAM<br>;clear INDF<br>;register<br>;inc pointer |

|      | BTFSC<br>GOTO                  | FSR <b>,</b> 4<br>NEXT       | ;all done?<br>;NO, clear next                                              |

| CONT | INUE                           |                              |                                                                            |

|      | :                              |                              | ;YES, continue                                                             |

|      | :                              |                              |                                                                            |

|      |                                |                              |                                                                            |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**Note:** Do not use banking. FSR <7:5> are unimplemented and read as '1's.

NOTES:

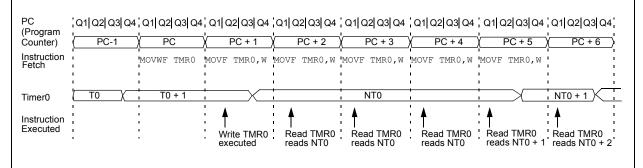

#### FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                    | Bit 7    | Bit 6     | Bit 5     | Bit 4    | Bit 3           | Bit 2     | Bit 1 | Bit 0 | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|----------|-----------|-----------|----------|-----------------|-----------|-------|-------|-------------------------------|---------------------------------|

| 01h     | TMR0                    | Timer0 – | 8-Bit Rea | I-Time CI | ock/Cour | nter            |           |       |       | XXXX XXXX                     | uuuu uuuu                       |

| N/A     | OPTION                  | GPWU     | GPPU      | TOCS      | T0SE     | PSA PS2 PS1 PS0 |           |       |       | 1111 1111                     | 1111 1111                       |

| N/A     | TRISGPIO <sup>(1)</sup> | —        | _         |           |          | I/O Cor         | ntrol Reg | ister |       | 1111                          | 1111                            |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged.

Note 1: The TRIS of the TOCKI pin is overridden when TOCS = 1

#### 6.1 Using Timer0 With An External Clock

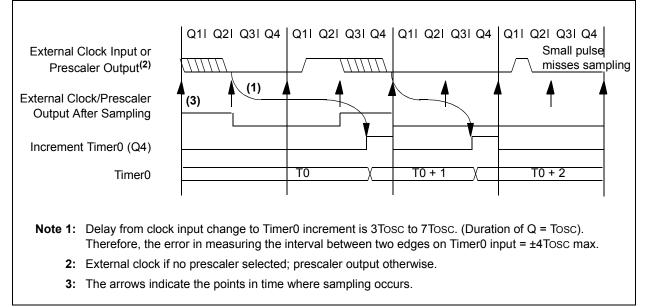

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

#### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 2Tt0H) and low for at least 2Tosc (and a small RC delay of 2Tt0H). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 4Tt0H) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

#### 6.1.2 TIMER0 INCREMENT DELAY

Since the prescaler output is synchronized with the internal clocks, there is a small delay from the time the external clock edge occurs to the time the Timer0 module is actually incremented. Figure 6-4 shows the delay from the external clock edge to the timer incrementing.

#### 6.2 Prescaler

An 8-bit counter is available as a prescaler for the Timer0 module or as a postscaler for the Watchdog Timer (WDT), respectively (see Section 8.6 "Watchdog Timer (WDT)"). For simplicity, this counter is being referred to as "prescaler" throughout this data sheet.

| Note: | The prescaler may be used by either the |

|-------|-----------------------------------------|

|       | Timer0 module or the WDT, but not both. |

|       | Thus, a prescaler assignment for the    |

|       | Timer0 module means that there is no    |

|       | prescaler for the WDT and vice-versa.   |

The PSA and PS<2:0> bits (OPTION<3:0>) determine prescaler assignment and prescale ratio.

When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x, etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT. The prescaler is neither readable nor writable. On a Reset, the prescaler contains all '0's.

#### 7.7 Analog Conversion Result Register

The ADRES register contains the results of the last conversion. These results are present during the sampling period of the next analog conversion process. After the sampling period is over, ADRES is cleared (= 0). A 'leading one' is then right shifted into the ADRES to serve as an internal conversion complete bit. As each bit weight, starting with the MSb, is converted, the leading one is shifted right and the converted bit is stuffed into ADRES. After a total of 9 right shifts of the 'leading one' have taken place, the conversion is complete; the 'leading one' has been shifted out and the GO/DONE bit is cleared.

If the GO/DONE bit is cleared in software during a conversion, the conversion stops. The data in ADRES is the partial conversion result. This data is valid for the bit weights that have been converted. The position of the 'leading one' determines the number of bits that have been converted. The bits that were not converted before the GO/DONE was cleared are unrecoverable.

#### 7.8 Internal Absolute Voltage Reference

The function of the Internal Absolute Voltage Reference is to provide a constant voltage for conversion across the devices VDD supply range. The A/D Converter is ratiometric with the conversion reference voltage being VDD. Converting a constant voltage of 0.6V (typical) will result in a result based on the voltage applied to VDD of the device. The result of conversion of this reference across the VDD range can be approximated by: Conversion Result = 0.6V/(VDD/256)

**Note:** The actual value of the Absolute Voltage Reference varies with temperature and part-to-part variation. The conversion is also susceptible to analog noise on the VDD pin and noise generated by the sinking or sourcing of current on the I/O pins.

#### REGISTER 7-1: ADCON0: A/D CONVERTER 0 REGISTER

| R/W-1 | R/W-1 | U-0 | U-0 | R/W-1 | R/W-1 | R/W-0   | R/W-0 |

|-------|-------|-----|-----|-------|-------|---------|-------|

| ANS1  | ANS0  | —   | —   | CHS1  | CHS0  | GO/DONE | ADON  |

| bit 7 |       |     |     |       |       |         | bit 0 |

| Legend:             |                                                                                                                                                   |                                                                                                                                         |                                      |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| R = Reada           | ble bit W = Writable                                                                                                                              | U = Unimplemented bit,                                                                                                                  | read as '0'                          |

| -n = Value          | at POR '1' = Bit is set                                                                                                                           | '0' = Bit is cleared                                                                                                                    | x = Bit is unknown                   |

| bit 7               | <b>ANS1:</b> ADC Analog Input Pin<br>1 = GP1/AN1 configured for an<br>0 = GP1/AN1 configured as di                                                | og input                                                                                                                                |                                      |

| bit 6               | <b>ANS0:</b> ADC Analog Input Pin<br>1 = GP0/AN0 configured as ar<br>0 = GP0/AN0 configured as di                                                 | nalog input                                                                                                                             |                                      |

| bit 5-4             | Unimplemented: Read as '0'                                                                                                                        |                                                                                                                                         |                                      |

| bit 3-2             | CHS<1:0>: ADC Channel Sele<br>00 = Channel 00 (GP0/AN0)<br>01 = Channel 01 (GP1/AN1)<br>1x = 0.6V absolute Voltage re                             |                                                                                                                                         |                                      |

| bit 1               | by hardware when the Al                                                                                                                           | <ul> <li>Setting this bit starts an ADC conversion<br/>is done converting.</li> <li>Inot in progress. Manually clearing this</li> </ul> |                                      |

| bit 0               | ADON: ADC Enable bit<br>1 = ADC module is operating<br>0 = ADC module is shut-off a                                                               | consumes no power                                                                                                                       |                                      |

| Note 1:<br>2:<br>3: | When the ANS bits are set, the char<br>function previously defined.<br>The ANS<1:0> bits are active regar<br>CHS<1:0> bits default to 11 after an |                                                                                                                                         | to analog mode regardless of the pin |

| 4:                  | If the ADON bit is clear, the GO/DOI                                                                                                              | bit cannot be set.                                                                                                                      |                                      |

| TABLE 9-2: IN | ISTRUCTION SET | SUMMARY |

|---------------|----------------|---------|

|---------------|----------------|---------|

| Mnem    | nonic,    | Description                                       | Cycles           | 12-1      | Bit Opc   | ode       | Status     | Notes    |

|---------|-----------|---------------------------------------------------|------------------|-----------|-----------|-----------|------------|----------|

| Oper    | ands      | Description                                       | Cycles           | MSb       |           | LSb       | Affected   | Notes    |

| ADDWF   | f, d      | Add W and f                                       | 1                | 0001      | 11df      | ffff      | C,DC,Z     | 1,2,4    |

| ANDWF   | f, d      | AND W with f                                      | 1                | 0001      | 01df      | ffff      | Z          | 2,4      |

| CLRF    | f         | Clear f                                           | 1                | 0000      | 011f      | ffff      | Z          | 4        |

| CLRW    | -         | Clear W                                           | 1                | 0000      | 0100      | 0000      | Z          |          |

| COMF    | f, d      | Complement f                                      | 1                | 0010      | 01df      | ffff      | Z          |          |

| DECF    | f, d      | Decrement f                                       | 1                | 0000      | 11df      | ffff      | Z          | 2,4      |

| DECFSZ  | f, d      | Decrement f, Skip if 0                            | 1 <sup>(2)</sup> | 0010      | 11df      | ffff      | None       | 2,4      |

| INCF    | f, d      | Increment f                                       | 1                | 0010      | 10df      | ffff      | Z          | 2,4      |

| INCFSZ  | f, d      | Increment f, Skip if 0                            | 1 <sup>(2)</sup> | 0011      | 11df      | ffff      | None       | 2,4      |

| IORWF   | f, d      | Inclusive OR W with f                             | 1                | 0001      | 00df      | ffff      | Z          | 2,4      |

| MOVF    | f, d      | Move f                                            | 1                | 0010      | 00df      | ffff      | Z          | 2,4      |

| MOVWF   | f         | Move W to f                                       | 1                | 0000      | 001f      | ffff      | None       | 1,4      |

| NOP     | _         | No Operation                                      | 1                | 0000      | 0000      | 0000      | None       |          |

| RLF     | f, d      | Rotate left f through Carry                       | 1                | 0011      | 01df      | ffff      | С          | 2,4      |

| RRF     | f, d      | Rotate right f through Carry                      | 1                | 0011      | 00df      | ffff      | С          | 2,4      |

| SUBWF   | f, d      | Subtract W from f                                 | 1                | 0000      | 10df      | ffff      | C,DC,Z     | 1,2,4    |

| SWAPF   | f, d      | Swap f                                            | 1                | 0011      | 10df      | ffff      | None       | 2,4      |

| XORWF   | f, d      | Exclusive OR W with f                             | 1                | 0001      | 10df      | ffff      | Z          | 2,4      |

|         |           | BIT-ORIENTED FILE REGISTE                         | R OPER           | ATIONS    | ;         |           |            |          |

| BCF     | f, b      | Bit Clear f                                       | 1                | 0100      | bbbf      | ffff      | None       | 2,4      |

| BSF     | f, b      | Bit Set f                                         | 1                | 0101      | bbbf      | ffff      | None       | 2,4      |

| BTFSC   | f, b      | Bit Test f, Skip if Clear                         | 1 <sup>(2)</sup> | 0110      | bbbf      | ffff      | None       |          |

| BTFSS   | f, b      | Bit Test f, Skip if Set                           | 1 <sup>(2)</sup> | 0111      | bbbf      | ffff      | None       |          |

|         |           | LITERAL AND CONTROL C                             | PERATIO          | ONS       |           |           | 1          |          |

| ANDLW   | k         | AND literal with W                                | 1                | 1110      | kkkk      | kkkk      | Z          |          |

| CALL    | k         | Call subroutine                                   | 2                | 1001      | kkkk      | kkkk      | None       | 1        |

| CLRWDT  | k         | Clear Watchdog Timer                              | 1                | 0000      | 0000      | 0100      | TO, PD     |          |

| GOTO    | k         | Unconditional branch                              | 2                | 101k      | kkkk      | kkkk      | None       |          |

| IORLW   | k         | Inclusive OR Literal with W                       | 1                | 1101      | kkkk      | kkkk      | Z          |          |

| MOVLW   | k         | Move Literal to W                                 | 1                | 1100      | kkkk      | kkkk      | None       |          |

| OPTION  | -         | Load OPTION register                              | 1                | 0000      | 0000      | 0010      | None       |          |

| RETLW   | k         | Return, place Literal in W                        | 2                | 1000      | kkkk      | kkkk      | None       |          |

| SLEEP   | -         | Go into standby mode                              | 1                | 0000      | 0000      | 0011      | TO, PD     |          |

| TRIS    | f         | Load TRIS register                                | 1                | 0000      | 0000      | Offf      | None       | 3        |

| XORLW   | k         | Exclusive OR Literal to W                         | 1                | 1111      | kkkk      | kkkk      | Z          |          |

| Note 1: | The 9th b | bit of the program counter will be forced to a '0 | by any i         | nstructio | on that v | vrites to | the PC exc | cept for |

GOTO. See Section 4.7 "Program Counter".

2: When an I/O register is modified as a function of itself (e.g., MOVF PORTB, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

**3:** The instruction TRIS f, where f = 6 causes the contents of the W register to be written to the tri-state latches of PORTB. A '1' forces the pin to a high-impedance state and disables the output buffers.

4: If this instruction is executed on the TMR0 register (and, where applicable, d = 1), the prescaler will be cleared (if assigned to TMR0).

#### 10.2 DC Characteristics: PIC10F220/222 (Extended)

| DC CHA       | RACTER | ISTICS                                        |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature -40×C £ TA £ +125×C (extended) |                          |                      |                                                                                                              |  |  |  |  |

|--------------|--------|-----------------------------------------------|------|--------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------|--------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Param<br>No. | Sym    | Characteristic                                | Min  | Typ <sup>(1)</sup>                                                                                                 | Max                      | Units                | Conditions                                                                                                   |  |  |  |  |

| D001         | Vdd    | Supply Voltage                                | 2.0  |                                                                                                                    | 5.5                      | V                    | See Figure 10-1                                                                                              |  |  |  |  |

| D002         | Vdr    | RAM Data Retention Voltage <sup>(2)</sup>     | 1.5* |                                                                                                                    |                          | V                    | Device in Sleep mode                                                                                         |  |  |  |  |

| D003         | VPOR   | VDD Start Voltage<br>to ensure Power-on Reset | -    | Vss                                                                                                                | -                        | V                    |                                                                                                              |  |  |  |  |

|              | IDD    | Supply Current <sup>(3)</sup>                 |      |                                                                                                                    |                          |                      |                                                                                                              |  |  |  |  |

| D010         |        |                                               |      | 175<br>0.625<br>250<br>0.800                                                                                       | 275<br>1.1<br>400<br>1.5 | μΑ<br>mA<br>μA<br>mA | VDD = 2.0V, Fosc = 4 MHz<br>VDD = 5.0V, Fosc = 4 MHz<br>VDD = 2.0V, Fosc = 8 MHz<br>VDD = 5.0V, Fosc = 8 MHz |  |  |  |  |

|              | IPD    | Power-down Current <sup>(4)</sup>             |      |                                                                                                                    |                          |                      |                                                                                                              |  |  |  |  |

| D020         |        |                                               | _    | 0.1<br>1                                                                                                           | 9<br>15                  | μΑ<br>μΑ             | VDD = 2.0V<br>VDD = 5.0V                                                                                     |  |  |  |  |

|              | Iwdt   | WDT Current <sup>(4)</sup>                    | •    | •                                                                                                                  |                          | -                    | •                                                                                                            |  |  |  |  |

| D022         |        |                                               | _    | 1.0<br>7                                                                                                           | 18<br>22                 | μΑ<br>μΑ             | VDD = 2.0V<br>VDD = 5.0V                                                                                     |  |  |  |  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

**3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

All I/O pins tri-stated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss. The peripheral current is the sum of the base IPD and the additional current consumed when the peripheral is enabled.

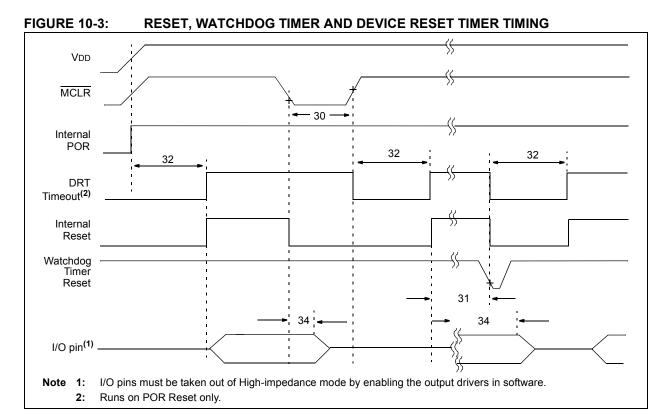

#### RESET, WATCHDOG TIMER AND DEVICE RESET TIMER - PIC10F220/222 TABLE 10-3:

| АС СНА       | ARACTE           | RISTICS                                       | Standard Operating Conditions (unless otherwise specifie         Operating Temperature       -40°C ≤ TA ≤ +85°C (industrial)         -40°C ≤ TA ≤ +125°C (extended)         Operating Voltage VDD range is described in Section 10.1 "Do         Characteristics:         PIC10F220/222 (Industrial)" |                    |              |          |                                                  |  |  |  |

|--------------|------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|----------|--------------------------------------------------|--|--|--|

| Param<br>No. | Sym              | Characteristic                                | Min                                                                                                                                                                                                                                                                                                   | Typ <sup>(1)</sup> | Max          | Units    | Conditions                                       |  |  |  |

| 30           | Тмс <sub>L</sub> | MCLR Pulse Width (low)                        | 2*<br>5*                                                                                                                                                                                                                                                                                              | _                  |              | μS<br>μS | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |  |  |  |

| 31           | Twdt             | Watchdog Timer Time-out Period (no prescaler) | 10<br>10                                                                                                                                                                                                                                                                                              | 18<br>18           | 29<br>31     | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |  |  |

| 32           | Tdrt*            | Device Reset Timer Period<br>(standard)       | 0.600<br>0.600                                                                                                                                                                                                                                                                                        | 1.125<br>1.125     | 1.85<br>1.95 | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |  |  |  |

| 34           | Tioz             | I/O High-impedance from MCLR low              | —                                                                                                                                                                                                                                                                                                     | _                  | 2*           | μS       |                                                  |  |  |  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

© 2005-2013 Microchip Technology Inc.

#### 12.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 12.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

#### 12.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 12.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

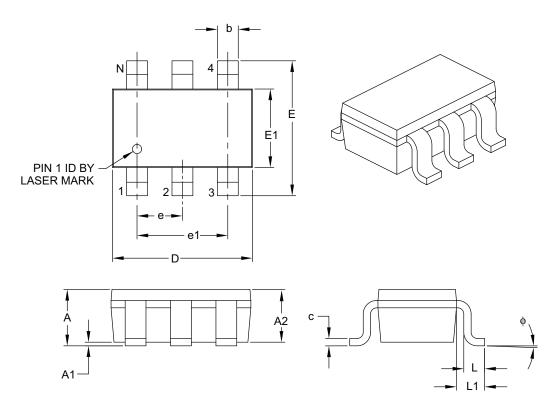

#### 6-Lead Plastic Small Outline Transistor (OT) [SOT-23]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |                  | MILLIMETERS |     | 6    |

|--------------------------|------------------|-------------|-----|------|

| Dimensio                 | Dimension Limits |             | NOM | MAX  |

| Number of Pins           | Ν                | 6           |     |      |

| Pitch                    | е                | 0.95 BSC    |     |      |

| Outside Lead Pitch       | e1               | 1.90 BSC    |     |      |

| Overall Height           | Α                | 0.90        | -   | 1.45 |

| Molded Package Thickness | A2               | 0.89        | -   | 1.30 |

| Standoff                 | A1               | 0.00        | -   | 0.15 |

| Overall Width            | Е                | 2.20        | -   | 3.20 |

| Molded Package Width     | E1               | 1.30        | -   | 1.80 |

| Overall Length           | D                | 2.70        | -   | 3.10 |

| Foot Length              | L                | 0.10        | -   | 0.60 |

| Footprint                | L1               | 0.35        | -   | 0.80 |

| Foot Angle               | φ                | 0°          | -   | 30°  |

| Lead Thickness           | С                | 0.08        | -   | 0.26 |

| Lead Width               | b                | 0.20        | -   | 0.51 |

#### Notes:

- 1. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.127 mm per side.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-028B

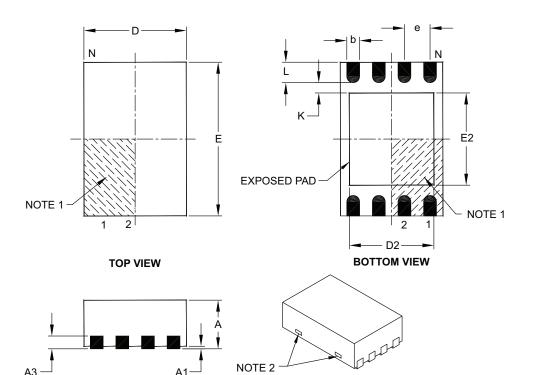

#### 8-Lead Plastic Dual Flat, No Lead Package (MC) – 2x3x0.9 mm Body [DFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                  |                  | MILLIMETERS |      |      |

|------------------------|------------------|-------------|------|------|

|                        | Dimension Limits | MIN NOM MA  |      | MAX  |

| Number of Pins         | N                | 8           |      |      |

| Pitch                  | e                | 0.50 BSC    |      |      |

| Overall Height         | A                | 0.80        | 0.90 | 1.00 |

| Standoff               | A1               | 0.00        | 0.02 | 0.05 |

| Contact Thickness      | A3               | 0.20 REF    |      |      |

| Overall Length         | D                | 2.00 BSC    |      |      |

| Overall Width          | E                | 3.00 BSC    |      |      |

| Exposed Pad Length     | D2               | 1.30        | -    | 1.55 |

| Exposed Pad Width      | E2               | 1.50        | -    | 1.75 |

| Contact Width          | b                | 0.20        | 0.25 | 0.30 |

| Contact Length         | L                | 0.30        | 0.40 | 0.50 |

| Contact-to-Exposed Pad | К                | 0.20        | -    | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-123C

### INDEX

|   | ۰. |

|---|----|

| , | ۰. |

| A/D                                      |    |

|------------------------------------------|----|

| Specifications                           | 60 |

| ADC                                      |    |

| Internal Sampling Switch (RSS) IMPEDANCE | 32 |

| Source Impedance                         | 32 |

| ALU                                      | 9  |

| Assembler                                |    |

| MPASM Assembler                          | 62 |

|                                          |    |

### В

| Block Diagram                |    |

|------------------------------|----|

| •                            |    |

| On-Chip Reset Circuit        |    |

| Timer0                       |    |

| TMR0/WDT Prescaler           |    |

| Watchdog Timer               | 39 |

| Block Diagrams               |    |

| Analog Input Model           |    |

| Brown-Out Protection Circuit |    |

#### С

| C Compilers                          |    |

|--------------------------------------|----|

| MPLAB C18                            |    |

| MPLAB C30                            |    |

| Carry                                | 9  |

| Clocking Scheme                      |    |

| Code Protection                      |    |

| Configuration Bits                   |    |

| Customer Change Notification Service |    |

| Customer Notification Service        | 75 |

| Customer Support                     | 75 |

|                                      |    |

### D

| DC and AC Characteristics | 65 |

|---------------------------|----|

| Development Support       | 61 |

| Digit Carry               | 9  |

### Е

### F

| Family of Devices |   |

|-------------------|---|

| PIC10F22X         | 5 |

| FSR               |   |

|                   |   |

#### G

| GPIO                                     | 21       |

|------------------------------------------|----------|

| I                                        |          |

| I/O Interfacing                          | 21       |

| I/O Ports                                | 21       |

| I/O Programming Considerations           | 23       |

| ID Locations                             | . 33, 41 |

| INDF                                     | 20       |

| Indirect Data Addressing                 | 20       |

| Instruction Cycle                        | 11       |

| Instruction Flow/Pipelining              |          |

| Instruction Set Summary                  | 44       |

| Internal Sampling Switch (RSS) IMPEDANCE | 32       |

| Internet Address                         | 75       |

| L                                        |          |

| Loading of PC 19 |

|------------------|

|------------------|

### Μ

| Memory Organization       13         Data Memory       14         Program Memory (PIC10F220)       13         Program Memory (PIC10F222)       13         Microchip Internet Web Site       75         MPLAB ASM30 Assembler, Linker, Librarian       62         MPLAB ICD 2 In-Circuit Debugger       63         MPLAB ICE 2000 High-Performance Universal       1         In-Circuit Emulator       63         MPLAB Integrated Development Environment Software       61         MPLAB REAL ICE In-Circuit Emulator System       63         MPLINK Object Linker/MPLIB Object Librarian       62 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| OPTION Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| PIC10F220/222 Device Varieties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Power-on Reset (POR)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| TO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Power-down Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Prescaler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| Q                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Q cycles 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Reader Response       76         Read-Modify-Write       23         Register File Map       PIC10F220         PIC040F2020       14                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| PIC10F22214<br>Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| Special Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| Reset         33           Reset on Brown-Out         40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| Sleep                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| Software Simulator (MPLAB SIM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Special Features of the CPU 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Special Function Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Stack                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

### Т

| Timer0                                         |    |

|------------------------------------------------|----|

| Timer0                                         | 25 |

| Timer0 (TMR0) Module                           | 25 |

| TMR0 with External Clock                       | 26 |

| Timing Parameter Symbology and Load Conditions | 57 |

| TRIS Registers                                 | 21 |

|                                                |    |

#### W

| Wake-up from Sleep         | 41     |

|----------------------------|--------|

| Watchdog Timer (WDT)       | 33, 38 |

| Period                     |        |

| Programming Considerations |        |

| WWW Address                | 75     |

| WWW, On-Line Support       | 3      |

| Z                          |        |

| Zero bit                   | 9      |